# Carnegie Mellon University

# CARNEGIE INSTITUTE OF TECHNOLOGY

# **THESIS**

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF Doctor of Philosophy

| TITLE          | Dependable Cyber-Physical Syst           | ems                 |

|----------------|------------------------------------------|---------------------|

|                |                                          |                     |

|                |                                          |                     |

| PRESENTED BY   | Junsung Kim                              |                     |

| ACCEPTED BY TH | HE DEPARTMENT OF                         |                     |

|                | Electrical and Computer Engine           | eering              |

|                | Raj Rajkumar<br>ADVISOR, MAJOR PROFESSOR | May 1, 2014<br>DATE |

|                | Jelena Kovacevic<br>DEPARTMENT HEAD      | May 1, 2014<br>DATE |

| APPROVED BY TH | HE COLLEGE COUNCIL                       |                     |

|                | Vijayakumar Bhagavatula<br>DEAN          | May 2, 2014<br>DATE |

# **Dependable Cyber-Physical Systems**

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

**Electrical and Computer Engineering**

# Junsung Kim

M.S., Electrical Engineering, Korea Advanced Institute of Science and Technology B.S., Electrical Engineering, Korea Advanced Institute of Science and Technology

Carnegie Mellon University Pittsburgh, PA

May 2014

© 2014 Junsung Kim. All rights reserved.

#### **Abstract**

CPS (Cyber-Physical Systems) enable a new class of applications that perceive their surroundings using raw data from sensors, monitor the timing of dynamic processes, and control the physical environment. Since failures and misbehaviors in application domains such as cars, medical devices, nuclear power plants, etc., may cause significant damage to life and/or property, CPS need to be safe and dependable. A conventional way of improving dependability is to use redundant hardware to replicate the whole (sub)system. Although hardware replication has been widely deployed in conventional mission-critical systems, it is cost-prohibitive to many emerging CPS application domains. Hardware replication also leads to limited system flexibility.

This dissertation studies the problem of making CPS affordably dependable and develops a system-level framework that manages critical CPS resources including processors, networks, and sensors. Our framework called SAFER (System-level Architecture for Failure Evasion in Real-time applications) incorporates configurable software mechanisms and policies to tolerate failures of critical CPS resources while meeting their timing constraints. It supports adaptive graceful degradation, the effective use of different sensor modalities, and the fault-tolerant schemes of hot standby, cold standby, and re-execution. SAFER reliably and efficiently allocates tasks and their backups to CPU and sensor resources while satisfying network traffic constraints. It also fuses and (re)configures sensor data used by tasks to recover from system failures. The SAFER framework aims to guarantee the timeliness of different types of tasks that fall into one of four categories: (1) tasks with periodic arrivals, (2) tasks with continually varying periods, (3) tasks with parallel threads, and (4) tasks with self-suspensions. We offer the schedulability analyses and runtime sup-

port for such tasks with and without resource failures. Finally, the functionality of the proposed system is evaluated on a self-driving car using SAFER. We conclude that the proposed framework analytically satisfies timing constraints and predictably operates systems with and without resource failures, hence making CPS dependable and timely.

### Acknowledgments

It has been a long journey to my PhD, but I have been lucky enough to work with talented, thoughtful, and passionate people from CMU (Carnegie Mellon University), RTML (Real-Time Multimedia and Systems Lab), GM-CMU ADCRL (General Motors-Carnegie Mellon Autonomous Driving Collaborative Research Lab), GM (General Motors), and SEI (Software Engineering Institute). I am also grateful to GM, NSF (National Science Foundation), and Goel Graduate Fellowship for funding my research.

My first and foremost thanks go to my adviser Prof. Raj Rajkumar. Since the first time I met him at CMU in 2008, he has been a good mentor and teacher. His endless creative ideas always intrigued me. His passions in his research resonated with me so that I could have countless sleepless nights to accomplish my goals. He always carefully listened to what I said and gave me sincere comments. Also, when I confronted personal problems, he was never hesitant to help me by sharing his experience, providing indirect support, and stepping up for me.

I would like to sincerely thank my thesis committee members: Prof. Dan Siewiorek, Prof. Anthony Rowe, and Dr. Markus Jochim. Prof. Dan Siewiorek always surprised me by providing different research perspectives and encouraged me to focus on the basics of research. Prof. Anthony Rowe's bright ideas always inspired me to be a thrill-seeking researcher. As a former RTML member, he has also been a good friend of mine and helped me in shaping my research ideas and getting used to Pittsburgh. Dr. Markus Jochim always encouraged me to maintain balance between academic and pragmatic thinking. This in turn helped me a lot in identifying exciting research problems.

Without RTML members, I could not have completed my Ph.D. I deeply thank

all who spent much time with me: Reza Azimi, Sheryl Benicky, Gaurav Bhatia, Max Buevich, Yong Hoon Choi, Alexei Colin, Vikram Gupta, Dr. Arvind Kandhalu, Prof. Shinpei Kato, Hyoseung Kim, Dr. Karthik Lakshmanan, Jay Reppert, Prof. Anthony Rowe, and Dr. Young-Woo Seo. Reza's cheerfulness spread to me. Gaurav has always been there to have good food, coffee, and discussions together. Vikram and I shared lots of pseudo-masala tea at the CIC (Collaborative Innovation Center) kitchen. The conversations with Arvind and Karthik at 3 a.m. were always productive. I still remember our special breakfast at 6 a.m. after a paper submission, and I hope to have more fun time with them in the near future. Shinpei's boundless energy always kept me awake. I also enjoyed Korean-centric discussions with Hyoseung days and nights. Young-Woo helped me with understanding new research areas. Sheryl always fed us very nice foods for long meetings.

My childhood dream was to make KITT from Knight Rider. I was delighted to be part of GM-CMU ADCRL as I could see that having KITT was not a dream anymore. I appreciate our team members tirelessly working and achieving the impossible: Jason Atwood, Hyunggi Cho, Dr. John Dolan, Tianyu Gu, JongHo Lee, Bruce Li, Dr. Paul Rybski, Alok Sharma, Jarrod Snider, Junqing Wei, and Wenda Xu. I appreciated John's disciplined group management. He always helped me with getting more organized in very complex environment. Being in an autonomous vehicle with Jarrod, JongHo, Junqing, Tianyu, and Wenda was always fun and exciting. Their infinite passion for autonomous driving made me proud of contributing to our automated vehicle. I was grateful that I could work with them.

Thankfully, I was able to work with excellent researchers from GM and SEI: Dr. Markus Jochim, Massimo Osella, Dr. Björn Andersson, and Dr. Dionisio de Niz. I was able to learn about the automotive industry much as Massimo was very inclusive when I was a student intern at GM. The discussions with Björn and Dio were

insightful and helped me with understanding the state-of-the-are real-time theories. I also had great opportunities to work with bright students: Dipendra Kumar Misra, Praful Puranik, and Uttkarsh Sarraf. I am thankful for all the support they have given me.

I thank the KDisTech members who made my Pittsburgh life more lively: Sang Kil Cha, Hyeju Jang, Hanbyul Joo, Minhee Jun, Gunhee Kim, Soonho Kong, Jay-Yoon Lee, Seunghak Lee, Soochahn Lee, Shane Moon, Hyun Soo Park, JunBum Shin, Seungmoon Song, Daegun Won, and Sungwook Yang. I deeply thank my friends who have backed me for decades: Fantastic Bundang 4 (Hyungbin Ahn, Minchul Kim, and Insun Park), my long-time roommate Moonseok Lee, (chu-) Tae-Hoon Choi, Sangchul Kim, Cheeta EunJung Li, and Michigan dudes Jay-Yong Lee and Maesoon Im.

My final and deepest thanks go to mom, dad, my sister, and my lovely wife Min Kyung Lee. My dad has taught me how to live. My mom has shown me how to love. Thank you so much for being my parents. My little sister has always been encouraging and supportive. I am grateful that you are always together with mom and dad in Korea. My wife Min has been my closest friend, companion, and advisor. I would never have completed this dissertation without her. Thank you for your support, understanding, and love.

# **Contents**

| 1 | Intr | oduction                                                      | 1  |

|---|------|---------------------------------------------------------------|----|

|   | 1.1  | Thesis Statement                                              | 3  |

|   | 1.2  | Scope of the Thesis                                           | 4  |

|   | 1.3  | Approach Overview                                             | 7  |

| 2 | Lite | rature Review                                                 | 15 |

|   | 2.1  | Resource Allocation for Fault-tolerant Computing              | 15 |

|   | 2.2  | Schedulability Analysis for Cyber-Physical Systems            | 16 |

|   | 2.3  | Runtime Support for Fault-tolerance Features                  | 22 |

| 3 | Reso | ource Allocation for Fault-Tolerant Computing                 | 25 |

|   | 3.1  | Design Implications                                           | 28 |

|   | 3.2  | Task Allocation with Hot Standby and Cold Standby Replication | 33 |

|   | 3.3  | Evaluation                                                    | 41 |

|   | 3.4  | Summary                                                       | 45 |

| 4 | Faul | lt-Tolerant Computing in the Automotive Context               | 47 |

|   | 4.1  | Motivation                                                    | 47 |

|   | 4.2  | System Model and Design                                       | 51 |

|   | 4.3  | Fault-Tolerant SW-C Allocation with Application Flows         | 57 |

|   | 4.4  | Fault-Tolerance with AUTOSAR                                  | 62 |

| 5 | Task | ss with Continually Varying Periods                                         | 73    |

|---|------|-----------------------------------------------------------------------------|-------|

|   | 5.1  | The Rhythmic Task Model                                                     | . 77  |

|   | 5.2  | One Rhythmic Task and One Periodic Task                                     | . 81  |

|   | 5.3  | One Rhythmic Task and Many Periodic Tasks                                   | . 88  |

|   | 5.4  | Case Study of the Rhythmic Task Model                                       | . 95  |

|   | 5.5  | Summary                                                                     | . 98  |

| 6 | Task | ks with Parallel Threads                                                    | 101   |

|   | 6.1  | System Model and Assumptions                                                | . 104 |

|   | 6.2  | Scheduling Fork-Join Real-Time Tasks                                        | . 107 |

|   | 6.3  | Resource Augmentation Bound Analysis for Global Deadline Monotonic Schedul- |       |

|   |      | ing                                                                         | . 111 |

|   | 6.4  | Global Scheduling on Linux/RK                                               | . 115 |

|   | 6.5  | Case Study on Self-Driving Car                                              | . 117 |

|   | 6.6  | Summary                                                                     | . 121 |

| 7 | Task | ks with Self-Suspensions                                                    | 123   |

|   | 7.1  | System Model and Assumptions                                                | . 126 |

|   | 7.2  | Fixed Priority Scheduling for Self-Suspending Tasks                         | . 128 |

|   | 7.3  | Segment-Fixed Priority Scheduling                                           | . 141 |

|   | 7.4  | Evaluation                                                                  | . 143 |

|   | 7.5  | Summary                                                                     | . 145 |

| 8 | Run  | time Support for Fault-tolerance Features                                   | 149   |

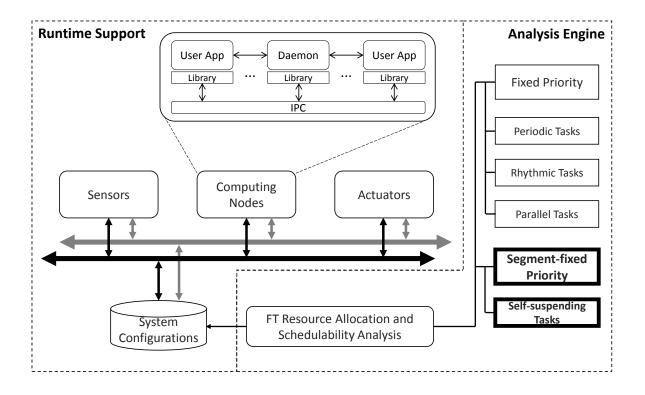

|   | 8.1  | The Architecture of SAFER                                                   | 151   |

| Bi | bliogi | raphy                     | 193 |

|----|--------|---------------------------|-----|

|    | 9.2    | Future work               | 189 |

|    | 9.1    | Contributions             | 186 |

| 9  | Con    | clusions and Future Work  | 185 |

|    | 8.7    | Summary                   | 182 |

|    | 8.6    | Sensor Failure Recovery   | 176 |

|    | 8.5    | Actuator Failure Recovery | 171 |

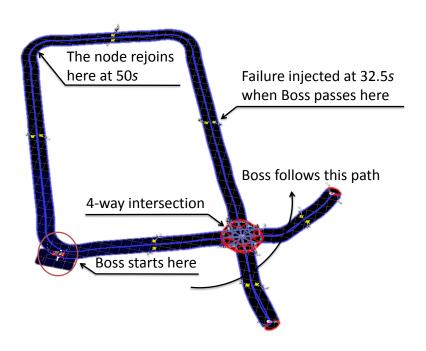

|    | 8.4    | Case study on Boss        | 168 |

|    | 8.3    | Evaluation                | 163 |

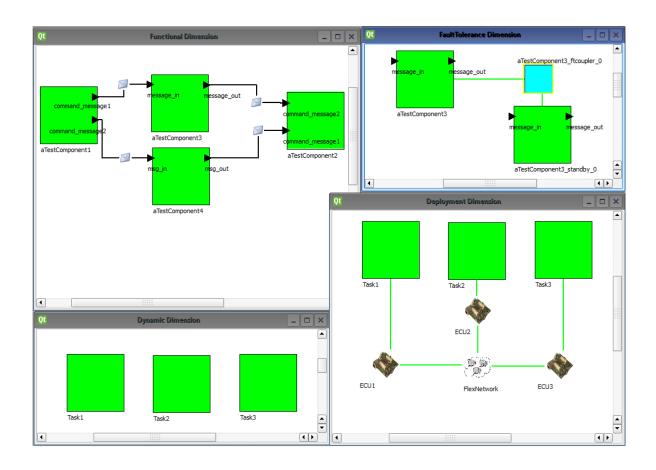

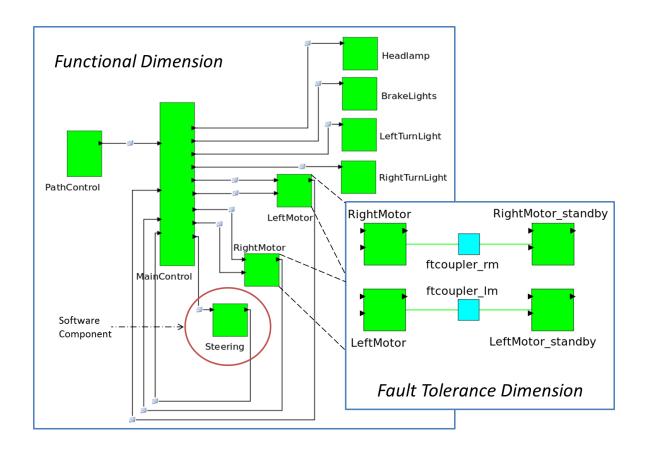

|    | 8.2    | SysWeaver Integration     | 162 |

# **List of Figures**

| 1.1 | Autonomous vehicle research platform developed at CMU                                       | 2  |

|-----|---------------------------------------------------------------------------------------------|----|

| 1.2 | Overview of the dissertation                                                                | 4  |

| 1.3 | Design space of the dissertation                                                            | 5  |

| 3.1 | Resource allocation for fault-tolerant computing in the dissertation overview               | 25 |

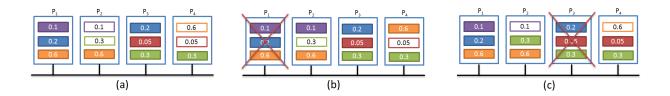

| 3.2 | Example operation scenario of hot standby and cold standby. (a) normal case (b)             |    |

|     | $P_1$ has failed, and the tasks on $P_1$ have been recovered. (c) $P_3$ has failed, and the |    |

|     | tasks on $P_3$ have been recovered                                                          | 31 |

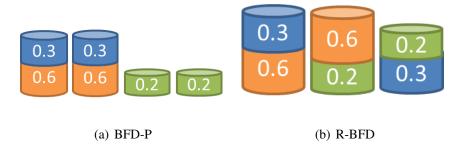

| 3.3 | Benefit of using R-BFD                                                                      | 36 |

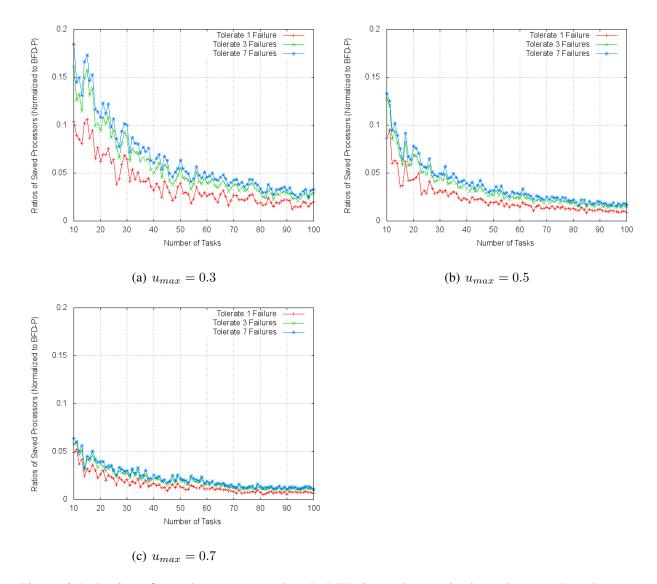

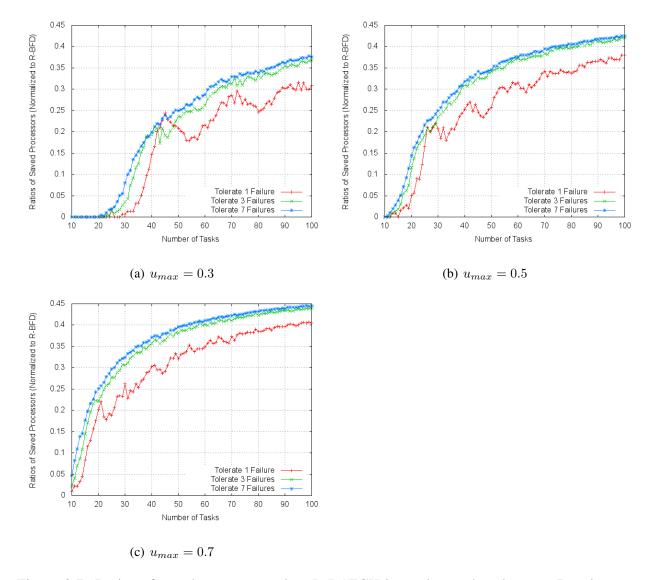

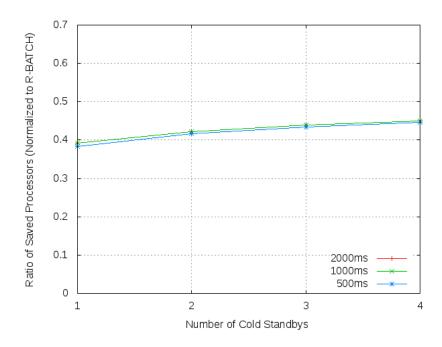

| 3.4 | Ratios of saved processors when R-BFD is used on a single-node case                         | 41 |

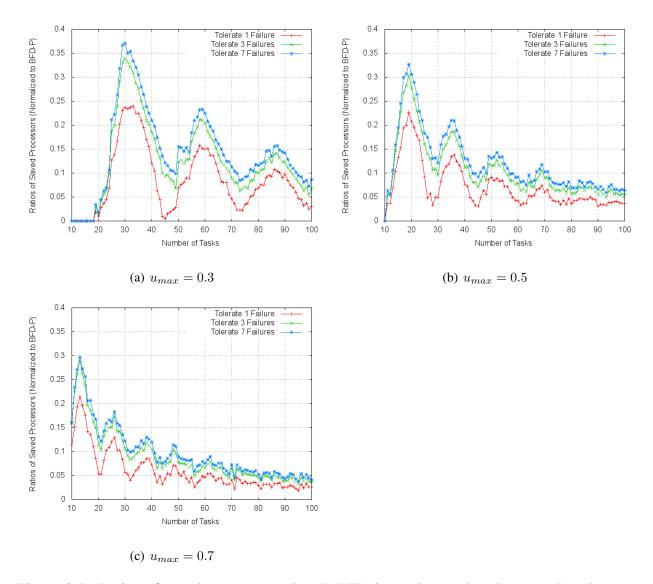

| 3.5 | Ratios of saved processors when R-BFD is used on a 4-node case                              | 42 |

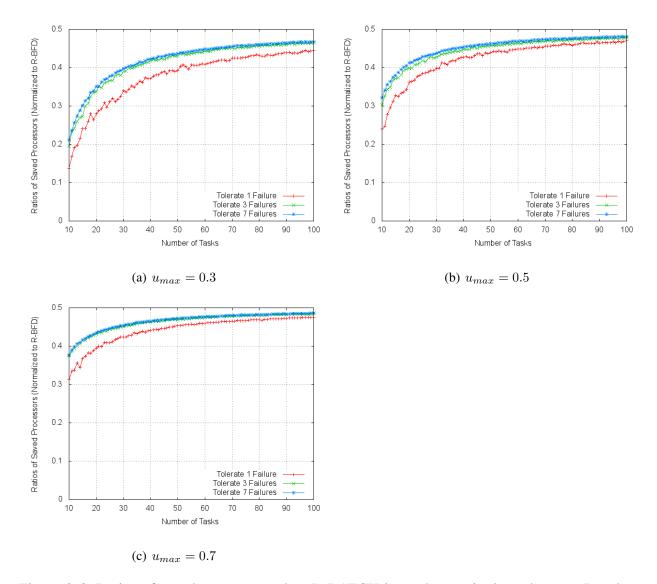

| 3.6 | Ratios of saved processors when R-BATCH is used on a single-node case                       | 43 |

| 3.7 | Ratios of saved processors when R-BATCH is used on a 4-node case                            | 44 |

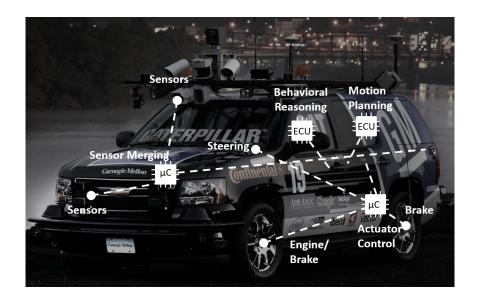

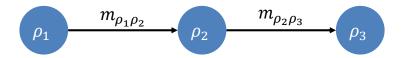

| 4.1 | Application flow model depicted on an autonomous vehicle                                    | 49 |

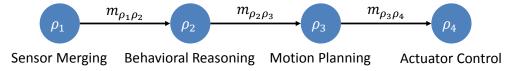

| 4.2 | Example of the application flow                                                             | 49 |

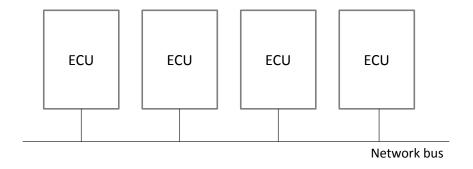

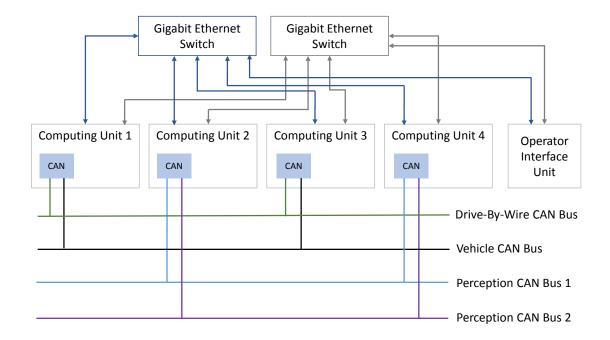

| 4.3 | Abstracted hardware architecture of an AUTOSAR-compliant platform                           | 53 |

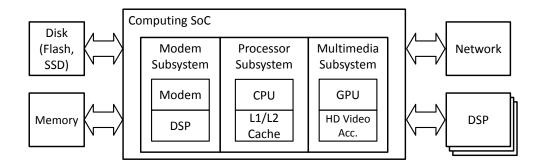

| 4.4 | Graph representation of an application flow $A.$                                            | 58 |

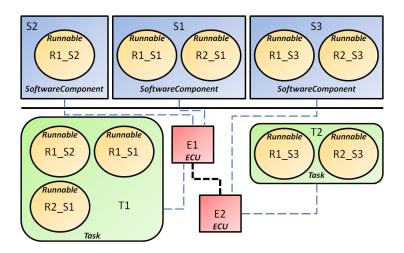

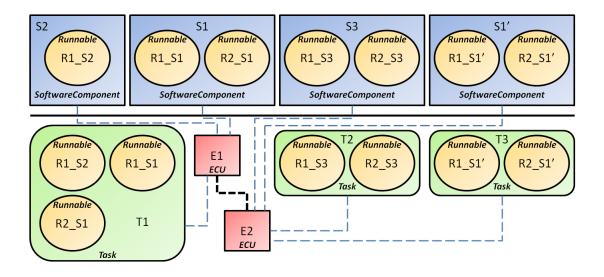

| 4.5 | An example configuration without replication                                                | 64 |

| 4.6 | An example configuration with replication                                                   | 65 |

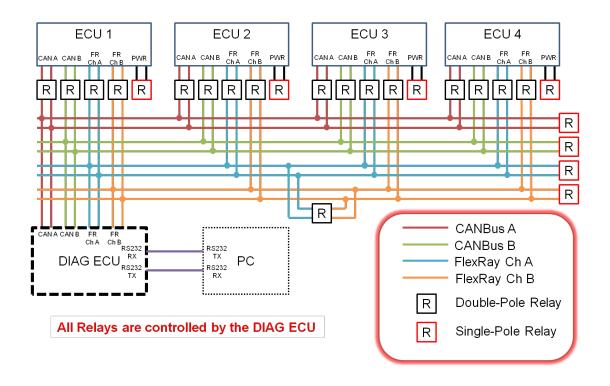

| 4.7 | Testbench architecture                                                                      | 66 |

| 4.8  | SysWeaver system model                                                                             | 67  |

|------|----------------------------------------------------------------------------------------------------|-----|

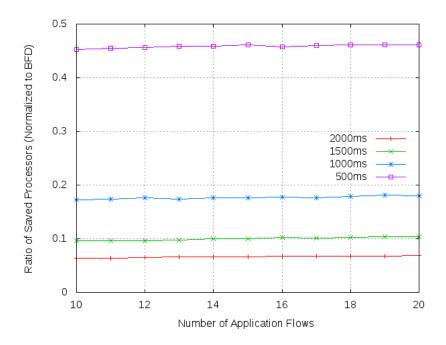

| 4.9  | Ratios of saved processors when FBFD is used with varying number of applica-                       |     |

|      | tion flows                                                                                         | 69  |

| 4.10 | Ratios of saved processors when FBFD is used with varying number of SW-Cs                          | 70  |

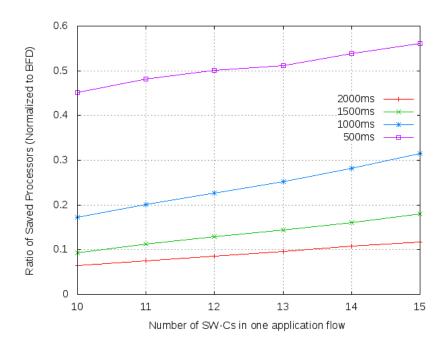

| 4.11 | Ratios of saved processors when R-FLOW is used with hot standbys                                   | 71  |

| 4.12 | Ratios of saved processors when R-FLOW is used with cold standbys                                  | 72  |

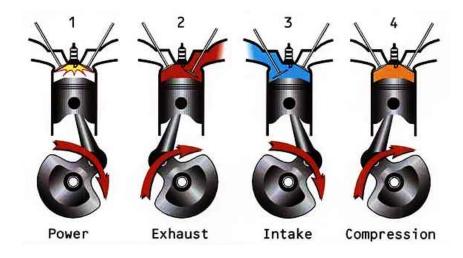

| 5.1  | Tasks with continually varying periods in the dissertation overview                                | 73  |

| 5.2  | Four-stroke cycle in gasoline engines                                                              | 74  |

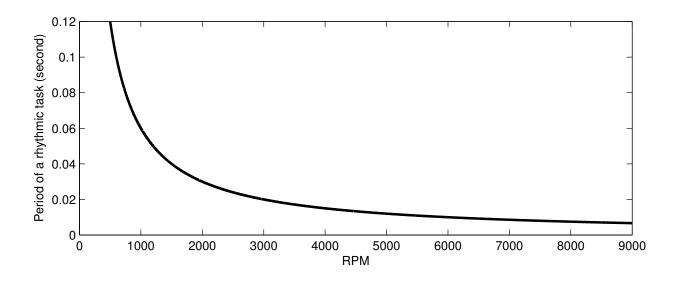

| 5.3  | The variation of period according to engine RPM                                                    | 76  |

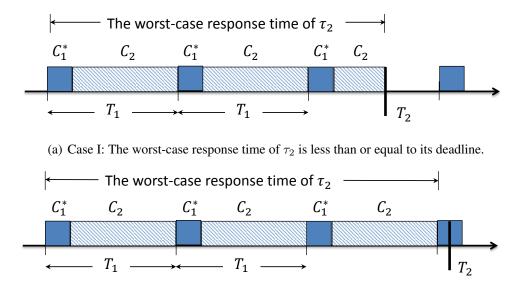

| 5.4  | Two different cases to consider to prove <i>Lemma</i> 9                                            | 79  |

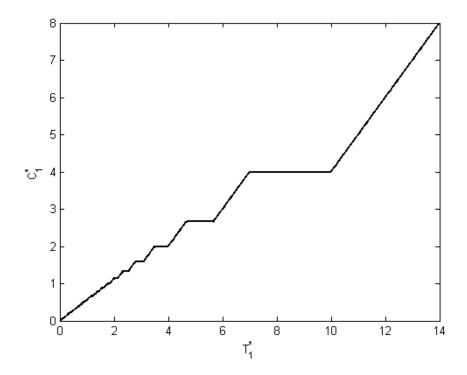

| 5.5  | Schedulable region of the taskset including $\tau_1^*$ and $\tau_2$ as (6,14)                      | 83  |

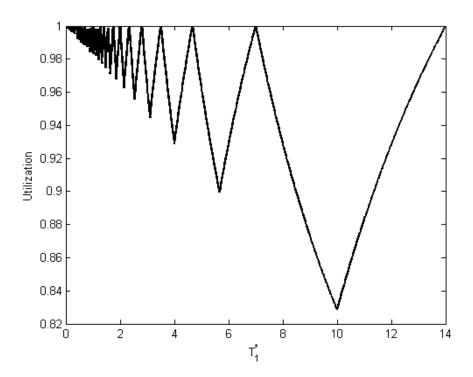

| 5.6  | Corresponding utilization value where there are one rhythmic task and one peri-                    |     |

|      | odic task, (6,14)                                                                                  | 84  |

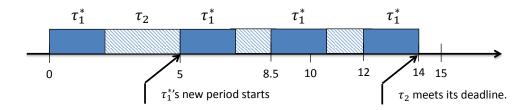

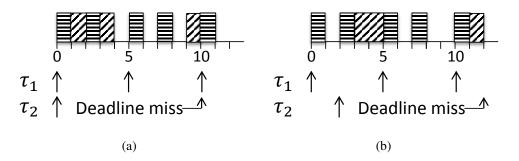

| 5.7  | The example scenario when a rhythmic task accelerates                                              | 86  |

| 5.8  | An example for a rhythmic task with 3 periodic tasks: $\tau_2$ : $(1,7)$ , $\tau_3$ : $(1,10)$ and |     |

|      | $\tau_4$ : (1, 23)                                                                                 | 90  |

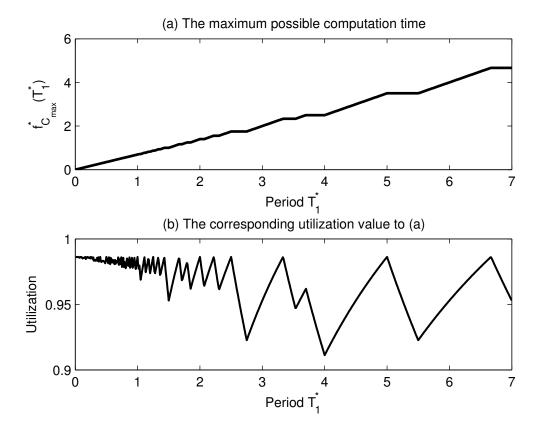

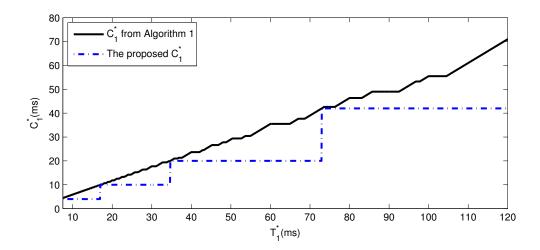

| 5.9  | The maximum possible computation time for a rhythmic task that has varying                         |     |

|      | period from 7.5ms to 120ms with 9 periodic tasks                                                   | 94  |

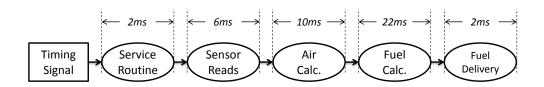

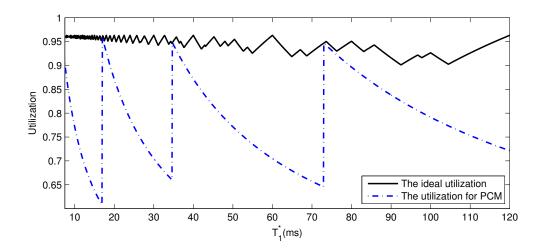

| 5.10 | Flow diagram for the start of injection in PCM software                                            | 95  |

| 5.11 | The corresponding utilization value to Figure 5.9 for a rhythmic task that has                     |     |

|      | varying period from $7.5ms$ to $120ms$ with 9 periodic tasks                                       | 96  |

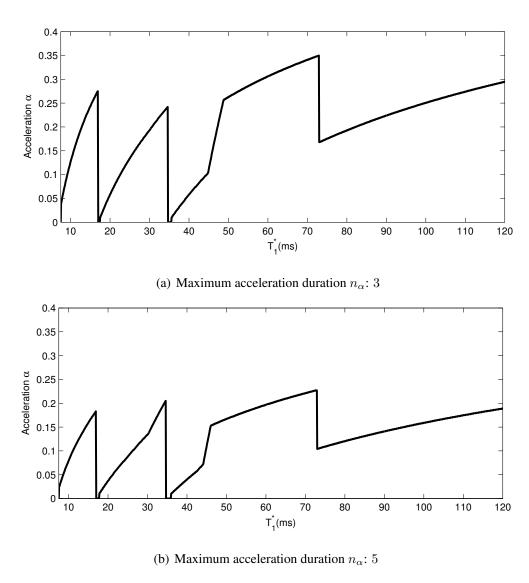

| 5.12 | Plots of acceleration values for a rhythmic task that has varying period from                      |     |

|      | 7.5ms to $120ms$ with 9 periodic tasks                                                             | 97  |

| 6.1  | Tasks with parallel threads in the dissertation overview                                           | 101 |

| 6.2  | A motion planning algorithm for autonomous driving                                                 | 102 |

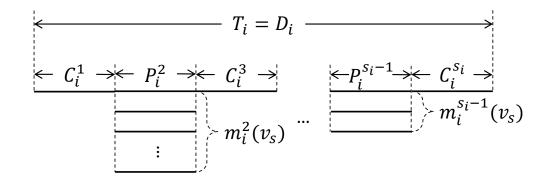

| 6.3  | A fork-join real-time task model                                                                   | 105 |

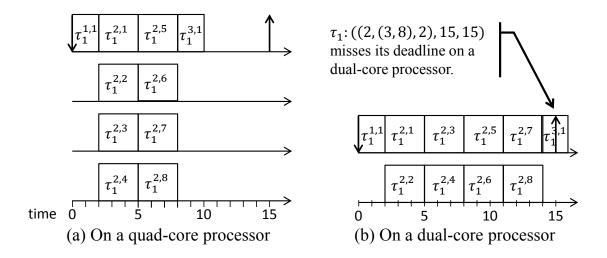

| 6.4  | $\tau_1:((2,(3,8),2),15,15)$ misses its deadline on a dual-core processor, but not                        |

|------|-----------------------------------------------------------------------------------------------------------|

|      | on a quad-core processor                                                                                  |

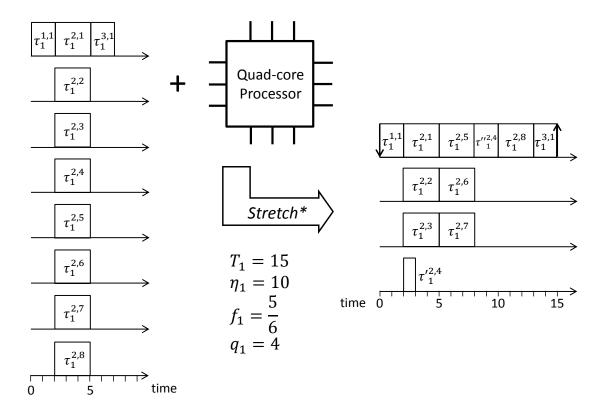

| 6.5  | The task $stretch^*$ transformation example with $\tau_1:((2,(3,8),2),15,15)110$                          |

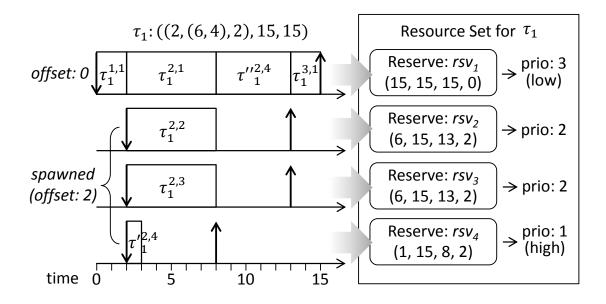

| 6.6  | CPU resource abstraction for a parallel task with global DM scheduling 116                                |

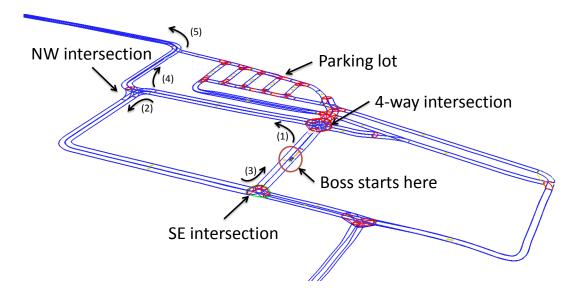

| 6.7  | The map followed by an autonomous vehicle                                                                 |

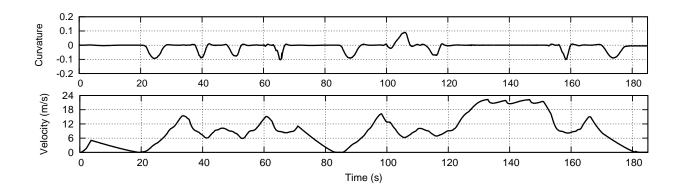

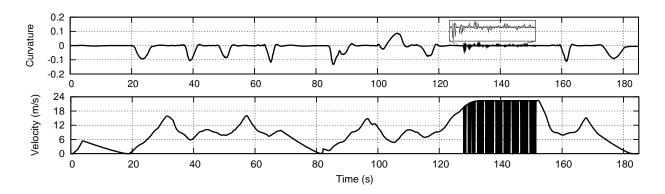

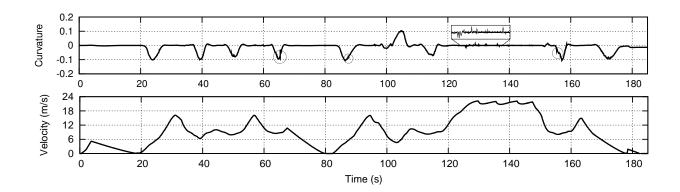

| 6.8  | Curvature and velocity profiles during the entire journey of Boss illustrated in                          |

|      | Figure 6.7                                                                                                |

| 6.9  | Curvature and velocity profiles of Boss when conventional resource reservation                            |

|      | is used                                                                                                   |

| 6.10 | Curvature and velocity profiles of Boss when previously known techniques [1]                              |

|      | are used                                                                                                  |

| 7.1  | Tasks with self-suspensions in the dissertation overview                                                  |

| 7.2  | Modern SoC architecture                                                                                   |

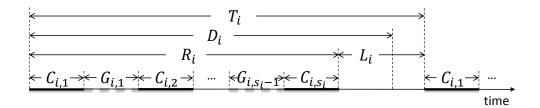

| 7.3  | A multi-segment self-suspending real-time task model                                                      |

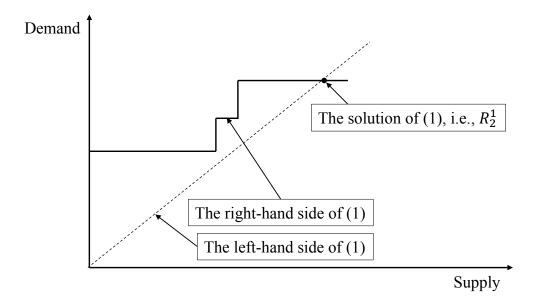

| 7.4  | The illustration of Equation (7.1) to find the response time of $\tau_2$                                  |

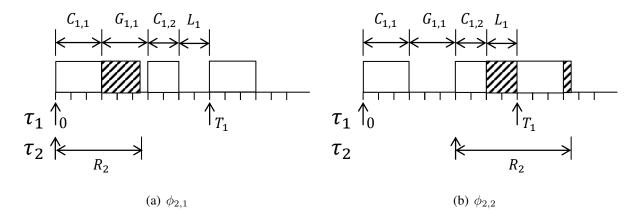

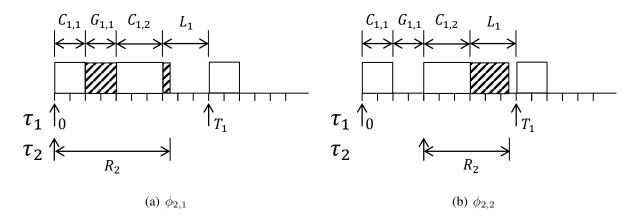

| 7.5  | $R_2$ in the case of $(C_{1,1} \ge C_{1,2}) \land (G_{1,1} \ge L_1) \land (G_{1,1} \ge C_2 > L_1)$ 131    |

| 7.6  | $R_2$ in the case of $(C_{1,1} < C_{1,2}) \land (G_{1,1} < L_1) \land (G_{1,1} < C_2 \le L_1) \ldots 133$ |

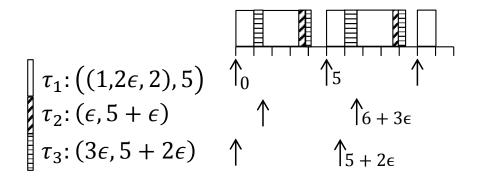

| 7.7  | An exemplary taskset, where the worst case phasing between $	au_2$ and $	au_1$ is differ-                 |

|      | ent from the one between $\tau_3$ and $\tau_1$                                                            |

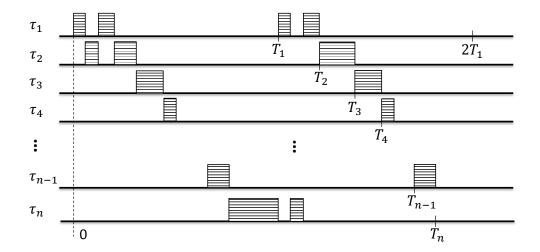

| 7.8  | The worst-case phasing for a taskset having one self-suspending task and $n-1$                            |

|      | non-suspending tasks                                                                                      |

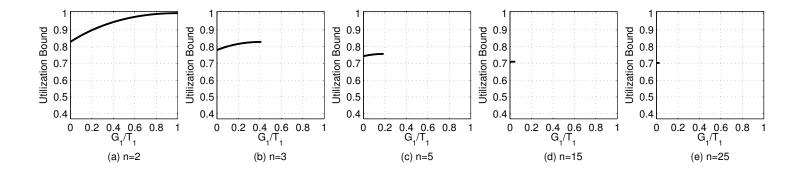

| 7.9  | Utilization bound for a taskset having one self-suspending task and $n-1$ non-                            |

|      | suspending tasks                                                                                          |

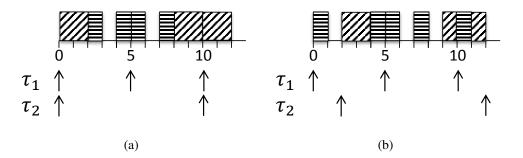

| 7.10 | Scheduling $\tau_1$ : $((1,1,1),5)$ and $\tau_2$ : $((2,5,2),10)$ with rate monotonic scheduling. 140     |

| 7.11 | Scheduling $\tau_1$ : $((1,1,1),5)$ and $\tau_2$ : $((2,5,2),10)$ with segment-fixed priority             |

|      | scheduling                                                                                                |

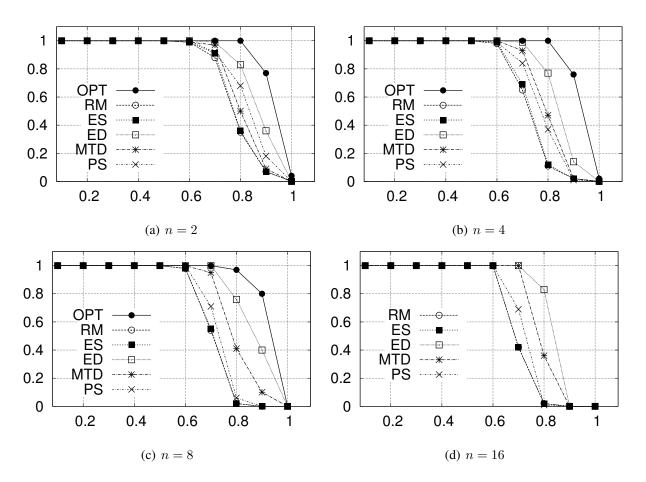

| 7.12 | Schedulability analysis results when $\max_{\forall i \in \Gamma} G_i/T_i = 0.1$ . The number of tasks |

|------|--------------------------------------------------------------------------------------------------------|

|      | varies from 2 to 16. The x-axis represents the maximum total utilization of                            |

|      | the randomly generated tasksets. The y-axis denotes the ratio of the number                            |

|      | of schedulable tasksets to the number of generated tasksets. For example, 0.5                          |

|      | means that half of the randomly generated tasksets are schedulable                                     |

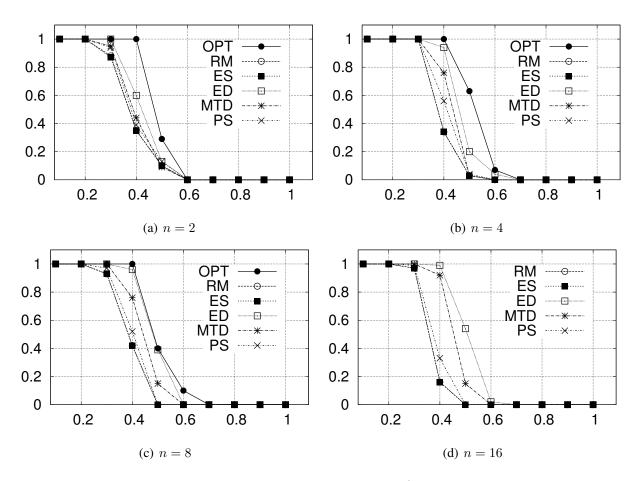

| 7.13 | Schedulability analysis results when $\max_{\forall i \in \Gamma} G_i/T_i = 0.6$ . The same axis defi- |

|      | nition as Figure 7.12 is used                                                                          |

| 8.1  | Runtime support for fault-tolerance features in the dissertation overview 149                          |

| 8.2  | The overall architecture of SAFER                                                                      |

| 8.3  | The primary-backup architecture                                                                        |

| 8.4  | The cold standby operation                                                                             |

| 8.5  | Fault-tolerance dimension in SysWeaver                                                                 |

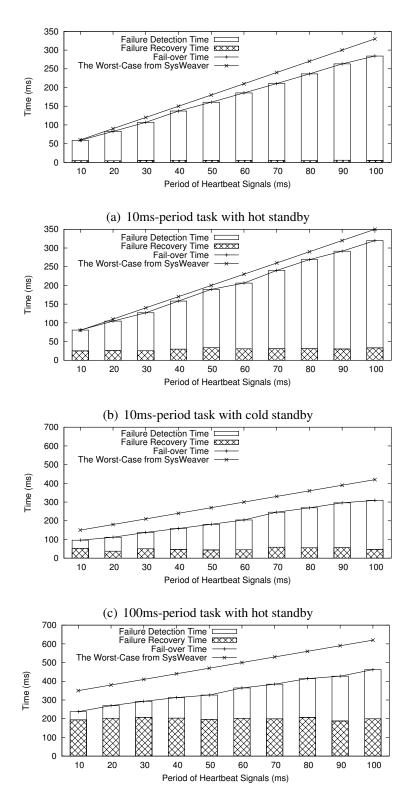

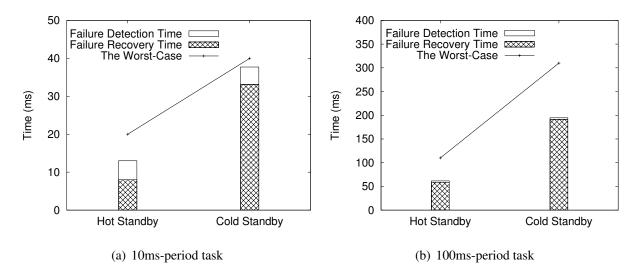

| 8.6  | Fail-over time measurements when time-based detection is used                                          |

| 8.7  | Fail-over time measurements when event-based detection is used                                         |

| 8.8  | The map that an autonomous vehicle follows during the simulation 168                                   |

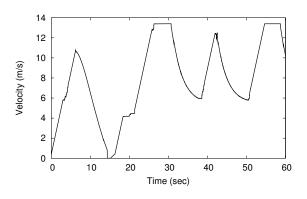

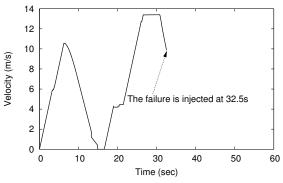

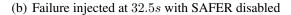

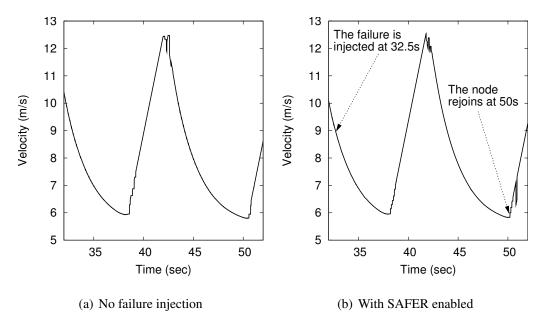

| 8.9  | The velocity trace of an autonomous vehicle measured from ControllerTask. 170                          |

| 8.10 | The scaled version of Figure 8.9(a) and 8.9(c)                                                         |

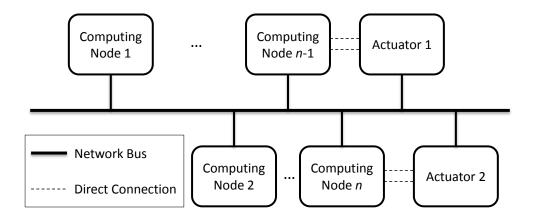

| 8.11 | An example of actuator connections on SAFER                                                            |

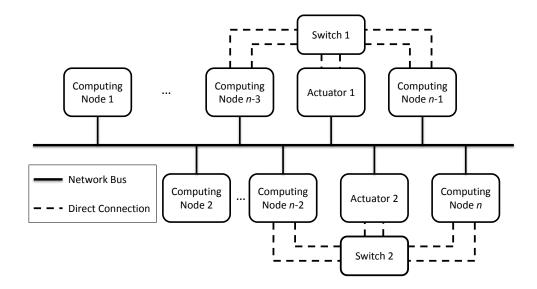

| 8.12 | An example of actuator connections with switches on SAFER                                              |

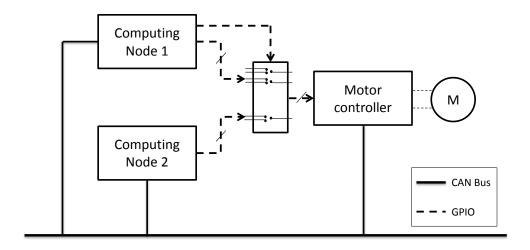

| 8.13 | A detailed switch diagram with the primary and standby nodes 175                                       |

| 8.14 | An abstracted computing hardware architecture of the automated SRX 178                                 |

| 8.15 | An example of interchange advance guide signs                                                          |

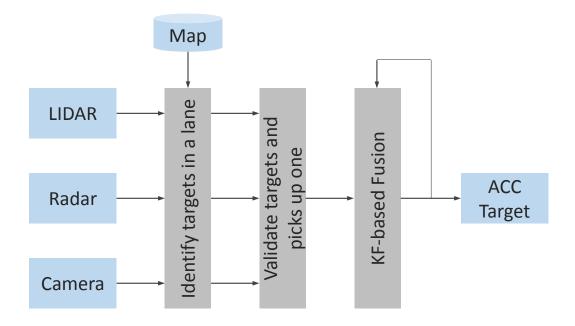

| 8.16 | The procedure block diagram of ACCTargetSelector                                                       |

# **List of Tables**

| 5.1 | Rhythmic task model notation.      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|-----|------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| J.1 | Mily tilline task inodel notation. | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |

# **List of Algorithms**

| 1  | $R-PACK(\Omega : \{O_1,, O_n\}, \Pi : \{\Pi_1,, \Pi_n\}, P : \{P_1,, P_m\})  .  .  .  .  .  35$                                                                                                                                                                                                                                                                                                      |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | R-BFD( $\Gamma : \{\tau_1, \tau_2,, \tau_n\}$ )                                                                                                                                                                                                                                                                                                                                                      |

| 3  | BFD-P( $\Gamma : \{\tau_1, \tau_2,, \tau_n\}$ )                                                                                                                                                                                                                                                                                                                                                      |

| 4  | R-BATCH: Allocate the given task set $\Gamma$ to processors $P$ for handling $\rho$ processor                                                                                                                                                                                                                                                                                                        |

|    | failures                                                                                                                                                                                                                                                                                                                                                                                             |

| 5  | generateVirtualTask $(\Gamma : \{\tau_1,, \tau_n\}, \Pi : \{\Pi_1,, \Pi_n\}, P, \rho)$ 40                                                                                                                                                                                                                                                                                                            |

| 6  | FBFD( $\Omega : \{\omega_1, \omega_2,, \omega_n\}, \Pi : \{\Pi_1, \Pi_2,, \Pi_n\}, P)$ 60                                                                                                                                                                                                                                                                                                            |

| 7  | $R-FLOW(\Omega: \{\omega_1, \omega_2,, \omega_n\})                                                                                                                                                                                                                                                                                                                                                 $ |

| 8  | Rhythm-Max- $C(\Gamma)$                                                                                                                                                                                                                                                                                                                                                                              |

| 9  | Rhythmic-Acc- $\alpha(\Gamma, \alpha, n_{\alpha})$                                                                                                                                                                                                                                                                                                                                                   |

| 10 | Num-Preemptions $(T_1^*, \alpha, n_\alpha, W_i^k)$                                                                                                                                                                                                                                                                                                                                                   |

| 11 | Execution-Time $(n_{p,i}^a(W_i^k), C_1^*, \alpha, n_\alpha)$                                                                                                                                                                                                                                                                                                                                         |

| 12 | Stretch* $(	au)$                                                                                                                                                                                                                                                                                                                                                                                     |

| 13 | Response-Time $(\Gamma, i, \vec{\phi_i})$                                                                                                                                                                                                                                                                                                                                                            |

| 14 | $ED(\Gamma)$                                                                                                                                                                                                                                                                                                                                                                                         |

| 15 | System-Schedulability-Test- $(\Gamma, P, \Pi)$                                                                                                                                                                                                                                                                                                                                                       |

# **Chapter 1**

# Introduction

Advances in CPS (Cyber-Physical Systems) have enabled a variety of different applications such as drones, implantable medical devices, smart cars, distributed transportation systems, smart grids, and planetary robots, which are tightly coupled with the physical world. As CPS become part of everyday life, we will have many societal benefits ranging from autonomous driving preventing accidents to smart buildings saving energy to implantable medical devices changing the paradigm for patient treatment. A recent report from NIST (National Institute of Standards and Technology) predicted that the technical CPS innovations could be applicable to areas constituting up to \$82 trillion in economic activity by 2025.

The rise of CPS, however, poses new reliability and safety challenges. CPS sense the physical environment, process data in real-time, control actuators, and guarantee the timing of the whole execution chain for ensuring safety. Since CPS are tightly coupled with the physical world, anomalies such as hardware failures and timing errors may cause significant damage to life and/or property. Therefore, CPS need to satisfy strict timing constraints based on operating characteristics, making timing guarantees an essential requirement. System dependability is also of high importance in CPS applications due to the interactions with the physical environment. A typical example of such systems of an autonomous vehicle is depicted in Figure 1.1 [2].

Common practices addressing those anomalies tend to over-provision resources, replicating

Figure 1.1: During a road test of an autonomous vehicle research platform developed at CMU

hardware components and keeping CPU and network loads low. However, many CPS systems are targeted towards large-scale cost-sensitive markets that have stringent space and bill-of-material constraints that cannot afford overprovisioning. For example, the automotive industry has been trying to consolidate in-vehicle CPUs to reduce assembly and maintenance costs, as CPU- and network-hungry autonomous driving features hit the market. More specifically, a recent high-end vehicle has several active safety features such as adaptive cruise control, collision avoidance, lane departure warning, and parking assist. Such a vehicle may not have enough space or it may become too expensive to deploy traditional hardware redundancy for all CPS features to meet reliability requirements. Higher assembly costs and complexity coming from overprovisioning resources may not be desirable either. This trend is expected to continue as these features will be available even in mid-range cars in the near future. We tackle such challenges by devising new computational models reflecting the timing nature of CPS for system timeliness and providing a runtime framework that improves CPS dependability.

# 1.1 Thesis Statement

A dependable cyber-physical system is achievable using a software framework that enables system analyzability and predictability.

In this dissertation, we study the problem of enabling dependable CPS through a system-level software framework that manages CPS resources including processors, networks, and sensors. The framework analytically satisfies timing constraints and predictably operates systems with and without resource failures. To address these challenges, we develop an analysis engine that supports efficient task allocation for software replication and guarantees timeliness of different types of tasks that fall into one of four categories:

- Tasks with periodic arrivals: the proposed approach leverages the characteristics of software replicas and network traffic for efficient task and/or backup allocation.

- Tasks with continually varying periods: a new task model is proposed to analyze tasks with continually varying periods and workloads. We name this type of tasks *rhythmic tasks*.

- Tasks with parallel threads: task transformations are used to effectively schedule real-time fork-join tasks with global fixed-priority assignment.

- Tasks with self-suspensions: a new scheduling algorithm that assigns different priority per task segment is provided to deal with tasks that suspend themselves.

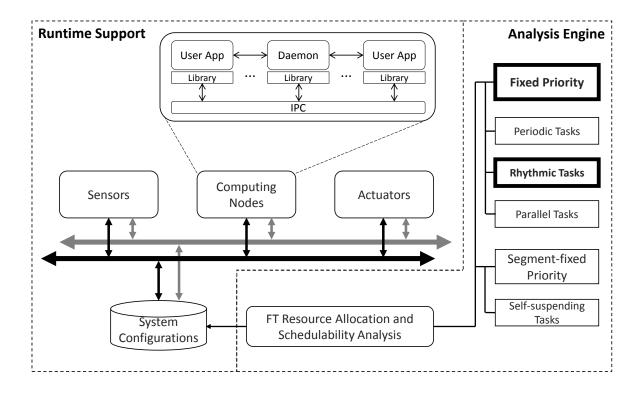

We design and prototype a runtime framework called SAFER (System-level Architecture for Failure Evasion in Real-time applications). It incorporates configurable software mechanisms and policies to tolerate failures of critical CPS resources while meeting task timing constraints. SAFER supports adaptive graceful degradation, effective use of different sensor modalities, and the fault-tolerance schemes of hot standby, cold standby, and re-execution. SAFER takes outputs of the analysis engine, and it then reliably and efficiently allocates tasks and their backups to CPU and sensor resources with network traffic considerations. It also fuses and (re)configures sensor data used by tasks to recover from system failures. The functionality of the proposed

Figure 1.2: Overview of the dissertation.

system is evaluated on a self-driving car using SAFER.

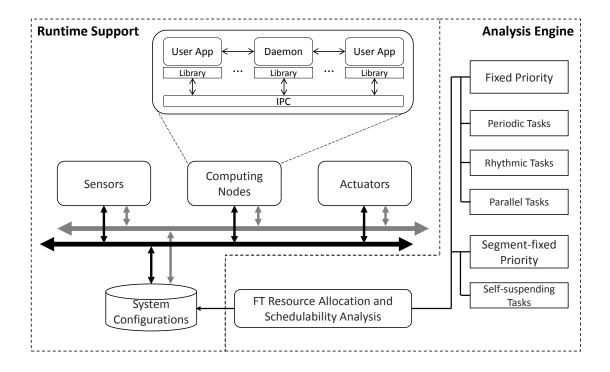

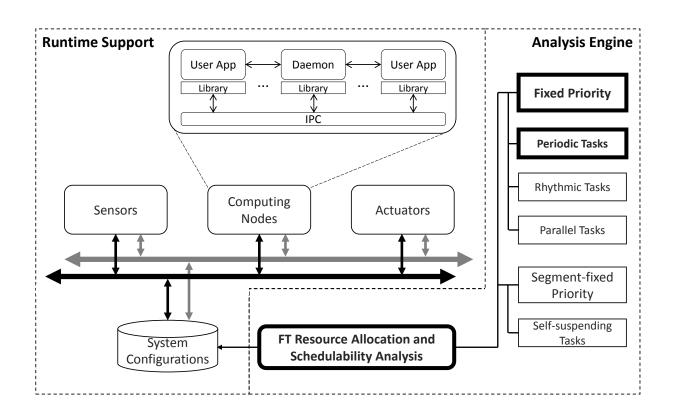

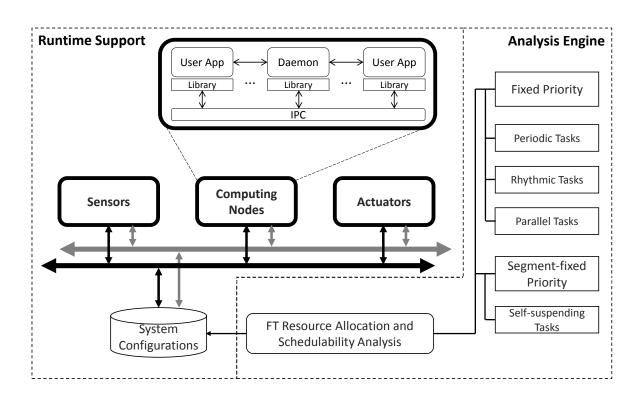

An overview of the proposed framework is depicted in Figure 1.2. The efficient resource allocation algorithms for software replication are described in Chapters 3 and 4. We study schedulability analyses for the different task models: periodic tasks in Chapter 5, rhythmic tasks in Chapter 6, parallel tasks in Chapter 7, and self-suspending tasks in Chapter 7. The results of the resource allocation and schedulability analysis methods are utilized in SAFER to telerate failures of critical CPS resources. The details of how SAFER works can be found in Chapter 8.

# **1.2** Scope of the Thesis

We assume that the system comprises p nodes communicating via messages over a network, where each node has a multi-core processor executing real-time tasks. Those tasks are scheduled

Figure 1.3: Design space of the dissertation.

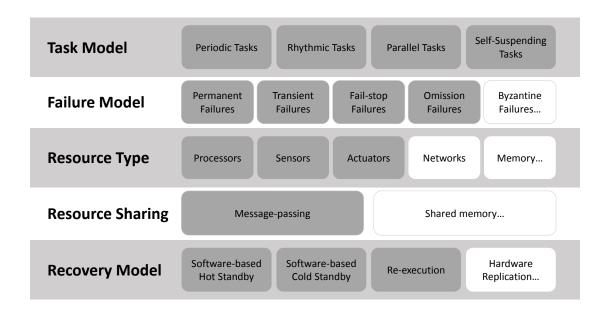

under the fixed-priority preemptive scheduling policy. Some tasks are independent<sup>1</sup>, and the other tasks use a Publish-Subscribe architecture to communicate with each other so that any task on the system can be configured to be recoverable. The network has an upper-bound on message delivery and is completely connected. In other words, a message is eventually delivered within a known delay bound, and the network is assumed not to partition<sup>2</sup>. The design space of this dissertation is depicted in Figure 1.3, where the dark gray rectangles represent the design assumptions considered in this dissertation.

#### 1.2.1 Failure Model

Tasks, processors, and sensors on the system are subject to fail-stop failures, where they fail by crashing and do not generate incorrect outputs. In other words, tasks running on a live pro-

<sup>&</sup>lt;sup>1</sup>Although tasks that share mutually exclusive resources are beyond the scope of this dissertation, conventional real-time synchronization protocols such as priority inheritance and priority ceiling protocol can be leveraged to incorporate such tasks.

<sup>&</sup>lt;sup>2</sup>Redundant links can make network partitioning highly unlikely. Such network redundancy is the topic of future study and is beyond the scope of this dissertation.

cessor/node are assumed to always emit correct outputs. Therefore, in order for the system to continue to correctly operate, recovery and restoration processes might be required. These failures may also happen concurrently. In this dissertation, no single-point-of-failure is allowed. We also expect failures to get recovered within a guaranteed time duration.

The system network may experience occasional omission failures, i.e., it may suffer from intermittent packet loss. This implies that the network does not fail completely. This again can be realized (say) by using redundant links.

#### 1.2.2 Task Model

Each task is assumed to generate an infinite series of independent jobs. Each job will have different characteristics based on the task model: periodic task, rhythmic task, parallel task, or self-suspending task. One common property is that all jobs have associated timing deadlines. Although we generally assume a hard real-time system, the effects of a deadline miss may vary. We assume that all jobs are preemptable with negligible cost. We also assume that there is negligible migration cost when a job is migrated from one core to another.

We model a real-time task as a sequence of jobs that are releasing every T units of time. Depending on whether T continually varies or not, we classify tasks into two different classes: periodic tasks or rhythmic tasks. When a task runs with multi-threads, we categorize it as a parallel task. When a task suspends itself and hence consists of multiple execution segments, we treat it as a self-suspending task. Although either a periodic task or a rhythmic task could be a parallel task and/or a self-suspending task, this dissertation assumes that (1) a self-suspending task does not have parallel threads, (2) a parallel task does not suspend itself, and (3) both a self-suspending task and a parallel task are periodic.

We aim to limit the fail-over time on each task to yield a reliable system. Depending on the fail-over time requirement, we classify each task into one of three classes: (1) *Hard Recovery Task*, which should be able to recover and complete within its original deadline, (2) *Soft Recovery*

*Task*, which has more relaxed fail-over time requirements, and (3) *Best-Effort Recovery Task*, whose recovery is optional depending on the amount of available resources.

## 1.2.3 Recovery Model

We use passive replication (primary-backup [3]), which has been mostly used for soft real-time systems. To support both hard and soft recovery tasks described above, we provide two different types of backups: *hot standby* and *cold standby*.

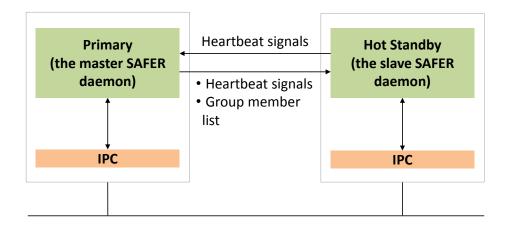

A hot standby runs concurrently with its primary on another processor. Depending on the reliability requirements, multiple hot standbys may coexist on different nodes. Only the primary emits its outputs. Its hot standbys simultaneously run on different nodes, receive the same input as the primary, but they do not generate any outputs. When a primary fails, one of the hot standbys is promoted to be the primary and starts generating outputs. Since it has been already running, only interface redirection from a null output device to the active channel needs to happen. This enables the use of hot standbys to recover hard recovery tasks<sup>3</sup>.

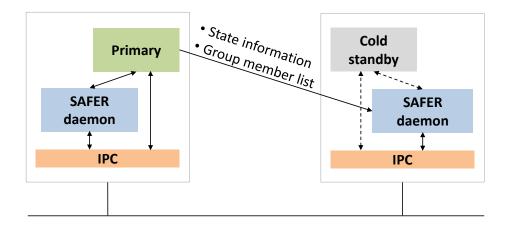

A cold standby is a dormant task which is triggered to run when a failure is detected. When its primary is running, its binary resides in the system memory, and it does not consume any CPU resources; however, state information from the primary task computations are periodically sent to its cold standby node(s). On failure of the primary or a specified number of hot standbys, the cold standby becomes active and starts from the last check-pointed status. The cold standbys can be used for recovering soft recovery tasks and best-effort recovery tasks.

# 1.3 Approach Overview

In this section, we describe our proposed approach. Various aspects of our work fall into one of three categories: (1) resource allocation for fault-tolerant computing, (2) schedulability analysis

<sup>&</sup>lt;sup>3</sup>A time synchronization service is important to support hot standbys.

for cyber-physical systems, and (3) runtime support for fault-tolerance features.

### 1.3.1 Resource Allocation for Fault-Tolerant Computing

Based on the task classification defined in Section 1.2.2, the recovery-time requirement imposed by hard recovery tasks does not allow much room for re-executing the failed jobs. For such tasks, a practical solution is to use multiple hot standbys that can take over the functionality under the presence of failures. Jobs of these hot standbys are released in parallel with those of the primary task, and they have the same deadline as the primary.

We assume a fail-stop failure model [4], where a working replica can assume control by detecting the lack of output from the primary. The replica can immediately provide the output since it would also have the output by the original deadline. In order to maximize task reliability, a process and its hot standbys should *not* be co-located on the same processor. We refer to this as the *placement constraint*. For this purpose, we develop a task allocation algorithm that optimizes for allocating tasks with hot standbys having such placement constraints.

Cold standbys reduce the resource over-provisioning costs further by getting activated only under failure conditions. The cold standbys use the task state information, which can be stored in shared memory or obtained during subsequent execution, and are used to recover soft recovery or best-effort recovery tasks. The benefit of a cold standby is that it leads to lesser consumption of resources under normal conditions. However, the recovery time bounds under cold standby will be much larger than those guaranteed by a hot standby. Using the system reliability requirement and the maximum number of processors that can fail during system operation, we can reduce the resource over-provisioning required for cold standbys of tasks allocated across different processors. Using this observation, we develop an algorithm that uses *virtual tasks* to consolidate and capture the resource requirements for cold standbys. The details can be found in Chapter 3.

We then consider a set of tasks that communicate each other to achieve the same goal in Chapter 4. For example, in Steer-by-Wire (SBW) systems [5], sensors measure information

about steering wheel movement, and computational components in microprocessors compute signals for controlling the wheels with the information from sensors. Actuators receive the control signals for the motors directly, and these signals are handled periodically for timely handling of user operations and reactions to the environment. In order to reflect this nature, we define an *application flow*, which is composed of periodically executing tasks generating information data and events regularly that flow through multiple tasks. An application flow also has an end-to-end delay constraint from input to output. From a dependability perspective, a single failure of a task within an application flow may affect all of its successors such that the overall application flow timing requirement is violated. By extending the two task allocation algorithms above, we also propose an algorithm designed for the application flow model. The algorithm captures communication among tasks and cluster them based on their network bandwidth needs.

## 1.3.2 Schedulability Analyses for Cyber-Physical Systems

To properly allocate CPS tasks to resources, it is important to understand the characteristics of CPS tasks beyond the conventional periodic task model. In this subsection, we will show three different task types: tasks with continually varying periods, tasks with parallel threads, and tasks with self-suspensions. We then propose how to predict their executions and analyze their properties for satisfying timing constraints on CPS.

#### **Tasks with Continually Varying Periods**

CPS require a high level of confidence in system timeliness as a critical task not meeting its timing deadline can lead to system failure. The dynamic nature of CPS is a dominant factor affecting the CPS timeliness. In automotive sub-systems, for example, the engine events activating the fuel injection task come from reference pulses generated by sensors at the engine crankshaft. Therefore, the periods of these tasks vary depending on the speed of the crankshaft. As an analog variable, speed is continuous and hence the period of the task can change both rapidly and con-

tinuously. The execution time of these tasks also vary and the worst-case execution time (WCET) arises when the engine speed increases to its maximum [6]. It is known in the automotive community that the engine control performance deteriorates with undersampling, i.e., tasks having a longer period than the required minimum period for a given speed.

Conventional task models such as periodic tasks or aperiodic tasks are not adequate to deal with such dynamic CPS behaviors as they do not incorporate physical attributes. In Chapter 5, therefore, we define a new task model called *Rhythmic Tasks* for characterizing and analyzing tasks that have continually varying periods depending on external physical events. We also propose response-time analyses for rhythmic tasks under three cases: constant engine speed, accelerating engine speed and decelerating engine speed. We provide guidelines well-suited for CPS applications to evaluate schedulable utilization levels for the rhythmic task model.

#### **Tasks with Parallel Threads**

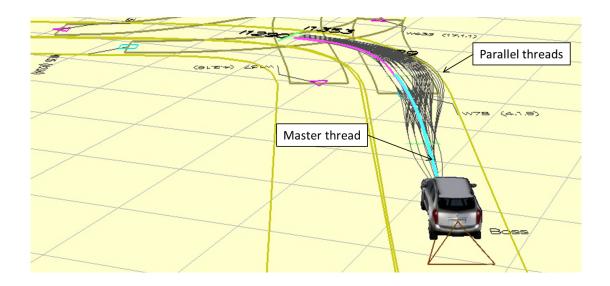

Many CPS tasks for perception (tracking) and actuation (planning) must run in real-time; however the CPU-hogging nature of these algorithms poses challenges in guaranteeing their time-liness. The timing challenge can be addressed by the fact that such algorithms are immensely parallelizable. For example, a planning algorithm of a self-driving car can benefit from parallelized tasks composed of numerous threads. The motion-planning algorithm calculates the best path for the vehicle to follow among a myriad of potential paths. Since the candidate paths are independent, this algorithm can be expedited by parallelizing the cost calculation for each path. The more paths the algorithm goes through, the better the driving quality will be. A perception subsystem of a self-driving car can also benefit from parallel tasks. In order for the vehicle to understand its surroundings, the perception subsystem should be able to process massive amounts of data from various types of sensors. The vehicle can classify and track the detected obstacles, whose number has a major impact on how many parallel threads are spawned by the perception subsystem.

In Chapter 6, we extend the fork-join real-time task model proposed in [1] so that an arbitrary number of threads can be scheduled, where the number of threads can vary depending on the physical attributes of the system. To efficiently schedule the proposed task model, we also propose a task transform to schedule the task model on a given number of processing cores. Then, we provide a resource augmentation bound for global Deadline Monotoic (DM) scheduling for fork-join real-time tasks. The proposed scheme is implemented on Linux/RK [7] and ported to the self-driving car Boss [8]. We evaluate our proposed scheme on Boss by showing its driving quality in terms of curvature and velocity profiles of the vehicle with an enhanced motion-planning algorithm [9].

#### **Tasks with Self-Suspensions**

An increasing number of special-purpose processors in CPS are added to improve the efficiency of frequently used operations. Unfortunately, the use of such special-purpose processors (a.k.a. hardware accelerators) may introduce suspension delays that must be taken into account in schedulability analyses when a task waits for a shared resource and interacts with an I/O device or communication interface. Offloading complex computations to hardware accelerators such as Digital Signal Processors (DSPs) or Graphics Processing Units (GPUs) can cause suspension delays as well, hence reducing the benefits of using such hardware accelerators.

Although many conventional real-time theories [10] have incorporated the delays in the worst-case execution/response time of a task that suspends itself, the analysis results lead to have significant pessimism. A pessimistic analysis is not desirable in a compute-intensive system such as the self-driving car depicted in Figure 1.1. Such systems run computationally-demanding algorithms ranging from perception [11] to planning [9, 12] on GPUs in real-time. In this case, if we use traditional schedulability analysis, the potential utilization improvement due to the use of GPUs is eliminated by the pessimism in the CPU scheduling.

In Chapter 7, to improve the schedulability of a taskset with tasks with self-suspensions,

we propose the segment-fixed priority scheduling that decomposes self-suspending tasks into multiple segments assigning them different priorities if needed. We use phase enforcement to prevent jitters [13, 14], and we develop an exact schedulability analysis.

## **1.3.3** Runtime Support for Fault-tolerance Features

To support the proposed approach in real-time, it is important to build a robust functional architecture for CPS that allows to perform the repeating sequence of perception, computation and control in the presence of possible system failures. Most importantly, no single point of failure is permitted. In other words, a task/processor/sensor failure should not lead to a system failure. Secondly, failure recovery within a guaranteed duration should be achieved. Since CPS are usually tightly connected to the physical world, failure recovery without predictable timing behavior could yield unpredictable results in the physical world. Apart from these two goals, predictive fault discovery and notification, resource isolation, ease of use of abstraction, ease of application development, and sensor/actuator control are other factors considered.

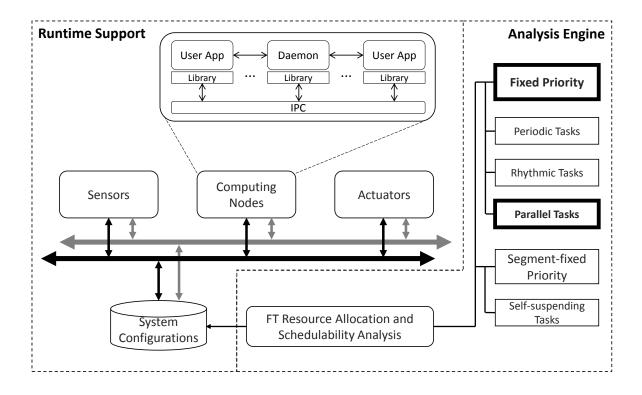

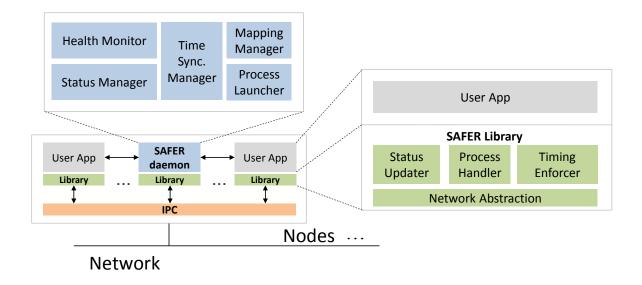

The goals are achieved using a layer called SAFER (System-level Architecture for Failure Evasion in Real-time applications) that incorporates configurable task-level fault-tolerance features to tolerate fail-stop processor, task, and sensor failures for CPS in a timely manner. To detect failures, SAFER monitors the health status and state information of each task and broadcasts the information. When a failure is detected using either time-based failure detection or event-based failure detection, SAFER reconfigures the system to retain the functionality of the whole system using task-level fault-tolerance techniques. More specifically, SAFER provides the following features: (a) Each task can have zero, one or more backup(s), (b) Each backup can be either a hot standby or a cold standby, (c) Failure detection and recovery latencies can be guaranteed, (d) A primary and each of its backup(s) are always allocated to run on independent processor boards to avoid common failure modes, (e) State transfer is managed for seamless recovery from failures, (f) In case of a sensor failure, tasks using the failed sensor will be notified to

apply appropriate sensor recovery schemes. The detailed information is discussed in Chapter 8.

Our fault-tolerant task allocation schemes proposed in 1.3.1 are integrated with SAFER through a model-based development tool, SysWeaver, developed at CMU [15]. Our analysis engine based on the formal timing analysis is added to SysWeaver, and we add a simulation capability of SAFER features under the presence of failures. Specifically, by injecting failures, we are able to simulate the timing behavior of the system and verify its operation with different models and system parameters.

#### **Sensor/Actuator Failure Recovery**

The effective use of *different sensor/actuator modalities* in CPS is essential. CPS have various sensor modalities providing 360-degree coverage. Many analog sensors are prone to intermittent faults, so using different sensor modalities is better than duplicating the same type of sensors because different types of sensors typically respond to the same environmental condition in diverse ways. Suppose an autonomous vehicle is equipped with radars for blind spot detection. If a backward-looking radar does not work properly, a vision algorithm detecting obstacles from images obtained through a backward-looking camera can be used. A similar approach is also applicable to actuators. An autonomous vehicle may use a low-grade sensor with complex data-processing algorithms after a high-grade sensor with simple algorithms fails, until the vehicle can safely stop.

# **Chapter 2**

# Literature Review

This chapter describes existing work related to this dissertation. Our work can fall into one of three categories: (1) resource allocation for fault-tolerant computing, (2) schedulability analysis for CPS, and (3) runtime support for fault-tolerance features. We will discuss the related work in each domain and explain how our work differs from the literature. Sensor failure recovery will also be discussed as a part of the runtime support for fault-tolerance features.

# 2.1 Resource Allocation for Fault-tolerant Computing

Real-time scheduling algorithms for uniprocessors have been studied extensively for guaranteeing timeliness. For example, Liu and Layland proposed a static real-time scheduling algorithm, RMS (Rate Monotonic Scheduling), which prioritizes periodic tasks according to their rates since [16]. Emerging demands on computational capability have driven various multiprocessor scheduling algorithms for supporting similar properties on multiprocessor environments. Multiprocessor scheduling is therefore a well-studied problem in real-time systems literature [17, 18, 19, 20]. Existing solutions are broadly classified into global [21] scheduling with unrestricted task migration, partitioned [22] scheduling with strictly no task migration, and hybrid [23, 24] with restricted task migration. Although each of these approaches has its own

benefits, in this work we are primarily interested in the partitioned approach on multiprocessor environments due to the high cost associated with migrating tasks across processors. We allow on-demand activation to deal with failed processors, where we explicitly capture the associated timing cost of restoring the task state on a different processor.

A wealth of literature exists on the topic of fault-tolerant computing [25, 26, 27]. active and passive replication are standard mechanisms to improve system reliability. These replication-based approaches affect on research [28, 29, 30] in real-time domain. The key distinction made in real-time contexts is systems with strict bounds on system recovery time. A successful recovery is one where the system not only resumes its normal operation but does so within a pre-specified recovery time. These recovery time requirements are typically derived from the physical environment in which the system operates. For example, an autonomous vehicle cannot stall significantly in the middle of a highway during system recovery.

Fault-tolerant scheduling in multiprocessor systems has also received attention in [31]. In [32], the FFD (First-Fit Decreasing) is augmented with placement constraints to allocate replicated tasks. Most closely related to our work is [33], where the authors proposed a BFD (Best-Fit Decreasing) with placement constraints as a practical solution, which we call BFD-P (BFD with Placement constraint). Our work differs from theirs in two ways: (i) we propose a new bin-packing heuristic using a cluster of replicated tasks which performs better than BFD-P, and (ii) we deal with the allocation of cold standbys that are passive entities, which can be potentially consolidated across processors.

#### 2.2 Schedulability Analysis for Cyber-Physical Systems

#### 2.2.1 Tasks with Continually Varying Periods

Extensions to the conventional periodic task model [16] such as constrained-deadline sporadic tasks [34] and arbitrary deadline tasks [35] have been explored in the past. Although these task

models represent tasks having different relationships between their periods and deadlines, the task parameters themselves are static and/or worst-case in nature. In this dissertation, we explore a model where certain tasks have dynamically changing parameters, which are determined by external or *physical* system attributes such as the engine speed in a PCM.

The importance of task periods on the quality of engine control has been demonstrated in [6]. As the engine speed varies, the system must continuously change the engine control task periods. Given vehicle dynamics [36], maintaining a close relationship between the control task and the engine speed is key for achieving high efficiency. Worst-case execution time analysis of engine tasks was carried out in [37]. At higher speeds, system designers tend to adaptively reduce the task computation times to counteract the shrinking task periods, and try to maintain approximately constant system utilization. We develop the rhythmic task model in detail to represent such types of engine control tasks and study the resulting properties.

Some task models with dynamically changing parameters have been studied in the past. For instance, the elastic task model [38] treats tasks as springs with given elastic co-efficients. More recently, the gravitational task model [39] was introduced by representing tasks as bobs hanging on a pendulum with the objective of preferably executing at a target set point. Although these task models have dynamically changing parameters, their usage is often motivated by the need to provide *quality of service* or to maximize *system utility*. Also, due to the fact that the elastic task model uses dynamic-priority scheduling and the gravitational task model is based on non-preemptive jobs, the previous work is not appropriate for fixed-priority preemptive scheduling. We consider a model where the changes in task parameters are resulting from the physical nature of the system, and changes in the operating environment drive task requirements.

From a schedulability analysis perspective, the analyses of minimum task periods and maximum worst-case execution time are well-known results for the periodic task model [40, 41]. The acyclic task model [42] uses a task model where a task comprises successive invocations but with no constraints between the periods of successive invocations. The utilization bound

for acyclic tasks was also derived. Our rhythmic task model is more restricted, is motivated by cyber-physical requirements and should yield better utilization. We provide some bounds and guidelines to find schedulable regions for the generic rhythmic task model. These results are also helpful to understand the utilization bounds when only the task periods are given. We study the properties of acceleration and deceleration, which correspond to the maximum rate at which task periods can be decreased and increased respectively. In this regard, the closest work to ours is that of the mode change protocol [43]. However, we are interested in understanding the effect of a series of *continuous* mode changes on the schedulability of lower-priority tasks, as opposed to one single independent system-level mode change.

Tasks with relationships between task periods and physical attributes can be also found in other cyber-physical subsystems besides the engine control task. For example, in the context of autonomous driving [8], the sensor processing tasks need to execute at a higher rate when the vehicle is moving at a higher speed, since the vehicle would cover a longer distance in a shorter time. Another good example is building energy management [44] where fine-grained management depending on varying environmental parameters will save more energy. Also, most CPS with control algorithms can likely obtain benefits from the rhythmic task model because the quality of control is affected significantly by sampling rates.

#### 2.2.2 Tasks with Parallel Threads

Since Dhall and Liu [17] showed that RMS and Earliest Deadline First (EDF) scheduling could utilize only one processor regardless of how many processors a system had, there has been extensive research on global real-time scheduling [20, 45, 46, 47, 48, 49, 50, 51], where a comprehensive survey can be found in [51]. It is well-known that the anomaly of global scheduling happens when a set of tasks has two types of tasks: tasks with a low ratio of the worst-case execution time to relative deadline and tasks with a high ratio of the worst-case execution time to relative deadline. Many algorithms have been invented to avoid such cases, and corresponding schedu-

lability tests have been proposed. Using our proposed task transformation, any existing global scheduling algorithm can be applied to schedule parallel real-time tasks. In this dissertation, we have used the schedulability bounds for global DM proposed in [46, 50].

There has not been much research on scheduling parallel real-time tasks [1, 52, 53, 54]. Lakshmanan et al. [1] proposed a fork-join real-time task model composed of alternating sequential and parallel segments. They also provided the analysis and resource augmentation bound for the partitioned DM scheduling [22] of parallel real-time tasks using the task *stretch* transformation. The proposed multiprocessor scheduling algorithm is shown to have a resource augmentation bound of 3.42, which implies that any task set that is feasible on m unit-speed processors can be scheduled by the proposed algorithm on m processors that are 3.42 times faster. Our work is a generalization of this model and provides a resource augmentation bound when global scheduling is used.

Saifullah et al. [53] also proposed a parallel synchronization model that is also generalized from the fork-join task model in [1] so that a task can have an arbitrary number of threads per segment. Based on the proposed model, a task decomposition method is used to decompose each parallel task into a set of sequential tasks. The task decomposition achieves a resource augmentation bound of 4 and 5 when the decomposed tasks are scheduled using global EDF and partitioned DM scheduling, respectively. Our work focuses more on global fixed-priority scheduling and shows the evaluation results measured from a real-world implementation.

More recently, Nelissen et al. [54] presented both offline and online algorithms to minimize the number of cores to be used to schedule multi-threaded tasks using a similar model to the model proposed in [53]. By using scheduling algorithms which can guarantee the schedulability of the given tasks as long as the sum of densities of all the given tasks is less than or equal to the number of processing cores, they obtained a resource augmentation bound of 2. Our perspective is different from theirs in a sense that we schedule a set of tasks under a given hardware constraint (the number of processing cores) rather than finding hardware for the given tasks. We also use

global DM scheduling algorithm more commonly used in practice and show the evaluation results obtained from a working system.

Apart from work using the *thread* model mentioned above, there has also been research based on *gang scheduling*, where all parallel components of the same task should arrive and complete at the same time. Gang EDF [52] was proposed to address gang scheduling in the real-time context. Our work is different from this in two ways: (1) our model allows the parallel segments to be preempted during the parallel execution, and (2) a different number of parallel threads can be used.

#### 2.2.3 Tasks with Self-Suspensions

Previous work related to task-fixed priority scheduling with suspension includes [14, 55, 56, 57, 58]. Ridouard, et al. [56, 58] proved that the problem of scheduling real-time tasks with selfsuspension is NP-Hard in the strong sense. In [55] the authors present a comparison between two multi-processor priority inheritance protocol (MPCP and MSRP), where tasks can suspend waiting for a remote lock. In this work the authors highlight the different approaches to deal with this suspension. In MPCP, a task waiting for a global lock is allowed to suspend, allowing lower-priority tasks to run, and a period-enforcement is used to avoid jitter [13]. In MSRP, on the other hand, a busy wait is used and no lower-priority tasks are allowed to run. In our work, we also use a period enforcement mechanism to avoid jitter in the suspension, but each segment (e.g. before and after the suspension) is given a different priority according to different schemes of segment deadline assignments. In [57] the authors analyze the execution of tasks with segments running in a local processors and segments running on remote co-processors that can be seen as a suspension in the local processor. In this case the authors bound the suspension with a minimum and maximum and provide a recurrence equation to find the worst-case interference that a task can suffer from higher-priority ones with a number of these segments. In contrast, we provide a schedulability bound for taskset with only the highest-priority task with suspension

while using a generalized task model with suspensions where each segment is assigned its own priority. The period enforcement of offsets, which [57] do not use, allows us to provide improved schedulability.

In [14] the authors analyze the scheduling of fixed-priority tasksets with self-suspension. Specifically, the authors characterize the critical instant of sporadic self-suspending task under the influence of non-suspending tasks and developed a response time test. In addition, they provide two execution control policies that transform the interference of high-priority suspending tasks into that similar to a non-suspending ones to be able to use their response-time test with these tasks. In contrast, we developed a schedulability bound for a taskset where the higher-priority is a self-suspending task and developed a response-time test for suspending tasks where each segment can be assigned different priorities and have release enforcement.

The schedulability of self-suspending tasks has also been studied for soft-real-time guarantees. In [59] Liu and Anderson presented a technique to analyze the schedulability of soft real-time tasks with suspension with bounded deadline tardiness requirements scheduled under global EDF in multiprocessors. In [60] the authors studied the problem of bounding the tardiness of soft-real-time tasks when using GPU as coprocessors, and model them with two techniques, as a shared resource and as a container. For the shared resource approach they used locking protocols to frame the analysis of GPU execution either as suspension or busy time depending on the locking protocol. For the container approach they use a hierarchical bandwidth reservation (a container) approach grouping all the tasks that use the GPU in a separate container to provide a FIFO scheduling discipline and considering their suspension as busy time.

In [61] the author presents a schedulability analysis for tasks with offsets. These offsets are used to synchronize the release of groups of tasks that synchronized within the group (known as transactions). In [62] the authors extend this work to allow offsets and deadlines to go beyond periods improving the schedulable utilization. The efficiency of the response time analysis in this model is then further improved in [63]. These papers have some similarities with the use of

offsets between segments in tasks in our model. However, in our work we start with suspension intervals that separate task segments from where we derive intermediate deadlines that in turn allows us to assign per-segment fixed priorities.

In [64] the authors developed another schedulability analysis for tasks with offsets. However, in this case the analysis assumes EDF scheduling and the results cannot be applicable to fixed-priority tasks.

#### 2.3 Runtime Support for Fault-tolerance Features

Fault-tolerant distributed embedded systems have been extensively studied in the literature. The ISIS system [65] is a well-known software system that supports fault-tolerance services. FT-CORBA (Fault-Tolerant CORBA) [27, 66, 67] has been used in various applications to design and implement a fault-tolerant distributed system, and practical experiences on two different FT-CORBA infrastructures are described in [68]. CORBA-based fault-tolerant middleware services are also surveyed in [69]. There are other replication-based recovery services such as Arjuna [70], REL [71] and IFLOW [72], which are not based on CORBA. One clear distinction between the existing work and SAFER is that SAFER provides the framework to support timely failure recovery in a generic distributed embedded system.

There have also been efforts on building real-time fault-tolerant systems. MEAD [73] provides a proactive fail-over framework using a failure prediction method to overcome the unpredictable nature of failure occurrences and support somewhat predictable timing behavior. FLARe [74] is designed and implemented to support fault-tolerance for distributed soft real-time applications. SAFER differs from the above-mention systems in that SAFER is built on a publish-subscribe model rather than a client-server model. In addition, SAFER provides predictable timing characteristics of failure detection and recovery when real-time systems become SAFER-enabled. SAFER also provides a flexible failure detection and recovery infrastructure. SAFER detects failures using heartbeat signals (time-based) as well as OS (Operating Systems) signals

(event-driven). A primary can use hot standby and/or cold standby as a backup.

#### 2.3.1 Sensor/Actuator Failure Recovery

There have been extensive efforts on detecting sensor failures and recovering from those failures. In general, there are two types of sensor failures: *hard* and *soft* failures [75]<sup>1</sup>. When a failure is hard, the failed sensor is stuck at a certain condition so that it outputs only one value including no output and the following measured data become invalid. When a sensor experiences a soft failure, its output becomes less reliable. In other words, the quality of the measurement is degraded, and the data should be cautiously used. To detect such failures, many different approaches have been proposed. In [75, 79], the authors used a bank of Kalman filters for a multiple model adaptive estimator to detect and identify sensor failures. The authors of [80, 81] leveraged a Bayesian belief network model to achieve these goals. Other methods such as fuzzy logic [82], the Nadaraya Watson statistical estimator [83], and subspace model identification [84] were also used. Although our scheme can be used on top of those methods, we choose to use a Kalman filter-based method in this dissertation due to its speed and accuracy on our evaluation platform.

Recovering from sensor failures has been extensively studied in the literature ranging from building a fault-tolerant sensor [85] to making data fusion reliable [78]. In [85], Marzullo proposed a process control program that can tolerate sensor failures. He used replication and voting to mask failures and studied hierarchies of failure models to average sensor values in a fault-tolerant way. Our work is more general in a sense that we do not necessarily use the same type of sensors. Our focus is also more on leveraging different modalities of sensors to improve the system dependability. In [86], the authors proposed an algorithm that used one type of sensors as backups of different types of sensors. They formulated it as a multi-modal sensor allocation problem and provided schemes that could deal with binary and multi-level sensors. In [78], the

<sup>&</sup>lt;sup>1</sup>There are other papers [76, 77, 78] that classify sensor failures into more detailed categories, but most of them fall into these two categories.

authors proposed a fault-tolerant data fusion technique for the same type of sensors to minimize the mean square error of sensor measurements. Although both papers use multi-sensor data fusion technique [87] to achieve their goals and our work is similar in that sense, our approach takes into account both the same and different types of sensors. There has also been research on building a reliable distributed control system [88, 89, 90], which can be applicable to actuator failure recovery.

# **Chapter 3**

# **Resource Allocation for Fault-Tolerant Computing**

Figure 3.1: Resource allocation for fault-tolerant computing in the dissertation overview.

Cyber-Physical Systems (CPS) are growing in terms of both scale and complexity. An emphasis on scalability, extensibility, and flexibility has led to complex electrical/electronic multiprocessor architectures. In a variety of applications such as industrial control, avionics, and automotive systems, such complexity can lead to unavoidable failures in both hardware and software. Furthermore, developers/designers may not be able to predict when and where faults can happen. System-level dependability is therefore a key concern in evolving CPS. An emerging application of such systems is autonomous driving. For example, the Urban Challenge winning autonomous vehicle, Boss [8], used several embedded processors and ten Intel Core2Duo processors due to high computing power requirements. However, CMOS scaling for performance improvements has decreased the reliability of processors [91]. This could potentially have catastrophic effects if not taken into account, for example, unmanned vehicles can lose driving capability due to processor failures.

Two different notions, *fault-tolerant* and *fail-safe*, are applicable for characterizing the system behavior under failures. A fault-tolerant system requires that a system/user does not recognize a failure occurrence during the operation in terms of functionalities. Several conventional replication methods such as hardware redundancy, software redundancy, and re-execution can be used to build fault-tolerant systems. A fail-safe system requires a different type of fault handling. It allows failures, but must not generate an unsafe system state by overriding a proper procedure when a failure occurs. Developing a fail-safe system requires us to consider specific failure scenarios. As described earlier, enumerating all possible failure scenarios is not an easy task for complex systems, therefore, we focus on achieving the more robust property of fault tolerance.