#### Design Techniques for Frequency Reconfigurability in Multi-Standard RF Transceivers

Submitted in partial fulfillment of the requirements for

the degree of

**Doctor of Philosophy**

In

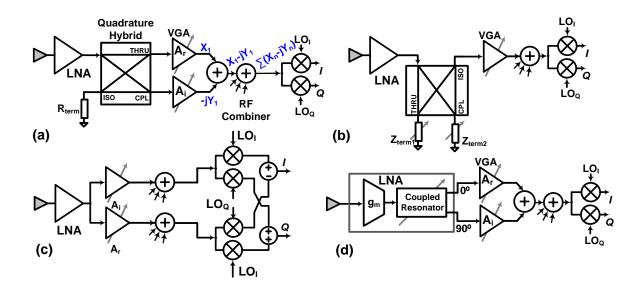

**Electrical and Computer Engineering**

Rahul Singh

B.Tech., Electronics Engineering, Indian Institute of Technology (BHU), Varanasi M.Sc., Electrical Engineering, Seoul National University, Seoul

Carnegie Mellon University Pittsburgh, PA Copyright © Rahul Singh, 2018

All rights reserved

## Acknowledgement

I thank Prof. Jeyanandh Paramesh for being my research advisor, and a vocal and when required, a silent supporter throughout my PhD journey. I consider myself lucky to have been given a chance to be his student even as his intellect far surpassed mine. If I demonstrate even a fraction of his commitment to scientific rigor, his earnest enthusiasm for all aspects of circuit design, and his honed talent for concise writing in the years to come, I would have repaid his investment of time in my development.

I thank Prof. L. Richard Carley for serving on my thesis and PhD Qualifiers committee, and for giving me a chance to serve as a teaching assistant to the 18-723 RFIC course twice. Prof. Carley is a fountain of knowledge and experience, and I benefited greatly from his lectures. I thank Prof. James A. Bain for being on my thesis committee, and for the various lessons I have learned through our interactions in the RF-FPGA program, through my serving as a teaching assistant for 18-220, and merely by being in his presence and see him interact with his students. His cheerful salutations on running into me in a random hallway and his generous words of encouragement have brightened many of my tougher days. With a deep sense of gratitude, I also thank Prof. Lawrence Larson, for serving on my thesis committee despite his very busy schedule. I sincerely thank him for his time, advice and feedback. I also thank Prof. Tamal Mukherjee for patiently working with me to solve the big and small problems of the RF Probe Station in REH 324 that needed attention to ensure the lab functioned smoothly.

My PhD journey could not have started without the mentorship of Ahmad Khairi. I had to pick up many skills very quickly, and Ahmad selflessly spent hours of his time teaching me the basics of everything – from laying out my first differential pair, to soldering a QFN package onto a PCB, and to making sensitive RF measurements in the lab. I am deeply indebted to him, and will never be able to repay his generosity in helping a struggling new student like me. I will also look back fondly at my association with all the fellow graduate students with whom I worked closely – Susnata, Xiaoliang, Ahmed, Mazen, Hoda, Shih-Chang, Mohsen, Greg, Nabil, Min, Jinglin and Shaolong. I thank them for their friendship, for the laughs, for their help and support, and the opportunities they provided to learn from them. I worked closely with Susnata the last three years, and I am certain that with his unique combination of intelligence, hard work, humility, and

sincerity, he will scale great heights in the future and make all of us very proud. I also thank Dan Worpell, a fellow TA of 18220: I could not have managed the labs of 18220 (with 100 students, no less!) and written my thesis in the same semester without his help.

I also thank Judy Bandola who expertly shielded me from a lot of administrative work. I am thankful to Nathan Snizaski, ECE's PhD Program Advisor for helping me navigate the maze of program requirements, and confusing OPT stipulations.

I will forever be grateful to Abhishek Jhajoo, Vamsi Paidi, and Raja Pullela for the opportunity to intern with Maxlinear Inc, Carlsbad. I was in constant awe of my mentor at Maxlinear, Masoud Koochakzadeh, for his excellent technical and managerial skills. Despite several looming deadlines and choc-a-block meetings, he found time to sit and discuss my work every day, and his encouraging smile always motivated me to try harder. I also worked closely with Pawan Agarwal, Yifei Li and Jeffrey Lee and I thank them for their mentorship. I thank Greg and Nabil for visiting me and showing me a good time, while I was in Carlsbad.

Last but not the least, I thank my small family, and my close friends. I am known only to a few people, and I inhabit a small world, but what a world it is! I have cashed out all my luck in this life to have such beautiful people around me, who mean the world to me, and who always inspire me to be a better version of myself every time I falter.

Finally, I acknowledge the support of DARPA and NSF for supporting this research. This work was supported in part by the DARPA RF-FPGA Program under Contract HR0011-12-C-0095, and in part by National Science Foundation under Grants EECS-1343324, CCF-1314876 and ECCS-13099.

#### Abstract

Compared to current single-standard radio solutions, multi-standard radio transceivers enable higher integration, backward compatibility and save power, area and cost. The primary bottleneck in their realization is the development of high-performance frequency-reconfigurable RF circuits. To that end, this research introduces several CMOS-integrated, transformer-based reconfigurable circuit techniques whose effectiveness is validated through measurements of designed transceiver front-end low-noise (LNA) and power amplifier (PA) prototypes.

In the first part, the use of high figure-of-merit phase-change (PC) based RF switches in the reconfiguration of CMOS LNAs in the receiver front-end is proposed. The first reported demonstration of an integrated, PC-switch based, dual-band (3/5 GHz) reconfigurable CMOS LNA with transformer source degeneration and designed in a 0.13 µm process is presented.

In the second part, a frequency-reconfigurable CMOS transformer combiner is introduced that can be reconfigured to have similar efficiencies at widely separated frequency bands. A 65-nm CMOS triple-band (2.5/3/3.5 GHz) PA employing the reconfigurable combiner was designed.

In the final part of this work, the use of transformer coupled-resonators in mm-wave LNA designs for 28 GHz bands was investigated. To cover contiguous and/or widely-separated narrowband channels of the emerging 5G standards, a 65-nm CMOS 24.9-32.7 GHz wideband multi-mode LNA using one-port transformer coupled-resonators was designed. Finally, a 25.1-27.6 GHz tunable-narrowband digitally-calibrated merged LNA-vector modulator design employing transformer coupled-resonators is presented that proposes a compact, differential quadrature generation scheme for phased-array architectures.

## **Table of Contents**

| A | Acknowledgementiii |                                                       |    |

|---|--------------------|-------------------------------------------------------|----|

| A | bstract            |                                                       | V  |

| 1 | Introdu            | action                                                | 1  |

|   | 1.1 Mo             | otivation and overview                                | 1  |

|   | 1.2 The            | esis Contributions and Organization                   | 5  |

| 2 | Freque             | ency Reconfiguration of RF Circuits Using PC Switches | 8  |

|   | 2.1 Int            | roduction                                             | 8  |

|   | 2.2 For            | ur Terminal PC Switches                               | 11 |

|   | 2.2.1              | MOS vs PC Switch                                      | 11 |

|   | 2.2.2              | PC Switch Design.                                     | 14 |

|   | 2.2.3              | PC Switch Characterization                            | 18 |

|   | 2.3 Du             | al-band LNA Design                                    | 20 |

|   | 2.3.1              | Dual-Band Simultaneous Noise and Input Match          | 21 |

|   | 2.3.2              | Narrowband Matching with Coupled Source Inductors     | 27 |

|   | 2.3.3              | Design Details                                        | 32 |

|   | 2.4 Me             | easurement Results                                    | 34 |

|   | 2.4.1              | PC Wafer Fabrication and Integration with CMOS        | 34 |

|   | 2.4.2              | Measurement Setup                                     | 36 |

|   | 2.4.3              | Characterization of Stand-alone Passive Structures    | 38 |

|   | 2.4.4              | Gain and NF Characterization of B1 and Baseline LNAs  | 39 |

|   | 2.4.5              | Characterization of B2 CMOS-PC LNAs                   | 43 |

| 2.4.6        | Input Matching                                             | 45             |

|--------------|------------------------------------------------------------|----------------|

| 2.4.7        | Cyclability                                                | 47             |

| 2.5 Ir       | ntegrated CMOS-PC LNA Summary                              | 50             |

| 3 A Tri      | iple-Band (2.5/3/3.5 GHz) Power Amplifier with a Frequency | Reconfigurable |

| Power Com    | biner                                                      | 52             |

| 3.1 Ir       | ntroduction                                                | 52             |

| 3.2 P        | ower Combiner Efficiency                                   | 55             |

| 3.3 O        | Optimum Combiner Design                                    | 58             |

| 3.4 P        | roposed Reconfigurable Transformer Combiner                | 61             |

| 3.5 C        | Combiner Switched Capacitor                                | 66             |

| 3.6 T        | riple-band Power Amplifier                                 | 71             |

| 3.6.1        | Doherty PA Basics                                          | 71             |

| 3.6.2        | Load Modulation in Power Combining PA                      | 73             |

| 3.6.3        | 4-way Power Combining PA                                   | 74             |

| 3.6.4        | CW Measurement Results                                     | 76             |

| 3.6.5        | Post-Measurement Analysis                                  | 79             |

| 3.7 S        | ummary                                                     | 88             |

| 4 A 28       | GHz Wideband Receiver Design Using One-Port Transf         | ormer-Coupled  |

| Resonators . |                                                            | 90             |

| 4.1 Ir       | ntroduction                                                | 90             |

| 4.2 T        | ransformer Coupled-Resonator Wideband Loads                | 92             |

| 4.2.1        | One-port vs Two-port Configuration                         | 92             |

| 4.2.2       | Reduction of Complex Zero Peaking                        | 98    |

|-------------|----------------------------------------------------------|-------|

| 4.2.3       | (k,ξ) Design Space                                       | 103   |

| 4.2.4       | Design Example                                           | 104   |

| 4.2.5       | Design Tunability                                        | 105   |

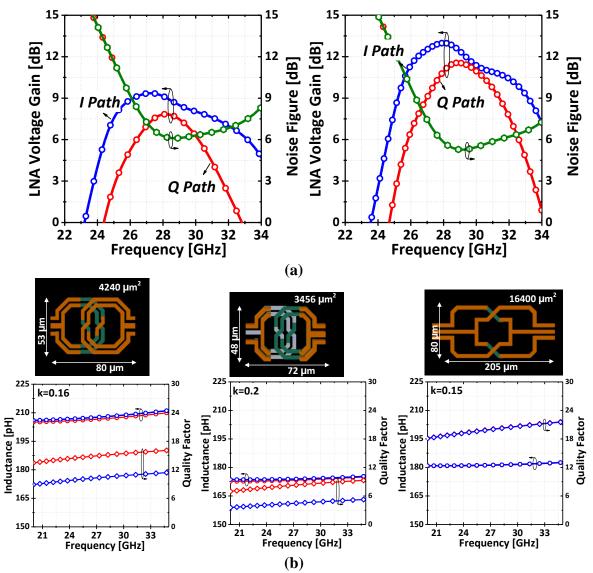

| 4.2.6       | Transformer Layout                                       | 107   |

| 4.3 W       | ideband Receiver Design                                  | 108   |

| 4.3.1       | Low-Noise Amplifier                                      | 109   |

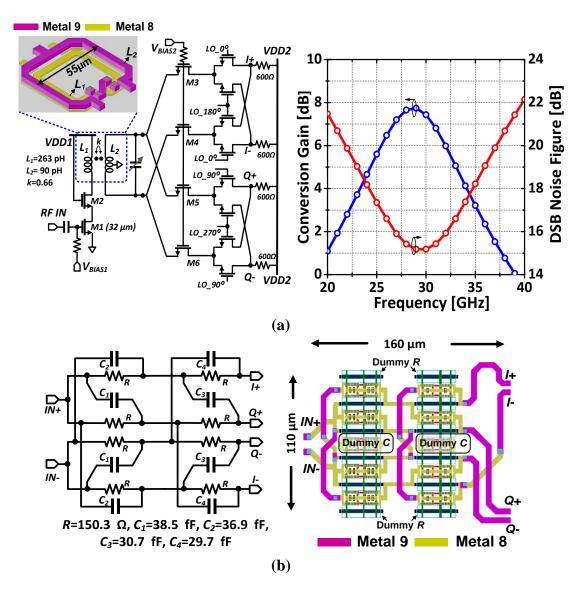

| 4.3.2       | RF Mixer and I/Q LO Generation                           | 111   |

| 4.4 M       | easurement Results                                       | 114   |

| 4.5 Su      | ımmary                                                   | 118   |

| 5 A 25.     | 1-27.6 GHz Frequency-Tunable Merged LNA Vector Modulator | Using |

| Transformer | -Coupled Resonators                                      | 120   |

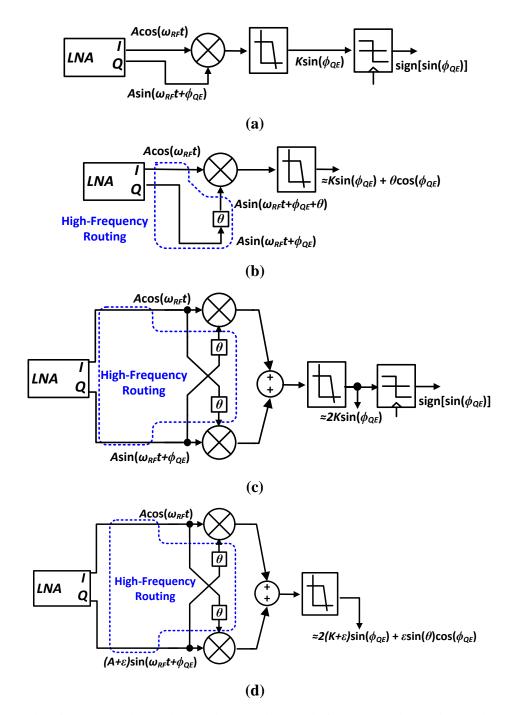

| 5.1 In      | troduction                                               | 120   |

| 5.2 W       | ideband vs. Narrowband Vector Modulator                  | 123   |

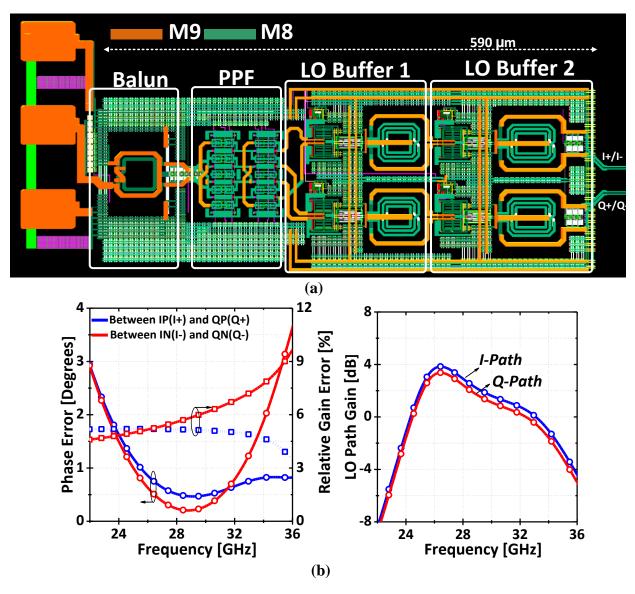

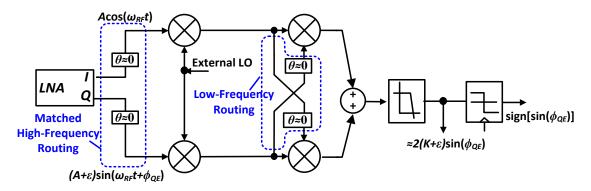

| 5.3 Co      | oupled-Resonator Quadrature Generation                   | 127   |

| 5.4 Di      | igitally-Calibrated Merged LNA Vector Modulator          | 130   |

| 5.4.1       | Merged LNA-VM                                            | 131   |

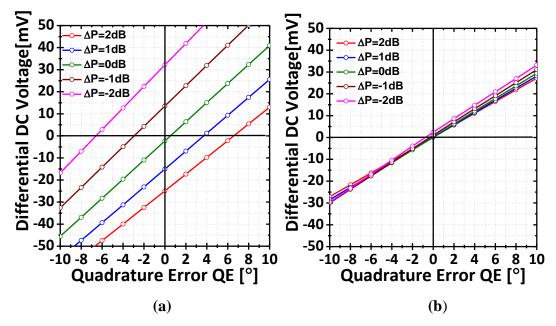

| 5.4.2       | Quadrature Error Correction                              | 135   |

| 5.4.3       | Quadrature Error Extractor                               | 137   |

| 5.5 M       | easurement Results                                       | 142   |

| 5.6 Su      | ımmary                                                   | 145   |

| 6 Conclu    | usions and Future Work                                   | 146   |

| F | Refere | nces                          | 154 |

|---|--------|-------------------------------|-----|

|   | 6.2    | Future Work                   | 149 |

|   | 6.1    | Conclusions and Contributions | 146 |

## **List of Figures**

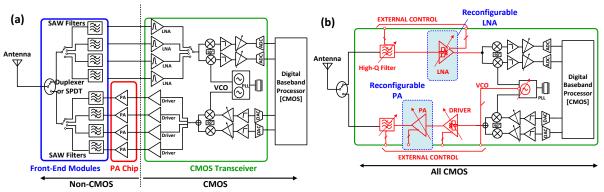

| Figure 1.1 (a) Conventional multi-band radio transceiver. (b) Frequency-reconfigurable, all-                                          |

|---------------------------------------------------------------------------------------------------------------------------------------|

| CMOS integrated radio.                                                                                                                |

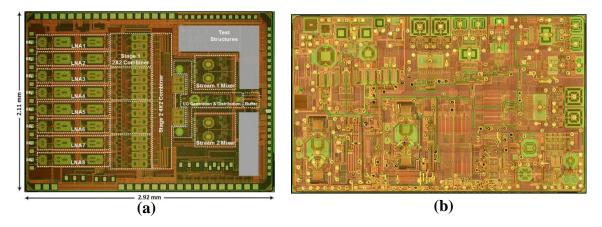

| Figure 1.2 Modern RFIC designs employ dozens of inductors/transformers: (a) state-of-the-art 8-                                       |

| channel beamforming MIMO receiver in 65-nm CMOS [85], (b) (not drawn to scale) Qualcomm's                                             |

| multi-band multi-mode RF transceiver (RTR8600) (Image taken from:                                                                     |

| https://www.ifixit.com/Teardown/Apple+A6+Teardown/10528)                                                                              |

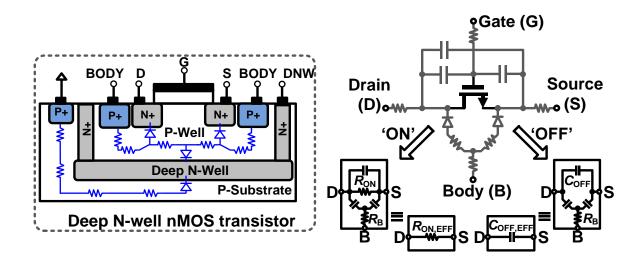

| Figure 2.1 (a) Structure of a deep N-well (NDW) nMOS transistor. (b) Equivalent model of the                                          |

| DNW transistor in the on-state and the off-state when used as a switch                                                                |

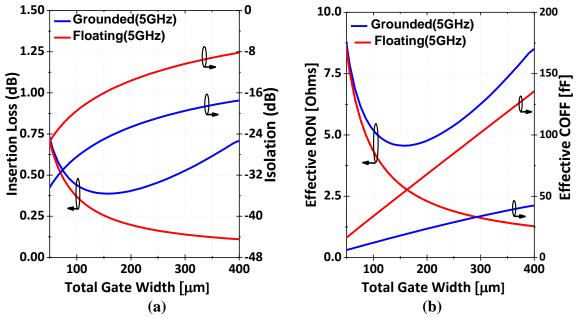

| Figure 2.2 Deep N-well nMOS transistor in 28 nm CMOS: (a) simulated insertion loss and                                                |

| isolation, (b) extracted effective R <sub>ON</sub> and C <sub>OFF</sub> with grounded and floated body terminals. All                 |

| simulations were performed at 5 GHz. In the floated configuration, the body terminal was                                              |

| connected to ground through a $10 \text{ k}\Omega$ resistor                                                                           |

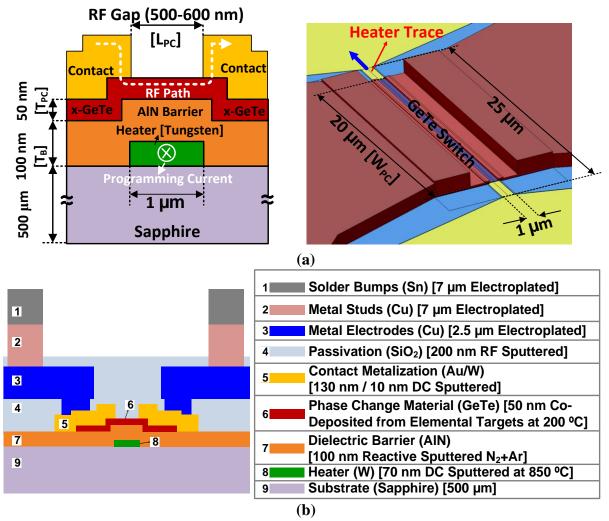

| Figure 2.3 (a) Cross-section and isometric view of the four-terminal PC switch. (b) The layer stack                                   |

| of the PC die with the layer materials and thicknesses indicated. The figures are not drawn to scale.                                 |

|                                                                                                                                       |

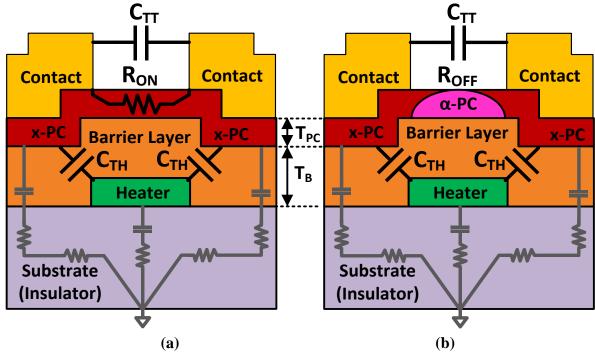

| Figure 2.4 Dominant parasitics in the four-terminal PC switch in the (a) on-state, and (b) off-state.                                 |

|                                                                                                                                       |

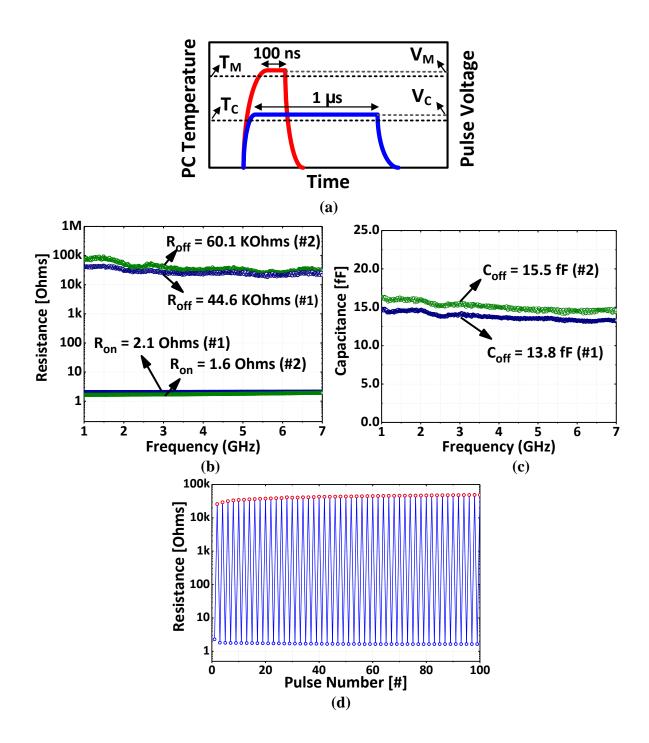

| Figure 2.5 (a) Heat and voltage profiles of the amorphization (red) and crystallization (blue)                                        |

| programming pulses with 10 ns rise and fall times. Stand-alone measurements of two fabricated                                         |

| PC switches (#1, #2): (b) R <sub>ON</sub> and R <sub>OFF</sub> , and (c) C <sub>OFF</sub> . (d) Switch #2 resistance as a function of |

| switching pulses                                                                                                                      |

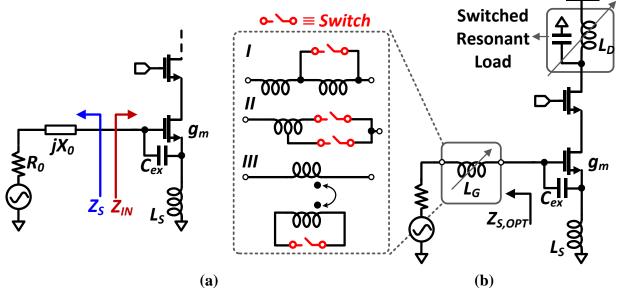

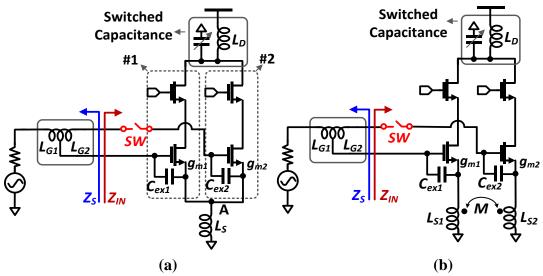

| Figure 2.6 (a) Input network of a inductively degenerated CS LNA (b) CS LNA with a                               |

|------------------------------------------------------------------------------------------------------------------|

| reconfigurable gate inductor for multi-band operation. The gate inductance is reconfigured either                |

| using a tapped-inductor (configurations I, II) or by switching the secondary coil of a transformer               |

| (configuration III). While CMOS switches can be used, high-F <sub>CO</sub> PC RF switches are preferable         |

| to maintain RF performance when the switches are turned on                                                       |

| Figure 2.7 (a) Dual-band CS LNA with two CS legs and a shared source inductor (b) Dual-band                      |

| CS LNA with two CS legs and coupled source inductors                                                             |

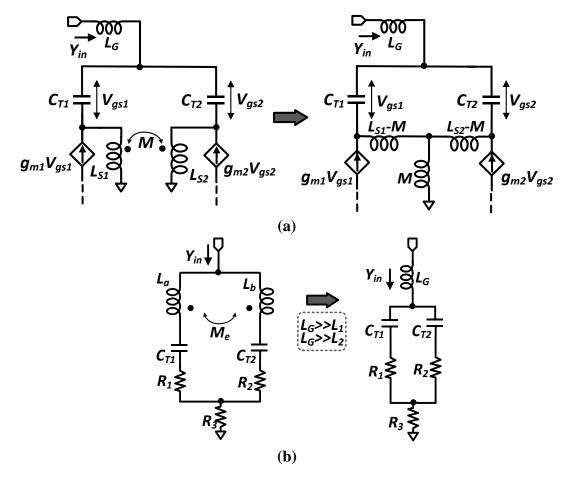

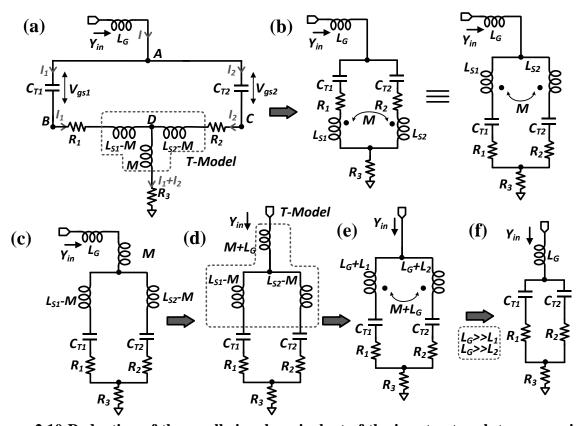

| Figure 2.8 (a) Small-signal equivalent of the input matching network of a CS LNA with two CS                     |

| legs, a shared gate inductor and with finite coupling between the source inductors. Effect of $C_{\text{gd}}$ is |

| ignored. (b) Equivalent representation with gate inductance merged into an equivalent transformer.               |

|                                                                                                                  |

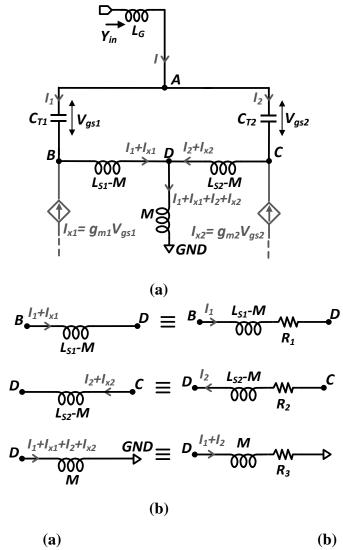

| Figure 2.9 (a) Small-signal equivalent of the input network with the branch currents identified. (b)             |

| Equivalent representation of the wire-segments with inductors                                                    |

| Figure 2.10 Reduction of the small-signal equivalent of the input network to a canonical                         |

| representation. 28                                                                                               |

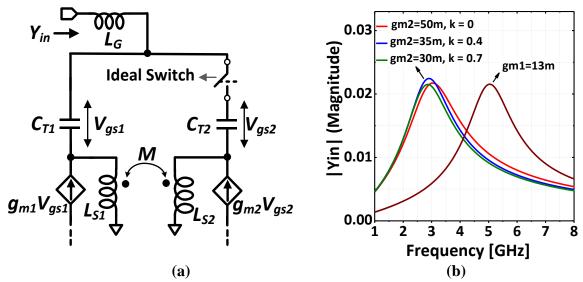

| Figure 2.11 (a) Design example of a dual-band input network using ideal elements and a single                    |

| switch. (b) Magnitude of input admittance for different values of coupling factor 'k' between the                |

| source inductors L <sub>S1</sub> and L <sub>S2</sub>                                                             |

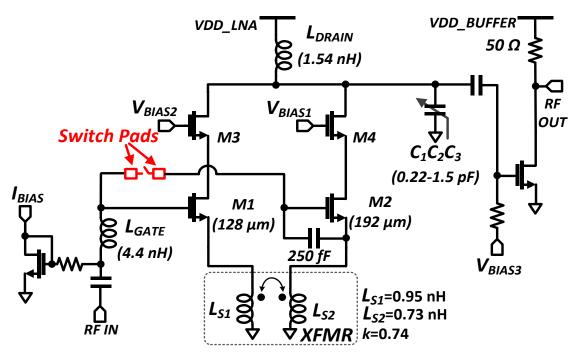

| <b>Figure 2.12</b> Schematic diagram of the 3/5 GHz LNA designed in a 0.13 μm process                            |

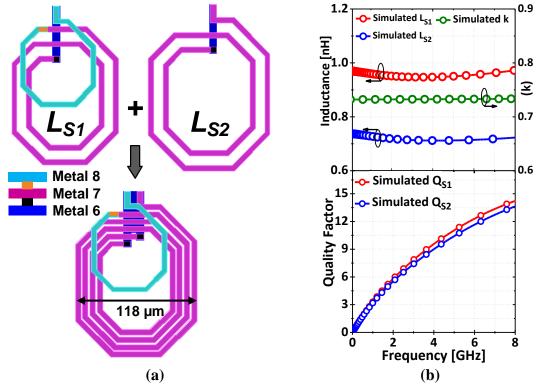

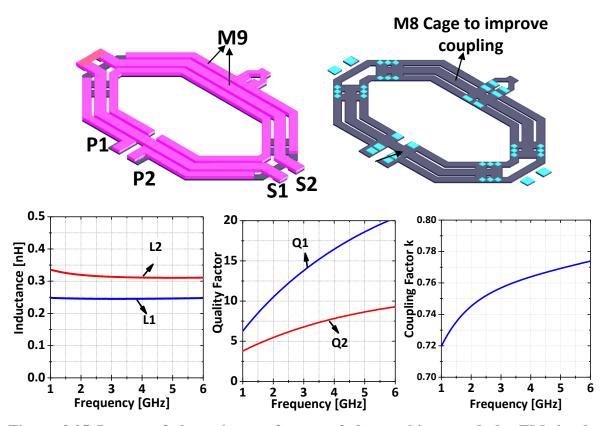

| Figure 2.13 (a) Layout implementation of three-terminal the high-k source transformer with                       |

| interleaved windings. (b) Simulated values of primary and secondary coil inductances and quality                 |

| factors, and the transformer coupling efficient k                                                                |

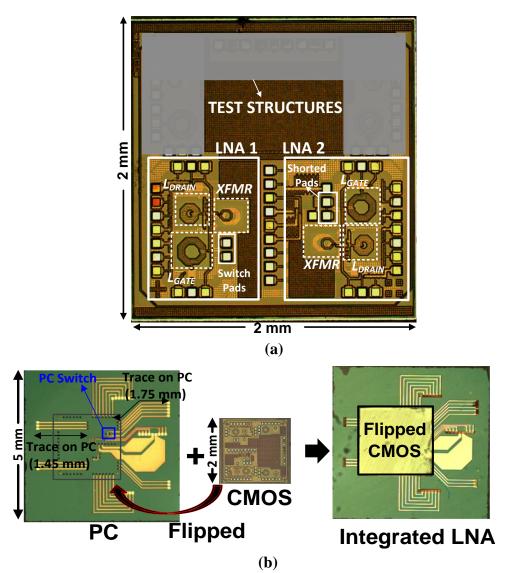

| <b>Figure 2.14</b> (a) Die photo in 0.13 μm CMOS. LNA #1 has open switch pads for integration with               |

|------------------------------------------------------------------------------------------------------------------|

| PC switch and for CMOS testing in the 5 GHz mode. LNA #2 has shorted switch pads for 3 GHz                       |

| mode testing. (b) Die photo of the integrated LNA.                                                               |

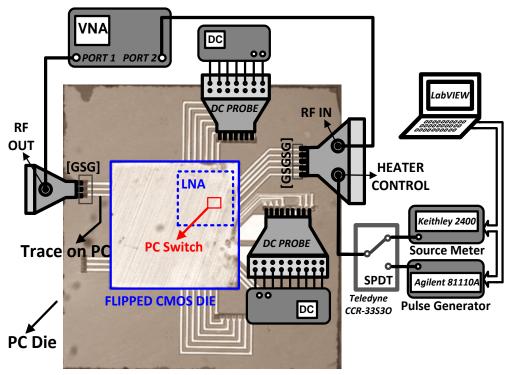

| Figure 2.15 Measurement setup of the integrated LNA-PC chip using two RF and two DC probes.                      |

|                                                                                                                  |

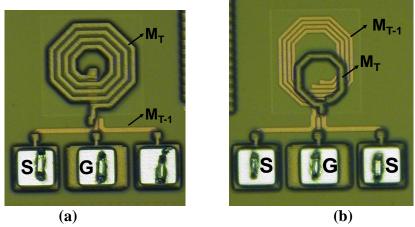

| Figure 2.16 (a) Micrograph of the single-ended inductor test structure (drain inductor of the                    |

| implemented CMOS LNA). (b) Micrograph of the high-k transformer test structure (source                           |

| transformer of the implemented CMOS LNA). M <sub>T</sub> = Top Metal                                             |

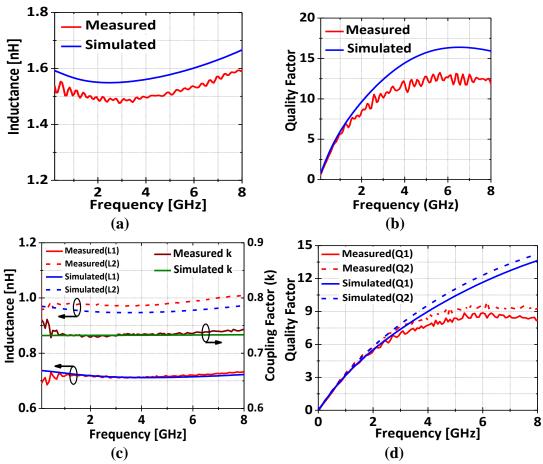

| Figure 2.17 Measured and simulated (a) inductance, and (b) quality factor of the inductor test                   |

| structure. Measured and simulated (a) inductances, coupling factor, and (b) quality factor of the                |

| coils in the transformer test structure                                                                          |

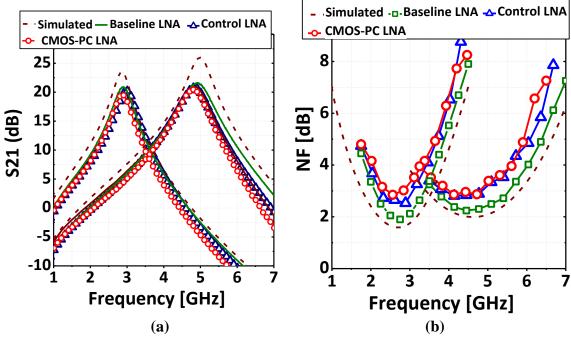

| Figure 2.18 Measured (a) $S_{21}$ and (b) NF of the CMOS-only baseline, control and the B1 CMOS-                 |

| PC LNAs. Simulated LNA performance is also shown. 38                                                             |

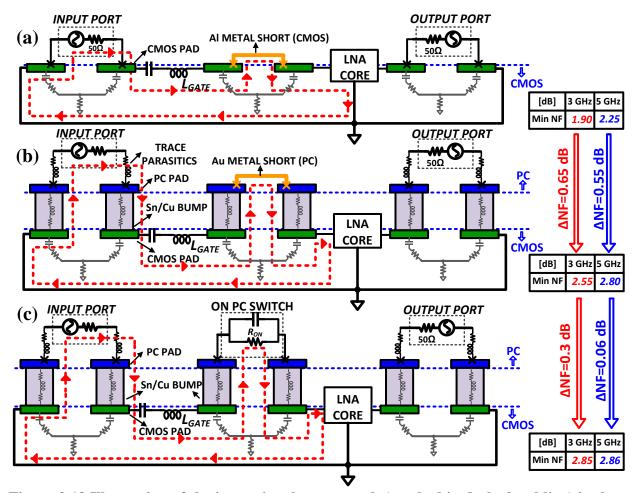

| Figure 2.19 Illustration of the input signal return path (marked in dashed red line) in the 3 GHz                |

| mode for (a) baseline CMOS with a metal short, (b) control LNAs with Au metal short on the PC                    |

| die, and (c) CMOS-PC LNA. In the 5 GHz mode, the input signal return path bypasses the switch                    |

| pads completely, the metal shorts in (a) and (b) are absent, and the PC switch in (c) is in the off-             |

| state. The magnitude of change in the minimum NF observed in the three configurations is also                    |

| shown                                                                                                            |

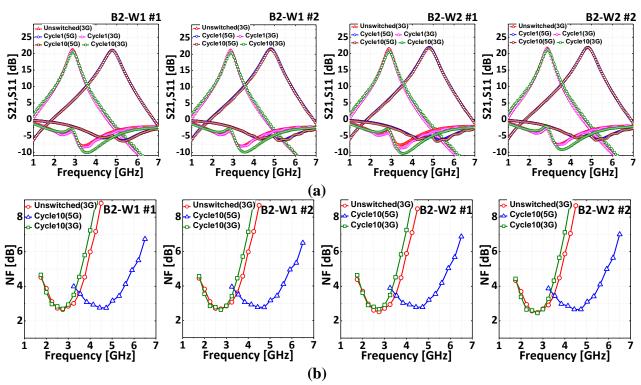

| Figure 2.20 (a) Measured S <sub>21</sub> , S <sub>11</sub> and (b) NF of 4 CMOS-PC LNAs (batch 2) in the 3/5 GHz |

| modes before switching, and after one/ten switching cycles                                                       |

| Figure 2.21 Measured IIP3 of the baseline LNA (CMOS-only) in (a) 3 GHz, and (b) 5 GHz modes.                     |

| 42                                                                                                               |

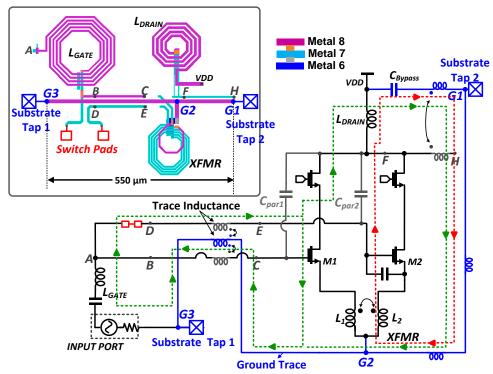

| Figure 2.22 Circuit and layout floorplan of the LNA. The buffer is not shown. Two possible AC                               |

|-----------------------------------------------------------------------------------------------------------------------------|

| current loops (external input loop in green, internal loop through bypass capacitance in red) are                           |

| marked by dashed lines. Interconnect segment G1-G2-G3 with substrate taps on either end is the                              |

| ground trace drawn in the top metal layer                                                                                   |

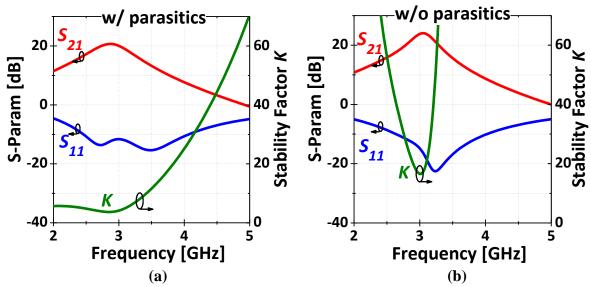

| Figure 2.23 Schematic simulations of the LNA in the 3 GHz mode (b) with and (c) without an EM                               |

| model of the input/output and ground metal traces and parasitic capacitances $C_{\text{par1}}$ and $C_{\text{par2}}$ . Both |

| C <sub>par1</sub> and C <sub>par2</sub> were assumed to be 20 fF                                                            |

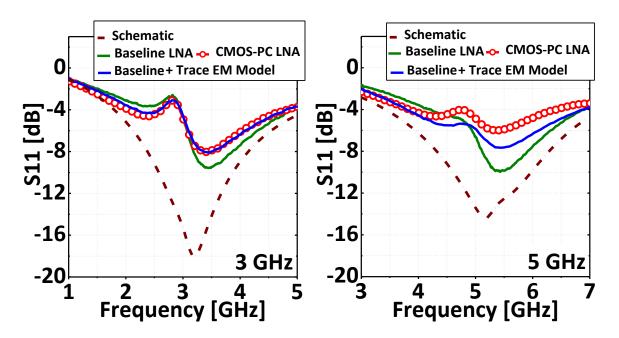

| Figure 2.24 Effect of the addition of an EM model of the input traces on PC die on the $S_{11}$ of the                      |

| baseline CMOS-only LNA and its comparison with $S_{11}$ of the B1 CMOS-PC LNA. Simulated $S_{11}$                           |

| of the LNA schematic (comprising foundry-provided RF models of the transistor and capacitors,                               |

| and EM models of the input/output pads, gate, drain inductors and the source transformer) is also                           |

| shown                                                                                                                       |

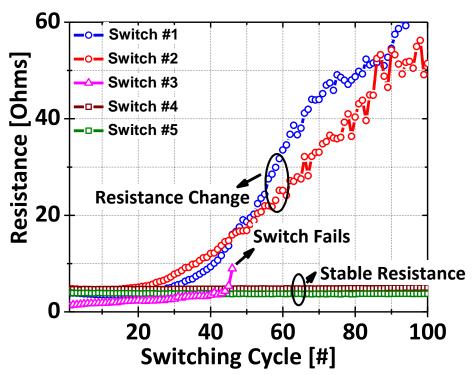

| <b>Figure 2.25</b> Measured resistance change of 5 standalone-switches over 100 switching cycles 47                         |

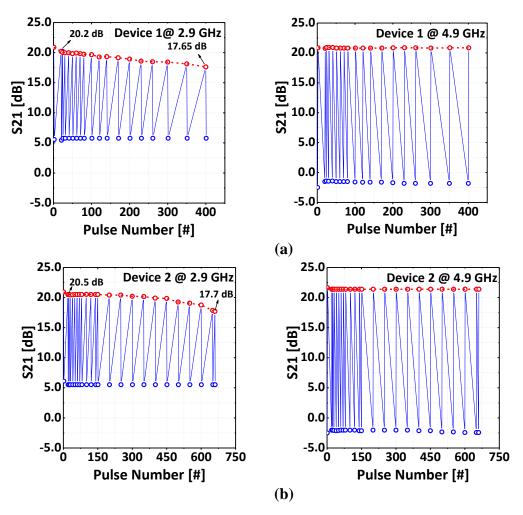

| Figure 2.26 (a) Measured LNA-PC B2-W1 #1 S <sub>21</sub> at 2.9 GHz and 4.9 GHz over 200 switching                          |

| cycles (total number of pulses = 400). Each switching cycle comprises one amorphization and one                             |

| crystallization pulse. (b)Measured LNA-PC B2-W1 #2 $S_{21}$ at 2.9 GHz, and 4.9 GHz over 330                                |

| switching cycles (total number of pulses = 660)                                                                             |

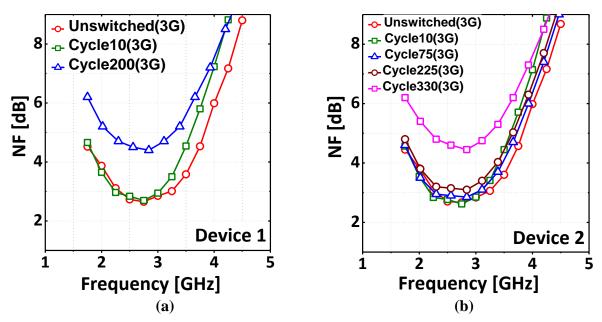

| Figure 2.27 Measured NF in the 3 GHz mode of (a) LNA-PC B2-W1 #1, and (b) LNA-PC B2-                                        |

| W1 #2 over large number of switching cycles                                                                                 |

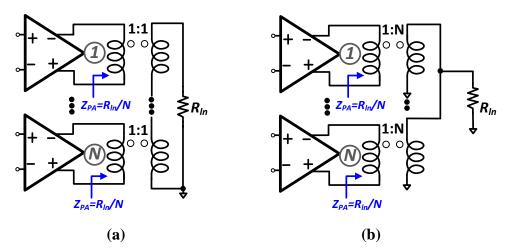

| Figure 3.1 Transformer-based power combiners. (a) Voltage combiner, and (b) current combiner                                |

| with 1:N turns ratio.                                                                                                       |

| Figure 3.2 Secondary tuning capacitance in a voltage transformer combiner and its effect on output                          |

| power level                                                                                                                 |

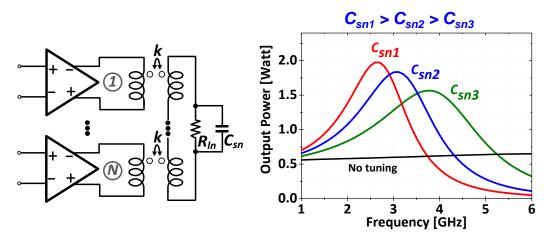

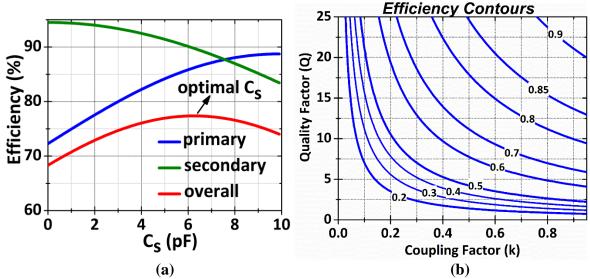

| Figure 3.3 (a) Single-stage equivalent of the transformer combiner. (b) Transformation steps to            |

|------------------------------------------------------------------------------------------------------------|

| derive a simplified equivalent network of a single-stage of the transformer combiner 54                    |

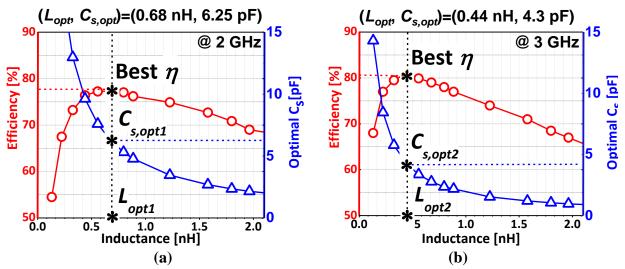

| Figure 3.4 (a) Variation of transformer efficiency with $C_s$ . Here, $L=0.68$ nH, $k=0.7$ , $Q_0=12$ ,    |

| $\omega 0 = 2$ GHz. (b) Transformer maximum efficiency contours in the (k,Q) design space                  |

| Figure 3.5 Transformer efficiency for different values of coil self-inductance (L) at (a) 2 GHz,           |

| and (b) 3 GHz                                                                                              |

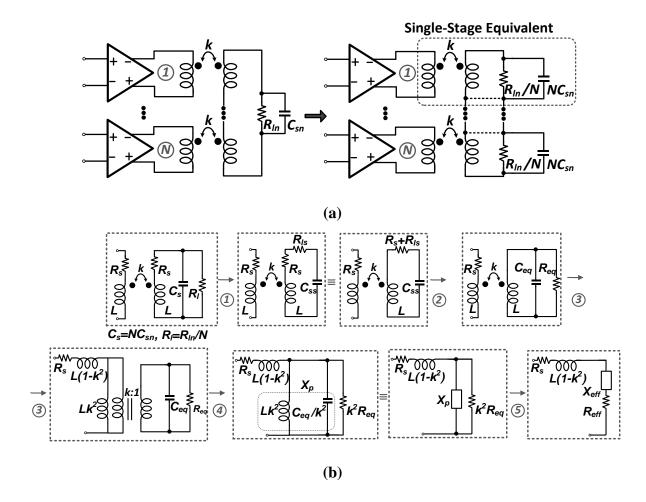

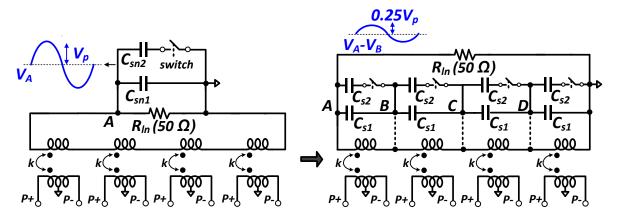

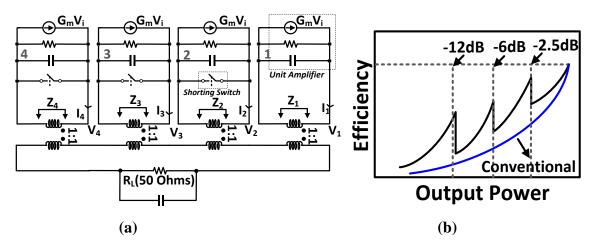

| <b>Figure 3.6</b> Capacitance-switched dual-band power-combining PA                                        |

| <b>Figure 3.7</b> Figure-8 combiner and its equivalent circuit representation                              |

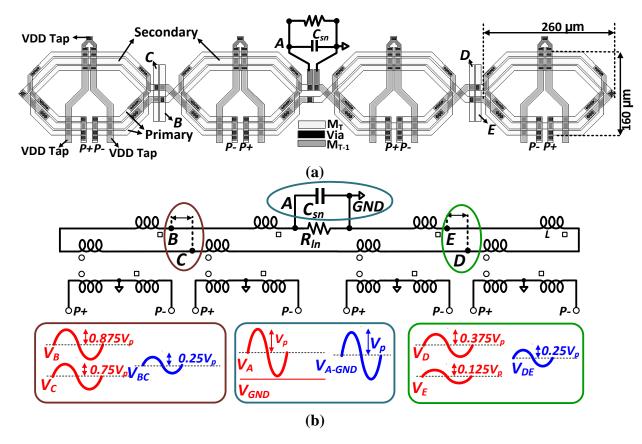

| Figure 3.8 (a) Modified 'figure-8' layout of the designed transformer combiner for low insertion           |

| loss and high coupling. The locations of two pairs of low-swing nodes (B-C and D-E) are also               |

| shown. (b) Equivalent circuit representation. 62                                                           |

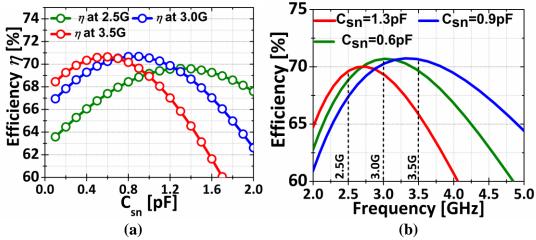

| Figure 3.9 (a) Optimal values of $C_{sn}$ ( $C_{sn,opt}$ ) at 2.5/3/3.5 GHz. (b) Efficiency variation with |

| frequency for different values of C <sub>sn,opt</sub>                                                      |

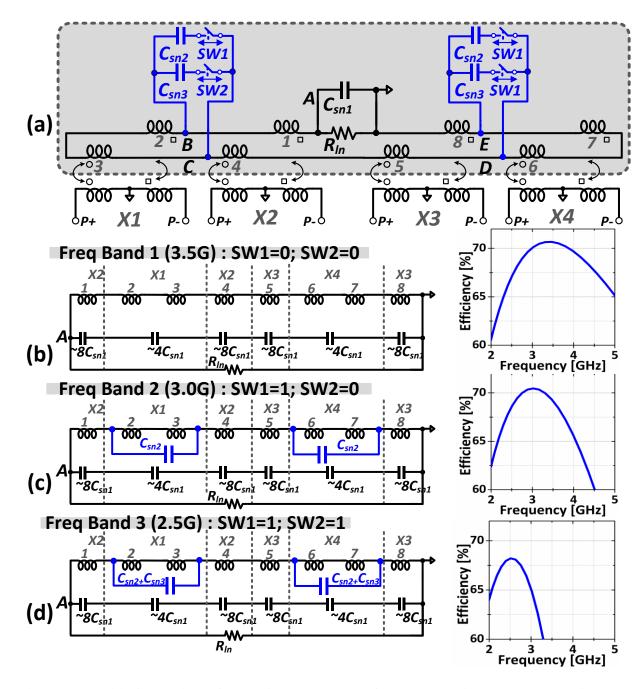

| Figure 3.10 (a) Operation of the triple-band transformer combiner and the equivalent circuit               |

| representation (b)-(d) of the secondary coil in the three frequency bands. Simulated efficiency            |

| curves of the designed transformer combiner assume ideal switches and the following capacitance            |

| values: $C_{sn1} = 0.55 \ pF$ , $C_{sn2} = 2.35 \ pF$ and $C_{sn3} = 2.8 \ pF$                             |

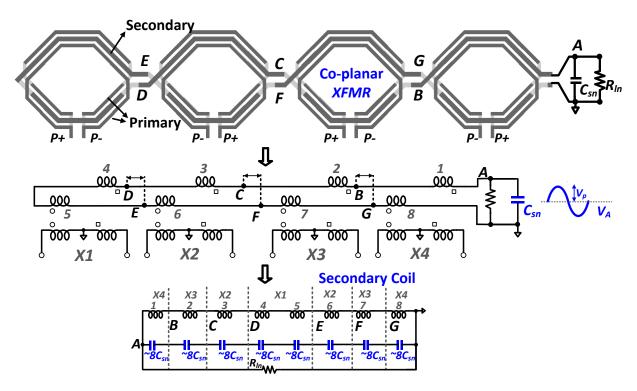

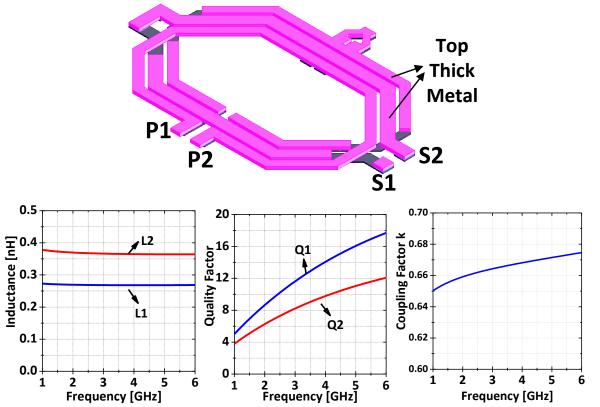

| Figure 3.11 Layout of the unit transformer of the combiner, and the EM-simulated inductance,               |

| quality factor of the primary and secondary coils and the coupling factor                                  |

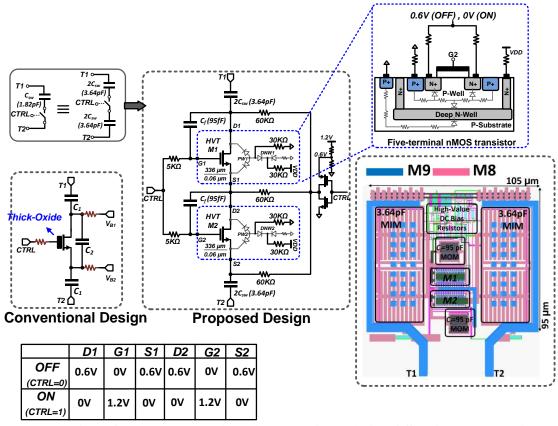

| Figure 3.12 Design of the three-terminal (T1, T2, CTRL) CMOS switched capacitor used in the                |

| transformer combiner. DC bias values of the transistor terminals in the ON and OFF states is also          |

| shown 67                                                                                                   |

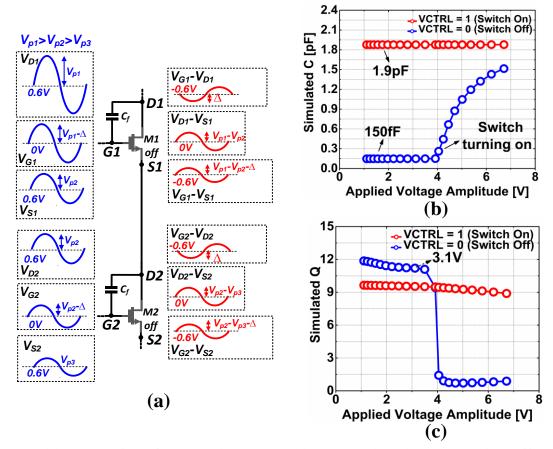

| Figure 3.13 (a) Illustration of the terminal-to-terminal RF swings in the capacitor off state. (b)  |

|-----------------------------------------------------------------------------------------------------|

| Simulation capacitance and quality factor with different incident power levels                      |

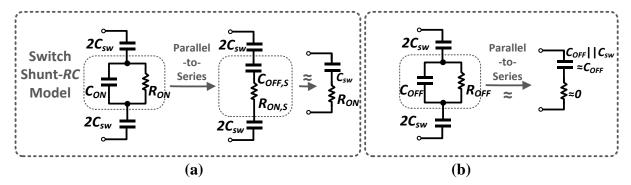

| Figure 3.14 Equivalent Circuit of the switched capacitor in the (a) on and (b) off states assuming  |

| a shunt-RC model for the transistor switch                                                          |

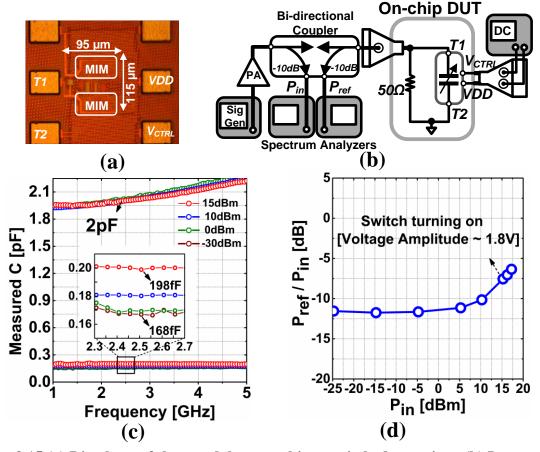

| Figure 3.15 (a) Die photo of the standalone combiner switched capacitor. (b) Large-signal           |

| measurement set-up. (c) Measured ratio of reflected and incident power for different incident       |

| power-levels. (d) Measured off-state and on-state capacitance values for different incident power   |

| levels                                                                                              |

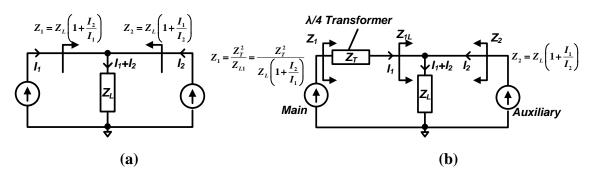

| Figure 3.16 (a) Active load-pull using two coherent sources. (b) Operation of a Doherty amplifier.  |

| 71                                                                                                  |

| Figure 3.17 (a) Model of a four-way power-combining PA. (b) Efficiency behavior at back-off.        |

|                                                                                                     |

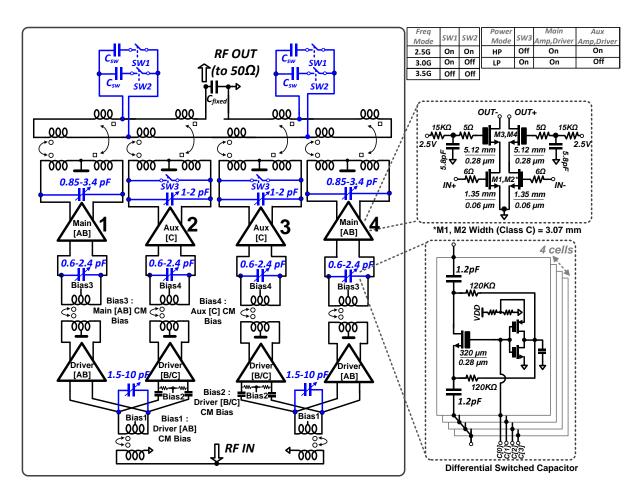

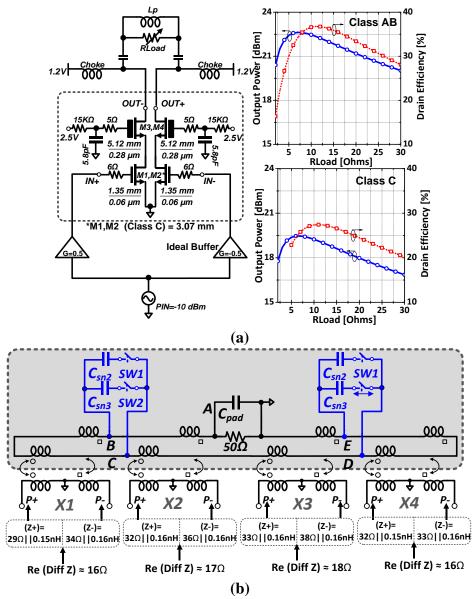

| Figure 3.18 Schematic of the implemented triple-band PA with a digitally-tuned, 4-way               |

| transformer combiner in the output stage                                                            |

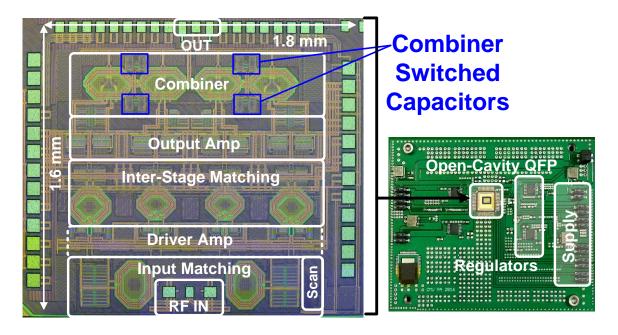

| Figure 3.19 PA die photo and PCB test board                                                         |

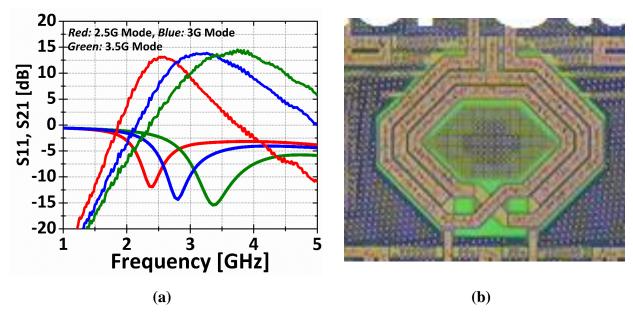

| Figure 3.20 (a) Measured PA small-signal performance. (b) Close proximity of thick transformer      |

| coil traces (< 4 $\mu m$ ) to high-density fill structures in top and lower level metal layers. All |

| transformer coil traces were 12 µm wide                                                             |

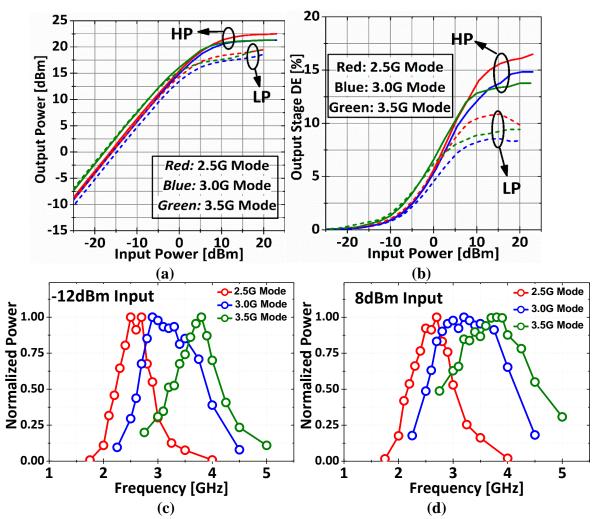

| Figure 3.21 Measured PA (a) output power and (b) output stage drain efficiency in the three         |

| frequency modes with 2.6/3/3.65 CW signals respectively. Measured frequency selectivity of the      |

| PA at low (-12 dBm input) and high (8 dBm) input power levels in the three frequency modes. 77      |

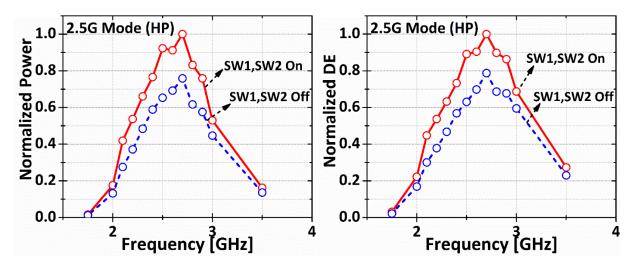

| Figure 3.22 PA behavior in the 2.5 GHz mode with the combiner switches turned on and off            |

|                                                                                                     |

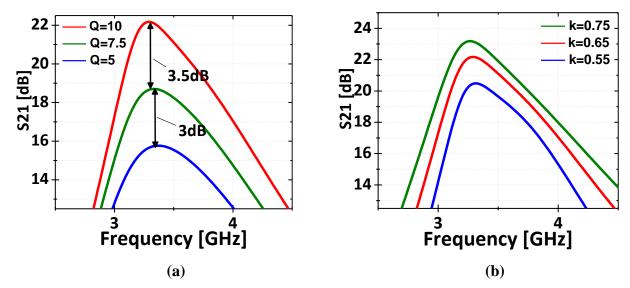

| Figure 3.23 Simulated small-signal PA gain in the 3.5 GHz mode with different (a) inductor Qs       |

|-----------------------------------------------------------------------------------------------------|

| and (b) transformer coupling factors (These simulations included C-extracted transistor caliber and |

| power/ground routing parasitics)                                                                    |

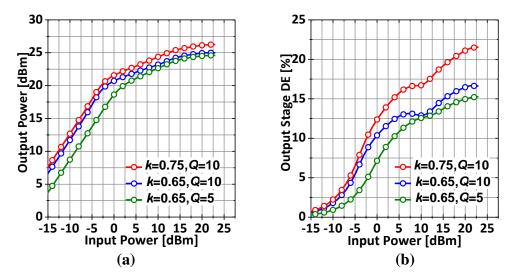

| Figure 3.24 Simulated PA power and output stage drain efficiency in the 3.5 GHz mode with           |

| different (a) inductor Qs and (b) transformer coupling factors (These simulations included C-       |

| extracted transistor netlists and power/ground routing parasitics)                                  |

| Figure 3.25 Layout of the unit transformer of the combiner, and the EM-simulated inductance,        |

| quality factor of the primary and secondary coils and the coupling factor                           |

| Figure 3.26 (a) Load-pull simulation setup of unit amplifiers. (b) Simulated impedances at the      |

| input of the designed transformer combiner. 82                                                      |

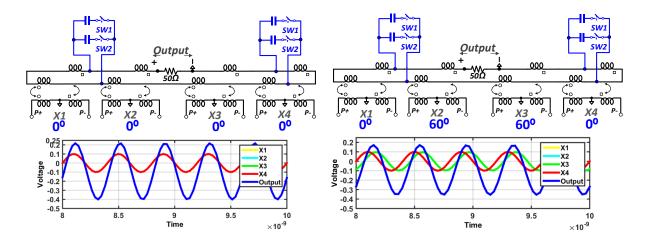

| Figure 3.27 Transient simulation demonstrating the effect of phase imbalance between the class      |

| AB and class C amplifiers on voltage combining in the designed transformer combiner. The            |

| combiner is in the 3.5 GHz mode (all combiner switches are turned off)                              |

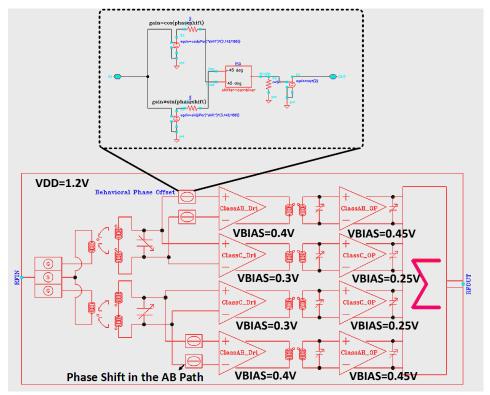

| Figure 3.28 Top-level PA simulation setup with behavioral phase offsets added in the main Class     |

| AB amplifier path. The phase offsets are inserted before the Class AB driver stage                  |

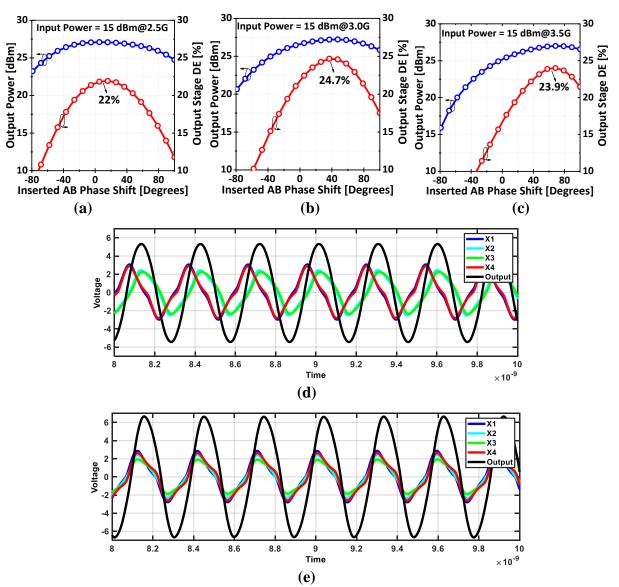

| Figure 3.29 Top-level PA simulation: Output power and output stage DE in the (a) 2.5 GHz, (b)       |

| 3 GHz, and (c) 3.5 GHz modes with different amounts of phase offsets in the main amplifier path.    |

| Transient simulations showing the voltages developed at the output of the Class AB amplifiers       |

| (X1, X4) and Class C amplifiers (X2, X3) (a) without any phase offset, and (e) with 60 phase offset |

| in the main amplifier path in the 3.5 GHz mode. All simulations are based on the setup shown in     |

| Figure 3.28                                                                                         |

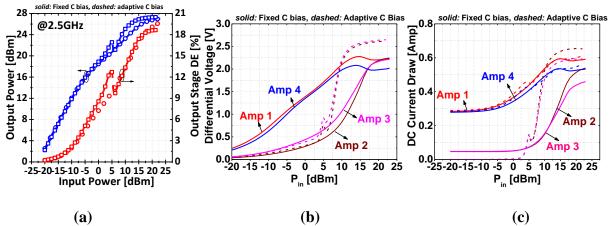

| Figure 3.30 Simulated (a) output power, output stage drain efficiency, (b) differential voltage     |

| amplitude of the unit amplifiers, and (c) DC current draw with and without adaptive C bias in the   |

| 2.5 GHz mode. Amp 1 and 2 are the class AB unit amplifiers, while Amp 3 and 4 are the class C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| amplifiers. The adaptive bias circuit adopted in these simulations was like the one implemented in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| [67]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

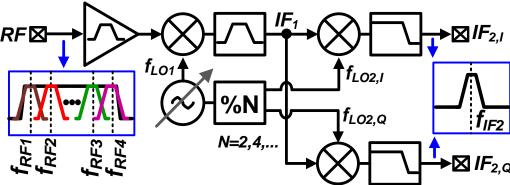

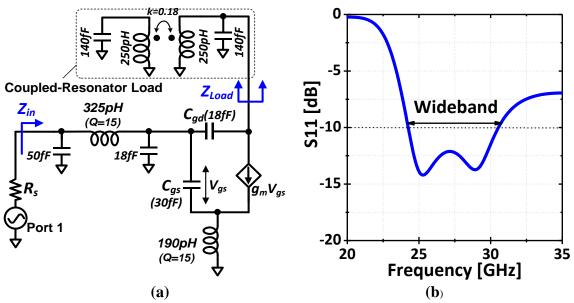

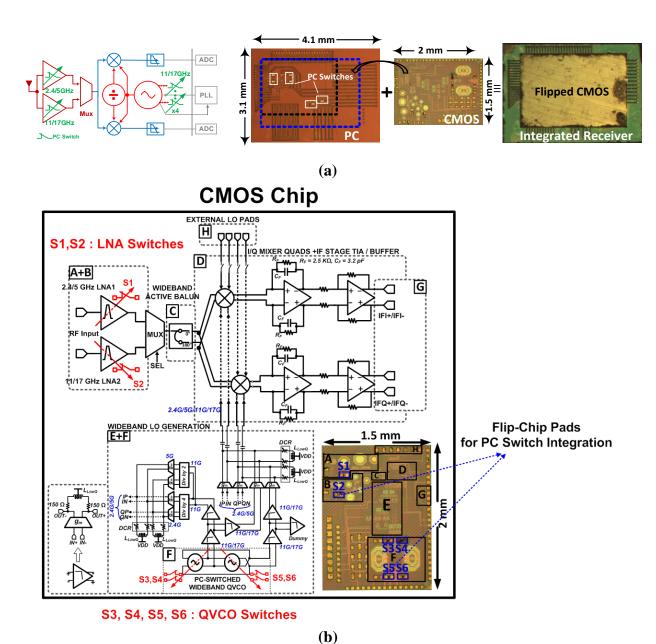

| Figure 4.1 Block diagram of a sliding IF quadrature receiver adopted to relax the requirements of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LO generation and distribution. In a direct-conversion and low-IF implementation, the first mixing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| and divide-by-N stages are omitted. A wideband LNA offers the flexibility of covering both                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| contiguous and non-contiguous narrowband channels using the same RF front-end90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

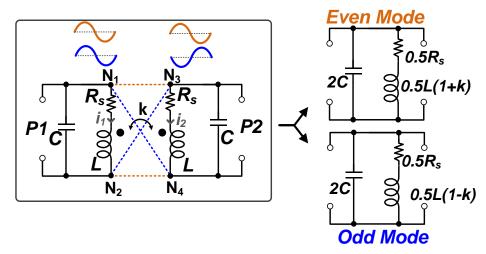

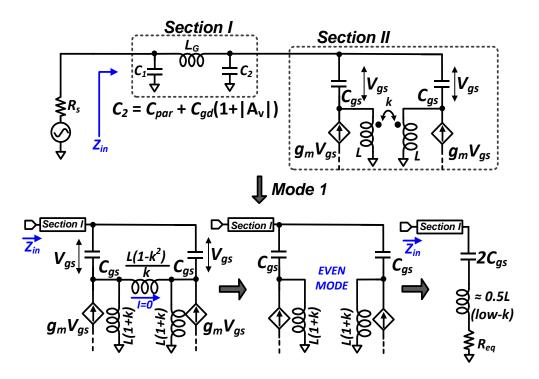

| Figure 4.2 Even and odd resonant modes of a transformer coupled-resonator. Since the current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| flowing in the primary and secondary coils are in phase (out of phase) in the even (odd) mode, the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| voltage amplitudes developed across nodes $N_1\text{-}N_2$ and $N_3\text{-}N_4$ are identical. Nodes $N_1$ and $N_2$ can                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| either be respectively electrically connected to $N_3$ and $N_4$ in the even mode, or with $N_4$ and $N_3$ in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| the odd mode, resulting in equivalent parallel-RLC networks from which the resonant mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| frequencies can be deduced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

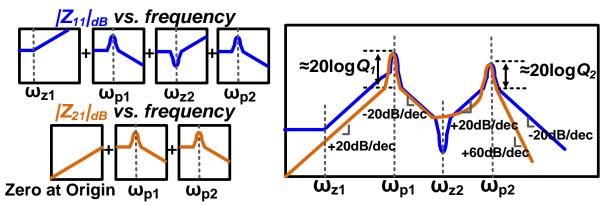

| <b>Figure 4.3</b> Representative bode amplitude plots of $Z_{11}$ and $Z_{21}$ of a transformer coupled-resonator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

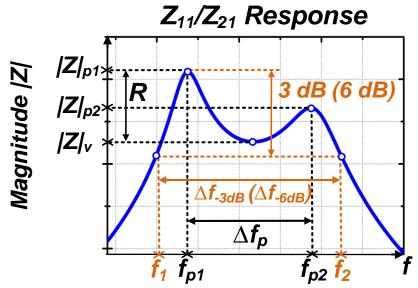

| Figure 4.4 Typical frequency response of magnitudes of $Z_{11}$ and $Z_{21}$ of transformer coupled-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| resonator. $f_{p1}$ and $f_{p2}$ are the locations of the complex pole pairs, and $\Delta f_p$ represents their frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| separation. $ Z _{p1}$ and $ Z _{p2}$ are the values of the gain peaks, $ Z _v$ is the minimum value of gain within                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\Delta f_p$ (where $f_{p1} \leq f \leq f_{p2}$ ). The 3-dB bandwidth, marked as $\Delta f_{\text{-3dB}}$ in the figure, is defined with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $respect \ to \  Z _{max} = max( Z _{p1}, \  Z _{p2}). \ In \ a \ similar \ manner, \ \Delta f_{\text{-6dB}} \ can \ also \ be \ defined. \ R =  Z _{max} -  Z _{vac} -  Z$ |

| represents the gain ripple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

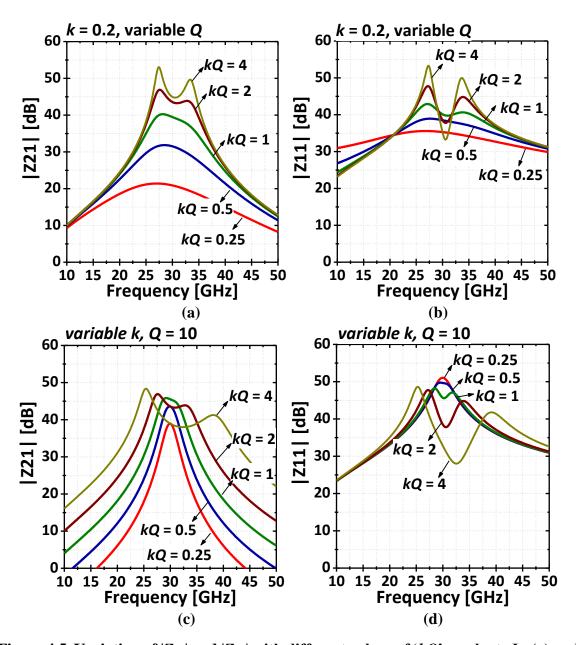

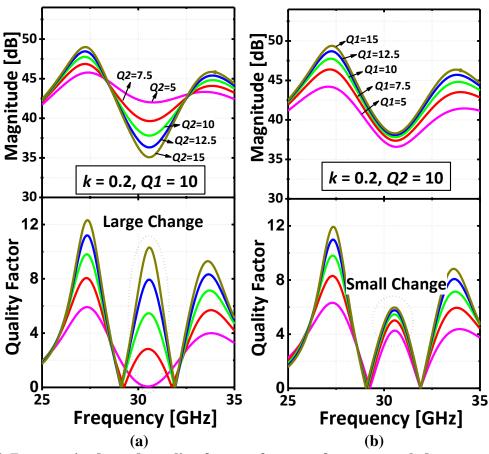

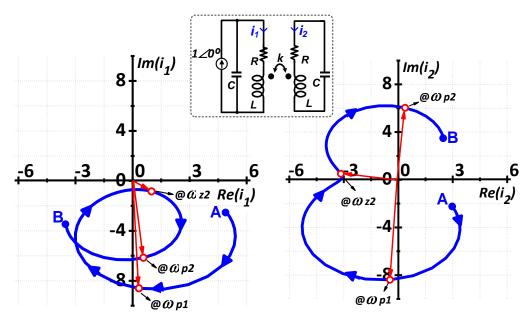

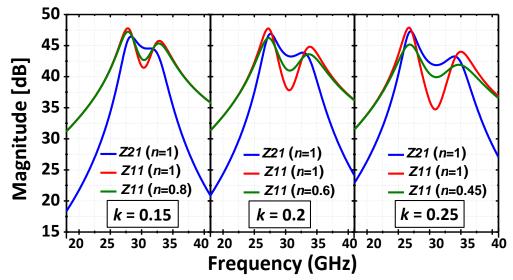

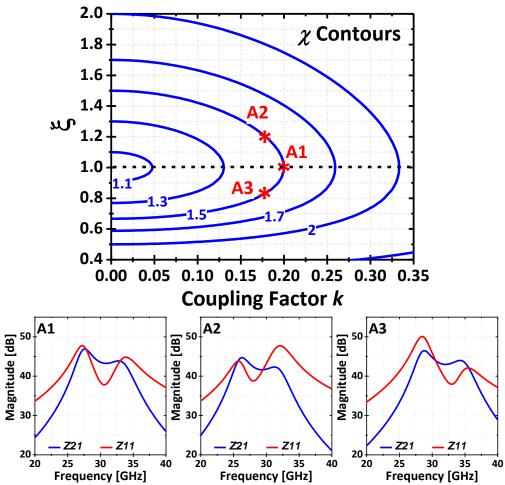

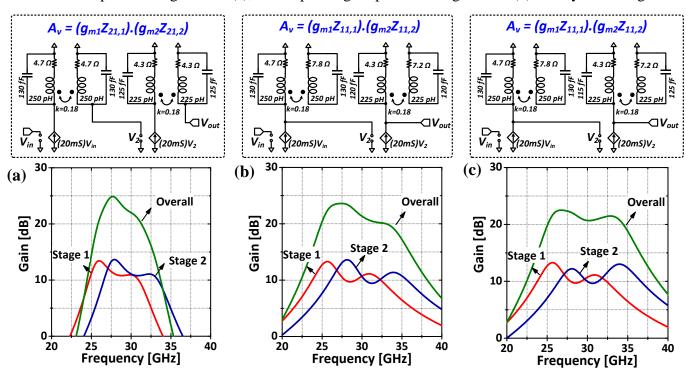

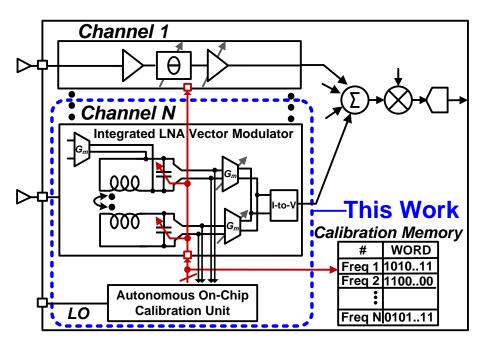

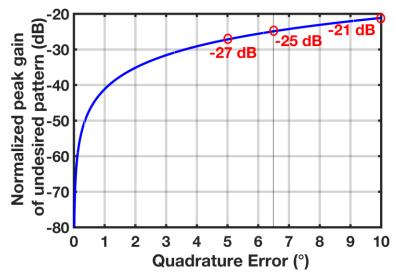

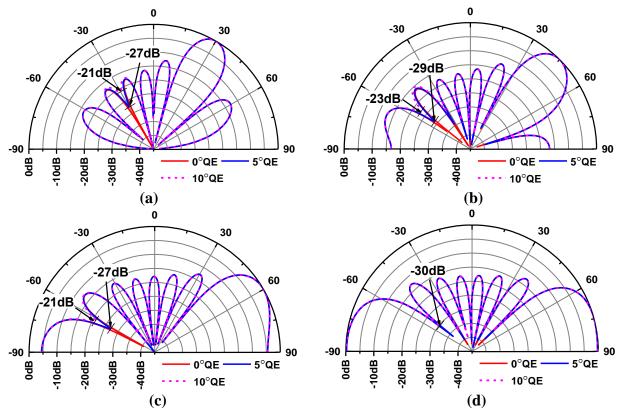

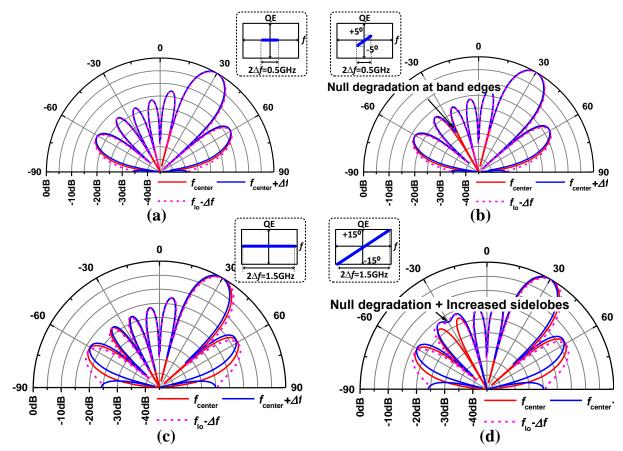

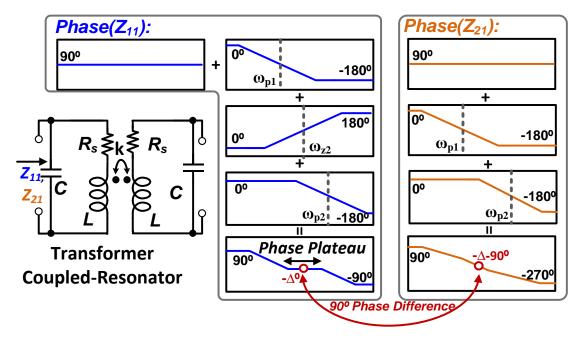

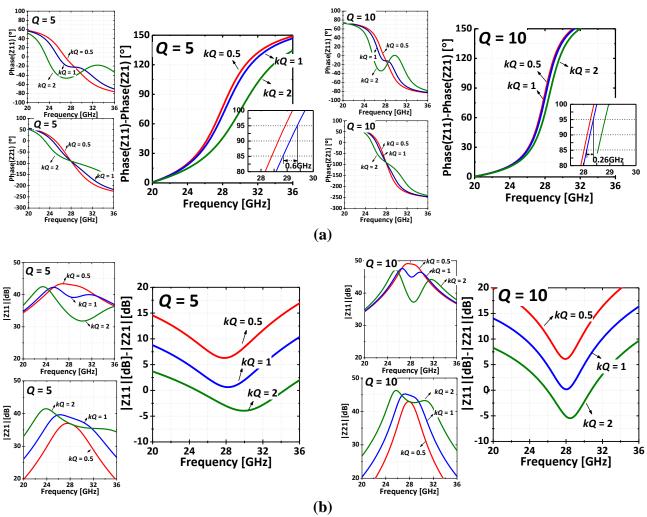

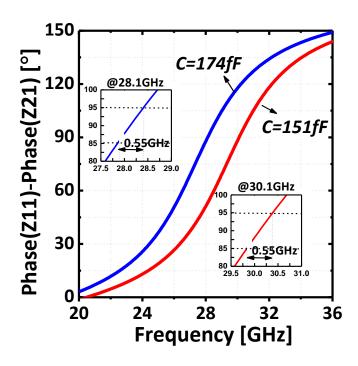

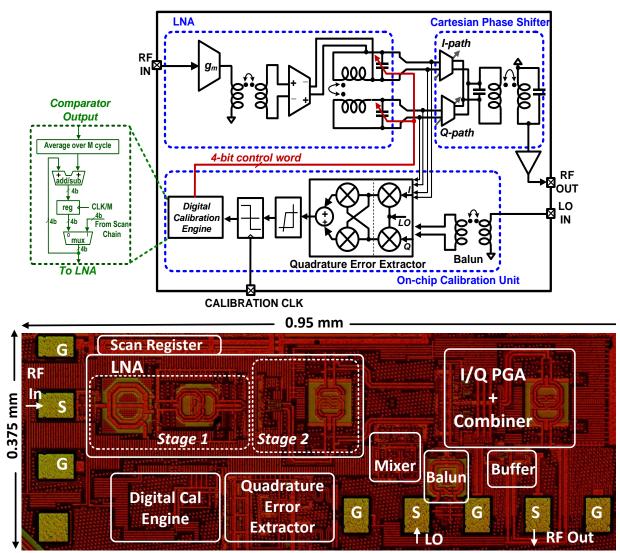

| <b>Figure 4.5</b> Variation of $ Z_{21} $ and $ Z_{11} $ with different values of 'kQ' product. In (a) and (b), Q was                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |