## Carnegie Mellon University

### CARNEGIE INSTITUTE OF TECHNOLOGY

### THESIS

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF Doctor of Philosophy

| TITLE | Discrete Dynamics in Chemical Process Control and Automation |  |

|-------|--------------------------------------------------------------|--|

|       |                                                              |  |

PRESENTED BY Blake Rawlings

ACCEPTED BY THE DEPARTMENT OF

Chemical Engineering

B. ERIK YDSTIE

4/25/16

B. ERIK YDSTIE, ADVISOR

DATE

4/25/16

L. BIEGLER

LORENZ BIEGLER, DEPARTMENT HEAD

DATE

APPROVED BY THE COLLEGE COUNCIL

VIJAYAKUMAR BHAGAVATULA

4/25/16

DEAN

DATE

### Discrete Dynamics in Chemical Process Control and Automation

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

$\mathrm{in}$

Chemical Engineering

Blake C. Rawlings B.S., Chemical Engineering, The University of Texas at Austin

> Carnegie Mellon University Pittsburgh, PA

> > May, 2016

#### Acknowledgements

First, I would like to thank my advisor, Prof. Erik Ydstie, for making this project possible, and for making sure that it was interesting both intellectually and practically. I recall many stimulating conversations with Erik that guided my thoughts on a variety of topics, not limited to research. In addition, I appreciate Erik's willingness to work in an area that has largely been neglected by the academic community in chemical engineering, despite its industrial significance. I would also like to thank the members of my doctoral committee, Prof. Ignacio Grossmann, Prof. John Kitchin, Prof. Bruce Krogh, and Dr. John Wassick, for their feedback and guidance.

Funding for the project was provided by The Dow Chemical Company. Early in the project, Ben Christenson was very helpful in defining a specific problem on the industrial side to motivate the academic research. Later in the project, Joe Bucci was very helpful in applying the results of the research to actual control systems. Throughout the course of the project, John Wassick provided the oversight and coordination to make it successful within Dow.

I would also like to thank my friends in Pittsburgh for making my time here enjoyable. In particular, the grad student softball league in the summers and pick-up soccer on Sundays gave me something to look forward to when research was not enough.

Finally, I would like to thank my family for their continued support and encouragement. Nothing I've done would have been possible without them. Most importantly, thank you Soraya.

#### Abstract

Formal verification has previously been applied to chemical plant control and automation systems to ensure that they operate as intended. This dissertation examines the related objective of proving that a particular control system does not operate as intended. To this end, we present a set of specifications that address certain aspects of the correct operation of a general control system. Some of those specifications, which relate to invariance and reachability of states that satisfy given logical constraints, do not fall within the classes of specifications that have been addressed in previous work related to the falsification of hybrid systems. For a specification from this class, a sound falsification algorithm is presented which can guarantee that a hybrid system does not meet the specification. The algorithm involves abstraction, as a finite-state discrete system, of the infinite-state hybrid dynamical system that arises when discrete control is applied to a continuous process. The falsification result relies on new results that we present which concern the supervisory control of discrete event systems subject to specifications that involve multiple reachability requirements. The methods we present are applied to two industrial case studies, which were provided by The Dow Chemical Company.

We also present two software tools which apply the methods that we have developed. The first tool, SynthSMV, is an extension of the model checking solver NuSMV that can solve some supervisory control problems. NuSMV was chosen as the basis for our work in falsification because previous work has shown that its symbolic model checking algorithms can handle models of industrial-scale control systems in the context of verification. The second tool, st2smv, translates industrial control code to a formal model that can be solved using SynthSMV. The approach is similar to what has been done in previous work that focused on model checking and verification, with some extensions to enable the application of our work concerning supervisory control and falsification.

# Contents

| 1 Introduction |     | 1                                                          |    |

|----------------|-----|------------------------------------------------------------|----|

|                | 1.1 | Control and Automation                                     | 1  |

|                | 1.2 | Design                                                     | 3  |

|                | 1.3 | Analysis                                                   | 3  |

|                | 1.4 | Outline                                                    | 5  |

| <b>2</b>       | Mo  | deling a Plant: Process, Control, and Automation           | 8  |

|                | 2.1 | Comparison of Modeling Frameworks                          | 8  |

|                | 2.2 | Sample-and-Hold Control Systems                            | 10 |

|                | 2.3 | Example: Liquid Holding Tank                               | 13 |

|                | 2.4 | Summary                                                    | 15 |

| 3              | Sup | ervisory Control with Multiple Reachability Specifications | 17 |

|                | 3.1 | Control of Discrete Systems                                | 17 |

|                | 3.2 | Finite Transition Systems                                  | 19 |

|                | 3.3 | Supervisor Synthesis via Model Checking                    | 20 |

|                |     | 3.3.1 Individual CTL Operators                             | 20 |

|                |     | 3.3.2 Multiple CTL Operators                               | 22 |

|                | 3.4 | Labeled Transition Systems                                 | 27 |

|                | 3.5 | Example                                                    | 30 |

|                | 3.6 | Summary                                                    | 34 |

| 4 | Synt        | thSMV                                  | ' v0.1.0                                       | 35 |

|---|-------------|----------------------------------------|------------------------------------------------|----|

|   | 4.1         | Relate                                 | ed Software                                    | 35 |

|   | 4.2         | 2 Changes from NuSMV                   |                                                | 36 |

|   |             | 4.2.1                                  | Input Language                                 | 36 |

|   |             | 4.2.2                                  | Modeling                                       | 38 |

|   | 4.3         | Implei                                 | mentation                                      | 40 |

|   | 4.4         | Exam                                   | ples                                           | 41 |

|   |             | 4.4.1                                  | The Cat and Mouse Problem                      | 41 |

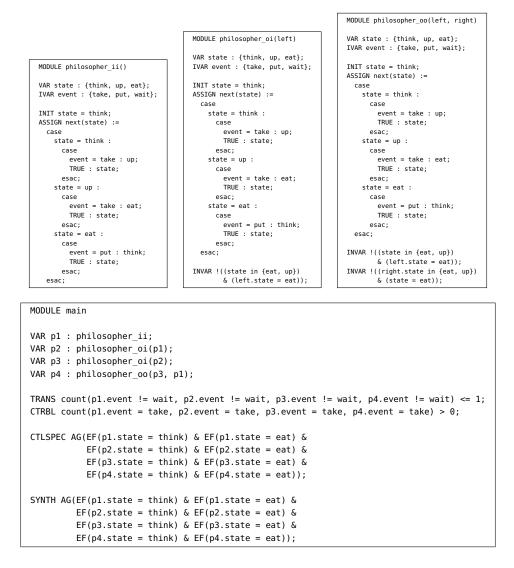

|   |             | 4.4.2                                  | The Dining Philosophers Problem                | 41 |

|   | 4.5         | Summ                                   | ary                                            | 44 |

| - | <b>F</b> -L | :::::::::::::::::::::::::::::::::::::: | an af Imanian ar d Daochabilita Cracifications | 45 |

| 5 |             |                                        |                                                |    |

|   | 5.1         | Falsifi                                | cation of Hybrid Systems                       | 45 |

|   | 5.2         | Discre                                 | te Logic in Sample-and-Hold Control Systems    | 47 |

|   |             | 5.2.1                                  | Discrete Jump System                           | 47 |

|   |             | 5.2.2                                  | SHCSs and $CIR$ Specifications $\hdots$        | 48 |

|   |             | 5.2.3                                  | Initial Abstraction                            | 49 |

|   | 5.3         | 5.3 Falsifying CIR Specifications      |                                                | 50 |

|   |             | 5.3.1                                  | Computing a Restricted Abstraction             | 51 |

|   |             | 5.3.2                                  | Refining the Initial Abstraction               | 55 |

|   | 5.4         | Exam                                   | ples                                           | 55 |

|   |             | 5.4.1                                  | Reduction to Reachability Verification         | 55 |

|   |             | 5.4.2                                  | Multiple Reachability Requirements             | 56 |

|   |             | 5.4.3                                  | Liquid Holding Tank                            | 58 |

|   | 5.5         | Summ                                   | ary                                            | 60 |

| 6 | For         | mal A                                  | nalysis of Large-Scale Control Systems         | 62 |

|   | 6.1         | Analy                                  | sis of Logical Control Systems                 | 62 |

|   | 6.2        | Discrete Logic in Chemical Plants                      |

|---|------------|--------------------------------------------------------|

|   |            | 6.2.1 Dynamics                                         |

|   |            | 6.2.2 Process-Independent Tests                        |

|   | 6.3        | Modeling PLC Programs                                  |

|   |            | 6.3.1 Translation to a Formal Model                    |

|   |            | 6.3.2 Function Blocks                                  |

|   | 6.4        | Formal Analysis                                        |

|   |            | 6.4.1 Abstraction as a Labeled Transition System       |

|   |            | 6.4.2 Verification                                     |

|   |            | 6.4.3 Falsification                                    |

|   | 6.5        | Mitigating the State-Explosion Problem                 |

|   |            | 6.5.1 Example: CIR Falsified after Simplification 85   |

|   | 6.6        | Case Study                                             |

|   | 6.7        | Summary                                                |

| 7 | st?s       | mv v0.1.0 90                                           |

| • | 7.1        | Modeling Logical Control Systems                       |

|   | 7.1<br>7.2 |                                                        |

|   |            | Translating Structured Text Control Code to a Model 91 |

|   | 7.3        | Example                                                |

|   | 7.4        | Summary                                                |

| 8 | Con        | clusions 97                                            |

|   | 8.1        | Contributions                                          |

|   | 8.2        | Recommendations for Future Work                        |

| Α | Mat        | thematical Background 108                              |

|   | A.1        | Hybrid Dynamical Systems                               |

|   | A.2        | Transition Systems   109                               |

|   | A.3        | Computation Tree Logic                                 |

|   | 11.0       | comparation rice police                                |

|     | A.3.1 Other Temporal Logics | 113 |

|-----|-----------------------------|-----|

| A.4 | Model Checking              | 113 |

| A.5 | Supervisory Control         | 115 |

# List of Figures

| 2.1 | The structure of a chemical plant control and automation system.         | 12 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | A liquid holding tank with high- and low-level indicators                | 13 |

| 2.3 | A simulation of the liquid holding tank, with overflow. $\ . \ . \ .$    | 16 |

| 0.1 |                                                                          | 00 |

| 3.1 | A specification with no optimal solution                                 | 23 |

| 3.2 | The maze from the cat and mouse problem. $\hdots \ldots \ldots \ldots$ . | 31 |

| 3.3 | Disabled transitions in the cat and mouse problem. $\ . \ . \ .$         | 32 |

| 3.4 | States that satisfy the specification in the cat and mouse problem.      | 33 |

|     |                                                                          |    |

| 4.1 | Implementation of the cat and mouse problem in $SynthSMV.$ .             | 42 |

| 4.2 | Implementation of the dining philosophers problem in ${\sf SynthSMV}.$   | 43 |

| 5.1 | A simulation of the modified liquid holding tank, without overflow.      | 61 |

| 0.1 | A simulation of the modified iquid folding tank, without overnow.        | 01 |

| 6.1 | Sequence between operating modes                                         | 75 |

| 6.2 | Operating mode sequence logic.                                           | 76 |

| 6.3 | Operating mode sequence diagram for a batch reaction                     | 81 |

|     |                                                                          |    |

| 7.1 | Structured Text program for the liquid holding tank example.             | 93 |

| 7.2 | SynthSMV model of the Structured Text program in Figure 7.1.             | 94 |

# List of Tables

| 2.1 | Variables in the liquid holding tank example                         | 15  |

|-----|----------------------------------------------------------------------|-----|

| 3.1 | Notation for transition systems                                      | 19  |

| 3.2 | Computing an optimal control policy for a single CTL operator.       | 21  |

| C 1 |                                                                      | CO  |

| 0.1 | Process-independent tests                                            | 68  |

| 6.2 | Mapping between model and Structured Text variable names.            | 83  |

| 6.3 | Overview of the case study problem size                              | 86  |

| 6.4 | Abstraction and runtime information from the case study              | 87  |

| 6.5 | PIT results from the case study                                      | 88  |

| 7.1 | Falsification results for the liquid holding tank example. $\ . \ .$ | 95  |

| A.1 | A subset of the CTL operators                                        | 112 |

## Chapter 1

### Introduction

#### **1.1** Control and Automation

Operation of a modern chemical plant involves a computer control system that performs control and automation tasks. The control system consists of all the logic that is required to operate the plant from startup, through operation, to shutdown. It also serves as the interface between the process and the operators, who monitor and guide the behavior of the plant to carry out tasks that cannot be automated. With modern control and automation systems, operators can complete complex tasks by providing relatively simple inputs, in a way that would otherwise be impossible. The control system then becomes a mission-critical component of the overall plant behavior, and if it fails, or its limitations are not respected, then the system will fail [Ste03]. A similar issue is discussed in a recent perspective, which advocates the viewpoint that the various elements that make up the overall system in a chemical plant are inextricably linked [LS13]. In light of these observations, any complete analysis of the operation of a chemical plant must address the interaction of the control system, the physical process, and the operators. The physical phenomena that drive chemical processes produce systems in which the variables evolve continuously as time passes. The implementation of a control system using digital computers produces a system in which the variables change instantaneously at discrete moments in time. The closed-loop system produced by applying discrete control to a continuous process is a hybrid (continuous/discrete) dynamical system, or hybrid system for short. Analysis of the overall behavior of a chemical plant, therefore, requires the analysis of the resulting hybrid system [Eng+00].

There are many (often competing) notions of correct operation of a chemical plant, ranging from operational constraints on the acceptable ranges of variables, to economic optimality conditions, and beyond. Any statement about the required, desired, intended, or expected behavior of the plant, including the process and the control system, can be seen as a (partial) specification of the overall correct behavior. From this point of view, if the system meets the specification, then it is (at least partially) correct, and if it does not meet the specification, then it is (again, at least partially) incorrect.

The continuous process dynamics in a chemical plant are essentially never known exactly; there is always uncertainty in the model or unmodeled disturbance. The discrete dynamics of the controller, on the other hand, are known exactly; it does what it was programmed to do. Even so, the complexity of a plant-wide control system, and the fact that its behavior is determined in part by its interaction with the (uncertain) process dynamics, makes the task of analyzing these known discrete dynamics difficult. This is an important problem when it comes to determining whether or not a given chemical plant will operate correctly.

### 1.2 Design

The obvious goal, given a model of the process dynamics and a specification of the desired closed-loop plant behavior, is to design a control system that enforces the specification. The development of algorithms to produce such correct-by-design control systems is an important research objective [GW00].

Unfortunately, the scale of a chemical plant (let alone an integrated chemical processing site) is beyond the reach of existing hybrid control design approaches [Eng+00]. Furthermore, it is not even clear how to specify everything that the system should (and should not) do, which is a prerequisite for designing the control logic. A control system that satisfies a partial specification of the overall desired plant behavior may not meet additional requirements that were not included in the partial specification.

### 1.3 Analysis

Because the full hybrid control system design problem is currently intractable for a chemical processing plant, much of the previous research in this area has focused on the associated analysis problem. In this problem, given an existing control system and a (partial) specification of the desired closed-loop behavior, the objective is to determine whether or not the system meets the specification. The analysis problem can be divided further into verification and falsification. In verification, the goal is to prove that the system meets the specification. Conversely, in falsification, the goal is to prove that the system does not meet the specification.

The analysis of hybrid systems amounts to solving the hybrid systems reachability problem. Given an initial state, a target state, and a model of the hybrid dynamics, the problem is to determine whether or not the system can reach the target state from the initial state. In general, the hybrid systems reachability problem is undecidable [Hen+98]. For certain classes of systems with restrictions placed on the form of the continuous dynamics, it is possible to either compute or approximate the set of reachable states. Some of these classes of hybrid systems (in order of increasing generality) are timed automata [LPY97; Yov97], linear hybrid automata[HHW97; Fre05], and piecewise-affine hybrid automata |Fre+11|; each class severely limits the direct application of the corresponding method to real systems. For systems with unrestricted continuous dynamics, the reachable set is approximated conservatively by solving a more restricted problem exactly [CK03; Col11]. These reachability approximations can be expensive to compute, so they are typically coupled with abstraction-based techniques. This gives rise to methods such as counterexample-guided abstraction refinement [Cla+03], in which a finite approximation of the hybrid system is iteratively refined to avoid unnecessary reachability approximations. For systems with complex discrete dynamics, such as plant control and automation systems, it is particularly important to only consider hybrid reachability problems when the discrete options have been exhausted [Seg07].

Much of the previous work in analyzing hybrid control systems in chemical plants has focused on verification [DSP97; Dim+96; Sri+98; Kow+99; KSB01; Bal+05]. The main issue with this approach is that currently it is not reasonable to require that every control system be verifiably correct, precisely because the design problem is intractable. Instead, systems are designed with the best available methods, including simulation and best practices, and put into operation. Thus, the implicit assumption is already that the system is correct, and verifying this correctness does not have any practical impact. Actionable results instead come from falsifying a specification; if the system is proven to not meet a given specification, then the control system should be modified. This is not a formal design algorithm, but is a step toward designing correct systems; first, any behavior that can be considered incorrect should be removed from existing systems.

Approaching the analysis problem in terms of falsification, instead of verification, necessitates identifying which classes of systems and specifications can be addressed algorithmically, and how those algorithms can be applied to large-scale systems like chemical plants. At a high level, falsification can be viewed as the opposite of verification. In this way, given a system and a specification that can be verified for that system, the negated form of the specification can be falsified. For obvious reasons, previous research in verification of hybrid systems focuses on classes of specifications of the desired system behavior that can be verified algorithmically. It is not necessarily true that those classes of specifications can be falsified efficiently. Therefore, at a lower level, it is important to treat falsification not only as the opposite of verification, but as a different technique, which applies to different types of specifications. Exploring the class of specifications that can be falsified can lead to specifications which address different aspects of plant operation than in previous work.

### 1.4 Outline

Chapter 2 introduces a model of the dynamics of a chemical process and its control system. The model is intended to be general enough to encompass the wide range of physical phenomena, and the common implementations of control systems, that appear in the chemical processing industry. At the same time, it should be specialized enough that there is an obvious correspondence between the model and the various components of the process and control system. The model is presented in the form of a hybrid dynamical system, and an example is used to demonstrate the modeling procedure. The model presented in Chapter 2 is the target of the analysis presented in the later chapters.

Chapter 3 presents results concerning supervisory control of discrete dynamical systems. The results relate to computing optimal supervisory control policies to enforce a class of specifications that includes multiple reachability requirements. Similar results have recently been reported in the literature for a single reachability requirement. Our results expand the previous results to multiple reachability requirements, which have also appeared in the literature in the context of supervisory control theory as multitasking supervisory control. We also show that the optimal control policy can be computed by solving a sequence of symbolic model checking problems. Chapter 4 describes the implementation of the methods presented in Chapter 3 in SynthSMV, which is an extension of the symbolic model checking solver NuSMV.

Chapter 5 describes a method for falsifying a class of specifications in hybrid systems. The systems of interest are represented by the model from Chapter 2, and the class of specifications is the same as in Chapter 3. An algorithm is presented and applied to a series of examples, including the example system from Chapter 2. The algorithm relies on the results from Chapter 3 to guarantee that the falsification results are sound.

Chapter 6 demonstrates how the results developed in the earlier chapters apply to chemical plant control and automation systems. This involves modeling the system as in Chapter 2, creating specifications of the desired system behavior that fit in the class of specifications from Chapter 3, and attempting to falsify those specifications by applying the algorithm from Chapter 5. In addition, the application of existing verification methods is explored in the context of falsification. A series of illustrative examples is presented, followed by computational results from an industrial case study which was provided by The Dow Chemical Company. Chapter 7 gives an overview of st2smv, which is a tool to apply the methods from Chapter 6 to control systems written in the Structured Text programming language for programmable logic controllers.

### Chapter 2

# Modeling a Plant: Process, Control, and Automation

#### 2.1 Comparison of Modeling Frameworks

Many frameworks exist that can be used to model hybrid dynamical systems, which combine continuous and discrete dynamics. Two notable examples are mixed logical dynamical (MLD) systems [BM99] and hybrid automata [Hen00].

MLD systems (and the equivalent classes of systems covered in [HDB01]) model discrete-time systems that involve linear dynamics and logical constraints. This modeling framework is notable because it has been successfully applied to a range of problems in the chemical processing industry, including verification [BTM01], control [DSL07], and supply chain optimization [MTA06]. In general, however, MLD systems do not capture the classes of systems that arise in the chemical processing industry. These systems usually involve continuous-time nonlinear dynamics, which are only approximated by MLD systems.

Hybrid automata provide a very general modeling framework for hybrid

systems. Informally, a hybrid automaton consists of a finite set of continuous variables and a finite set of logical modes, each of which describes the continuous dynamics of the system when it is in that mode, the conditions under which the system switches to a different mode, and the effect that switch has on the variables. One shortcoming of hybrid automata is that the logical modes are defined explicitly [BL02]. In a plant control system, the discrete mode is defined by the value assigned to each of a set of discrete variables. The discrete variables represent conditions such as whether or not a particular alarm is turned on in the control room, or which recipe is being executed in a reactor. The number of logical modes in the hybrid automaton model of such a system grows exponentially with the number of discrete variables, which is often on the order of hundreds to thousands in a chemical plant [Eng+00]; this makes it impractical to model the hybrid systems that arise in chemical plants as hybrid automata.

The modeling framework described in Section A.1 has rich enough descriptive capabilities to subsume MLD systems and hybrid automata [GST12]. In addition, it does not require the explicit enumeration of logical modes as in the case of hybrid automata, instead allowing the discrete state to be defined by a set of discrete state variables. For these reasons, we use systems that have the form (A.1) to model the dynamics of chemical plants.

In this chapter, we develop a model in the framework of (A.1) that is general enough to capture a large subset of the dynamical systems that arise in the control and automation of chemical plants. The model allows for nonlinear (and possibly uncertain) continuous process dynamics, and sample-and-hold control systems with both continuous and discrete variables.

### 2.2 Sample-and-Hold Control Systems

In a sample-and-hold control system (SHCS), a controller repeatedly (usually at a fixed frequency) performs the following steps:

- 1. The state of the plant is sampled.

- 2. Continuous and discrete control inputs are calculated.

- 3. The new inputs are applied to the plant.

- 4. The system evolves according to the process dynamics until the next sample.

In step 2, the continuous control inputs include values like valve positions, and discrete control inputs are logical values such as whether or not to activate a particular piece of equipment.

The system produced by an SHCS controlling a continuous chemical process is a hybrid dynamical system that can be modeled in the framework (A.1) as:

$$x = \begin{pmatrix} z \\ u \\ s \\ \tau \end{pmatrix} \in \mathbb{R}^{n_z} \times \mathbb{R}^{n_u} \times \{0, 1\}^{n_s} \times [0, T] =: X$$

$$F(x) = \begin{pmatrix} F_z(z, u) \\ 0 \\ 0 \\ 1 \end{pmatrix}$$

$$G(x) = \begin{pmatrix} F_z(z, u) \\ 0 \\ 1 \end{pmatrix}$$

$$G(x) = \begin{pmatrix} \left\{ \begin{pmatrix} u^+ \\ s^+ \end{pmatrix} \mid \exists r \in \rho(z) : u^+ \in G_u(z, s^+) \\ s^+ = g_s(r, s) \\ 0 \end{pmatrix}$$

$$D = \{x \in X \mid \tau = T\}$$

$$C = X \setminus D$$

$$(2.1)$$

#### where:

- z is a vector of continuous process state variables.

- u is a vector of continuous control inputs.

- *s* is a vector of discrete variables that describe the logical state of the system.

- $\tau$  is a timer variable that tracks the amount of time that has passed since the previous sample was taken.

- $F_z : \mathbb{R}^{n_z} \times \mathbb{R}^{n_u} \rightrightarrows \mathbb{R}^{n_z}$  represents the process dynamics.

- *u* and *s* are both 0 because the control variables only change value in discrete jumps when samples are taken.

- $z^+ = z$  because the plant is continuous.

- G<sub>u</sub>: ℝ<sup>n<sub>z</sub></sup> × {0,1}<sup>n<sub>s</sub></sup> ⇒ ℝ<sup>n<sub>u</sub></sup> is the feedback law, which may depend on the logical state of the system.

- $g_s: \{0,1\}^{n_r} \times \{0,1\}^{n_s} \to \{0,1\}^{n_s}$  is the discrete automation logic.

- $\rho : \mathbb{R}^{n_z} \rightrightarrows \{0, 1\}^{n_r}$  returns discrete readings from the plant.

- $\dot{\tau} = 1$  and  $\tau^+ = 0$  cause samples to occur every T time units.

- T is the sample time.

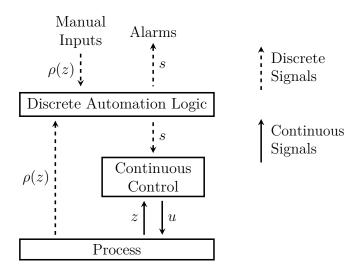

The elements in (2.1) fit into the layout of a plant as shown in Figure 2.1.

The set of possible initial states is restricted by  $X_0 \subseteq \{x \in X \mid \tau = 0\}$ . Because the underlying process is continuous, the jump set D is the set of points where the process state is sampled and the control inputs are updated (when  $\tau = T$ ). The flow set C is the remainder of the state space. When

Figure 2.1: The structure of a chemical plant control and automation system.

$x \in C$ , the continuous state of the plant evolves subject to  $\dot{z} \in F_z(z, u)$ , the timer increases subject to  $\dot{\tau} = 1$ , and u and s are held constant. When  $x \in D$ , the logical state of the control system is updated to  $s^+$ , new control inputs  $u^+$  are computed, and the timer is reset to 0. The actions of sampling the plant, computing  $s^+$  and  $u^+$ , applying the new values, and resetting the timer are modeled as instantaneous events, so the fact that the plant is continuous means that  $z^+ = z$ .

Modeling the process dynamics as a differential inclusion rather than a differential equation allows for uncertainty in the dynamics. If the process dynamics are known exactly, then the relationship reduces to the differential equation  $\dot{z} = f_z(z, u)$ . Similarly, modeling the continuous feedback law as a difference inclusion allows for uncertainty or indifference concerning the actual values computed by the controller. We do assume that the discrete logic is known exactly, so  $g_s$  is a function, not a set-valued map. The discrete jumps in the logical state of the plant, s, are still governed by a difference inclusion (not a difference equation), however, because there may be external inputs to the control logic that do not depend on the state. This behavior is contained in  $\rho$ .

For example, an operator may send a particular discrete signal (by pressing a button in the control room) at any time, regardless of the state of the plant, and the control system reacts accordingly.

Without loss of generality, we assume that all discrete variables are binary. To simplify notation involving discrete variables, we use "0" and "1" to represent the integer values 0 and 1 as well as the Boolean constants *false* and *true*, respectively. That is, for  $s \in \{0, 1\}^2$ , we treat the expressions  $s_1 + s_2 \ge 1$ and  $s_1 \lor s_2$  as being equivalent.

For set-valued maps and functions, we use uppercase letters to denote set-valued maps, and lowercase letters to denote functions. In the definition of a set-valued map, we will omit the bracket notation around sets that consist of a single element, i.e., the z that appears in the definition of G(x) in (2.1) is the set  $\{z\}$ .

### 2.3 Example: Liquid Holding Tank

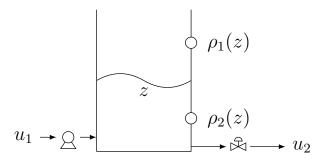

To demonstrate the model developed in this chapter, we now present an example of a simple process and control system. In the example, the process is a liquid holding tank, with inlet and outlet flows determined by upstream and downstream requirements. The tank is shown in Figure 2.2.

Figure 2.2: A liquid holding tank with high- and low-level indicators.

The state and dynamics are modeled by the system:

$$x = (z, u_{1}, u_{2}, s_{1}, s_{2}, s_{3}, s_{4}, s_{5}, s_{6}, \tau)^{\mathsf{T}} \in \mathbb{R} \times \mathbb{R}^{2} \times \{0, 1\}^{6} \times [0, 1] =: X$$

$$f(x) = \begin{pmatrix} u_{1} - u_{2} \\ 0 \\ 0 \\ 1 \end{pmatrix}$$

$$G(x) = \begin{pmatrix} \left\{ \begin{pmatrix} u^{+} \\ s^{+} \end{pmatrix} \middle| \\ \exists r \in \rho(z) : \begin{array}{c} z \\ s_{2}^{+} = \neg s_{6} \land r_{2} \\ s_{3}^{+} = s_{1}^{+} \lor (s_{3} \land r_{1}) \\ s_{4}^{+} = s_{2}^{+} \lor (s_{4} \land r_{2}) \\ s_{5}^{+} = (s_{1}^{+} \land r_{3}) \lor s_{5} \\ s_{6}^{+} = (s_{2}^{+} \land r_{4}) \lor (s_{6} \land r_{2}) \\ 0 \end{pmatrix}$$

$$\rho(z) = \begin{pmatrix} z > 8 \\ z < 2 \\ \{0, 1\} \\ \{0, 1\} \end{pmatrix}$$

$$D = \{x \in X \mid \tau = 1\}$$

$$C = X \setminus D$$

with the variables and parameters listed in Table 2.1. The initial state is  $x_0 = (5, \mathbf{0}^{\mathsf{T}}, \mathbf{0}^{\mathsf{T}}, \mathbf{0})^{\mathsf{T}}$ . Note that even in this small example, the 6 discrete state variables would produce 64 discrete locations in a hybrid automaton model.

The minimum and maximum liquid levels that the tank can accommodate are 0 and 10, respectively; if the level reaches 0, then underflow occurs, and if it reaches 10, then overflow occurs. The flow rates into and out of the tank (inputs  $u_1$  and  $u_2$ ) are dictated by (unmodeled) upstream and downstream requirements, so  $u^+ \in G_u$  is left as a difference inclusion. In order to prevent overflow or underflow, the controller includes alarms and logic to set the appropriate input to 0 in response to high or low level measurements. The

|          | <u>i</u>                    |

|----------|-----------------------------|

| Variable | Description                 |

| z        | Liquid level                |

| $u_1$    | Inlet flow rate             |

| $u_2$    | Outlet flow rate            |

| $s_1$    | High-level alarm            |

| $s_2$    | Low-level alarm             |

| $s_3$    | Inlet flow lock             |

| $s_4$    | Outlet flow lock            |

| $s_5$    | High-level acknowledgement  |

| $s_6$    | Low-level acknowledgement   |

| $ ho_1$  | High-level indicator        |

| $ ho_2$  | Low-level indicator         |

| $ ho_3$  | Operator: acknowledge $s_1$ |

| $ ho_4$  | Operator: acknowledge $s_2$ |

Table 2.1: Variables in the liquid holding tank example.

objective is that the tank can be filled and emptied as necessary, subject to the requirement that the liquid level stay within the acceptable operating range.

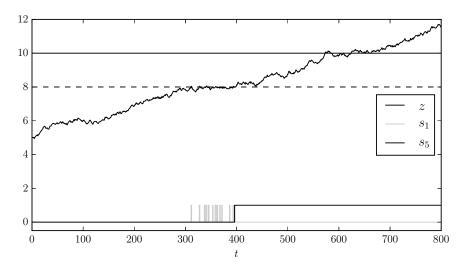

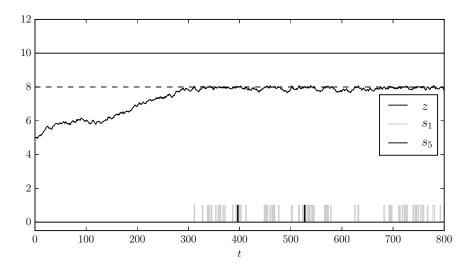

A simulation of the system dynamics is shown in Figure 2.3. In the simulation, the tank overflows before t = 700. While the simulation does indicate that the control system contains a flaw, it does not indicate what the flaw is. Furthermore, there is no guarantee that simulating a finite number of different trajectories would have uncovered this behavior. Analysis of the system dynamics is required to determine what led to overflow.

#### 2.4 Summary

In this chapter, we have introduced a model that captures the dynamics of a continuous process interacting with a sample-and-hold control system that includes discrete logic. The modeling framework, taken from [GST12], avoids some of the shortcomings of other popular approaches, including MLD systems and hybrid automata, while still allowing for a compact representation of the dynamics. An example was included to demonstrate the class of systems that

Figure 2.3: A simulation of the liquid holding tank, with overflow.

can be modeled as (2.1), and to motivate the formal analysis of such systems to uncover flaws in the control logic.

## Chapter 3

# Supervisory Control with Multiple Reachability Specifications

### 3.1 Control of Discrete Systems

The classical development of supervisory control theory for discrete event systems is based on automata and formal languages, as described in Section A.5. In particular, the system is modeled as a deterministic finite automaton, a superset of the desired system behavior is specified as a formal language, and a single set of states (the so-called marked states) is designated that should always remain reachable. One issue with this approach is that it is often more convenient to specify the behavior of a system using temporal logic such as computation tree logic (CTL), which is described in Section A.3. Another (more fundamental) issue is that only allowing a single set of marked states precludes enforcing the reachability of multiple (disjoint) sets of states simultaneously.

The use of temporal logic specifications has been investigated as an alter-

native to formal languages [ZS05; JK06; GPT06; Ehl+16]. The most general methods address supervisory control subject to CTL\* specifications, but they do not address whether or not the supervisors are maximally permissive or unique [ZS05; JK06]. The work that addresses permissiveness of the controller only applies to more restricted classes of specifications, such as invariance specifications [GPT06] or specifications with a single set of states that should be reachable [Ehl+16].

Other work has focused on the problem of specifying multiple reachability requirements. It has been shown that a system with multiple sets of marked states (modeled by a "colored marking generator") can be addressed by an extension of the classical theory to compute a maximally-permissive supervisor that enforces multiple reachability requirements. This is called multitasking supervisory control [dCW05]. The downside is that the results are limited to automata-based models and formal language specifications.

In addition to work concerning how the desired system behavior is specified, the way in which supervisors are implemented has also been investigated. It has been shown that instead of dynamic supervisors (as described in Section A.5), it suffices to consider control policies that only depend on the current state of the system [Len+14; Ehl+16]. Work in this area has also focused on formal language specifications.

In this chapter, we show how to compute a maximally-permissive statebased control policy for a finite transition systems to enforce a class of CTL specifications with combined invariance and reachability requirements. We address multiple reachability requirements, which is similar to the strong nonblocking requirement of multitasking supervisory control. The algorithm we develop relies on symbolic model checking for the computation.

### **3.2** Finite Transition Systems

The systems we consider are modeled by finite transition systems,  $\mathcal{T} = (Q, \Delta)$ , as in (A.2). See Table 3.1 for a description of the notation used. A system  $\mathcal{T}$ begins in an initial state  $q_0 \in Q_0$ , where  $Q_0 \subseteq Q$ . The system evolves by making a sequence of transitions, where each transition has the form  $(q, q^+) \in \Delta$ , which indicates that the system moves from state q to state  $q^+$ . These discrete changes in the system state occur instantaneously, with the only concept of time being the order in which the transitions occur.

| Table 3.1: Notation for transition systems.  |                                                          |  |

|----------------------------------------------|----------------------------------------------------------|--|

| Symbol                                       | Meaning                                                  |  |

| $\mathcal{T} = (Q, \Delta)$                  | Finite transition system                                 |  |

| Q                                            | Set of states                                            |  |

| $\Delta \subseteq Q \times Q$                | Set of transitions                                       |  |

| $\Delta_c \subseteq \Delta$                  | Set of controllable transitions                          |  |

| $\Delta_d \subseteq \Delta_c$                | Set of disabled transitions                              |  |

| $\theta$                                     | CTL specification                                        |  |

| $\llbracket \theta \rrbracket_{\mathcal{T}}$ | The set of states in $\mathcal{T}$ that satisfy $\theta$ |  |

Specifications about a transition system describe its behavior as it moves from state to state. We address specifications written in computation tree logic (CTL). These specifications involve properties such as invariance (AG) and reachability (EF) of particular sets of states in the system. The most basic properties of states are given by atomic propositions. Without loss of generality, we assume that the state is defined by a vector of state variables, and that the atomic propositions are relational expressions involving those state variables, as in Section A.3. The atomic propositions are intrinsic properties of the individual states, and therefore are not affected by the transition relation,  $\Delta$ . The CTL operators listed in Table A.1 are, however, affected by the transitions and paths that exist in the system.

Analysis of transition systems using model checking is described in Sec-

tion A.4. The model checking algorithm accepts the model of a system  $\mathcal{T} = (Q, \Delta)$  and a specification  $\theta$ , and returns the set of states in  $\mathcal{T}$  that satisfy  $\theta$ , written  $\llbracket \theta \rrbracket_{\mathcal{T}}$  as in Table 3.1. Given a set of initial states  $Q_0 \subseteq Q$ , if  $Q_0 \subseteq \llbracket \theta \rrbracket_{\mathcal{T}}$ , then  $\mathcal{T}$  itself satisfies  $\theta$ . For CTL specifications (including those we consider in this chapter), symbolic model checking algorithms exist to efficiently solve model checking problems for large systems.

#### **3.3** Supervisor Synthesis via Model Checking

If some subset of a system's transitions,  $\Delta_c \subseteq \Delta$ , can be disabled, then it may be possible to alter the system's behavior (by disabling some of those transitions) so that it satisfies a specification. This gives rise to a control problem for transition systems. Given a system  $\mathcal{T} = (Q, \Delta)$  with controllable transitions  $\Delta_c \subseteq \Delta$  and a specification  $\theta$ , the control problem is to determine which of the controllable transitions in  $\Delta_c$  need to be disabled so that  $\mathcal{T}_d$  satisfies  $\theta$ , where  $\mathcal{T}_d \coloneqq (Q, \Delta \setminus \Delta_d)$  and  $\Delta_d \subseteq \Delta_c$  is the set of disabled transitions.

Certain types of solutions to the control problem are particularly interesting. First, it is usually important to maximize (in terms of set inclusion) the set of states that satisfy the specification in the controlled system,  $\llbracket \theta \rrbracket_{\mathcal{T}_d}$ . As a secondary objective, it is also desirable to minimize (in terms of set inclusion) the set of disabled transitions,  $\Delta_d$ . In this section, we address both objectives.

#### 3.3.1 Individual CTL Operators

For a CTL specification that consists of a single CTL operator (along with arbitrary atomic propositions and Boolean operators), the approaches listed in Table 3.2 can be used to calculate a control policy that maximizes  $\llbracket \theta \rrbracket_{\mathcal{T}_d}$ . No transitions should be disabled to satisfy a specification that only involves reachability (EF). In fact, disabling transitions may remove states from  $\|\theta\|_{\mathcal{T}_d}$ that would otherwise be included in  $\|\theta\|_{\mathcal{T}}$ . For specifications involving invariance (AG), some transitions may need to be disabled so that all the remaining reachable states satisfy the invariant property. These strategies are supported by Lemmas 3.1 and 3.2.

Table 3.2: Computing an optimal control policy for a single CTL operator. Operator Strategy EF Do not disable any transitions. Initially, disable all controllable transitions  $(\Delta_d = \Delta_c)$ . AG After calculating  $\llbracket \theta \rrbracket_{(Q,\Delta \setminus \Delta_d)}$ , enable all transitions *except*

$\left\{ (q,q^+) \in \Delta_c \mid q \in \llbracket \theta \rrbracket_{(Q,\Delta \setminus \Delta_d)} \land q^+ \notin \llbracket \theta \rrbracket_{(Q,\Delta \setminus \Delta_d)} \right\}.$

**Lemma 3.1** (disabled transitions and reachability). If  $\Delta \subseteq \Delta'$ , then  $\llbracket \mathsf{EF}(p) \rrbracket_{\mathcal{T}} \subseteq$  $\llbracket \mathsf{EF}(p) \rrbracket_{\mathcal{T}'}, \text{ where } \mathcal{T} = (Q, \Delta) \text{ and } \mathcal{T}' = (Q, \Delta').$

*Proof.* The more transitions there are available, the more paths there will be leading to a state that satisfies p.  $[[\mathsf{EF}(p)]]_{\mathcal{T}}$  is the least fixed point of the monotonic function  $f(Z) = \llbracket p \rrbracket_{\mathcal{T}} \cup \llbracket \mathsf{EX}(Z) \rrbracket_{\mathcal{T}}$ , where  $\llbracket \mathsf{EX}(Z) \rrbracket_{(Q,\Delta)} \coloneqq$  $\{q \in Q \mid \exists (q,q^+) \in \Delta : q^+ \in Z\}$ . Let f' be a similar function that depends on  $\Delta'$  instead of  $\Delta$ , so that  $\llbracket \mathsf{EF}(p) \rrbracket_{\mathcal{T}'}$  is the least fixed point of f'.

$\Delta \subseteq \Delta' \implies [\![\mathsf{EX}(Z)]\!]_{\mathcal{T}} \subseteq [\![\mathsf{EX}(Z)]\!]_{\mathcal{T}'}, \text{ therefore } f(Z) \subseteq f'(Z). \text{ Both least}$ fixed point calculations are initiated at  $Z_0 = Z_0' = \emptyset$ , so  $f(Z_0) \subseteq f'(Z_0')$ . From the monotonicity of f and  $f', Z_i \subseteq Z_i' \implies f(Z_i) \subseteq f(Z_i')$ , and because  $f(Z_i) \subseteq f'(Z_i)$ , it follows that  $f(Z_i) \subseteq f'(Z_i)$ .

In the fixed point calculations,  $Z_{i+1} = f(Z_i)$  and  $Z_{i+1}' = f'(Z_i')$ , so  $Z_i \subseteq Z_i' \implies Z_{i+1} \subseteq Z_{i+1}'$ . This means  $Z_i \subseteq Z_i' \ \forall i$ , therefore  $\llbracket \mathsf{EF}(Z) \rrbracket_{\mathcal{T}} \subseteq$  $\llbracket \mathsf{EF}(Z) \rrbracket_{\mathcal{T}'}.$

**Lemma 3.2** (disabled transitions and invariance). If  $\Delta \subseteq \Delta'$ , then  $[\![\mathsf{AG}(p)]\!]_{\mathcal{T}} \supseteq$  $\llbracket \mathsf{AG}(p) \rrbracket_{\mathcal{T}'}, \text{ where } \mathcal{T} = (Q, \Delta) \text{ and } \mathcal{T}' = (Q, \Delta').$

*Proof.* AG and EF are logical duals, i.e.,  $AG(p) \iff \neg EF(\neg p)$ . Therefore,  $\llbracket AG(p) \rrbracket_{\mathcal{T}} \equiv Q \setminus \llbracket EF(p) \rrbracket_{\mathcal{T}}$  and  $\llbracket AG(p) \rrbracket_{\mathcal{T}'} \equiv Q \setminus \llbracket EF(p) \rrbracket_{\mathcal{T}'}$ . From Lemma 3.1,  $\Delta \subseteq \Delta' \implies \llbracket EF(p) \rrbracket_{\mathcal{T}} \subseteq \llbracket EF(p) \rrbracket_{\mathcal{T}'}$ , so  $\llbracket AG(p) \rrbracket_{\mathcal{T}} \supseteq \llbracket AG(p) \rrbracket_{\mathcal{T}'}$ .

In addition to maximizing  $\llbracket \theta \rrbracket_{\mathcal{T}_d}$ , the strategies in Table 3.2 return the minimal set of disabled transitions,  $\Delta_d$ , that achieves this primary objective. In the case of reachability (EF) this is obviously true, because no transitions are disabled. The case of invariance (AG) is addressed in Theorem 3.3. Because the strategies meet both objectives regarding the control policy, we say they compute optimal solutions to the supervisory control problem, or optimal control policies. In both cases, the existence of an optimal control policy depends only on the form of the specification, not on the system to be controlled.

**Theorem 3.3** (optimal control with invariance requirements). The strategy listed in Table 3.2 computes the minimal set of disabled transitions required to maximize the set of states that satisfy a specification of the form AG(p), where p does not include any additional CTL operators.

Proof. From Lemma 3.2, initially disabling all transitions in  $\Delta_c$  will maximize the set of states included in  $[\![\mathsf{AG}(p)]\!]_{\mathcal{T}_d}$ . Enabling any transition  $(q, q^+) \in \Delta_c$ , where  $q \in [\![\theta]\!]_{\mathcal{T}_d}$  and  $q^+ \notin [\![\theta]\!]_{\mathcal{T}_d}$ , would exclude q from  $[\![\mathsf{AG}(p)]\!]_{\mathcal{T}_d}$ . Therefore, those transitions must remain disabled to maximize the set. All other transitions in  $\Delta_c$  can be enabled without excluding any states from that satisfying set, which results in the minimal set of disabled transitions that yields the maximal set of states satisfying the specification.  $\Box$

#### 3.3.2 Multiple CTL Operators

When multiple CTL operators appear in the specification, they are linked through the set of disabled transitions, and this interaction needs to be accounted for. For example, from Table 3.2, the CTL operators AG and EF require opposite control strategies to maximize the respective sets of satisfying states. The opposing strategies come from the opposite effect of disabling a transition, described in Lemmas 3.1 and 3.2.

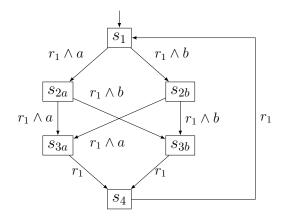

Simply fixing  $\Delta_d$  and calculating  $\llbracket \theta \rrbracket_{\mathcal{T}_d}$  as an ordinary model checking problem for each of the  $2^{|\Delta_c|}$  possible control policies is one way to address the interaction, but this approach is not useful for any but the smallest systems. More importantly, whether or not an optimal control policy even exists depends on the specification,  $\theta$ . For example, Figure 3.1 shows a system with a single state variable  $q \in \{1, 2, 3\}$  in which the specification

$$\mathsf{EF}(\mathsf{AG}((q=1) \lor (q=2))) \land \mathsf{EF}(q=3)$$

does not have an optimal solution. Either of the states (q = 1) or (q = 2), but not both, can be made to satisfy the specification, depending on the control policy. Without additional information or requirements, it is impossible to determine which solution (if either) is better. In light of this difficulty, it is important to determine (for a given specification and system) whether or not there exists an optimal solution.

Figure 3.1: The specification  $\theta = \mathsf{EF}(\mathsf{AG}((q = 1) \lor (q = 2))) \land \mathsf{EF}(q = 3)$  does not have an optimal solution. The first diagram shows the uncontrolled system, where dashed edges represent controllable transitions. In the two potential solutions, states shown in black satisfy the specification, while those shown in gray do not. Gray edges are disabled transitions, and black edges are enabled transitions.

A specification AG(EF(p)), where p does not contain any CTL operators, can express the controllability and nonblocking requirements of classical supervisory control theory, and therefore corresponds to an optimal control policy [Ehl+16]. In light of multitasking supervisory control [dCW05], with multiple sets that should always be reachable, we consider specifications of the form:

$$\mathsf{AG}\left(\bigwedge_{I} p_{i} \wedge \bigwedge_{J} \mathsf{EF}\left(p_{j}\right)\right) \tag{3.1}$$

where the  $p_i$  and  $p_j$  do not contain any CTL operators. We refer to specifications that can be written in the form (3.1) as *combined invariance and reachability* (CIR) specifications. Because these specifications combine multiple CTL operators, the methods in Table 3.2 do not apply directly, and it is necessary to determine whether or not such a specification admits an optimal control policy.

In a formula that involves multiple CTL operators, the interaction between those CTL operators might be managed by first disabling transitions as in Table 3.2 for each subformula, and then checking what effect that has on the other subformulas. This idea leads to the following approach:

- 1. For each CTL operator, starting with the innermost subformula and working outward, follow the approach in Table 3.2, and record the sets of satisfying states and disabled transitions.

- 2. After the outermost formula, remove from the system every transition that was disabled while processing any of the subformulas.

- 3. Using the updated system, return to the innermost subformula and repeat the process until no further transitions are disabled.

Algorithm 3.1 applies this approach for CIR specifications.

Algorithm 3.1: Optimal control for CIR specifications.

$\begin{aligned} \mathbf{Input} &: \text{Finite transition system } \mathcal{T} = (Q, \Delta) \text{ with controllable} \\ & \text{transitions } \Delta_c \subseteq \Delta \text{ and } \mathsf{CIR specification} \\ \theta &= \mathsf{AG}\left(\bigwedge_I p_i \land \bigwedge_J \mathsf{EF}(p_j)\right) \\ \mathbf{Output} : \Delta_d \subseteq \Delta_c, \text{ the minimal set of disabled transitions that} \\ & \text{maximizes } \llbracket \theta \rrbracket_{(Q,\Delta \setminus \Delta_d)} \\ \theta_{in} \leftarrow \bigwedge_I p_i \land \bigwedge_J \mathsf{EF}(p_j) \\ \Delta_d^0 \leftarrow \emptyset \\ \Delta^0 \leftarrow \Delta \\ \mathcal{T}^0 \leftarrow \mathcal{T} \\ k \leftarrow 0 \\ \mathbf{repeat} \\ & k \leftarrow k+1 \\ & Z_{in}{}^k \leftarrow \llbracket \theta_{in} \rrbracket_{\mathcal{T}^{k-1}} \\ & Z^k \leftarrow \llbracket \mathsf{AG}(Z_{in}{}^k) \rrbracket_{(Q,\Delta \setminus \Delta_c)} \\ \Delta_d^k \leftarrow \left\{ (q,q^+) \in \Delta_c \ \middle| \ q \in Z^k \land q^+ \notin Z^k \right\} \\ & \Delta^k \leftarrow \Delta^{k-1} \setminus \Delta_d{}^k \\ & \mathcal{T}^k \leftarrow (Q,\Delta^k) \\ \mathbf{until } \Delta^k = \Delta^{k-1} \\ & \Delta_d \leftarrow \Delta_d{}^k \\ & \mathbf{return } \Delta_d \end{aligned}$

**Theorem 3.4** (optimal control with invariance and reachability requirements). Algorithm 3.1 computes the minimal set of disabled transitions that maximizes the set of states that satisfy the specification if the  $p_i$  and  $p_j$  do not include any additional CTL operators.

Proof. Let  $Z^*$  be the maximal set of states (if it exists) that can satisfy  $\theta$  in the controlled system, let  $\Delta_d^* \subseteq \Delta_c$  be the minimal set of disabled transitions (if it exists) such that  $\llbracket \theta \rrbracket_{\mathcal{T}^*} = Z^*$ , where  $\mathcal{T}^* := (Q, \Delta \setminus \Delta_d^*)$ , and let  $Z_{in}^*$  be  $\llbracket \theta_{in} \rrbracket_{\mathcal{T}^*}$ . Because  $\Delta_d^*$  is the minimal set of disabled transitions,  $Z_{in}^*$  is the maximal set of states (from Lemma 3.1) that can satisfy  $\theta_{in}$ , subject to the requirement that  $Z^*$  be maximized.

First, show (by induction on k) that  $Z_{in}^{k} \supseteq Z_{in}^{*}$  in Algorithm 3.1. For the base case (k = 1),  $Z_{in}^{1} = \llbracket \theta_{in} \rrbracket_{(Q,\Delta)} \supseteq \llbracket \theta_{in} \rrbracket_{(Q,\Delta \setminus \Delta_{d}^{*})} = Z_{in}^{*}$ , from Lemma 3.1. For the inductive step, assume that, in iteration  $k, Z_{in}^{k} \supseteq Z_{in}^{*}$ . From the monotonicity of AG,  $Z^{k} = \llbracket AG(Z_{in}^{k}) \rrbracket_{(Q,\Delta \setminus \Delta_{c})} \supseteq \llbracket AG(Z_{in}^{*}) \rrbracket_{(Q,\Delta \setminus \Delta_{c})}$ . From Lemma 3.2,  $\llbracket AG(Z_{in}^{*}) \rrbracket_{(Q,\Delta \setminus \Delta_{c})} \supseteq \llbracket AG(Z_{in}^{*}) \rrbracket_{\mathcal{T}^{*}} = Z^{*}$ . Therefore,  $Z^{k} \supseteq Z^{*}$ , so  $\forall (q, q^{+}) \in \Delta_{d}^{k} : q^{+} \notin Z^{*}$ . As a result,  $(Z_{in}^{k} \setminus Z_{in}^{k+1}) \cap Z_{in}^{*} = \emptyset$ . Consider  $q_{in} \in (Z_{in}^{k} \setminus Z_{in}^{k+1}); q_{in}$  was prevented from satisfying  $\theta_{in}$  because a controllable transition  $(q, q^{+})$  was disabled, where  $q^{+} \notin Z^{*}$ . If  $q_{in} \in Z_{in}^{*}$ , then q is reachable from  $q_{in}$  in  $\mathcal{T}^{*}$ , so the transition  $(q, q^{+})$  must be disabled to maximize  $Z^{*}$ (because otherwise  $q \notin Z^{*}$ ). However, disabling  $(q, q^{+})$  causes  $q_{in}$  to not satisfy  $\theta_{in}$ , so  $q_{in} \notin Z_{in}^{*}$ , a contradiction. Therefore,  $\forall q_{in} \in (Z_{in}^{k} \setminus Z_{in}^{k+1}) : q_{in} \notin Z_{in}^{*}$ . Thus,  $Z_{in}^{k+1} \supseteq Z_{in}^{*}$ . This concludes the proof by induction.

Then, from  $Z_{in}{}^{k} \supseteq Z_{in}{}^{*}$ , along with the monotonicity of AG and Lemma 3.2 (as before, in the inductive step),  $Z^{k} \supseteq Z^{*}$  in Algorithm 3.1. In the final iteration, K, no new transitions are disabled, so  $Z^{K} = \llbracket \theta \rrbracket_{\mathcal{T}^{K}}$ . Therefore, the upper bound is indeed realized, and  $Z^{K} \equiv Z^{*}$ . From Theorem 3.3,  $\Delta_{d}{}^{K} \equiv \Delta_{d}{}^{*}$ . **Corollary 3.5** (termination). Algorithm 3.1 terminates after no more than  $\min \{|Q|, |\Delta_c|\}$  iterations.

Proof. Both  $Z^k$  and  $\Delta^k$  are finite sets that decrease monotonically from one iteration to the next, and the algorithm terminates when they stop decreasing. At most  $|\Delta_c|$  transitions can be removed from  $\Delta^k$ , and at most |Q| states can be removed from  $Z^k$ , so Algorithm 3.1 will terminate after at most min  $\{|Q|, |\Delta_c|\}$ iterations.

These results show that a CIR specification (3.1), that combines multiple invariance and reachability requirements, corresponds to an optimal control policy, regardless of the system. This makes it possible to check whether or not a given system can be made to satisfy such a specification by first computing the optimal control policy, and then checking whether or not  $Q_0 \subseteq \llbracket \theta \rrbracket_{\mathcal{T}^*}$ .

As the iterations in Algorithm 3.1 are carried out, the "largest" model (in terms of the number of states and transitions) that is checked is the uncontrolled system itself. After each iteration, transitions are removed from  $\Delta$ , so that in future iterations model checking is applied to a system which is "smaller" than the uncontrolled system. These notions of system size only apply directly to the explicit representation of the system; a symbolic representation using binary decision diagrams (BDDs) may decrease or increase in size as transitions are disabled, depending on the structure of the system and the variable ordering.

## 3.4 Labeled Transition Systems

We now show how the results in Section 3.3 apply to discrete event systems with controllable events, modeled as deterministic finite labeled transitions systems (LTSs) as in (A.3). In [Ehl+16], the authors show that the standard supervisory control problem can be reduced to a simpler problem that only involves reachability (a nonblocking requirement). Furthermore, they show that the simpler problem has a solution in the form of a unique, maximallypermissive, state-based supervisor (if any solution exists).

**Definition 3.6** (state-based supervisor). Given an LTS  $\mathcal{L} = (Q, \Sigma, \Delta)$  with controllable events  $\Sigma_c \subseteq \Sigma$ , then a *state-based supervisor* is a set-valued map

$$\Gamma: Q \rightrightarrows \Sigma$$

where  $\Gamma(q)$  is the set of events which are enabled in state q.  $\Gamma$  cannot disable uncontrollable events, so  $\forall q \in Q : (\Sigma \setminus \Sigma_c) \subseteq \Gamma(q)$ .

The closed-loop system produced by a state-based supervisor  $\Gamma$  controlling an LTS  $\mathcal{L}$  is

$$\Gamma/\mathcal{L} = (Q, \Sigma, \Delta')$$

where

$$\Delta' \coloneqq \left\{ (q, \sigma, q^+) \in \Delta \mid \sigma \in \Gamma(q) \right\}$$

That is, the supervisor removes the transitions that are caused by disabled events, and the system is otherwise unchanged.

**Definition 3.7** (permissiveness). Given the state-based supervisors  $\Gamma : Q \rightrightarrows \Sigma$ and  $\Gamma' : Q \rightrightarrows \Sigma$ ,  $\Gamma$  is not less permissive than  $\Gamma'$  if  $\forall q \in Q : \Gamma(q) \supseteq \Gamma'(q)$ . If  $\Gamma$ is not less permissive than  $\Gamma'$  and, in addition,  $\exists q \in Q : \Gamma(q) \supset \Gamma'(q)$ , then  $\Gamma$  is more permissive than  $\Gamma'$ .

**Definition 3.8** (maximally-permissive supervisor). For an LTS  $\mathcal{L}$  and a specification  $\theta$ ,  $\Gamma : Q \rightrightarrows \Sigma$  is the maximally-permissive supervisor that enforces  $\theta$  in  $\mathcal{L}$  if and only if  $\Gamma/\mathcal{L}$  satisfies  $\theta$ , and there does not exist a more permissive supervisor  $\Gamma' : Q \rightrightarrows \Sigma$  such that  $\Gamma'/\mathcal{L}$  satisfies  $\theta$ .

To convert from an LTS  $\mathcal{L} = (Q, \Sigma, \Delta_{\mathcal{L}})$  with controllable events  $\Sigma_c \subseteq \Sigma$ to a TS  $\mathcal{T} = (Q, \Delta)$  with controllable transitions  $\Delta_c \subseteq \Delta$ , apply the following:

$$\Delta = \{ (q, q^+) \mid \exists \sigma \in \Sigma : (q, \sigma, q^+) \in \Delta_{\mathcal{L}} \}$$

$$\Delta_c = \{ (q, q^+) \mid \forall \sigma \in \Sigma : (q, \sigma, q^+) \in \Delta_{\mathcal{L}} \implies \sigma \in \Sigma_c \}$$

The sets of states and initial states are the same in both systems. The set of unlabeled transitions,  $\Delta$ , is the set of all labeled transitions that exist in  $\mathcal{L}$ , with the label removed. The set of controllable transitions,  $\Delta_c$ , is the subset of  $\Delta$  for which every corresponding labeled transition in  $\mathcal{L}$  is labeled by a controllable event. Because the states are the same in both systems, the atomic propositions (which are relational expressions involving the state variables) are also the same.

To convert from a set of disabled transitions  $\Delta_d \subseteq \Delta_c$  to a state-based supervisor  $\Gamma : Q \Longrightarrow \Sigma$ , apply the following:

$$\Gamma = q \mapsto \left\{ \sigma \in \Sigma \ \left| \ \nexists q^+ \in Q : (q, q^+) \in \Delta_d \land (q, \sigma, q^+) \in \Delta_{\mathcal{L}} \right\} \right\}$$

The enabled events in each state are all the events such that the corresponding transition in  $\mathcal{T}$  is not in the set of disabled transitions,  $\Delta_d$ .

The key result we take from Section 3.3 is that, given a finite deterministic LTS  $\mathcal{L} = (Q, \Sigma, \Delta_{\mathcal{L}})$  with controllable events  $\Sigma_c \subseteq \Sigma$  and a CIR specification  $\theta = \mathsf{AG}\left(\bigwedge_I p_i \land \bigwedge_J \mathsf{EF}(p_j)\right)$  as in (3.1), it is possible to compute the maximallypermissive state-based supervisor that maximizes the set of states in  $\mathcal{L}$  that satisfy  $\theta$ . This is done by first converting  $\mathcal{L}$  to the TS  $\mathcal{T}$ , then applying Algorithm 3.1 to compute the minimal set of disabled transitions to enforce  $\theta$  in  $\mathcal{T}$ , and finally converting the result back to a state-based supervisor  $\Gamma$ . Because  $\mathcal{L}$  is finite,  $\mathcal{T}$  is also finite, and Algorithm 3.1 can be applied. Because  $\mathcal{L}$  is deterministic, the resulting set of disabled transitions can be implemented as a state-based supervisor. This procedure is formalized in Algorithm 3.2.

### Algorithm 3.2: Optimal state-based supervisor synthesis. Input : LTS $\mathcal{L} = (Q, \Sigma, \Delta_{\mathcal{L}})$ , controllable events $\Sigma_c \subseteq \Sigma$ , and CIR specification $\theta = \mathsf{AG}\left(\bigwedge_I p_i \land \bigwedge_J \mathsf{EF}(p_j)\right)$ Output: Γ, the maximally-permissive state-based supervisor that maximizes the set of states in $\mathcal{L}$ that satisfy $\theta$ $\Delta \leftarrow \{(q, q^+) \mid \exists \sigma \in \Sigma : (q, \sigma, q^+) \in \Delta_{\mathcal{L}}\}$ $\mathcal{T} \leftarrow (Q, \Delta)$ $\Delta_c \leftarrow \{(q, q^+) \mid \forall \sigma \in \Sigma : (q, \sigma, q^+) \in \Delta_{\mathcal{L}} \implies \sigma \in \Sigma_c\}$ $\Delta_d \leftarrow \text{Apply Algorithm 3.1 to } (\mathcal{T}, \Delta_c, \theta)$ $\Gamma \leftarrow q \mapsto \{\sigma \in \Sigma \mid \nexists q^+ \in Q : (q, q^+) \in \Delta_d \land (q, \sigma, q^+) \in \Delta_{\mathcal{L}}\}$ return Γ

# 3.5 Example

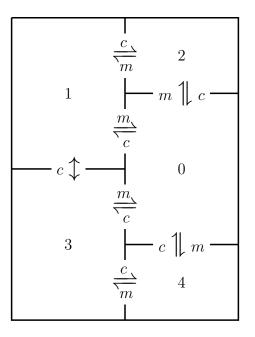

The classic cat and mouse problem [RW89] is an example of a system with a single reachability requirement. In the problem, a cat and mouse are placed in a maze, shown in Figure 3.2. The cat and mouse are initially placed in separate rooms (2 and 4, respectively). Adjacent rooms are connected by doors through which the cat or mouse can move. The cat and mouse can pass through the doors only in the directions indicated in Figure 3.2. Each door can be opened or closed depending on the current rooms occupied by the cat and mouse, except the cat's door between rooms 1 and 3, which is always open. Either the cat or the mouse may move in a given turn, but not both. The invariance requirement is that the cat and mouse should never be in the same room, and the reachability requirement is that they should always be able to return to their original rooms. The control policy is a set of disabled transitions, which corresponds to a mapping from the current rooms occupied by the cat and mouse to a set of closed doors.

Figure 3.2: The maze from the cat and mouse problem. Arrows represent doors that the cat and mouse can pass through in the indicated direction.

The state space of the system is  $Q = \{0 \dots 4\} \times \{0 \dots 4\}$ , and each state in the system has the form  $q = (c, m) \in Q$ , where c and m are the rooms occupied by the cat and mouse, respectively. The set of initial states is  $Q_0 = \{(2, 4)\}$ , which contains the single initial state mentioned previously. The atomic propositions are numeric (equality or inequality) comparisons involving the state variables c and m; for example,  $(2, 4) \in [(c \neq m)]$ . Transitions have the form  $((c, m), (c^+, m^+))$ , subject to the constraint  $(c^+ = c) \vee (m^+ = m)$  (i.e., the cat and mouse do not both move simultaneously). The transitions are, of course, also restricted to those that are feasible given the layout of the maze in Figure 3.2. All of the transitions are controllable *except* those such that  $(c \in \{1,3\}) \wedge (c^+ \in \{1,3\}) \wedge (c^+ \neq c)$  (the cat moves between rooms 1 and 3) or  $(c^+ = c) \wedge (m^+ = m)$  (neither the cat nor mouse moves). In terms of this model, the overall specification is:

$$\mathsf{AG}((c \neq m) \land \mathsf{EF}((c = 2) \land (m = 4)))$$

Algorithm 3.1 was applied to solve the problem. The disabled transitions and the states that satisfy the specification in the controlled system are shown in Figures 3.3 and 3.4. Note that, in this example, the number of iterations (3) is much lower than the upper limit given by min  $\{|Q|, |\Delta_c|\} = |Q| = 25$ .

| $\overline{\}$ | 00 | 01 | 02 | 03 | $\overline{04}$ | 10 | 11 | 12 | 13 | 14 | $\frac{1}{20}$ | $\overline{21}$ | 22 | $\overline{23}$ | $\frac{1}{24}$ | 30 | 31 | 32 | 33 | 34 | 40 | 41 | 42 | $\overline{43}$ | 44 |

|----------------|----|----|----|----|-----------------|----|----|----|----|----|----------------|-----------------|----|-----------------|----------------|----|----|----|----|----|----|----|----|-----------------|----|

| <b>00</b>      | *  | •  | *  | •  | *               | *  | •  | •  | •  | •  | •              | •               | •  | •               | •              | *  | •  | •  | •  | •  | •  | •  | •  | •               |    |

| 01             | 1  | *  |    |    |                 |    | 1  |    |    |    |                |                 |    |                 |                |    | 1  |    |    |    |    |    |    |                 |    |

| 02             |    | *  | *  | •  |                 |    | •  | *  |    |    |                | •               |    |                 |                |    |    | *  |    |    |    |    |    |                 |    |

| 03             | 1  | •  | •  | *  |                 |    | •  | •  | 1  |    |                | •               |    |                 |                |    |    |    | 1  |    |    |    |    |                 | •  |

| 04             | •  | •  | •  | 2  | *               | •  | •  | •  |    | *  | •              | •               | •  | •               |                | •  |    | •  | •  | *  | •  | •  | •  |                 |    |

| 10             | •  | •  | •  | •  | •               | *  | •  | 2  |    | *  | *              | •               |    | •               |                | *  |    | •  | •  | •  | •  | •  | •  |                 |    |

| 11             | •  | •  | •  | •  | •               | *  | *  | •  | •  | •  | •              | *               | •  | •               | •              | •  | *  | •  | •  | •  | •  | •  | •  | •               | •  |

| 12             | •  | •  | •  | •  | •               | •  | 1  | *  | •  | •  | •              | •               | 1  | •               | •              | ·  | •  | *  | ·  | •  | •  | ·  | •  | •               | •  |

| 13             | •  | •  | •  | •  | •               | *  | •  | •  | *  | •  | •              | •               | •  | *               | •              | ·  | •  | •  | *  | ·  | ·  | ·  | •  | •               | •  |

| 14             | •  | •  | •  | •  | •               | •  | •  | •  | 1  | *  | •              | •               | •  | •               | *              | •  | •  | •  | •  | *  | •  | •  | •  | •               | •  |

| 20             | 1  | •  | •  | •  | •               | ·  | ·  | •  | •  | •  | *              | •               | 1  | •               | *              | ·  | •  | •  | ·  | ·  | ·  | ·  | •  | •               | •  |

| 21             | •  | 2  | •  | •  | •               | •  | •  | •  | •  | •  | *              | *               | •  | •               | •              | ·  | •  | •  | ·  | •  | •  | ·  | •  | •               | •  |

| 22             | •  | •  | *  | •  | •               | •  | •  | •  | •  | •  | •              | *               | *  | •               | •              | ·  | •  | •  | ·  | •  | •  | ·  | •  | •               | •  |

| 23             | ·  | •  | ·  | 2  | ·               | ·  | ·  | •  | ·  | ·  | *              | ·               | •  | *               | ·              | ·  | ·  | •  | ·  | ·  | ·  | ·  | ·  | ·               | •  |

| 24             | ·  | •  | ·  | •  | *               | ·  | •  | ·  | ·  | •  | ·              | •               | ·  | *               | *              | ·  | •  | •  | ·  | ·  | ·  | ·  | ·  | ·               | •  |

| 30             | •  | •  | ·  | •  | ·               | *  | •  | ·  | •  | ·  | •              | •               | •  | •               | •              | *  | •  | 2  | ·  | *  | 2  | ·  | ·  | •               | •  |

| 31             | ·  | •  | •  | ·  | ·               | ·  | *  | ·  | ·  | ·  | ·              | ·               | •  | ·               | ·              | *  | *  | •  | ·  | ·  | ·  | *  | ·  | ·               | •  |

| 32             | •  | •  | ·  | •  | •               | •  | •  | *  | •  | •  | •              | •               | ·  | •               | •              | ·  | 1  | *  | ·  | ·  | •  | ·  | *  | •               | ·  |

| 33             | ·  | ·  | ·  | ·  | ·               | ·  | ·  | ·  | *  | ·  | ·              | ·               | •  | ·               | ·              | *  | ·  | •  | *  | ·  | ·  | ·  | ·  | *               | •  |

| 34             | •  | •  | •  | ·  | ·               | ·  | •  | •  | ·  | *  | ·              | ·               | •  | ·               | ·              | ·  | ·  | •  | 1  | *  | ·  | ·  | •  | ·               | 1  |

| 40             | 1  | •  | •  | •  | •               | •  | •  | •  | •  | •  | •              | •               | •  | •               | •              | ·  | •  | •  | ·  | •  | *  | ·  | *  | •               | 1  |

| 41             | ·  | *  | ·  | ·  | ·               | ·  | •  | •  | ·  | ·  | ·              | ·               | ·  | ·               | ·              | ·  | ·  | •  | ·  | ·  | *  | *  | •  | ·               | ·  |

| 42             | ·  | •  | *  | •  | ·               | ·  | •  | •  | ·  | ·  | ·              | ·               | ·  | ·               | ·              | ·  | ·  | •  | ·  | ·  | ·  | *  | *  | •               | ·  |

| 43             | ·  | •  | ·  | *  | •               | ·  | •  | •  | ·  | ·  | ·              | ·               | ·  | ·               | ·              | ·  | ·  | •  | ·  | ·  | *  | ·  | •  | *               | ·  |

| 44             | ·  | ·  | ·  | ·  | *               | ·  | ·  | ·  | ·  | •  | ·              | ·               | ·  | ·               | ·              | ·  | ·  | ·  | ·  | ·  | ·  | ·  | ·  | *               | *  |

Figure 3.3: Disabled transitions in the cat and mouse problem.

In Figure 3.3, each row corresponds to the initial state of a transition, and the column gives the final state. The first number is the room occupied by the cat, and the second number is the room occupied by the mouse. Transitions marked with  $\cdot$  are infeasible given the system definition, those marked with a number k are disabled after the  $k^{th}$  iteration, and transitions that remain enabled are marked with \*.

In Figure 3.4, the row and column correspond to the rooms occupied by the

| $\backslash$ | 0 | 1 | 2              | 3        | 4 |

|--------------|---|---|----------------|----------|---|

| 0            | 1 | 2 | 2              | <b>2</b> | * |

| 1            | * | 1 | $\overline{2}$ | 1        | * |

| 2            | * | * | 1              | *        | * |

| 3            | * | 1 | 2              | 1        | * |

| 4            | 2 | 2 |                | 2        | 1 |

Figure 3.4: States that satisfy the specification in the cat and mouse problem.

cat and mouse, respectively. The states marked with \* satisfy the specification subject to the disabled transitions shown in Figure 3.3. The states that do not satisfy the specification are marked with a number k, where k indicates the iteration in which that state was removed from the intermediate solution.

From the state (2, 4), if either the cat or mouse leaves its initial room, the other one is no longer allowed to leave its room. Whichever one left its initial room first is then allowed to travel to any room it can reach, except the other one's initial room.

Note that Figure 3.4 shows the maximal set of states that satisfy the specification, not only those that are reachable (according to the model definition) from the initial state. In particular, states (1,0), (3,0), and (2,1) are not reachable from the initial state (2,4), but they satisfy the specification subject to the solved-for optimal control policy. This demonstrates the fact that the optimal control policy does not depend on the initial state of the system; instead, it determines the set of all initial conditions that satisfy the specification. If the cat and mouse were to start in a state that is not included in this set, then no control policy can guarantee that the specification is satisfied. If they happen to move to a state in the satisfying set, then the controller could take over again and enforce the specification.

# 3.6 Summary

In this chapter, an algorithm was developed to compute the maximallypermissive control policy for a discrete event system that maximizes the set of states in the system that satisfy a specification that involves invariance and reachability requirements. This is called the optimal control policy, and it was proven to exist for such a specification, regardless of the particular system that is to be controlled. The class of specifications involves multiple reachability requirements, as in multitasking supervisory control. The algorithm uses CTL model checking to perform the intermediate calculations.

# Chapter 4

# SynthSMV v0.1.0

## 4.1 Related Software