## **Carnegie Mellon University**

### CARNEGIE INSTITUTE OF TECHNOLOGY

### THESIS

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF Doctor of Philosophy

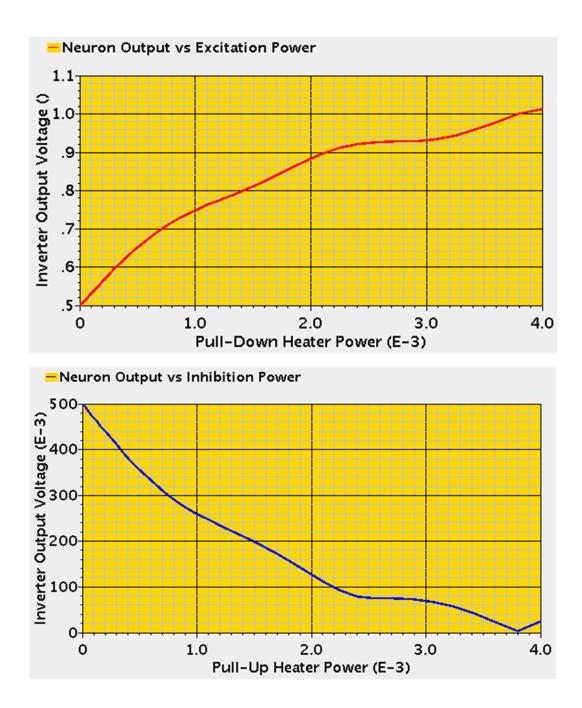

Neurocomputing and Associative Memories Based on Emerging

Technologies: Co-optimization of Technology and Architecture

Vehbi Calayir PRESENTED BY

TITLE

ACCEPTED BY THE DEPARTMENT OF

Electrical and Computer Engineering

ADVISOR, MAJOR PROFESSOR

DEPARTMENT HEAD

9/17/2014 DATE 9/24/2014 DATE

APPROVED BY THE COLLEGE COUNCIL

DEAN

DATE

### Neurocomputing and Associative Memories Based on Emerging Technologies: Co-optimization of Technology and Architecture

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

**Electrical and Computer Engineering**

Vehbi Calayir

B.S., Electrical and Electronics Engineering, Bilkent University M.S., Electrical and Computer Engineering, Carnegie Mellon University

> Carnegie Mellon University Pittsburgh, PA

> > September, 2014

Copyright © 2014 Vehbi Calayir

All rights reserved

## Acknowledgments

#### All the praises and thanks be to Allah, the Lord of the Worlds!

I would like to first express my sincerest gratitude to my advisor, Prof. Larry Pileggi, for his excellent guidance throughout my graduate studies. This research would not have been possible without his continuous support, inexhaustible funding and exceptional vision. He has taught me many crucial things, among which are how to think analytically and critically, see through what other people think impossible, judge everything from both positive and negative sides, and not lose hope, especially when it comes to this line of work. "There is no black or white when you are doing research. There is always gray somewhere. That is what research is," he has always reminded me. His remarkable comments and suggestions constitute a big portion of this interdisciplinary study and have helped me complete my PhD much easier than what I had initially thought.

Next I would like to thank my other thesis committee members, Prof. James Bain (Carnegie Mellon University), Prof. Jeffrey Weldon (Carnegie Mellon University), and Dr. George Bourianoff (Intel Corporation) for their significant help and feedback as well as accepting my invitation in the first place.

I would like to also appreciate my lab members for their helpful discussions and brilliant advices in addition to always forming a motivating atmosphere in the workplace. In particular, I thank David Bromberg, Renzhi Liu, Ekin Sumbul, Daniel Morris, Soner Yaldiz, Thomas Jackson, Ozan Iskilibli, Kaushik Vaidyanathan, Gokce Keskin, Umut Arslan, Curtis Ratzlaff, Andrew Phelps, Vanessa Chen, Bishnu Prasad Das, Qiuling (Jolin) Zhu, Ying-Chih Wang, Jinglin Xu, and Cheng-Yuan Wen.

Last but not least, I would like to express my special and deepest thanks to my family for everything in my life: my mother, Nuray Calayir; my father, Yusuf Calayir; my brothers, Enes and Muhammed Uveys Calayir; my little sister, Zeynep Betul Calayir; and my beloved wife, Zehra Calayir. I would also like to specially thank my brother, Enes Calayir, for being a perfect and elusive comrade as a PhD student here with me at Carnegie Mellon University. I would not have survived during my PhD without his invaluable support and companionship as well as his unexcelled brotherhood.

This work was supported in part by the National Science Foundation under contract CCF1146799 and contract CCF1318160, and a grant from the Semiconductor Research Corporation Nanotechnology Research Initiative. This work was also supported in part by the Systems on Nanoscale Information fabriCs (SONIC), one of six centers supported by the STARnet phase of the Focus Center Research Program (FCRP), a Semiconductor Research Corporation program sponsored by MARCO and DARPA. Finally, this work was supported in part by the Intelligence Advanced Research Program Agency and Space and Naval Warfare Systems Center Pacific under Contract No. N66001-12-C-2008. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the Intelligence Advanced Research Program Agency Research Program Agency and Space and Naval Warfare Systems Center Pacific.

### Abstract

Neurocomputers offer a massively parallel computing paradigm by mimicking the human brain. Their efficient use in statistical information processing has been proposed to overcome critical bottlenecks with traditional computing schemes for applications such as image and speech processing, and associative memory. In neural networks information is generally represented by phase (e.g., oscillatory neural networks) or amplitude (e.g., cellular neural networks). Phase-based neurocomputing is constructed as a network of coupled oscillatory neurons that are connected via programmable phase elements. Representing each neuron circuit with one oscillatory device and implementing programmable phases among neighboring neurons, however, are not clearly feasible from circuits perspective if not impossible. In contrast to nascent oscillatory neurocomputing circuits, mature amplitude-based neural networks offer more efficient circuit solutions using simpler resistive networks where information is carried via voltage- and current-mode signals. Yet, such circuits have not been efficiently realized by CMOS alone due to the needs for an efficient summing mechanism for weighted neural signals and a digitally-controlled weighting element for representing couplings among artificial neurons.

Large power consumption and high circuit complexity of such CMOS-based implementations have precluded adoption of amplitude-based neurocomputing circuits as well, and have led researchers to explore the use of emerging technologies for such circuits. Although they provide intriguing properties, previously proposed neurocomputing components based on emerging technologies have not offered a complete and practical solution to efficiently construct an entire system. In this thesis we explore the generalized problem of co-optimization of technology and architecture for such systems, and develop a recipe for device requirements and target capabilities. We describe four plausible technologies, each of which could potentially enable the implementation of an efficient and fully-functional neurocomputing system.

We first investigate fully-digital neural network architectures that have been tried before using CMOS technology in which many large-size logic gates such as D flip-flops and look-up tables are required. Using a newly-proposed all-magnetic non-volatile logic family, *mLogic*, we demonstrate the efficacy of digitizing the oscillators and phase relationships for an oscillatory neural network by exploiting the inherent storage as well as enabling an all-digital cellular neural network hardware with simplified programmability. We perform system-level comparisons of mLogic and 32nm CMOS for both networks consisting of 60 neurons.

Although digital implementations based on mLogic offer improvements over CMOS in terms of power and area, analog neurocomputing architectures seem to be more compatible with the greatest portion of emerging technologies and devices. For this purpose in this dissertation we explore several emerging technologies with unique device configurations and features such as *mCell* devices, *ovenized aluminum nitride resonators*, and tunable *multi-gate graphene* devices to efficiently enable two key components required for such analog networks – that is, summing function and weighting with compact D/A (digital-to-analog) conversion capability. We demonstrate novel ways to implement these functions and elaborate on our building blocks for artificial neurons and synapses using each technology. We verify the functionality of each proposed implementation using various image processing applications based on compact circuit simulation models for such post-CMOS devices. Finally, we design a proof-of-concept neurocomputing circuitry containing 20 neurons using 65nm CMOS technology that is based on the primitives that we define for our analog neurocomputing scheme. This allows us to fully recognize the inefficiencies of an all-CMOS implementation for such specific applications. We share our experimental results that are in agreement with circuit simulations for the same image processing applications based on proposed architectures using emerging technologies. Power and area comparisons demonstrate significant improvements for analog neurocomputing circuits when implemented using beyond-CMOS technologies, thereby promising huge opportunities for future energy-efficient computing.

## **Table of Contents**

| Chapte | er 1 | Introduction1                                                            |

|--------|------|--------------------------------------------------------------------------|

| 1.1    | Neur | ocomputing and Associative Memories1                                     |

| 1.2    | Neur | ocomputing Circuits Using CMOS Technology3                               |

| 1.3    | Orga | nization of Thesis6                                                      |

| Chapte | er 2 | Emerging Technologies for Neurocomputing8                                |

| 2.1    | Prev | ous Work8                                                                |

| 2.2    | Arch | itecture Abstraction for Neurocomputing Based on Emerging Technologies13 |

| 2,2    | 2.1  | Digital Neural Networks14                                                |

| 2.2    | 2.2  | Analog Neural Networks15                                                 |

| 2.3    | Towa | ards Highly-Efficient Associative Memories and Neurocomputing17          |

| Chapte | er 3 | Fully-Digital Associative Memories and Neurocomputing19                  |

| 3.1    | mCel | l: Non-Volatile Programmable Magnetic Device19                           |

| 3.2    | mLog | gic: Non-Volatile All-Magnetic Logic Technology 21                       |

| 3.3    | Prop | osed Fully-Digital ONN Architecture24                                    |

| 3.3    | 3.1  | Derivation of Discrete-Time ONN Dynamics24                               |

| 3.3    | 3.2  | Implementation of Fully-Digital ONN26                                    |

| 3.    | 3.3   | Behavioral Simulation28                                           |

|-------|-------|-------------------------------------------------------------------|

| 3.    | 3.4   | System-Level Comparison to 32nm CMOS Technology29                 |

| 3.4   | Prop  | osed Fully-Digital CNN Architecture                               |

| 3.    | 4.1   | Derivation of Discrete-Time CNN Dynamics                          |

| 3.    | 4.2   | Implementation of Fully-Digital CNN                               |

| 3.    | 4.3   | Behavioral Simulation33                                           |

| 3.    | 4.4   | System-Level Comparison to 32nm CMOS Technology35                 |

| 3.5   | Sumr  | nary                                                              |

| Chapt | er 4  | All-Magnetic Analog Associative Memory and Neurocomputing         |

| 4.1   | mCel  | ls for Neurocomputing                                             |

| 4.2   | Prop  | osed Neurocomputing Architecture Using mCells                     |

| 4.3   | Circu | it Simulation Results                                             |

| 4.    | 3.1   | Comparisons to Digital CMOS and mLogic Implementations45          |

| 4.4   | A Gu  | ideline for Future Device Development for mCells46                |

| Chapt | er 5  | Thermal-Based Analog Associative Memory and Neurocomputing 48     |

| 5.1   | Oven  | ized AlN Resonator48                                              |

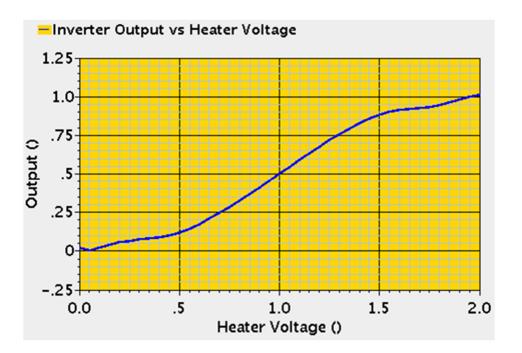

| 5.2   | Prop  | osed Architecture for Neurocomputing Based on Ovenized Resonators |

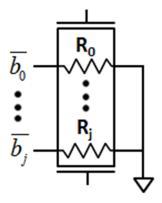

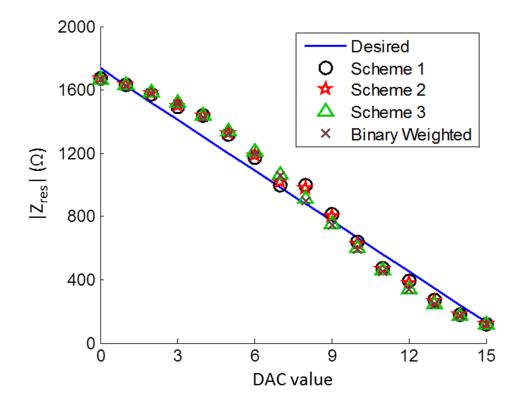

| 5.3   | Imple | ementing D/A Programming Feature56                                |

| 5.    | 3.1   | Derivation of Variable-Size Heater Resistances59                  |

| 5.    | 3.2   | A "Thermal DAC" Example 60                                        |

| 5.4   | Circu | it Simulation Results                                             |

| 5.    | 4.1   | Energy and Area Comparisons                                       |

| 5.5   | Towa  | rds Viable Thermal Neurocomputing Circuits67                      |

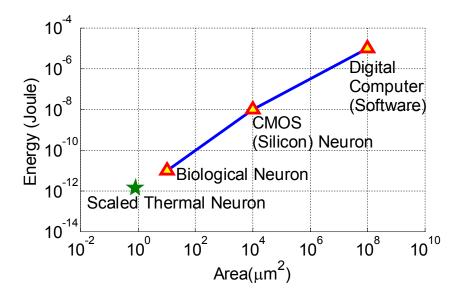

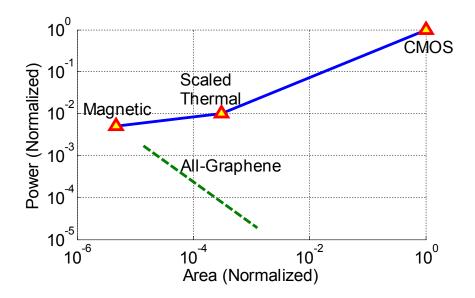

| Chapt | er 6  | All-Graphene Analog Associative Memory and Neurocomputing         |

### ix

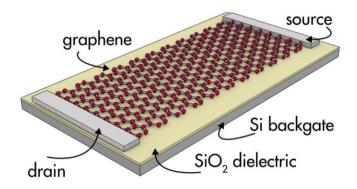

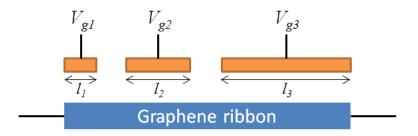

| 6.1                | Multi                                       | -Gate Programmable Resistive Device Using Graphene                                                                                                                                                  |                 |

|--------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

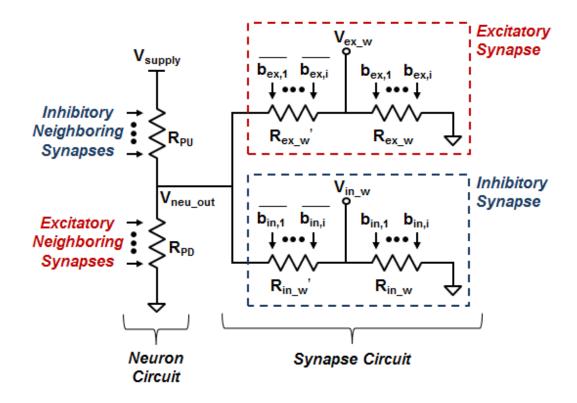

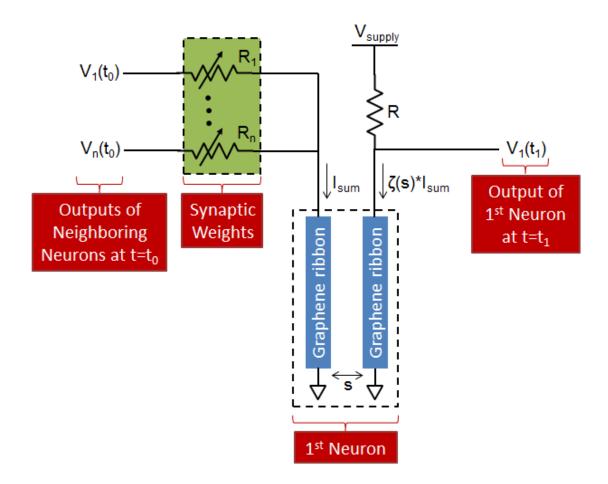

| 6.2                | Propo                                       | osed Neurocomputing Circuits Based on Graphene                                                                                                                                                      | 72              |

| 6.3                | Circu                                       | it Simulations                                                                                                                                                                                      | 75              |

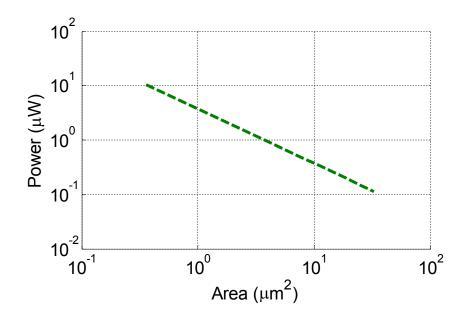

| 6.4                | Devic                                       | e Scaling and Improvements for Affordable All-Graphene Neurocomputing                                                                                                                               | g Circuits78    |

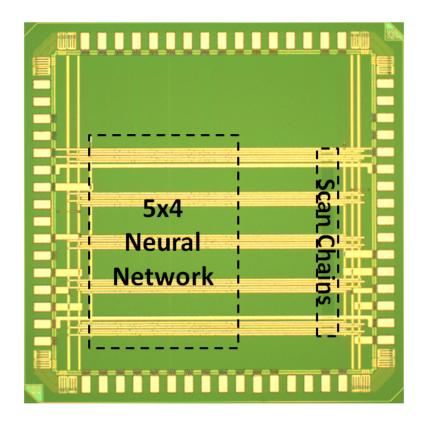

| Chap               | ter 7                                       | Proof-of-Concept 65nm CMOS Analog Neurocomputing Chip                                                                                                                                               | 80              |

| 7.1                | Desig                                       | n of Analog CMOS Emulation Circuitry                                                                                                                                                                | 80              |

| 7.2                | Expe                                        | imental Test Results                                                                                                                                                                                | 84              |

| 7.3                | Comp                                        | parisons to Our Proposed Analog Neural Networks Based on Emerging Tec                                                                                                                               | hnologies 88    |

|                    |                                             |                                                                                                                                                                                                     | 0               |

| Chap               | ter 8                                       | Conclusion and Future Directions                                                                                                                                                                    | C               |

| <b>Chap</b><br>8.1 |                                             | <b>Conclusion and Future Directions</b>                                                                                                                                                             |                 |

| 8.1                |                                             |                                                                                                                                                                                                     | <b>90</b>       |

| 8.1                | Futur                                       | e Considerations                                                                                                                                                                                    | <b>90</b><br>92 |

| 8.1                | Futur                                       | e Considerations<br>All-Graphene Neural Network Enabled by Evanescent Wave Coupling                                                                                                                 |                 |

| 8.1                | Futur<br>.1.1<br>8.1.1.1                    | e Considerations<br>All-Graphene Neural Network Enabled by Evanescent Wave Coupling<br>Proposed Architecture                                                                                        |                 |

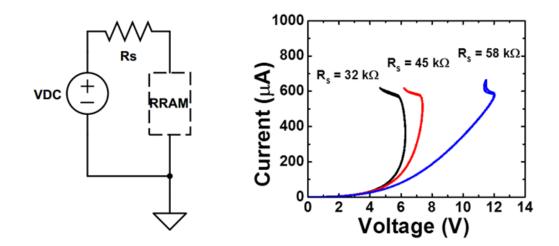

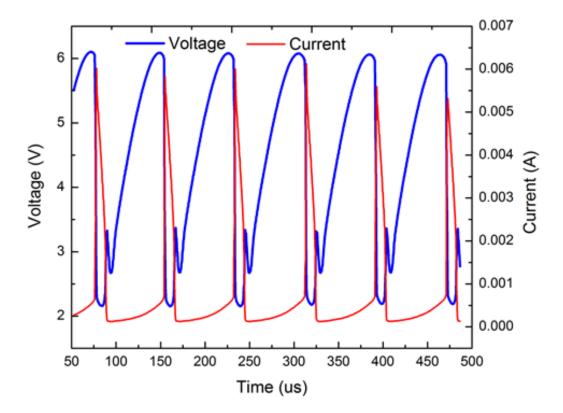

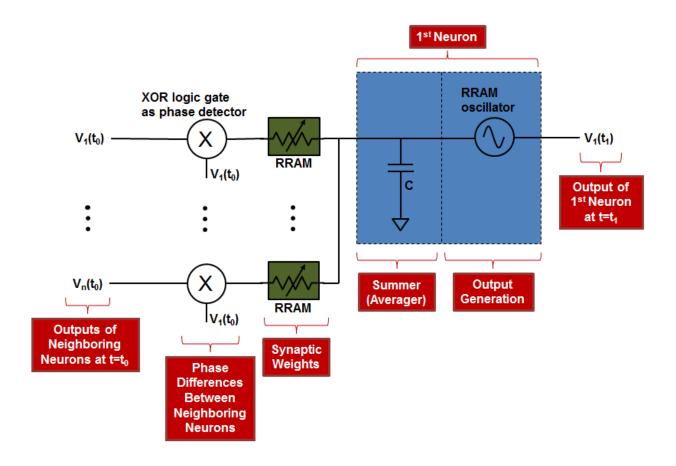

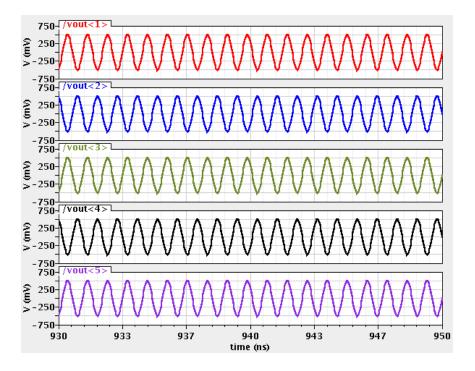

| 8.1                | Futur<br>.1.1<br>8.1.1.1<br>.1.2            | e Considerations<br>All-Graphene Neural Network Enabled by Evanescent Wave Coupling<br>Proposed Architecture<br>Oscillatory Neural Networks Using Low-Power RRAM Oscillators                        |                 |

| 8.1                | Futur<br>.1.1<br>8.1.1.1<br>.1.2<br>8.1.2.1 | e Considerations<br>All-Graphene Neural Network Enabled by Evanescent Wave Coupling<br>Proposed Architecture<br>Oscillatory Neural Networks Using Low-Power RRAM Oscillators<br>The RRAM Oscillator |                 |

# **List of Figures**

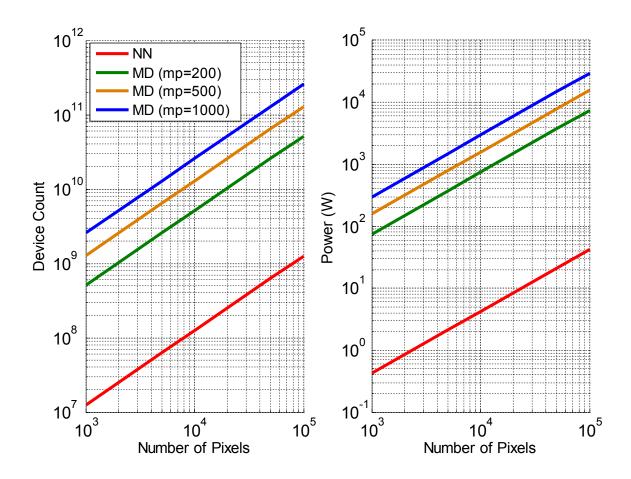

| Figure 1.1. | Hardware comparison of MD- and NN-based associative memory. $mp$ denotes the                                                                                                                                                                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | number of memorized patterns4                                                                                                                                                                                                                                                                    |

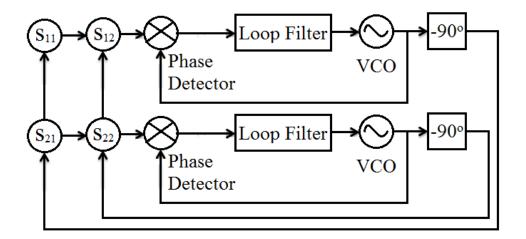

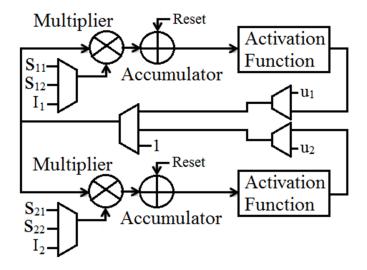

| Figure 1.2. | Conceptual architecture of PLL NNs for a 2-neuron system. VCO in this figure represents the voltage-controlled oscillator; and $s_{11}$ , $s_{12}$ , $s_{21}$ , and $s_{22}$ denote the corresponding programmable synaptic weights between artificial neurons that can be implemented with VGAs |

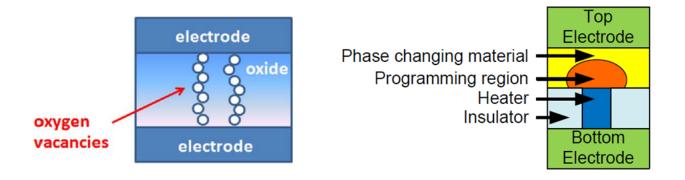

| Figure 2.1. | RRAM [9] (left) and PCM [13] (right)9                                                                                                                                                                                                                                                            |

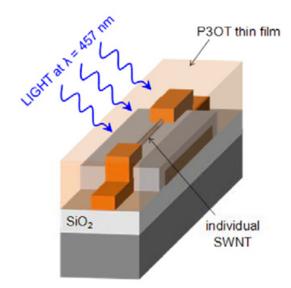

| Figure 2.2. | OG-CNTFET [14]10                                                                                                                                                                                                                                                                                 |

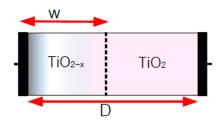

| Figure 2.3. | Titanium dioxide (TiO <sub>2</sub> )-based memristor [17]10                                                                                                                                                                                                                                      |

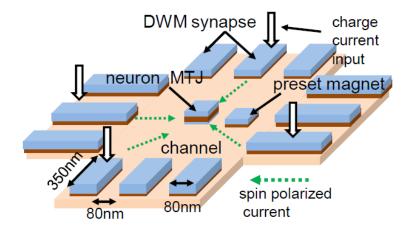

| Figure 2.4. | Spintronic neuron-synapse unit consisting of MTJ and DWM devices [18]11                                                                                                                                                                                                                          |

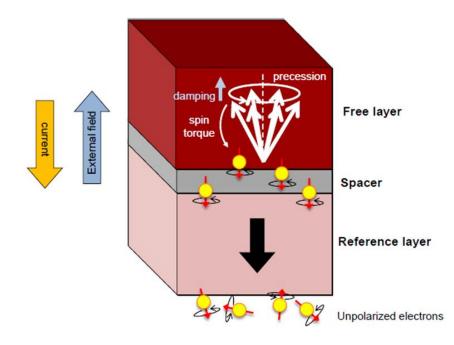

| Figure 2.5. | STO (Courtesy of Jimmy Zhu's group from Carnegie Mellon University)12                                                                                                                                                                                                                            |

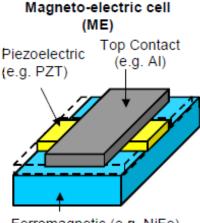

| Figure 2.6. | Magneto-electric cell [24]13                                                                                                                                                                                                                                                                     |

| Figure 2.7. | Conceptual architecture of a typical neuron-synapse model14                                                                                                                                                                                                                                      |

| Figure 3.1. | 2D cross section view of mCell for the write-path current direction from left to right<br>(left) and right to left (center), and its schematic symbol (right)                                                                                                                                    |

| Figure 3.2.  | Traditional NAND (left), inversion-free NAND (center), and AND (right) gate             |

|--------------|-----------------------------------------------------------------------------------------|

|              | examples using mLogic technology22                                                      |

| Figure 3.3.  | An inverter driving three two-input NOR gates. The fanout mCells are connected in       |

|              | series as highlighted by the red path. Two non-overlapping power clocks are applied to  |

|              | the driven and driving mLogic gates23                                                   |

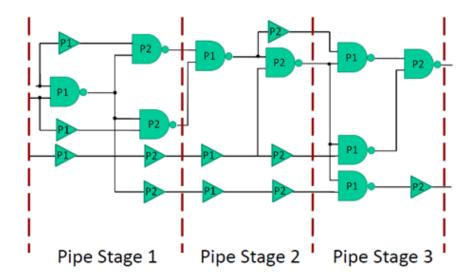

| Figure 3.4.  | Pipelined mLogic gate stages [27]. Each pipeline stage is divided into two sub-stages.  |

|              | The mLogic gates in the first sub-stages and second sub-stages are clocked with two     |

|              | non-overlapping power clocks for power savings24                                        |

| Figure 3.5.  | Transfer function for fully-digital ONN25                                               |

| Figure 3.6.  | High-level circuit representation of the discrete-time ONN. The signal-selecting blocks |

|              | are multiplexers27                                                                      |

| Figure 3.7.  | 60-pixel memorized bit patterns. They are stored in the neural network via synaptic     |

|              | weights                                                                                 |

| Figure 3.8.  | Pattern recognition process (Example 1). The initial input pattern is the distorted     |

|              | version of the bit pattern '1'29                                                        |

| Figure 3.9.  | Pattern recognition process (Example 2). The initial input pattern is the distorted     |

|              | version of the bit pattern 'o'                                                          |

| Figure 3.10. | mLogic vs CMOS comparison per neuron for different ONN system sizes: Device count       |

|              | comparison (left) and power comparison (right)                                          |

| Figure 3.11. | A 2D CNN illustrating neighboring cells for a CNN cell when $r=1$ 32                    |

| Figure 3.12. | High-level circuit representation of the discrete-time CNN34                            |

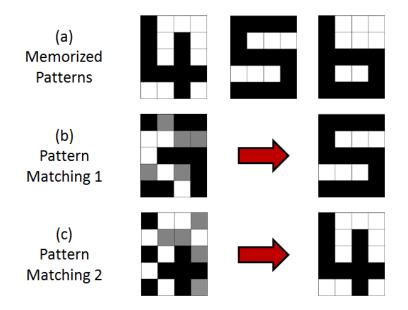

| Figure 3.13. | Memorized bit patterns and pattern recognition examples for our proposed fully-         |

|              | digital CNN system                                                                      |

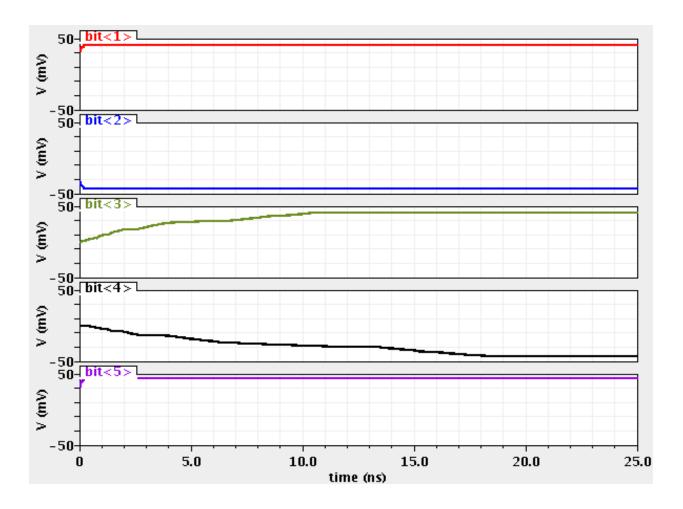

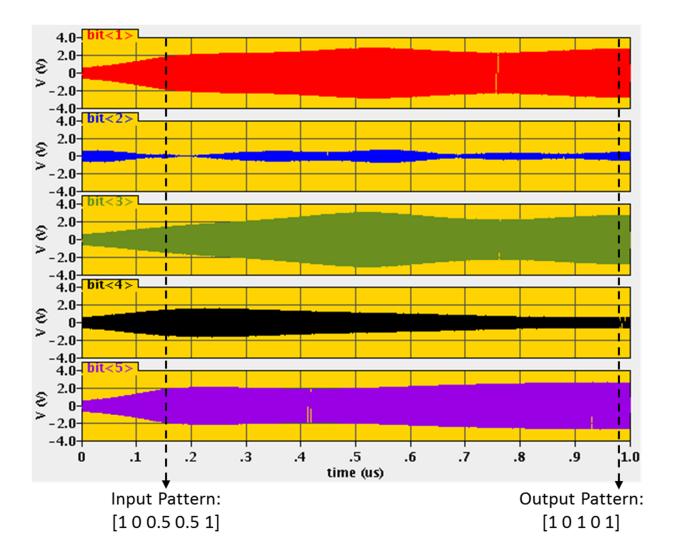

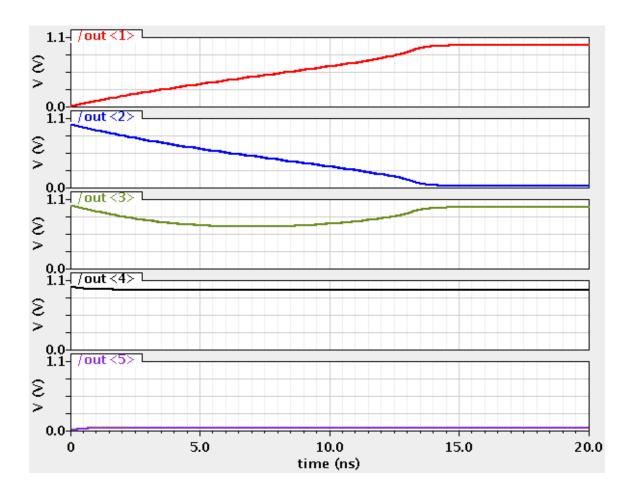

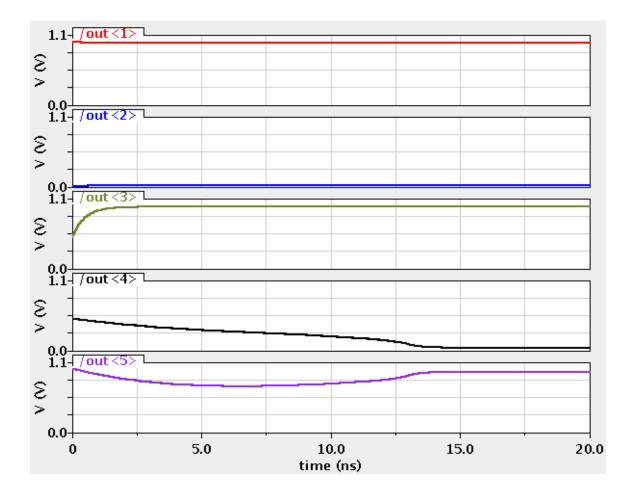

- Figure 4.3. Pattern recognition example based on a 5-neuron system. Intermediate pixel values are possible as initial conditions by means of different switching thresholds of mCells in the neuron circuits. For this example the initial input pattern is [1 0 0.5 0.5 1] at time=0s and the recovered output pattern is [1 0 1 0 1] at time=25ns......43

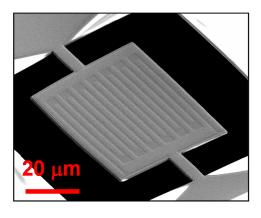

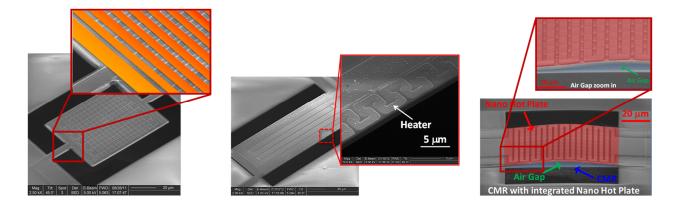

- Figure 5.1. Micrograph of an example AlN RF resonator (*Courtesy of Gianluca Piazza's group* from Carnegie Mellon University). The resonator size is relatively large

- Figure 5.3. Example heater implementations as a serpentine on the bottom electrode [41] (left), around the top electrode [42] (center), and on top of the resonator [43] (right). ....... 51

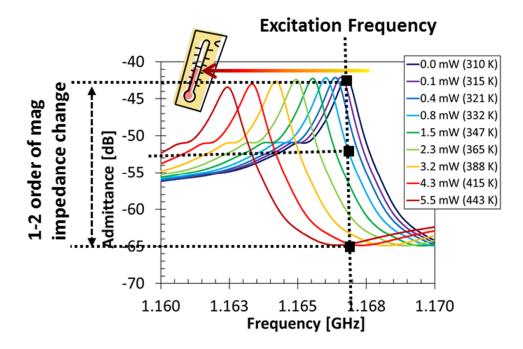

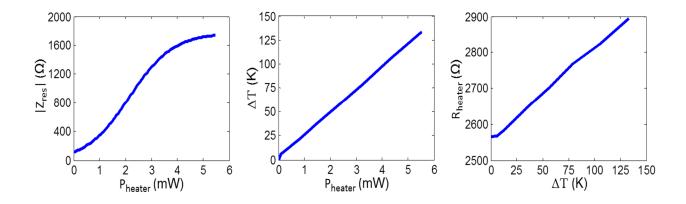

| Figure 5.9. | Resonator impedance versus heater power curve at 1.1667GHz operation frequency           |

|-------------|------------------------------------------------------------------------------------------|

|             | (left), temperature increase in the resonator versus heater power curve (center), and    |

|             | heater resistance versus temperature increase in the resonator curve (right). All curves |

|             | are extracted from measured data for an example resonator [41]61                         |

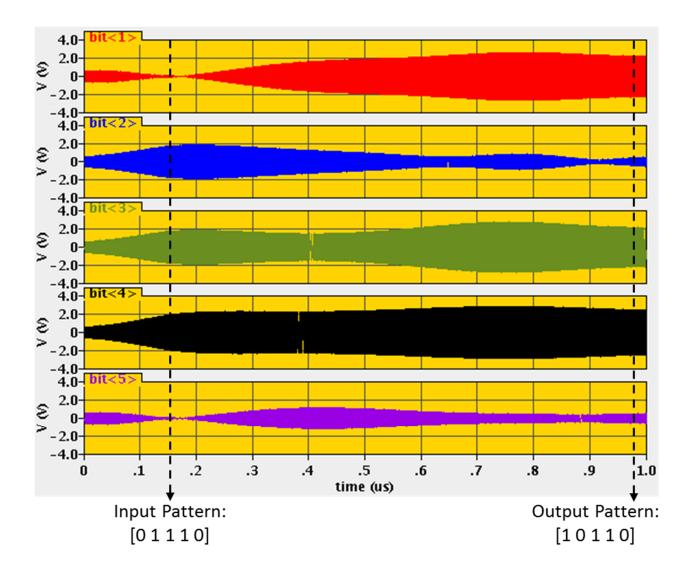

- Figure 5.12. Pattern recognition example based on a 5-neuron system. Associative memory fully recognizes the pattern [1 0 1 1 0] despite 40% distortion in the initial input pattern...64

- Figure 6.2. Cross-section drawing of the multi-gate graphene resistance. Each gate controls the conductivity of the corresponding area underneath it.  $V_{g_1}$ ,  $V_{g_2}$  and  $V_{g_3}$  represent

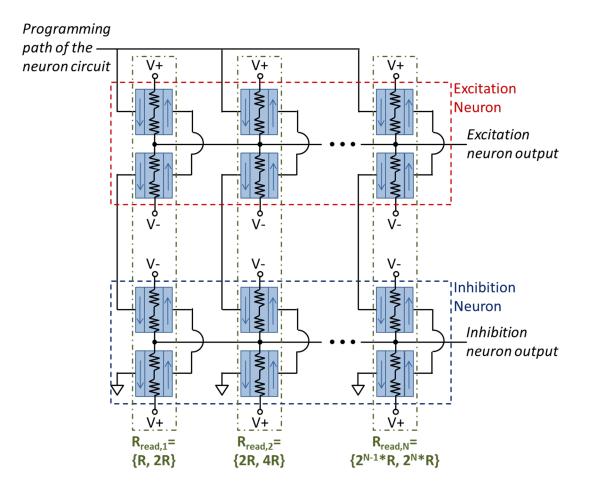

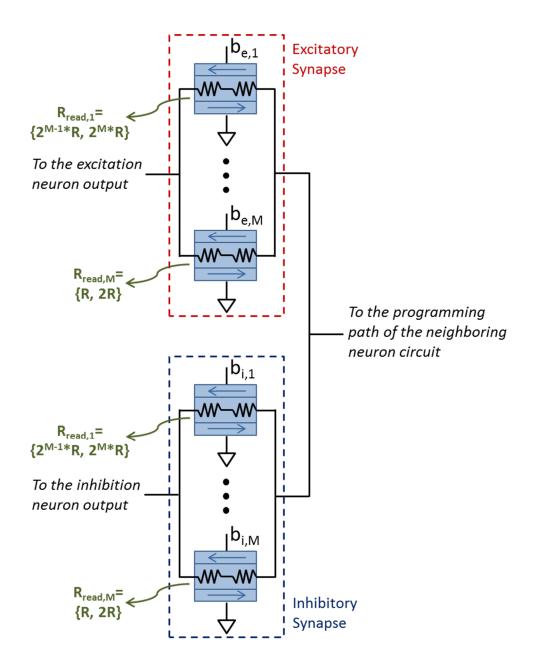

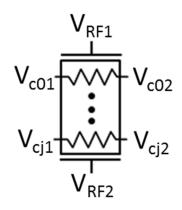

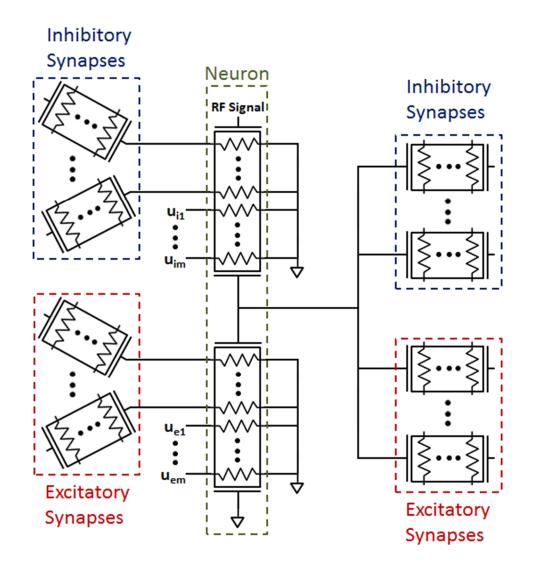

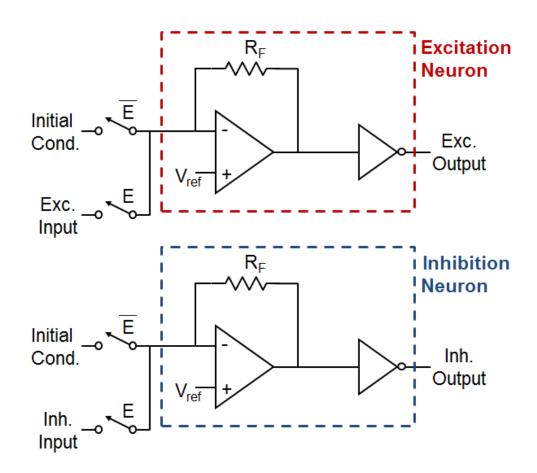

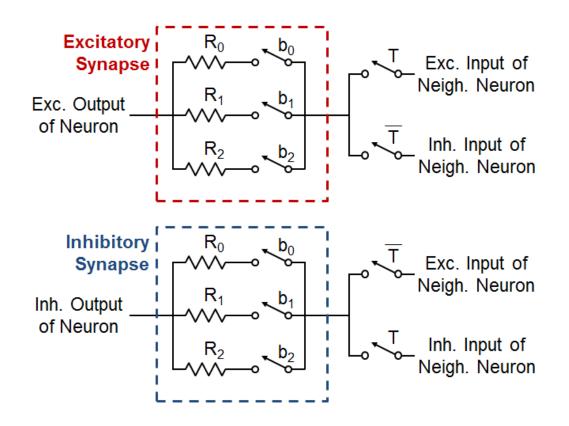

- Figure 6.3. Proposed neuron and synapse circuits based on multi-gate graphene devices.  $b_{ex,i}$ - $b_{ex,i}$  and  $b_{in,i}$ - $b_{in,i}$  represent *i*-bits binary numbers for excitatory and inhibitory synaptic weights, respectively......73

- Figure 6.4. Pattern recognition example based on a 5-neuron system. Associative memory fully recognizes the pattern [1 0 1 1 0] despite 40% distortion in the initial input pattern...76

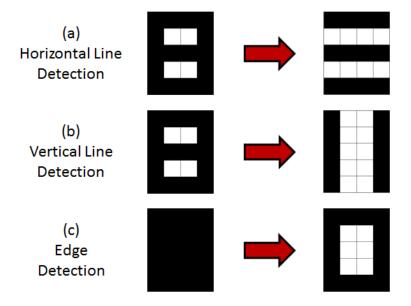

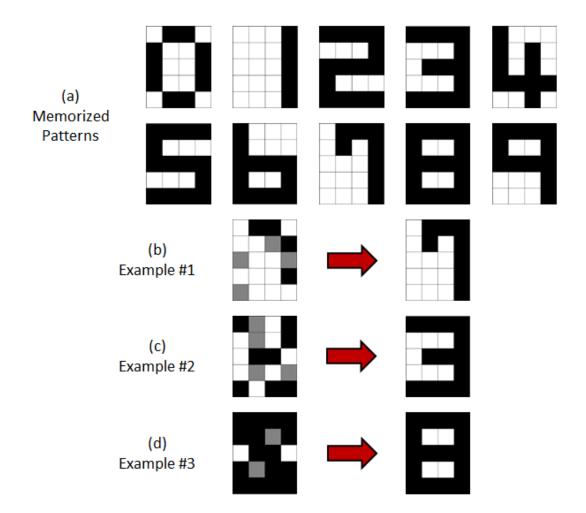

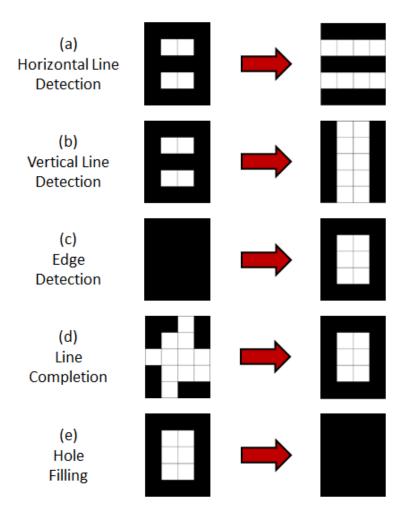

| Figure 7.6. | Testing results for different image processing applications. Input patterns (left) a | nd  |

|-------------|--------------------------------------------------------------------------------------|-----|

|             | output patterns (right). (a) Horizontal line detection. (b) Vertical line detection. | (c) |

|             | Edge detection. (d) Line completion. (e) Hole filling                                | 88  |

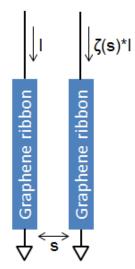

- Figure 8.1. The graphene coupler. The current through the second graphene sheet is affected by the current through the first one and the distance between the two.  $\zeta$  denotes the coupling coefficient between two graphene ribbons and is a function of *s*, the distance between these ribbons......93

- Figure 8.6. The system stays in the locked state with stored pattern, [1 0 1 1 0], as initial state. ...98

- Figure 8.7. The system stays in the locked state with stored pattern, [1 0 1 0 1], as initial state. ...99

- Figure 8.9. Synchronization of our proposed network with two 50% distorted pixels. Input pattern: [1 0.5 0.5 0 1] & Output pattern: [1 0 1 1 0]......100

- Figure 8.10.Synchronization of our proposed network with one 25% and two 50% distorted pixels.Input pattern: [1 0.5 0.5 0 0.75] & Output pattern: [1 0 1 0 1].....100

## **List of Tables**

| Table 5.1.         | Scaling equations for ovenized AlN resonators. $w$ , $l$ and $t$ denote the width, length and |

|--------------------|-----------------------------------------------------------------------------------------------|

|                    | thickness of the device, respectively. Device dimensions used throughout this chapter         |

|                    | are in the form of $\{w \ge l \ge t\}$                                                        |

| Table 7.1.         | Chip performance. The neuron-synapse module is composed of one neuron circuit                 |

|                    | with nine artificial synapses85                                                               |

| Table <b>7.2</b> . | Hamming distance as a percentage between stored and initial input patterns for three          |

|                    | digit recognition examples in Figure 7.5 (b)-(d)                                              |

# Chapter 1 Introduction

As we reach the end of the CMOS roadmap researchers have started to intensively focus on post-CMOS technologies for circuit and system solutions. While there are several emerging technologies that offer great promise as CMOS alternatives, there are none that completely replace CMOS for the systems and architectures that are implemented today. For this reason it is important to explore system opportunities for emerging technologies as they evolve, since small block- or circuit-level comparisons to CMOS technology are unlikely to demonstrate any significant benefit. The greatest potential for an emerging technology will only be evident in terms of complete systems that are configured and optimized to exploit their unique features.

### 1.1 Neurocomputing and Associative Memories

Neurocomputing is considered an intriguing alternative to computing based on traditional techniques due to its brain-inspired massive parallelism. A neurocomputer attempts to mimic the human brain via a network of coupled artificial neurons that process information in parallel. Each brain neuron corresponds to a computational unit in a neurocomputer, and a connection between two artificial neurons represents a synapse that is connecting two brain neurons. The

strength of this synapse is the synaptic weight in a neurocomputer that relates one artificial neuron to another. In this way, neurocomputers operate analogously to the human brain.

Traditional computing schemes (variants of the von Neumann architecture) run a software algorithm for a specific application by sequentially executing each line in the instruction code. Even though each execution might take a very short time the overall computation efficiency is not that high due to the serial execution of instructions when compared to neurocomputing [1]-[3]. Instead, a neurocomputer performs pattern recognition via associative memory in a massively-parallel manner. It maps a set of input patterns to a set of output patterns via synaptic weights, whereby an output pattern can be retrieved for a given initial pattern. It therefore represents a powerful component for non-algorithmic, nonlinear, complex problems, and statistical information processing applications such as pattern recognition, image processing, and associative memory. These applications would otherwise require numerous memory fetch operations and a processor that is executing a list of commands for optimization.

For example, traditional associative memory circuits use *Manhattan distance (MD)* technique to find the best match among stored patterns in the system for a given noisy input pattern [4]-[5]. Since directly implementing MD is costly due to the required numerous subtraction and absolute value operations, binary bits representing the grey-scale pixels are first converted into thermometer bits, and then *Hamming distance* is applied to find the number of unmatched bit locations between that input pixel and the corresponding pixel in the stored patterns. However, such an approach consumes significant amount of memory resources because each memorized pattern has to be stored in the system as opposed to the neural networks (NNs) where the stored patterns are represented by synaptic weights among artificial neurons. This technique does not also provide functional flexibility that associative memories based on NNs offer because MD finds a deterministic match while NNs offer a statistical

approach which is useful for various image processing applications other than pattern matching as well.

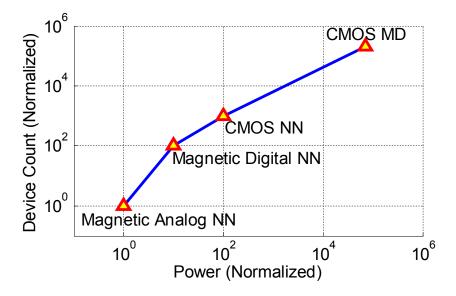

We have modeled both MD and NN using a hardware description language (VHDL). We have mapped these models to standard logic gates using a logic synthesis tool (Synopsys Design Compiler). Figure 1.1 shows a hardware comparison of both associative memories that are implemented in 32nm CMOS. Although a computer would require less power to perform these functions, and we would never consider an MD implementation of the scale that would require 10's of kilowatts, this comparison does show how these two custom implementations would compare to each other in terms of power and area when built to perform the same functions. Apart from aforementioned implementation challenges MD requires 200x more devices and dissipates 700x more power for large-scale systems. This comparison does not consider the potential benefits of localized highly-distributed memory and computation that the NNs offer as opposed to a separate memory and processor.

### 1.2 Neurocomputing Circuits Using CMOS Technology

While neurocomputers offer a promising architecture for energy-efficient, future computing systems, their CMOS implementations have largely been viewed as impractical and significantly inferior to implementations based on more traditional CMOS architectures and memories due to the required circuit complexity and corresponding power consumption, thereby limiting the wide use of such architectures.

Oscillatory neural networks (ONNs), a prevalent example of phase-based neurocomputing, are particularly interesting systems since they mimic nature and the brain. But each neuron requires a voltage or current controlled oscillator and a means of programming the phase relationship among all neurons to represent the stored information. Importantly, ONNs rely on having connections (artificial synapses) among *all* artificial neurons – that is, the ability to

program the  $n^2$  phase relationships among *n* artificial neurons. CMOS voltage-controlled oscillators (VCOs) are theoretically viable to represent oscillations, but completely impractical from an energy standpoint. Moreover, implementing the phase relationships among the VCOs is even more costly. For example, proposed ONN architecture based on phase-locked loops (PLLs) in Figure 1.2 [3] requires one PLL for each artificial neuron and one variable gain amplifier (VGA) for each programmable synapse. It would be impractical to power *n* PLLs and  $n^2$  VGAs on a single CMOS chip for even a modest-size associative memory. To provide an analog control voltage to VGAs this architecture also necessitates the use of digital-to-analog converters (DACs) to convert digital control bits for synapse programming to an analog voltage level, further exacerbating the overall system performance.

Figure 1.1. Hardware comparison of MD- and NN-based associative memory. *mp* denotes the number of memorized patterns.

While nascent ONN systems have severe implementation challenges, amplitude-based cellular neural networks (CNNs) offer more efficient circuits due to being a more mature technology. For CNNs there are training algorithms that have already been developed based on only *local connections* among just the nearest neighboring neurons. Independent of memory size or number of neurons, each artificial neuron is interconnected only to neighboring neurons within a specified radius. The radius can be extended for better accuracy such that all neurons share one-to-one connections like ONN architectures, but CNNs can also be implemented using the smallest possible radius that corresponds to only 9 connections to neighboring neurons. Even with so few connections though, CNN implementation of the neurons and synapses via CMOS is inefficient as compared to more traditional computing architectures.

Figure 1.2. Conceptual architecture of PLL NNs for a 2-neuron system. VCO in this figure represents the voltage-controlled oscillator; and  $s_{11}$ ,  $s_{12}$ ,  $s_{21}$ , and  $s_{22}$  denote the corresponding programmable synaptic weights between artificial neurons that can be implemented with VGAs.

For example, analog implementations of CNNs have been attempted whereby a digital input for each programmable synapse is converted to a control voltage using a DAC and an analog variable-gain amplifier/multiplier [6]-[7]. Since each neuron in a CNN system has 9 artificial synapses, *nine DACs and nine analog amplifiers are needed for each artificial neuron*, which is impractical for large-scale systems. Such implementations also lack the functional flexibility of neurocomputers, since artificial neuron circuits share the same synapse circuits using a cloning template for synaptic weights to compensate the high circuit complexity required for synapse circuits. Moreover, the best reported digital CNN implementation in CMOS [8] requires *32 D flip-flops and 155 mostly-large-size logic gates* (e.g., look-up tables, multiplexers, XORs, etc.) *for each neuron*, which is also not practical for large-scale systems.

### 1.3 Organization of Thesis

Although CMOS is inefficient for constructing neurocomputers, emerging technologies portend to offer new opportunities. However, the proposed implementations so far have either not addressed and solved all the performance issues that CMOS-based architectures already have, or posed new problems that require special circuit and/or manufacturing techniques. In this thesis we describe our novel approach to enable efficient and feasible neurocomputing circuits and associative memories. For this purpose we begin with a survey of previously proposed designs based on emerging technologies and show the issue(s) associated with each design in Chapter 2. Then we explain our design approach (i.e., co-optimization of technology and architecture) to deal with such issues, and provide the required device/technology specifications for building affordable neurocomputing systems. Next, using these specifications, we demonstrate our proposals for both digital and analog neurocomputing circuits and associative memories enabled by emerging technologies such as mLogic, mCell, ovenized aluminum nitride (AlN) resonator and graphene in Chapter 3, Chapter 4, Chapter 5 and Chapter 6, respectively. In these chapters we also provide circuit simulations and performance comparisons to CMOS technology using Verilog-A compact models for the corresponding devices all developed based on measurement data, and discuss device developments required for building practical systems based on such devices. We strongly believe our findings in these chapters will guide the beyond-CMOS device development for energy-efficient computing. Chapter 7 presents the design and experimental results of a proof-of-concept CMOS chip in 65nm that emulates our proposed analog neurocomputing scheme. Chapter 8 concludes the thesis with brief summary and future considerations.

# Chapter 2 Emerging Technologies for

## Neurocomputing

In this chapter we investigate the use of emerging technologies for a more efficient implementation of neurocomputing circuits. We start with an overview of recently proposed neurocomputing circuits and associative memories based on post-CMOS technologies, such as resistance change devices. We further evaluate the challenges and deficiencies associated with the deployment of these device technologies in actual neurocomputing systems. We then propose a generalized abstraction for a neurocomputing circuit that would be required to implement artificial neurons and synapses in a system context. We postulate how our system approach would be implemented, and outline the design features required for the device/technology for both digital and analog implementations.

### 2.1 Previous Work

Emerging technology devices offer new opportunities to efficiently construct a tunable analog resistance that could be used to implement programmable artificial synapses for neurocomputers. Recently the use of specific memristor devices such as RRAM (resistive RAM) [9]-[10] and PCM (phase change memory) [11]-[13] (see Figure 2.1) has been shown to efficiently implement electronic synapses. Such voltage-controlled resistances are adjusted to have programmable synaptic weights. However, since these devices have only one control path for setting their resistances, using them as artificial synapses requires either *one DAC per synapse* to convert digital control bits into an analog control signal or *one digitally-controlled pulse generator for each synapse* to provide a pulse-based programming scheme for gradual resistance change [9]-[13]. In such implementations the neuron circuits would be implemented in traditional CMOS technology, which requires compatible monolithic integration with CMOS.

Figure 2.1. RRAM [9] (left) and PCM [13] (right).

Optically gated carbon nanotube field effect transistors (OG-CNTFETs) in Figure 2.2 have also been proposed to efficiently represent artificial synapses using a pulse-based programming for gradual resistance change [14]. Along with the aforementioned issues for two-terminal memristor devices, *OG-CNTFETs suffer from high resistance values ranging from M* $\Omega$  *to G* $\Omega$ , *thereby requiring high voltages* to create reliable/distinguishable currents through artificial synapses. For example, the proposed neurocomputing scheme in [14] uses a 7V supply voltage to generate only 10-40nA current, which would present design challenges with internal and external noise sources.

Figure 2.2. OG-CNTFET [14].

Another design based on memristors (e.g., titanium dioxide in Figure 2.3) [15]-[17] relies on a *memristor bridge synapse* consisting of 4 or 5 devices and a CMOS differential pair to convert voltage-mode signals to current-mode signals for an efficient summing of neural signals. The neuron circuit is implemented as a differential amplifier to sum these currents coming from neighboring neurons and generate an output voltage based on the summation. This implementation uses *wide and strong pulses to program memristors (synapse programming), but small and narrow pulses during neural evaluation* in order not to significantly alter resistance of memristors. This requires *complex pulse generation circuitry*, which is costly in terms of area and power. To prevent undesired resistance drift during neural evaluation, *a doublet generator* has been proposed [16] that results in further power and area consumption.

Figure 2.3. Titanium dioxide (TiO<sub>2</sub>)-based memristor [17].

Spintronic devices have also been recently proposed to implement neurocomputers by exploiting spin properties of electrons to perform efficient computation [18]-[19]. Such circuits use domain wall magnets (DWMs) for constructing programmable synapses and magnetic tunnel junctions (MTJs) for implementing artificial neurons as shown in Figure 2.4. However, both neuron and synapse circuits still require *CMOS devices for converting spin-based signals into charge mode signals via latches and sending neural information through long-distance connections*. They also necessitate one *DAC for programming each artificial synapse and another DAC for applying initial inputs to each artificial neuron*. It is important to note, however, that domain wall based synapses would not be reliable for these types of applications since neural processing currents and/or thermal fluctuations and/or external magnetic fields can change the position of the domain wall inside the magnet during neural evaluation, thereby changing the corresponding synaptic weight and causing incorrect functioning.

Figure 2.4. Spintronic neuron-synapse unit consisting of MTJ and DWM devices [18].

Nanoscale spin torque oscillators (STOs) depicted in Figure 2.5 offer single device oscillators to model the artificial neurons as well [20]-[21]. Such devices have been demonstrated to couple when implemented on a shared free layer for the magnetic spin [22]; however, efficiently implementing a programmable phase among all oscillators to represent the stored data is a daunting challenge if not completely infeasible. *Local distances between neighboring neurons* have been claimed to represent such synaptic weights [21]. Yet, *an architecture based on using fixed distances as weights cannot be re-programmed once fabricated*, thereby eliminating the flexible functionality neurocomputers naturally enable. Moreover, a dc current is required to specify the STO oscillation frequency, thereby consuming significant stand-by power to store state. Several CMOS amplifying stages are also required to boost the tiny STO output power [23].

Figure 2.5. STO (Courtesy of Jimmy Zhu's group from Carnegie Mellon University).

Lastly, a neural network design has been demonstrated based on spin waves for information exchange [24]. Each artificial neuron is constructed as a magneto-electric cell (see Figure 2.6) that has only two magnetic polarization states. Therefore, *gray-scale image pixels are not possible with this neuron circuit*, thus limiting the functionality of overall neurocomputing system. Couplings between the cells can be adjusted only by the direction and strength of a global magnetic field, so only a few functions can be performed once manufactured. In addition, extra circuitry is required to convert electrical signals to spin waves for the initialization of the neural network.

Ferromagnetic (e.g. NiFe)

Figure 2.6. Magneto-electric cell [24].

### 2.2 Architecture Abstraction for Neurocomputing Based on Emerging Technologies

While proposed NN architectures based on emerging technologies that have been discussed in the previous section do not offer a complete, highly-efficient system solution for neurocomputing, co-design and co-optimization of future emerging devices and untried NN architectures could produce an efficient and practical neurocomputing system. Our cooptimization methodology consists of three key steps: i) determine device requirements for an efficient NN implementation, ii) explore emerging technologies and new device configurations based on these pre-determined requirements, and iii) develop novel neurocomputing systems using selected and/or proposed post-CMOS devices via technology-driven architecture optimization.

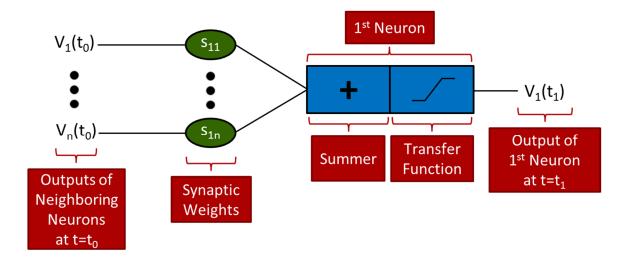

In this section we analyze a conceptual circuit diagram of a generalized neuron-synapse model that can be used for both feed-forward and recurrent (feedback) networks to explore what device specifications are required to construct it efficiently and robustly. Figure 2.7 demonstrates a typical neuron-synapse model that has been used in both phase- and amplitudebased NNs [2]-[3], [6]-[8]. In this model the outputs of neighboring neurons are multiplied with corresponding synaptic weights. Then the results of these multiplications are accumulated in the neuron circuit to generate the neuron state. Finally, neuron circuit takes this summation and generates the output of the neuron based on an activation function that generally corresponds to a variant of the sigmoid function. Based on this model we now determine required device properties for both analog and digital implementations.

Figure 2.7. Conceptual architecture of a typical neuron-synapse model.

#### 2.2.1 Digital Neural Networks

In a digital implementation both synaptic weights and neuron outputs are represented by binary bits (e.g., 4 or 5 bits [8], [25]). Multiplication of the neighboring neuron outputs by synaptic weights, summation of neural signals, and output generation based on this summation are done by standard digital logic gates. Therefore, a practical implementation of digital associative memories based on NNs requires *non-volatile* and *easily-programmable* logic families.

*Non-volatile logic*: Digital CMOS neurocomputing circuits consume a great deal of memory resources (e.g., D flip-flops, look-up tables and SRAM) for a sequential operation and storing data [8]. A non-volatile logic family provides storage at each logic stage, thereby eliminating the need for any extra memory element. By exploiting the inherent storage of logic state high throughput via deep pipelining can also be achieved [27].

*Simplified programmability*: Associative memories based on neurocomputing offer highlydistributed memory among small computational units in contrast to traditional computing schemes that require separate processor and memory. However, CMOS technology could not enable such a feature with today's technology. Therefore, the emerging technology device must provide easy, low-power re-configurability in order to enable highly-efficient digital associative memories.

#### 2.2.2 Analog Neural Networks

In an analog implementation the neuron outputs are in voltage form, and the synaptic weights are represented as resistances that adjust the amount of current going into the neuron input from each neighboring neuron. The neuron circuit must efficiently sum these currents and then generate an output voltage based on that summation. Hence, an efficient implementation of analog associative memories based on neurocomputing requires all of the followings: i) an efficient tunable resistance element to represent artificial synapses; ii) an efficient means of converting between digital control data and analog computation engine; iii) an efficient summing mechanism for neural signals; iv) an efficient device with electrically-isolated input and output terminals; and v) an efficient conversion of the summed currents into an analog voltage level.

*Tunable resistance element*: A programmable analog resistance is required to represent artificial synapses. Artificial synapses are used to represent couplings between neighboring neurons based on the set of patterns that will be stored in the system. When implemented as a tunable resistor the strength of these synapses can be gradually increased or reduced using a digital control data with 4-5 bits. Such resolution is sufficient enough for a hardware implementation of neurocomputing systems [2], [6], [8], [25]. Neurocomputers can also tolerate fuzziness on such resistances up to 15% [6], but still continue functioning correctly.

*Efficient D/A (digital-to-analog) conversion*: The control inputs for both synapse programming and neuron initialization are in digital form. Such digital data must be efficiently converted to a resistance value in a binary-weighted approach that is a typical feature of conventional DAC circuits. Hence, provided tunable analog resistance nature of an emerging technology device must be supported by such a property for an efficient NN implementation (i.e., digital control data applied to such a device must gradually alter its resistance in a binary-weighted fashion).

*Efficient summing mechanism for neural information processing signals*: As explained above, inputs to the neuron circuits coming from neighboring synapses are in current form. The device that is to be used for implementing artificial neurons must add such currents in a fast and compact manner without affecting the current level on artificial synapses.

*Electrically-isolated input-output terminals*: Since the input and output of the neuron circuits are in different forms (i.e., one is current, and the other voltage) they must not affect each other during neural evaluation. In other words, the output voltage must not impact the current level on artificial synapses, and currents coming from neighboring synapses must not leak into output path. This can be achieved by a device with electrically-isolated input-output terminals. This feature is also required to separate programming and reading paths of artificial synapses during neural evaluation (i.e., current passing through reading path of the device must not significantly affect its resistance). This would otherwise require special powering schemes and circuits, or tight integration with CMOS technology [9]-[19].

*Efficient conversion mechanism between the summed neural signals and neuron output*: Though an electrical isolation between the input and output paths of the device that will be used for efficiently building a neurocomputer is necessary, an efficient coupling mechanism between these two paths is required to convert the summation of neural signals into an analog output voltage using an inverter/buffer-like resistive divider (e.g., magnetic or thermal coupling). This provides a sigmoid-like transfer function for the neuron circuits.

An emerging technology that provides the aforementioned features in an efficient and compact way can enable a practical realization of an analog associative memory by representing each artificial neuron as a voltage divider with two tunable (pull-up and pull-down) resistors and each artificial synapse as a programmable resistor with 4 or 5 digital control bits.

# 2.3 Towards Highly-Efficient Associative Memories and Neurocomputing

Based on these requirements for both analog and digital architectures, we propose novel neurocomputing systems via a technology-driven architecture optimization in the following chapters that utilize various emerging technologies to create what might not be the definitive neural system, but could be a step toward a practical realization of a complete working system that could improve with future technology improvements and tuning.

It is important to note that both storage capacity and recognition accuracy of the proposed associative memories and neurocomputing architectures in the next chapters do not depend on the enabling devices and circuits, but on the selected training algorithms to calculate synaptic weights. Developing such algorithms, however, is not within the scope of this thesis. Moreover, the overall storage capacity can be further increased by hierarchical tree approach proposed in [20]. It is also possible to improve recognition capability of large neural systems by partitioning the network to process smaller parts of input patterns simultaneously (i.e., building smaller associative memories in parallel) while still having the nearest neighbor coupling within each computing unit. In such an approach the final output pattern can be easily obtained by combining the pattern retrieval results from each partitioned unit.

# Chapter 3 Fully-Digital Associative Memories and Neurocomputing

In this chapter we propose an approach for associative memories whereby the non-volatility offered by a newly-proposed magnetic logic family, *mLogic*, is exploited to construct fully-digital neurocomputing circuits with great efficiency [26]. This chapter first explains how to build mLogic circuits enabled by novel mCell devices, following a brief description for the structure and working mechanism of these devices. Second, it demonstrates our design approach for fully-digital NNs in application to CNN and ONN systems, along with related behavioral simulation results obtained from MATLAB. Last, it provides system-level comparison results with respect to 32nm digital CMOS implementations.

### 3.1 mCell: Non-Volatile Programmable Magnetic Device

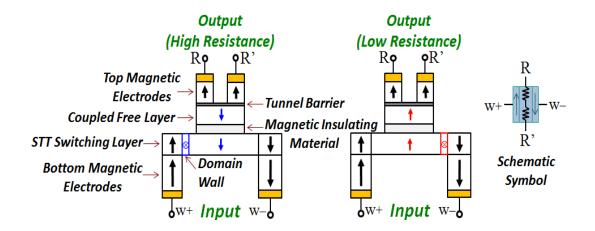

The mCell device that has been recently proposed in [27]-[29] is based on modification of an existing STT-MTJ-based MRAM (magnetic RAM) device [30] to incorporate an electrically isolating but magnetically coupling layer [31] between the STT switching layer and coupled free

layer, as shown in Figure 3.1. With this added isolation layer it becomes a four terminal device comprised of a write-path (w+, w-) and an electrically-isolated read-path (R, R) (see Figure 3.1). The magnetic moments of the top magnetic electrodes are in the same direction and permanently fixed, acting as magnetic reference layer. The STT switching layer is composed of a magnetic metal connecting the bottom magnetic electrodes. For these electrodes, the magnetic moments at the opposite ends are oriented in the opposite direction by a pinning mechanism. A domain wall (i.e., a transition region of rotating magnetic moments) is formed due to this opposite magnetization in the bottom electrodes.

Figure 3.1. 2D cross section view of mCell for the write-path current direction from left to right (left) and right to left (center), and its schematic symbol (right).

The domain wall in the STT switching layer can be moved by sending a small current pulse through the write-path, utilizing an STT effect. This also programs the magnetization of coupled free layer via magnetic coupling between that layer and the STT switching layer. The domain wall has only two stable locations, as shown in Figure 3.1. As such, the magnetization of coupled free layer becomes only parallel or antiparallel to the magnetic moments of the top electrodes. When these two are in parallel, the read-path resistance is low and vice versa. This makes mCell work in two stable resistance states that are determined by both direction and pulse duration of the write-path current. These resistances are set by a non-volatile magnetic polarization and therefore, remain the same when the device is powered off. With today's technology, the readpath resistance changes by only a factor of 2x [32] and has been best shown to change by 7x with special techniques [33]. It is expected that with improvements in magnetic devices and materials the high-to-low read-path resistance ratio will further increase, possibly surpassing what has been considered a 10x theoretical limit.

### 3.2 mLogic: Non-Volatile All-Magnetic Logic Technology

Although building non-volatile logic using mCells is challenging due to dynamic range for the read-path resistance as small as 2-3x with today's materials (e.g.,  $2.5k\Omega/1.25k\Omega$ ), a complete mLogic family has been recently developed based on novel current-steering technique [27]-[29]. Pulsed supply voltages that synchronize and power the logic circuits provide current-based logic programming signals via resistor dividers. Hence, both input and output signals of mLogic gates are of currents, not voltages. The corresponding input and output logic levels are then determined by the direction of these currents (e.g., a positive current corresponds to logic '1' while a negative current corresponds to logic '0').

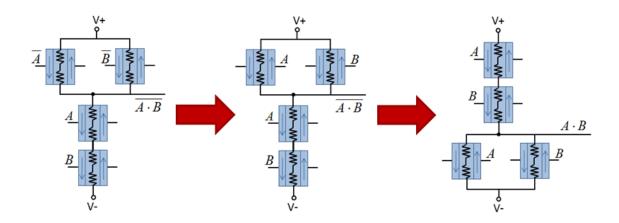

The mLogic NAND gate example implemented in a similar way to a CMOS NAND gate is illustrated in Figure 3.2 (left). A unique property of this logic technology is that inversion is free, since the read-path resistance of the mCell device is determined by the direction of its write-path current. For example, the *A* and *B* signals can be connected to the right terminal of the mCell devices in the pull-up network instead of connecting their inversions to the left terminal of those devices, as depicted in Figure 3.2 (center). Similarly, any other mLogic gate can be implemented without needing complementary inputs.

Moreover, a complementary mLogic gate can be obtained by simply interchanging the pullup and pull-down networks, since the output logic level is determined by the resistance ratio of these two networks. In this way, for instance, the mLogic NAND gate in Figure 3.2 (center) can be converted to an AND gate without requiring an inverter, as shown in Figure 3.2 (right). It is also important to note that inverters/buffers may still be used for signal buffering and restoration, or as delay elements in this logic family.

Figure 3.2. Traditional NAND (left), inversion-free NAND (center), and AND (right) gate examples using mLogic technology.

The vertical terminals of mCells (i.e., read-path) are characterized by two series MTJ resistances that are formed between the top electrodes and free layer via a tunnel barrier as shown in Figure 3.1. The horizontal path (i.e., write-path) for the programming current has small resistance as low as  $120\Omega$  [27]. This low input resistance represents the fanouts that are connected in series to form the current path that programs the states of mCells as shown in Figure 3.3. As such, each fanout mCell receives the same programming current, thereby preventing current shunting through unbalanced loads.

Even with only 2-3x read-path resistance change, with proper sizing and voltage levels the programming current signals can be properly steered to drive the logic states of the fanouts [27]-[29]. For example, referring to Figure 3.3, consider that the non-overlapping power clocks are positive ( $pClk_{1,2}+$ ) and negative ( $pClk_{1,2}-$ ) with respect to the ground shown at the end of the fanout chain. If the read-path resistance of mCell with the *A* input to the upward arrow is high resistance, and that to the downward arrow is low resistance, then the logic signal F would be a

current flowing from right to left in that figure. The direction of this current would program the states of mCells with the *F* input signal.

Figure 3.3. An inverter driving three two-input NOR gates. The fanout mCells are connected in series as highlighted by the red path. Two non-overlapping power clocks are applied to the driven and driving mLogic gates.

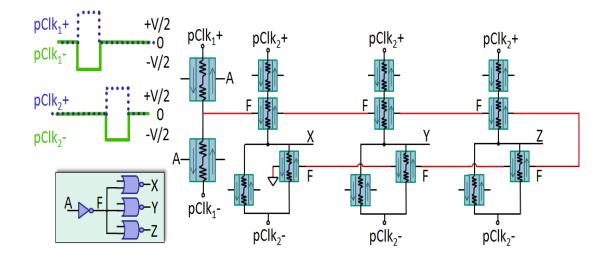

Moreover, efficient logic pipelining (see Figure 3.4) is enabled by the inherent storage of the mCell state and the non-overlapping power clocks [27]. In each pipeline stage the mLogic gates marked by  $P_1$ , and those marked by  $P_2$  are clocked with the non-overlapping  $pClk_1+/-$  and  $pClk_2+/-$  shown in Figure 3.4, respectively. This results in further power reduction for our proposed fully-digital associative memories in the next sections because only some of the mLogic gates will dissipate power at each time interval.

It is possible to integrate CMOS transistors with mCells to form a hybrid non-volatile logic family, but this eliminates some of the aforementioned energy-saving benefits. Moreover, there are integration issues that make this costly and impractical, since tightly integrating mCells and mLogic on top of CMOS would consume routing resources that are needed for all of the artificial synapses in our proposed fully-digital associative memory architectures. Instead, we envision a fully-functional mLogic chip that can be layered or stacked (using through-silicon vias) with CMOS only for power, clocking and input/output (I/O).

Figure 3.4. Pipelined mLogic gate stages [27]. Each pipeline stage is divided into two sub-stages. The mLogic gates in the first sub-stages and second sub-stages are clocked with two non-overlapping power clocks for power savings.

# 3.3 Proposed Fully-Digital ONN Architecture

ONNs are particularly interesting systems since they mimic nature and the human brain. In ONNs, memorized patterns are synchronized oscillatory states in which neurons periodically communicate with each other according to certain relations between their phases. This interaction between neurons is based on phase modulation (PM) encoding. The PM encoding neuron changes its firing pattern (i.e., at which time within the cycle the firing occurs) to represent its state. It is theoretically shown that ONNs can be built using PLLs [3], laser oscillators [35], and microelectromechanical system (MEMS) oscillators [36].

#### 3.3.1 Derivation of Discrete-Time ONN Dynamics

Referring to the PLL-based NN shown in Figure 1.2, its dynamics is given by [3]:

$$\stackrel{\bullet}{\theta_i} = \Omega + V(\theta_i) \sum_{j=1}^n s_{ij} V(\theta_j - \pi/2)$$

(4.1)

where  $\theta_i$  is the phase of the i<sup>th</sup> VCO,  $\Omega$ >>1 is the natural frequency of the system,  $s_{ij}$ 's are synaptic weights, and *V* is the VCO output signal. Since  $\Omega$ >>1, we can average Eq. 1 over time, which yields:

$$\stackrel{\bullet}{\theta_i} = \Omega + \sum_{j=1}^n s_{ij} H(\theta_j - \theta_i) \tag{4.2}$$

where the averaged transfer function *H* is:

$$H(\theta_j - \theta_i) = \lim_{T \to \infty} \frac{1}{T} \int_0^T V(\theta_i) V(\theta_j - \pi/2) dt .$$

(4.3)

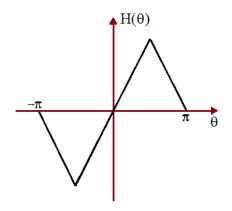

Various types of transfer functions are given in [3] based on the different PLL output waveforms. Since we discretize the whole system, any of them could be selected; however, transfer function corresponding to the rectangular waveform is the easiest one to discretize (see Figure 3.5). This transfer function has only three stable points at  $\theta = 0$ ,  $\pi$ , and  $-\pi$ . Therefore, synchronization is achieved only if all oscillatory neurons are in-phase or anti-phase with respect to each other.

Figure 3.5. Transfer function for fully-digital ONN.

Next we define excess phase as:

$$\phi_i = \theta_i - \Omega t \,. \tag{4.4}$$

Plugging (4.4) into (4.2) results in:

$$\phi_i = \sum_{j=1}^n s_{ij} H(\phi_j - \phi_i) .$$

(4.5)

Discretizing the continuous-time ONN system in (4.5) gives the discrete-time ONN dynamic equation as:

$$\phi_i[k+1] = \phi_i[k] + \sum_{j=1}^n s_{ij} H(\phi_j[k] - \phi_i[k])$$

(4.6)

where k is the iteration step. The training algorithm is applied to specify synaptic weights that represent the patterns that are stored in this system. Solutions to this difference equation then correspond to these stored patterns.

#### 3.3.2 Implementation of Fully-Digital ONN

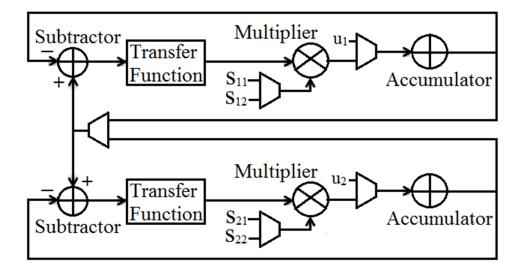

The proposed fully-digital ONN architecture shown in Figure 3.6 is the representation of the discrete-time ONN dynamic system in (4.6). One adder without a reset signal is needed to accumulate excess phase. The transfer function block in Figure 3.6 is the realization of H function drawn in Figure 3.5.  $u_1$  and  $u_2$  are the initial inputs for the first and second neurons, respectively.

Most importantly, efficient implementation of this discretized ONN system is enabled by the inherent storage of the non-volatile logic family that allows us to *digitally* represent oscillations in phase domain instead of converting phase-domain computations into voltage domain. With local storage of state we can easily track the accumulation of excess phase, thus transforming the

oscillator's function into digital domain. Moreover, phase relationships among artificial neurons are discretized via non-volatile storage by digitally representing the transfer function shown in Figure 3.5.

Figure 3.6. High-level circuit representation of the discrete-time ONN. The signal-selecting blocks are multiplexers.

The non-volatile logic with the inherent storage of state offers additional advantages: i) easy *programmability* without the need for extra memory; and ii) high throughput via a *fully-pipelined* architecture without the need for D flip-flops [27]. With inherent pipelining and simplified programmability, only a few hundred non-volatile logic cells are required to model each oscillatory neuron. With improvements in training algorithms for ONNs, even fewer logic gates would be needed. For example, the training algorithm proposed in [37] that can be potentially applied to any NNs used for associative memories is claimed to render implementation of sparsely-interconnected NNs possible. If it can be successfully applied to oscillatory associative memories as well, it will enable sparsely-interconnected ONNs, thus further simplifying the proposed ONN implementation.

#### 3.3.3 Behavioral Simulation

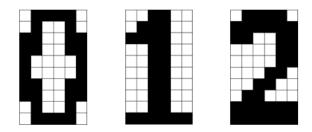

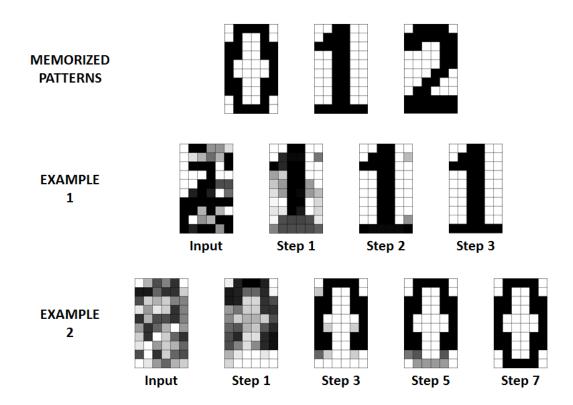

To validate the functionality of our discretized ONN system we generate a high-level behavioral model with MATLAB based on our proposed architecture that is shown in Figure 3.6. This model is formed by direct implementation of each individual block (i.e., multiplier, multiplexer, accumulator, subtractor, and transfer function) in this proposed architecture. Using pattern recognition example from [3], the 60-pixel bit patterns shown in Figure 3.7 are stored in the system via synaptic weights. We use *Hebbian Rule* to calculate these weights as described in [3].

Figure 3.7. 60-pixel memorized bit patterns. They are stored in the neural network via synaptic weights.

In our model we represent inputs and synaptic weights as 5-bit signed binary numbers. Therefore, 31 possible phase levels can be defined in this system. Moreover, number of step size to recognize the pattern would alter with different choices of representing data and how higher order bits generated during neural computation are handled.

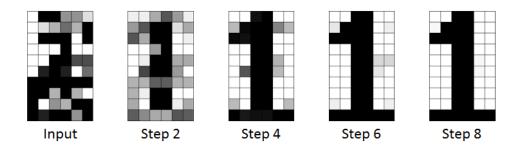

Figure 3.8 shows our first example with an input pattern that is generated as close to that used in [3] as possible. Eight steps are required to fully recognize the pattern. In this example, oscillatory associative memory gets locked to one of the stored patterns *as designated in the example in [3]*.

Figure 3.8. Pattern recognition process (Example 1). The initial input pattern is the distorted version of the bit pattern '1'.

Figure 3.9 demonstrates our second example using a different input pattern. Seven steps are required to fully retrieve one of the stored patterns. These examples verify that our proposed ONN system functions correctly, and does not lose any significant data due to discretization of system dynamics.

Figure 3.9. Pattern recognition process (Example 2). The initial input pattern is the distorted version of the bit pattern '0'.

#### 3.3.4 System-Level Comparison to 32nm CMOS Technology

We constructed our proposed ONN architecture in Figure 3.6 with CMOS and mLogic based on circuit simulation modeling for both. We assumed a fully-interconnected 60-neuron system to comply with behavioral simulation presented in the previous sub-section. Similarly, 5-bit signed binary numbers were chosen for inputs and synaptic weights. For the CMOS implementation we first generated a VHDL (VLSI hardware description language) based model for an oscillatory neuron and then compiled it using a logic synthesis tool (Synopsys Design Compiler) with 32nm CMOS logic library that completed the circuit optimization based on timing targets we provided. We verified the implementation of the same ONN architecture based on mLogic with +/-12.5mV supplies for buffers and multiplexers, and +/-50mV supplies for other logic gates using a circuit simulation with a physics-based device model for mCells [27]-[28].

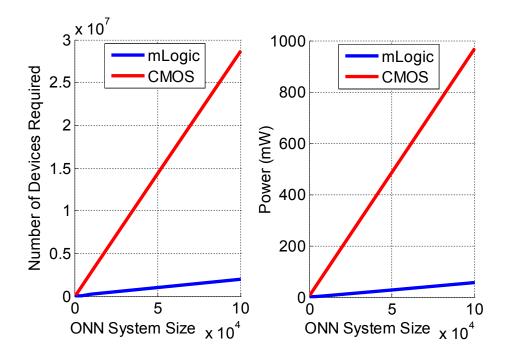

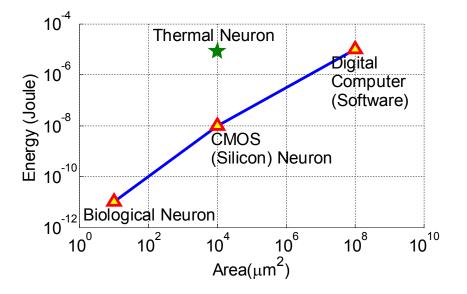

In both implementations each neuron consists of two major blocks: i) a computation block (CB) that performs neural computation; and ii) an interconnection block (IB) that stores synaptic weights and inputs them to the computation block in an orderly manner. With our 60neuron system example for each neuron the CMOS implementation with 0.7V supply requires 2168 transistors and 87.4µW power for CB, and 17208 transistors and 581µW power for IB. Nevertheless, for the same system the mLogic implementation per neuron requires 2238 mCell devices and 573µW power for CB, and 1200 mCell devices and 33µW power for IB. Hence, for a 60-neuron system the mLogic implementation represents a 5.6x improvement in the number of devices required while consuming comparable power as the CMOS implementation. With increase in the number of neurons, however, interconnections would dominate due to the fullyinterconnected architecture. Hence, for large-scale oscillatory associative memories the improvement with mLogic would reach approximately 15x for the number of devices required and 18x for power as shown in Figure 3.10. As explained in Section 4.3.1 the device count comparison fairly represents the area comparison, since nanoscale mCell and CMOS transistor occupy approximately the same area. Moreover, these comparisons do not consider the potential benefits of layout and stacking of this all-magnetic logic technology.

Figure 3.10. mLogic vs CMOS comparison per neuron for different ONN system sizes: Device count comparison (left) and power comparison (right).

# 3.4 Proposed Fully-Digital CNN Architecture

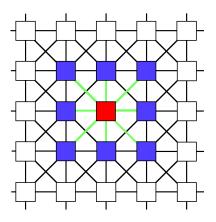

The CNN that was first proposed by L. O. Chua and L. Yang in 1988 [38] is a special class of NNs as it offers only local interconnections among artificial neurons. Regardless of the number of neurons in the CNN system, each neuron is connected to only neighboring neurons within a specified radius r and itself. For example, referring to a 2D CNN architecture shown in Figure 3.11, for r=1 the red cell in the center interacts only with the blue cells and itself, whereas it interacts with the white cells as well for r=2. This radius can be extended for better accuracy such that all neurons share one-to-one connections like other NN systems, but CNNs can be built for more efficient hardware implementations using the smallest possible radius that corresponds to only 9 connections for each neuron.

In CNNs each cell has an input, a state and an output, and interacts with the cells within its neighborhood r according to certain relations between their amplitudes. This interaction

between the CNN cells is based on amplitude modulation (AM) encoding. The AM encoding neuron changes its firing rate (i.e., the magnitude of its response over one cycle) to represent its state.

Figure 3.11. A 2D CNN illustrating neighboring cells for a CNN cell when *r*=1.

#### 3.4.1 Derivation of Discrete-Time CNN Dynamics

The conventional dynamic equation of a continuous-time CNN is given by:

$$\mathbf{x}_{i} = -\mathbf{x}_{i} + \sum_{j \in Neighbors of i} \mathbf{s}_{ij} G(\mathbf{x}_{j}) + \sum_{j \in Neighbors of i} \mathbf{b}_{ij} \mathbf{u}_{j} + I$$

(4.7)

where  $x_i$  is the state of the i<sup>th</sup> CNN cell,  $s_{ij}$ 's are feedback coefficients,  $b_{ij}$ 's are control coefficients,  $u_j$  is the input of the j<sup>th</sup> CNN cell, I is the bias term, and the activation function G is usually the saturation function defined as:

$$G(x) = \begin{cases} x & if \ -1 \le x \le 1 \\ 1 & if \ x > 1 \\ -1 & if \ x < -1 \end{cases}$$

(4.8)

We convert this continuous-time CNN dynamic equation in (4.7) into the discrete-time CNN dynamic equation as follows:

$$x_i[k+1] = \sum_{j \in Neighbors of i}^n s_{ij} G(x_j[k]) + I_i$$

(4.9)

where k is the iteration step and  $I_i$ , the bias term corresponding to the i<sup>th</sup> CNN cell, is given by:

$$I_i = \sum_{j \in Neighbors of i} b_{ij} u_j + I.$$

(4.10)

The training algorithm is applied to specify both feedback and control coefficients that represent the patterns stored in this system. Solutions to the difference equation in (4.9) then correspond to the stored patterns.

#### 3.4.2 Implementation of Fully-Digital CNN

Using the discrete-time CNN dynamics in (4.9) we construct our proposed fully-digital CNN system. Its conceptual diagram consisting of two neurons is shown in Figure 3.12. The signal-selecting blocks in that figure are multiplexers. Most importantly, the implementation of this discretized CNN system is enabled by the non-volatile logic. The inherent storage of logic state offers simplified *programmability* and highly-efficient *pipelined* stages, thereby eliminating the need for look-up tables and D flip-flops. As such, only a few hundred mLogic gates would be required to model each artificial neuron.

#### 3.4.3 Behavioral Simulation

As an illustrative example we have generated a high-level behavioral model for the proposed CNN architecture in MATLAB, assuming zero bias terms for all artificial neurons. This model consists of individual implementations of each block shown in Figure 3.12. Similar to pattern recognition examples in Section 3.3.3 we use pattern recognition example demonstrated in [3]. The feedback coefficients are calculated based on the 60-pixel memorized bit patterns shown in Figure 3.13 using the synthesis procedure as described in [39].

Figure 3.12. High-level circuit representation of the discrete-time CNN.

In this model 5-bit binary numbers are assumed to be used for inputs and feedback coefficients. As such, 31 possible gray-scale color levels can be defined in the model. Moreover, the number of steps to retrieve one of the stored patterns would alter with different choices of representing data and how higher order bits that are generated during neural computations are handled.

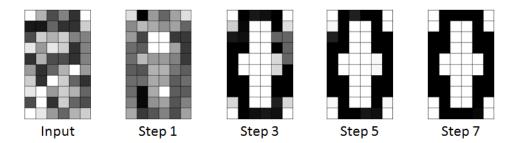

For our first pattern recognition example in Figure 3.13 we use the same input pattern given in the example in [3]. The generated CNN system is locked to the stored bit pattern '1' at three steps *as in the case in [3]*. In our second pattern recognition example we use the distorted input pattern '0'. This time seven steps are required to recognize the pattern. All the results presented here comply with the results obtained for a fully-digital ONN in Section 3.3.3 with exception of time evolution of the retrieved output patterns, thereby confirming correct functionality of our proposed fully-digital CNN system.

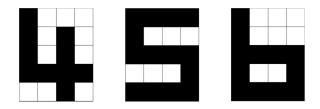

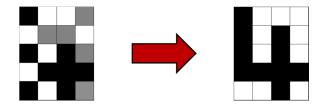

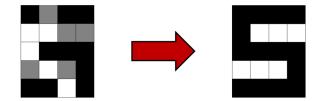

Figure 3.13. Memorized bit patterns and pattern recognition examples for our proposed fully-digital CNN system.

#### 3.4.4 System-Level Comparison to 32nm CMOS Technology

We constructed our proposed fully-digital CNN architecture shown in Figure 3.12 using mLogic technology and compared it with the best-reported CMOS-based digital CNN topology [8] that is implemented here using logic gates for comparison purposes. This CNN system implemented in CMOS leverages a novel multiplication scheme that significantly reduces the number of CMOS transistors required. We used 5-bit binary numbers for inputs and feedback coefficients while assuming zero bias terms for all artificial neurons. The neural networks were built using the smallest possible interconnections among artificial neurons – that is, each neuron has only 9 connections.

For the CMOS implementation we first generated a behavioral model for the best-reported CNN hardware in [8] using a hardware description language (VHDL). Then we compiled it with 32nm CMOS standard logic library using a logic synthesis tool (Synopsys Design Compiler) that performed a circuit optimization based on our timing constraints. We used a 0.7V supply voltage, and a 500MHz clock for synchronization and pipelining.

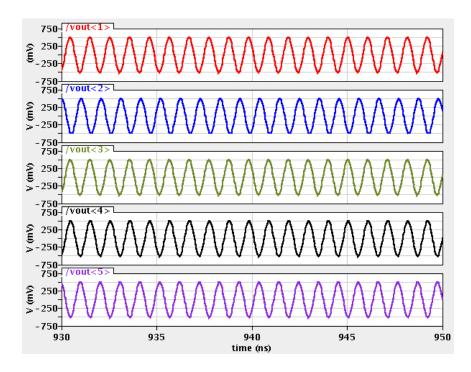

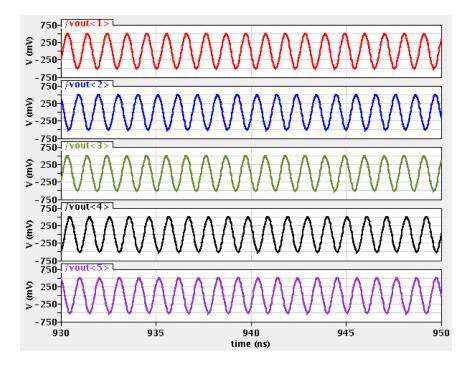

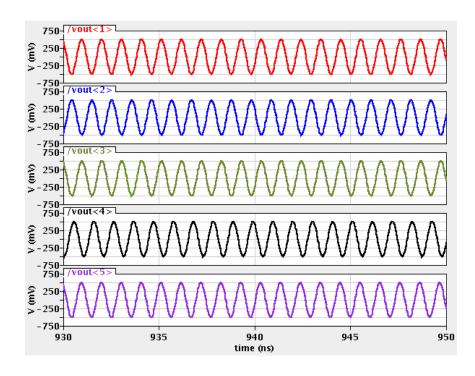

For the mLogic implementation we used the Verilog-A model of the mCell device that was written in SPICE for circuit simulations using a first-order approximation of the underlying physics [27]-[28]. We applied +/-10mV power supplies for buffers and +/-25mV power supplies for the remaining mLogic gates. Again we used the same clock frequency of 500MHz as in the CMOS implementation.