# Self-healing Narrowband MEMS Filter Design for RF Receivers

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR

THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN

ELECTRICAL AND COMPUTER ENGINEERING

Jinglin Xu

B.S., Optoelectronics Engineering, Zhejiang University

M.S., Electrical and Computer Engineering, Carnegie Mellon University

PhD Thesis Committee:

Prof. Gary K. Fedder (Advisor) Prof. Larry Pileggi (Advisor) Prof. Gianluca Piazza Dr. Cheng-Yuan Wen (Nvidia)

> Carnegie Mellon University Pittsburgh, PA

> > May, 2017

© Jinglin Xu 2017 All rights reserved

## Acknowledgements

First, I would like to thank my advisor Professor Gary K. Fedder for all his support and guidance throughout the past five years. His enthusiasm for emerging MEMS technology and insight into cutting edge research topics has been the initial drive of my study. His dedication to work and determinant pursuit of truth has set a model for me as a researcher.

Second, I would like to thank my co-advisor Professor Larry Pileggi. It was him who introduced me to this project and guided me to RF circuit design using statistical calibration, during which I came up with the method in this thesis. His intelligent advice and generous support have always been a reliable guarantee for my study.

Next, I would like to thank the rest of my dissertation committee members. Professor Gianlucca Piazza's pioneering works in AlN resonator filters is the milestone that makes this research possible. His instructions in the MEMS fabrication has been essential to the demonstration of this thesis work. Dr. Cheng-Yuan Wen was a senior student in our group who also worked on CMOS-device integration. His thesis work has been an inspiration for the design in this research.

I would also like to thank my fellow lab members. Renzhi Liu has patiently taught me how to be an analog designer when I was a rookie. As a senior student to me, his advices also helped me to go through graduate student life. Shaolong Liu and Thomas Jackson entered the Ph.D. program at the same year as I did. I appreciate all the collaborations we have in classes as well as in research projects with the thoughtful discussions and sincere advices. I would also like to thank the rest of the current and past lab members in Professor Fedder's and Professor Pileggi's groups who overlapped with me and friends who helped me in my thesis work: Abhay Kochhar, Abhishek Sharma, Ahmad Khairi, Ahmed Hussein, Albert Patterson, Amritanshu Pandey, Andy Yang, Ayan Biswas, Bishnu P Das, Congzhong Guo, Changting Xu, Chengyang Wu, Cristian Cassella, Daniel Wei, David Bromburg, Ekin Sumbul, Emad Mehdizadeh, Enes Calayir, Erdinc Tatar, Fazle Sadi, Hai li, Hoe Joon Kim, Jason Gao, Jeronimo Segovia, Joe Sweeney, Kai-Chun Lin, Kaushik Vaidyanathan, Kuntal Shah, Lionel Wong, Marko Jereminov, Martin Wagner, Mats

Forssell, Mayler Martins, Mary Beth Galanko, Meric Isgenc, Min Xu, Mohamed Omar Darwish, Naeem Maroof, Nai Kuei-Kuo, Ozan Iskilibli, Qiuling Zhu, Rahul Singh, Rongye Shi, Sam Pagliarini, Sean Yen, Shih-Chang Hung, Siddhartha Ghosh, Sudipta Bhuin, Suresh Santhanam, Vanessa Chen, Vehbi Calyir, Xi He and Xiao Chuan Ong. I treasure the years that we spent together at CMU. Last but not least, I would like to thank my boyfriend Ryan Xu. I feel lucky to have met you in CMU. Without your sweet company the bitterness in the final year of my Ph.D. would be intolerable.

The work presented in this dissertation was supported in part by the Intelligence Advanced Research Program Agency and Space and Naval War-fare Systems Center Pacific under Contract No. N66001-12-C-2008.

Finally, I would like to thank my parents. They raised me as a healthy and positive individual to overcome any unexpected difficulties. They have always patiently encouraged me when I felt unsure about myself. Words cannot express my grate for their unconditional support and love in every way of my life.

## Abstract

As the radio frequency (RF) spectrum is becoming increasingly occupied, receivers are designed to resist out-of-band interferers. Due to lack of on-chip high quality factor (high-Q) filters, conventional receivers pursue frequency translation using mixers and VCOs, which inevitably increases power consumption and area and degrades noise and linearity. The piezoelectric AlN contour mode resonator filter, with its high-Q, low insertion loss and compatibility with CMOS integration, has emerged as a viable option for a high performance channel selection filter as the first stage of a direct sampling receiver. However, maintaining frequency precision for any high Q filter is challenging in the presence of both random and systematic process variations. To address this, the extended statistical element selection (ESES) method is applied to compensate for the frequency variations using a combinatorial redundancy scheme.

This research explores the feasibility, advantages, implementation, and testing of a heterogeneously integrated switchable AIN filter system that can minimize parasitics and "self-heal" to increase yield and to realize uniform loading. In addition, several design techniques are proposed to implement the self-healing filter to a 1 GHz receiver frontend, including breaking LNAs into sub-LNAs to select sub-filters and using current summing to uniformly combine signal outputs. To control parasitics, 3-D integration is used to limit the interconnection lengths between the CMOS switches and the AlN resonators.

# Contents

| 1 | Introduction                                                               | 1  |

|---|----------------------------------------------------------------------------|----|

|   | 1.1 Motivation                                                             | 1  |

|   | 1.2 Background                                                             | 2  |

|   | 1.2.1 RF receiver design challenges                                        | 2  |

|   | 1.2.2 AIN MEMS resonators and filters                                      | 3  |

|   | 1.2.3 Process variations in AlN MEMS resonator filters                     | 7  |

|   | 1.2.4 Conventional tuning and trimming methods in MEMS resonator filters   | 9  |

|   | 1.2.5 Statistical Element Selection (SES) method in MEMS resonator filters | 10 |

|   | 1.3 Proposed system and contributions                                      | 12 |

| 2 | Wide range calibration approach                                            | 16 |

|   | 2.1 ESES method                                                            | 16 |

|   | 2.2 ESES design optimization                                               | 18 |

|   | 2.2.1 Filter and resonator statistical data collection                     | 18 |

|   | 2.2.2 Basic layout pattern                                                 | 22 |

|   | 2.2.3 Layout placement rotations for a pseudo-variation sequence           | 23 |

|   | 2.2.4 Monte Carlo simulation for success rate evaluation                   | 26 |

|   | 2.2.5 Optimization of pseudo-variation sequence                            | 29 |

| 3 | ESES Filter Array Implementation and Measurement                           | 33 |

|   | 3.1 Finger width modulation of resonator center frequency                  | 33 |

|   | 3.2 Fine frequency tuning filter fabrication and measurement               | 35 |

|   | 3.2.1 MEMS only fabrication process flow                                   | 35 |

|   | 3.2.2 Fine finger width modulation test design and measurement             | 36 |

|   | 3.2.3 ESES reconfigurable filter design and measurement                    | 38 |

| 4 | Reconfigurable receiver frontend design                                    | 40 |

|   | 4.1 Systematic specifications                                                                                                                                                                                                                                             | 40             |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|

|   | 4.1.1 Communication standards                                                                                                                                                                                                                                             | 40             |  |

|   | 4.1.2 Switching method                                                                                                                                                                                                                                                    |                |  |

|   | 4.1.3 Proposed system                                                                                                                                                                                                                                                     |                |  |

|   | 4.2 LNA design                                                                                                                                                                                                                                                            |                |  |

|   | 4.2.1 LNA topology                                                                                                                                                                                                                                                        |                |  |

|   | 4.2.2 Input impedance matching                                                                                                                                                                                                                                            |                |  |

|   | 4.2.3 Noise figure                                                                                                                                                                                                                                                        |                |  |

|   | 4.2.4 Linearity                                                                                                                                                                                                                                                           | 50             |  |

|   | 4.2.5 Power optimization                                                                                                                                                                                                                                                  | 50             |  |

|   | 4.2.6 Switching and summing                                                                                                                                                                                                                                               | 53             |  |

|   | 4.2.7 System parasitic optimization                                                                                                                                                                                                                                       |                |  |

| 5 | Circuit implementation and measurement                                                                                                                                                                                                                                    | 56             |  |

|   | 5.1 Stand-alone frontend components testing                                                                                                                                                                                                                               | 58             |  |

|   |                                                                                                                                                                                                                                                                           |                |  |

|   | 5.1.1 Stand-alone LNA design and testing                                                                                                                                                                                                                                  |                |  |

|   | <ul><li>5.1.1 Stand-alone LNA design and testing</li><li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li></ul>                                                                                                                                                  |                |  |

|   |                                                                                                                                                                                                                                                                           | 60             |  |

|   | 5.1.2 Stand-alone Balun, VGA and Buffer stage testing                                                                                                                                                                                                                     | 60<br>61       |  |

|   | <ul><li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li><li>5.2 MEMS Filter fabrication and testing</li></ul>                                                                                                                                                   | 60<br>61<br>61 |  |

|   | <ul> <li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li> <li>5.2 MEMS Filter fabrication and testing</li> <li>5.2.1 MEMS with Thin Film Encapsulation Fabrication Process Flow</li> </ul>                                                                      |                |  |

|   | <ul> <li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li> <li>5.2 MEMS Filter fabrication and testing</li> <li>5.2.1 MEMS with Thin Film Encapsulation Fabrication Process Flow</li> <li>5.2.2 MEMS with Thin Film Encapsulation Device Measurements</li> </ul> |                |  |

|   | <ul> <li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li> <li>5.2 MEMS Filter fabrication and testing</li></ul>                                                                                                                                                 |                |  |

|   | <ul> <li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li></ul>                                                                                                                                                                                                  |                |  |

|   | <ul> <li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li></ul>                                                                                                                                                                                                  |                |  |

|   | <ul> <li>5.1.2 Stand-alone Balun, VGA and Buffer stage testing</li></ul>                                                                                                                                                                                                  |                |  |

| 4  | Conclusion and future work |  |

|----|----------------------------|--|

|    | 4.1 Conclusion             |  |

|    | 4.2 Future work            |  |

| Re | ference                    |  |

# List of figures

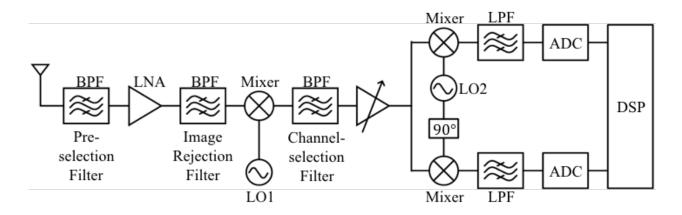

| Figure 1-1 (a) Super-heterodyne receiver architecture. (b) Direct sampling receiver architecture3                    |

|----------------------------------------------------------------------------------------------------------------------|

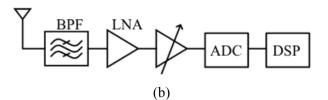

| Figure 1-2 AlN contour-mode resonator (a) SEM picture of the resonator. (b) Diagram of the resonator. (c)            |

| Lumped circuit model of the resonator                                                                                |

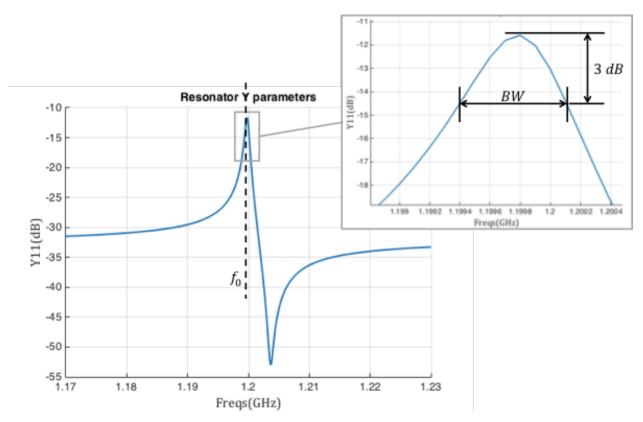

| Figure 1-3 Input admittance, Y11, of an AlN two-port resonator with the output port short-circuited5                 |

| Figure 1-4 AlN resonator filter schematic model                                                                      |

| Figure 1-5 Resonator center frequency data collected from 40 resonators on 4 chips                                   |

| Figure 1-6 Proposed receiver frontend                                                                                |

| Figure 2-1 Wafer-level center frequency profile measurement                                                          |

| Figure 2-2 Plane model for cell-level center frequency distribution                                                  |

| Figure 2-3 Histogram of f0 plane parameters, taken from measurements                                                 |

| Figure 2-4 Histogram of resonator parameters, taken from measurements                                                |

| Figure 2-5 Basic layout for ESES filter array                                                                        |

| Figure 2-6 Frequency interval for the pseudo frequency in ESES filter array                                          |

| Figure 2-7 Frequency rotation for the pseudo frequency in the ESES filter array                                      |

| Figure 2-8 A 4×4 sub-filter array on a 2 mm by 2 mm die with center frequency pseudo-variation27                     |

| Figure 2-9 Flow chart for Monte Carlo Simulation                                                                     |

| Figure 2-10 Success rate at each rotation with Fps from 800 to 1200 kHz. Table 2-3 and figure 2-6 define             |

| the rotations specified in the legends                                                                               |

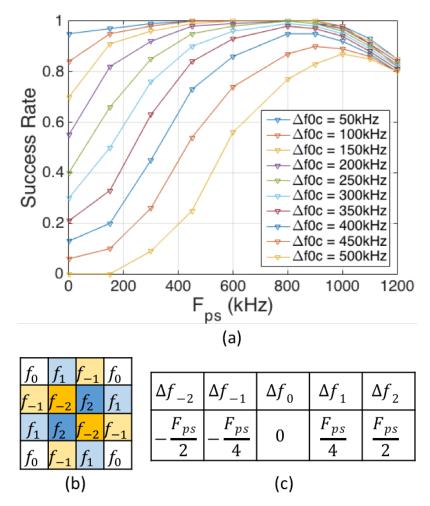

| Figure 2-11 (a) Success rate at different $\Delta f0c$ for ESES sub-filter array with (b) layout rotation 42 and (c) |

| even interval                                                                                                        |

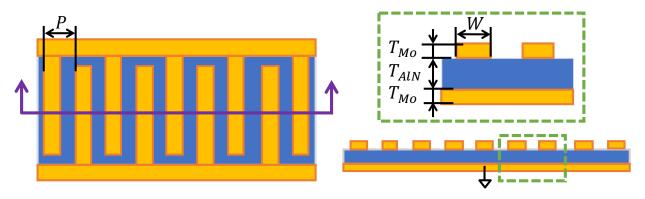

| Figure 3-1 Loading effect of metal fingers on AlN resonator                                                          |

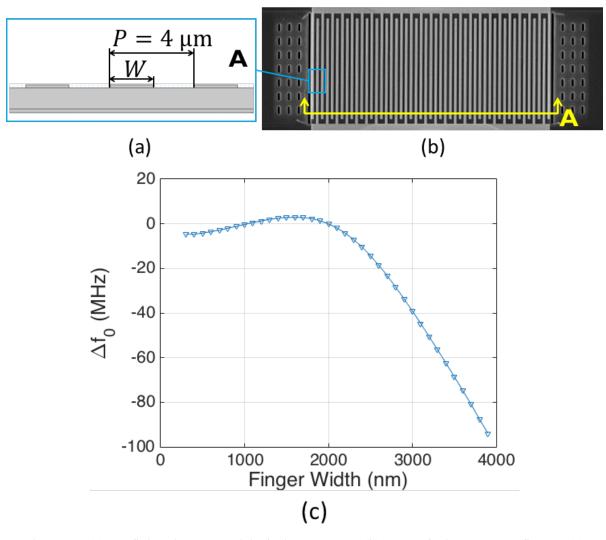

| Figure 3-2 (a) 2D finite-element model of AlN resonator. (b) SEM of AlN resonator fingers. (c)                       |

| Simulated frequency shift vs. layout finger width                                                                    |

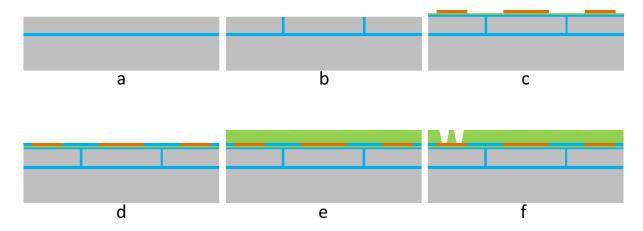

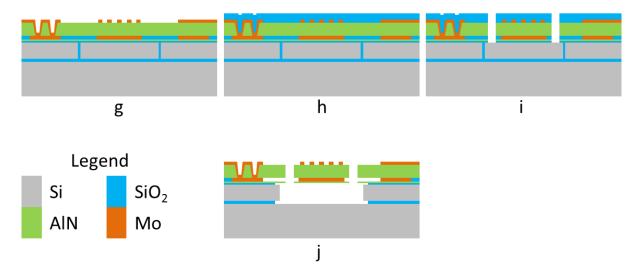

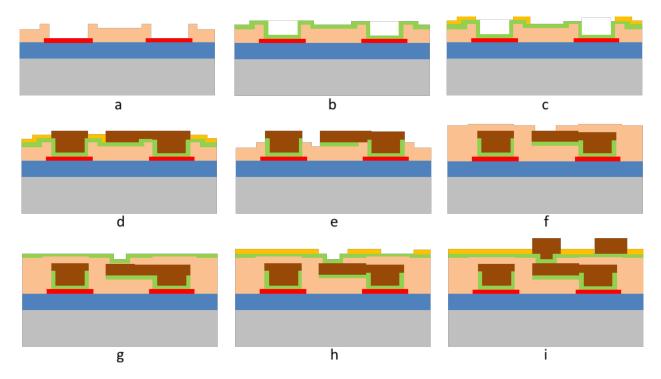

| Figure 3-3 MEMS only process flow: (a) Initial wafer. (b) Formation of isolation trench. (c) Deposition |

|---------------------------------------------------------------------------------------------------------|

| and patterning of bottom molybdenum. (d) Planarization. (e) Deposition of aluminum nitride. (f)         |

| Etching of vias. (g) Deposition and patterning of top molybdenum. (h) Deposition of silicon dioxide     |

| passivation. (i) Etching of release holes. (j) Xenon difluoride release and vapor hydrofluoric acid     |

| etch                                                                                                    |

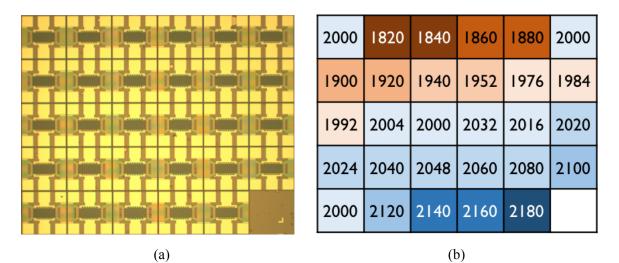

| Figure 3-4 Test chip for fine frequency shift using finger width modulation                             |

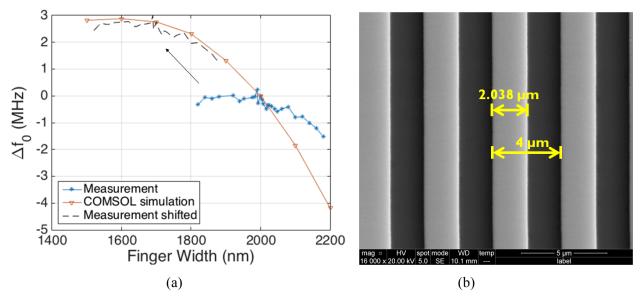

| Figure 3-5 (a) Center frequency shift vs. finger width adjustment (b) SEM image of resonator fingers    |

| designed to be 2 µm with a 4 µm pitch                                                                   |

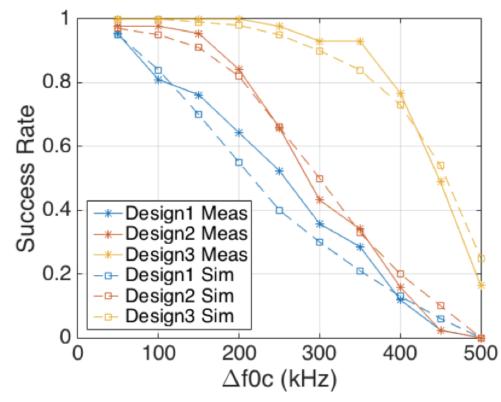

| Figure 3-6 Measured and simulated filter success rate                                                   |

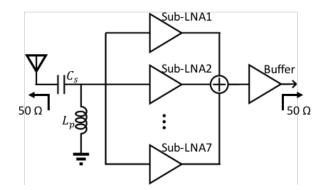

| Figure 4-1 Switching scheme using sub-LNAs and ground switches                                          |

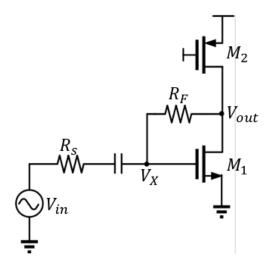

| Figure 4-2 Resistive feedback common source stage                                                       |

| Figure 4-3 Resistive feedback noise canceling LNA                                                       |

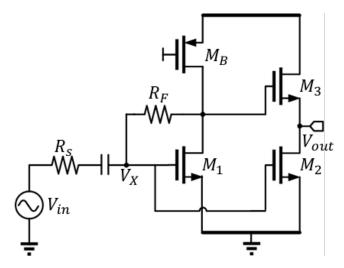

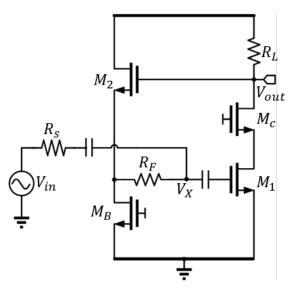

| Figure 4-4 Active feedback LNA                                                                          |

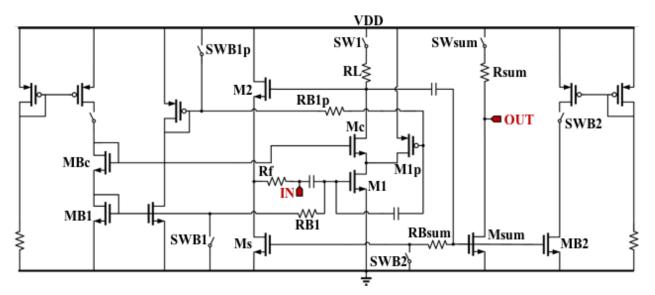

| Figure 4-5 Active feedback LNA circuit schematic                                                        |

| Figure 4-6 LNA design parameter optimization                                                            |

| Figure 4-7 LNA design parameter optimization                                                            |

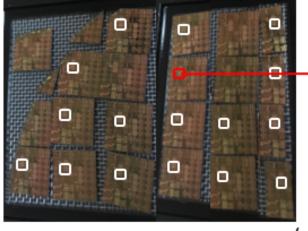

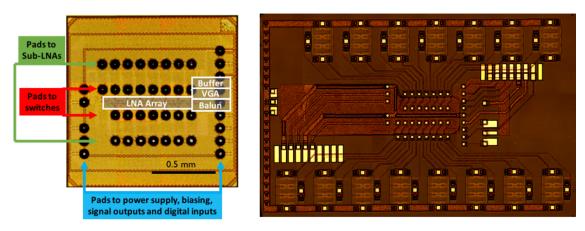

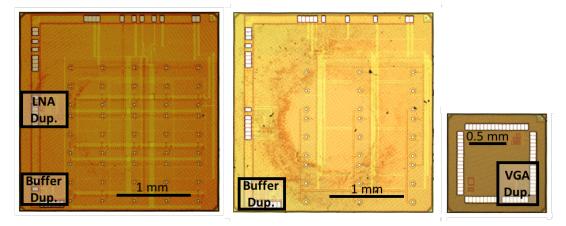

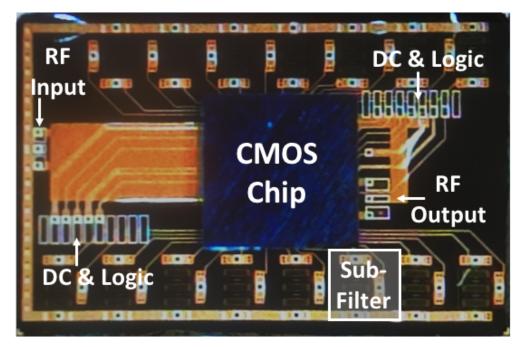

| Figure 5-1 Optical image of MEMS and CMOS chips for flip-chip integration                               |

| Figure 5-2 Optical image of frontend duplication circuits                                               |

| Figure 5-3 Diagram of LNA duplication circuit measurement                                               |

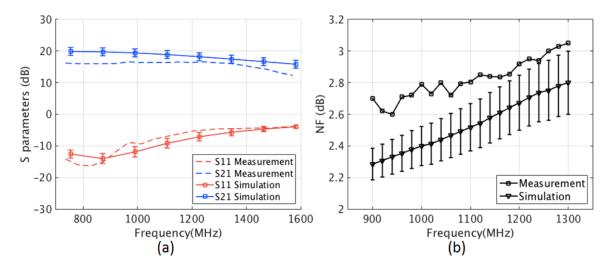

| Figure 5-4 Measurement results of LNA duplication (a) S21 and S11 of                                    |

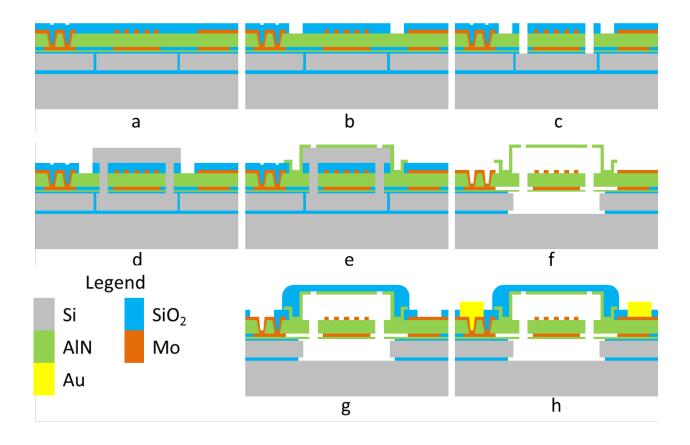

| Figure 5-5 MEMS with TFE process flow: (a) Device fabricated through MEMS only process flow up to       |

| step h in Figure 3-3(h). (b) Etching of encapsulation anchor. (c) Etching of release holes. (d)         |

| Formation of sacrificial silicon. (e) Deposition and patterning of AlN capping layer. (f) Xenon         |

| difluoride release and vapor hydrofluoric acid etch. (g) Deposition and patterning of Silicon dioxide   |

| sealing layer. (h) Deposition of under bump metallization                                               |

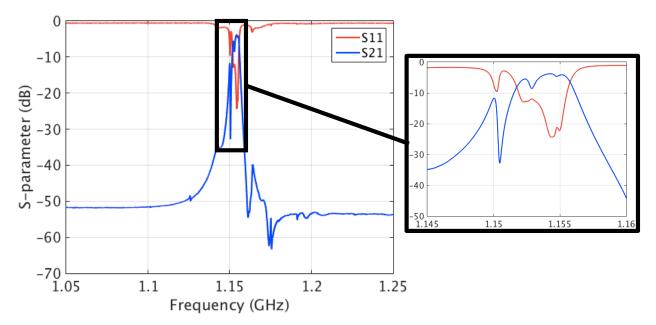

| Figure 5-6 S-parameters of 2-port AIN MEMS characterization filter matched to 350 Ω63                   |

| Figure 5-7 Process flow for RDL fabrication                                                              |

|----------------------------------------------------------------------------------------------------------|

| Figure 5-8 Model for RDL routing wire parasitics                                                         |

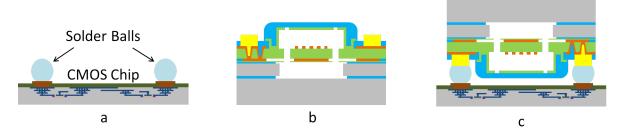

| Figure 5-9: Flip chip bump bonding (a) CMOS chip with solder balls. (b) MEMS Chip. (c) MEMS chip         |

| flip chip bonded to CMOS chip                                                                            |

| Figure 5-10 Optical image of flip-chip stack                                                             |

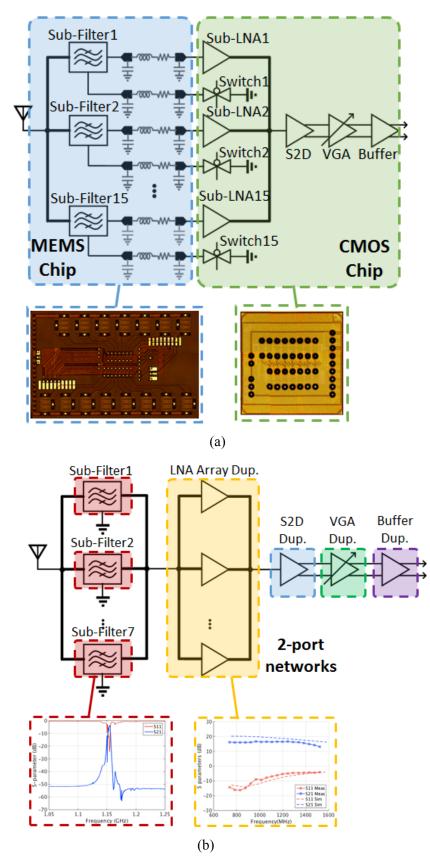

| Figure 5-11 Measurement diagram of (a) flip-chip bonded frontend (b) calculation of cascaded frontend    |

|                                                                                                          |

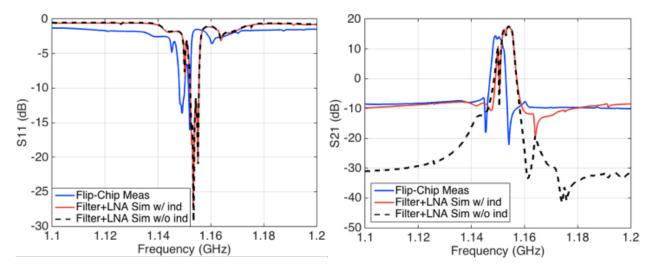

| Figure 5-12 S-parameters for the flip-chip bonded frontend and the calculation of cascaded frontend7     |

| Figure 5-13 Model of feedthrough parasitics                                                              |

| Figure 5-14 S-parameters for the flip-chip bonded frontend with different number of branches selected .7 |

| Figure 5-15 S-parameters for the flip-chip bonded frontend with different single branches selected7      |

| Figure 5-16 Capacitive loading from unselected sub-filter-LNA branches                                   |

# List of tables

| Table 1-1 Statistical study of AlN resonator filters.    9                                             |

|--------------------------------------------------------------------------------------------------------|

| Table 2-1 Performance statistics of standalone MEMS filters for 1136 samples measured across 71 dies.  |

|                                                                                                        |

| Table 2-2 Performance statistics of standalone MEMS resonator for 304 samples measured across 19 dies. |

|                                                                                                        |

| Table 2-3 Combinations of frequency interval for the pseudo frequency in ESES filter array24           |

| Table 2-4 Combinations of frequency rotation for the pseudo frequency in the ESES filter array24       |

| Table 2-5 Targets for success rate in Monte Carlo simulation.    28                                    |

| Table 3-1 Design 1-3 finger widths and actual Fps.    39                                               |

| Table 4-1 LTE E-UTRA specifications                                                                    |

| Table 4-2 Simulated S-parameter of ground switching    43                                              |

| Table 5-1 Testing result of receiver front-end stages    60                                            |

| Table 5-2 Performance for the flip-chip bonded frontend and the calculation of cascaded frontend71     |

# **1** Introduction

### **1.1 Motivation**

Emerging MEMS resonators are exciting candidates for high quality filtering elements [1]. Among all MEMS resonator materials, Aluminum Nitride (AlN) contour mode resonators (CMR) have demonstrated the potential for high quality factor (Q) filters with varying frequencies on a single chip [2]. This motivates the implementation of such devices in software-defined radio (SDR) [3,4,5], where frequency selection can be achieved via an array of switchable filters. Despite the promising features of AlN resonator filters, challenges of process variation and of parasitic capacitance and inductance exist as barriers to realizing the full potential in integrated receiver applications. To address these challenges, the goal of this research is:

Designing and testing a heterogeneously integrated switchable AlN filter system that can minimize parasitics and "self heal" to increase yield and realize uniform loading.

For such a system to *self heal*, the filter will reconfigure its circuit structure by digital control to calibrate its center frequency ( $f_0$ ), bandwidth (BW), insertion loss (IL) and out-of-band rejection (OBR) to meet the system specifications. The calibration range is designed to cover process and environmental variations so that one design can adjust to various conditions and all of the designs in aggregate can achieve yield improvements.

### **1.2 Background**

### 1.2.1 RF receiver design challenges

With the rapidly growing wireless communication technology, modern electronic devices: smart phones, fitness monitors and sensor networks are required to be compatible with multiple communication standards. This puts pressure on the RF components (e.g. receivers) to be able to function under strong interferences. Due to non-linearity in the transistor based components, interferers in other frequency channel can fold into the desired signal channel. When the interference power is strong, the folded components can exceed the receiver dynamic range, causing gain degradation during the signal amplification. Furthermore, if the interferer is a modulated signal, modulation can transfer from the interferer to the desired signal.

To avoid signal corruption from interference, conventional receiver architectures incorporate multiple filtering stages. The most widely used configuration in RF receivers is the super-heterodyne architecture [25]. Shown in Figure 1-1a, the received signal is first filtered by a pre-selection filter, amplified by the LNA and then passes through an image-rejection filter before translated from RF to IF. Following this stage, the signal is again filtered and demodulated to baseband. The second mixing stage can be I/Q modulation [25] to retrieve better signal information. Super-heterodyne architecture relies on multiple filtering and frequency translation components, making the receiver bulky and challenging for integration.

Figure 1-1 (a) Super-heterodyne receiver architecture. (b) Direct sampling receiver architecture.

A more simplified architecture uses direct sampling, as shown in Figure 1-1. After going through a channel selection filter, the signal of a desired channel is selected. Following amplification by the LNA, the signal is directly sampled by a sub-sampling ADC. The sub-sampling operation has a frequency translation effect, bringing the signal to base band while being digitized. This architecture relies on the first channel selection filter to suppress strong interferers. Since an interferer may fall only one or two channels away from the desired signal, the filter must provide a very high selectivity (i.e., a high Q). Moreover, during the sub-sampling stage, the aliasing effect will fold noise from bands at all integer multiplications of sampling frequency to the base-band, which will desensitize the digitization stage. This requires the filter to further suppress out-of-band noises to limit the overall folded noise level.

Another challenge with the channel selection filter is due to the fact that a different carrier frequency may be allocated to the user at different times, since such a filter would need a variable, yet precise, center frequency [26]. The variability can be fulfilled by adding switchable multi-frequency branches. The precision requirement is a property hard to reach, especially for high Q filters. For mechanical filters, center frequency is determined by device parameters including effective density and effective Young's modulus, which are easily affected by process induced variations. Change of thickness as trivial as 2 nm can cause center frequency shift by a few MHz, which is the channel bandwidth for some applications.

Based on the discussion above, to simplify the receiver architecture without sacrificing system performance, a channel selection filter that is highly selective, easily integrated and robust in terms of center frequency against process variations is needed.

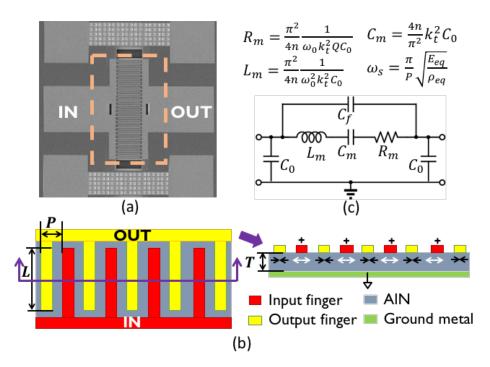

#### **1.2.2 AIN MEMS resonators and filters**

The AlN CMR resonator is part of a class of piezoelectric resonant devices that are able to span a broad range of frequencies from a few MHz up to GHz on the same silicon chip [6]. These resonators can achieve quality factors above 1,000 in air over the entire frequency spectrum [7]. Figure 1-2a is an SEM image of a two-port AlN CMR resonator. An AlN film is sandwiched between top electrodes (input and output) and bottom plate (ground). When applying an electric field across the film, the AlN structure expands laterally. The film can be excited in contour-mode resonant vibrations via the piezoelectric coefficient  $d_{31}$  as long as the signal frequency coincides the device natural frequency  $f_o$ , which is set by the pitch of the electrode, *P*.

Figure 1-2 AlN contour-mode resonator (a) SEM picture of the resonator. (b) Diagram of the resonator. (c) Lumped circuit model of the resonator.

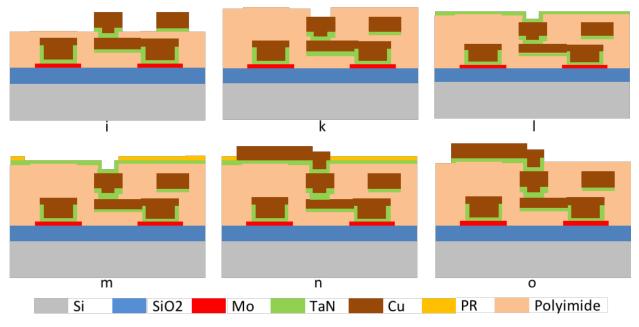

The signal in the mechanical domain is transmitted in the AlN film through energy exchange between elastic energy (stress) and kinetic energy (mass motion), which can be modeled by a mechanical secondorder system determined by mass density  $\rho$ , Young's modulus *E*, quality factor *Q*, and device geometry. Due to the similarity between the mechanical system to an *RLC* second-order circuit, the AlN resonator is modeled using the Butterworth-Van Dyke model [8]. The lumped circuit components are derived from the material parameters and the device dimensions (Figure 1-2c). The electrode length L, electrode number n and the AlN film thickness T set the resonator motional resistance  $R_m$ , intrinsic capacitance  $C_0$  and the resonant tank  $L_m$ ,  $C_m$ . The electrical and mechanical coupling is represented by coupling coefficient  $k_t^2$  and is determined by the ratio of  $C_m$  and  $C_0$ . The transfer function of the *RLC* tank takes the form of a resonator with capacitive feedthrough (as illustrated in Figure 1-3).

Figure 1-3 Input admittance, Y11, of an AlN two-port resonator with the output port short-circuited.

To build a robust channel selection filter and to achieve the desired filter performance specifications requires proper interconnection of multiple AlN two-port resonators. A switchable array of smaller "sub-filters" provides the capability to select the best combination of parallel-connected sub-filters in order to implement self healing. This section describes the design considerations involved in the self-healing filter array.

AlN contour mode resonator-based filters must meet specific design goals for the application of channel selection. First, fractional bandwidth (FBW, the ratio between the filter 3 dB BW and the center

frequency  $f_0$  ) needs to be small enough to achieve channel selection at RF frequencies. Second, the outof-band rejection (OBR) needs to be larger than 20 dB to reject out-of-channel interferers. Third, as the first stage of a receiver, low insertion loss is critical to ensure system SNR is adequate. Finally, since it serves as a connection between antenna and transceivers, the channel selection filter is required to be impedance matched to the characteristic impedance of the antenna feed, which is usually 50  $\Omega$  for lownoise systems.

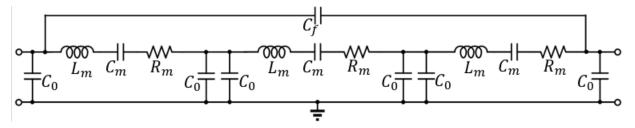

In this work, a coupled resonator filter topology with three series-connected AlN contour-mode twoport resonators is implemented to meet the specifications for a channel-selection filter [9]. The three identical resonators are connected in series, resulting in three resonant modes from the interaction between the RLC branches (Figure 1-4). Without considering process variations, this filter topology has been reported to offer center frequency above 1 GHz, insertion loss below 3 dB, FBW around 0.3% of center frequency, out-of-band rejection above 20 dB [4]. The insertion loss can meet the 9 dB noise figure (NF) spec for the Long-Term Evolution (LTE) wireless communication protocol [10] with a moderate receiver frontend NF spec of 3 dB. The 20 dB OBR can alleviate the linearity specification of the thirdorder interception point (IP3) by 30 dB.

Figure 1-4 AlN resonator filter schematic model.

To maximize power transmission from the input to the output port, the filter needs to be terminated by a proper resistance  $R_0 = \left| \frac{1}{j\omega_0 C_0} \right|$ . For a channel selection filter operating at 1 GHz, to match to a 50  $\Omega$ antenna, the intrinsic capacitance would be greater than 3 pF. To achieve an intrinsic capacitance of 3 pF, the resonator AlN film size is around 350 µm by 350 µm (a larger resonator aspect ratio is desired to accommodate the flip-chip pad separation rule with 3D integration – see Section 5.4.1). A larger resonator not only requires longer release time, but is also at higher risk of fracture during fabrication due to large trapped residual stresses in the AIN. Therefore, a larger filter area can be formed by coupling many smaller sub-filters electrically. Each *RLC* resonant circuit comprises an array of k smaller resonator filters (sub-filters) coupled electrically in parallel, so that the termination resistance is k times lower than a single sub-filter. In previous experiments, a sub-filter size that is matched to 350  $\Omega$  and  $k = 4 \sim 7$  is a proper selection to achieve overall 50  $\Omega$  impedance. To implement SES on the AIN resonator filters, the total area of the selected sub-filters should be the same for all k selections out of a total N sub-filters in the array. To improve the effective filter yield while keeping the load matched, the number of M possible combinations of k out of N sub-filters can be large and so it can take a long time to calibrate to find the best combination (or even an adequate combination that meets the specifications).

#### 1.2.3 Process variations in AlN MEMS resonator filters

From the lumped circuit model of the AIN resonators, given the center frequency  $f_0$ , the quality factor Q determines the resonator bandwidth (BW) as well as the insertion loss at resonance. Intrinsic capacitance  $C_0$  contributes to the out-of-band transimpedance. The coupling coefficient  $k_t^2$  sets the separation of the peak and dip frequency (parallel frequency). These four parameters ( $f_0$ , Q,  $C_0$ , and  $k_t^2$ ) determine the resonator's electrical performance. In the literature [11], AIN two-port contour mode resonators at room temperature (300 K) achieved a center frequency of 1 GHz, with unloaded quality factor around 2000 and  $k_t^2$  of 1.35%. The high Q and low insertion loss make AIN resonators good candidates for channel selection filters.

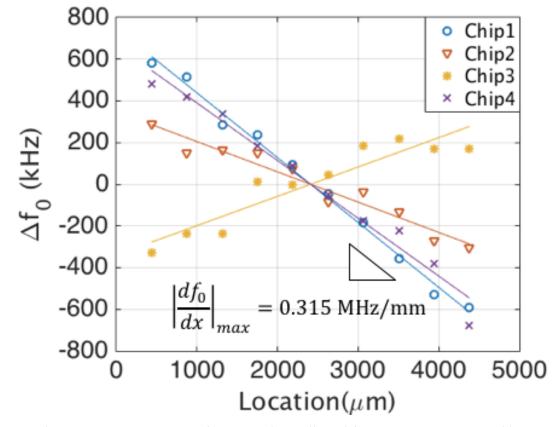

The corresponding deviations in the parameters (*Q*-value,  $f_0$ ,  $C_0$  and  $k_t^2$ ) due to process variations induce deviations in the resonator electrical characteristics. For example, a 1 GHz center frequency corresponds to interdigitated electrode half pitch  $W = 2 \mu m$ . A pitch change of 12 nm would cause a frequency shift of 6 MHz, which is the bandwidth of the resonator when it is loaded with a 50  $\Omega$ impedance. To study the statistical characterization of resonators, 10 identical two-port resonators were laid out in a row with a total length of 0.5 mm. Four chips that are on the same wafer fabricated by the Institute for MicroElectronics, A-Star Singapore (IME), were measured to obtain the center frequency for the 40 filters (Figure 1-5).  $\Delta f_0$  is the difference between the center frequency of each filter and the mean value of the 10 filters on the same chip. The important observation is that the distribution of the center frequency of the devices exhibits a linear relationship with the device position. Therefore, systematic error is dominating the AIN resonator center frequency variations, as expected . Previous works have reported the statistical characteristics of the AIN two-port resonator filter performance [4], shown in Table 1-1. Among the four parameters, center frequency shows a biggest difference between inter-chip and intra-chip standard deviation ( $\sigma$ ). The inter-chip deviation reaches 5.3 MHz, which is the bandwidth of some communication channels [10]. This can cause problems when we design a channel selection filter for a specific communication band. The self-healing method can be used to improve this filter performance.

Figure 1-5 Resonator center frequency data collected from 40 resonators on 4 chips.

|                   | <i>f</i> <sub>0</sub> (GHz) | IL (dB) | BW (MHz) | OBR (dB) |

|-------------------|-----------------------------|---------|----------|----------|

| Pooled mean value | 1.15                        | 4.44    | 3.83     | 24.81    |

| Pooled STD        | 0.0053                      | 0.65    | 0.23     | 1.91     |

| Intra-chip STD    | 0.0002                      | 0.62    | 0.059    | 0.53     |

Table 1-1 Statistical study of AlN resonator filters.

#### 1.2.4 Conventional tuning and trimming methods in MEMS resonator filters

AIN MEMS resonator filters, due to their high Q characteristic, have been used as stable frequency references. In such applications, the main performance metrics are its center frequency  $(f_0)$ , Q value, insertion loss (IL), out-of-band rejection (OBR) and in-band ripple. In transition from research laboratories to commercial products, these metrics require precise control. According to the process variation measured,  $f_0$  variations dominate all other metrics, therefore,  $f_0$  control is crucial. Research investigation in  $f_0$  control techniques can be categorized into tuning and trimming. The former provides  $f_0$  tuning by changing the device effective stiffness, and the latter provides  $f_0$  trimming by changing the device effective density.

Mechanisms commonly employed to alter the effective stiffness involve electrostatic and thermal tuning. In electrostatic tuning devices, an electrical spring with stiffness tunable via a DC voltage is added to provide  $f_0$  tuning. The small stiffness of the electrical spring, due to low-efficiency electrostatic transduction, limits the technique to low-frequency low-stiffness flexural-mode resonators [12]. A relatively high frequency (20 MHz) IBAR oscillator with temperature compensation is designed in [13]. The tuning range is achieved through high DC control voltage (>10 V), making it inappropriate for portable electronic device applications. In thermal tuning devices, a tunable heater element is added, resulting in changing resonator temperature and tuning frequency due to large TCF. Wide tuning range (3000 ppm) can be achieved [14] at a cost of additional bulky heating elements.

Trimming methods permanently shift device parameters by selectively adding or removing material, usually after fabrication. Examples of this class of technique include laser or ion beam trimming through a transparent package [15] and localized oxide growth using thermal actuation [16]. *In situ* trimming corrects process variations and packaging uncertainties at the same time, which makes it attractive. However, the tuning accuracy is limited by the laser or ion beam diameter. Also fine tuning each device is generally too time-consuming for mass production.

#### 1.2.5 Statistical Element Selection (SES) method in MEMS resonator filters

SES is a self-healing methodology that can be used to alleviate the variation challenges when using AIN resonators. SES is a post manufacturing calibration technique that accommodates large-scale process variations to improve the matching of transistors [17].

According to Pelgrom's transistor mismatch model [23], standard deviations of the current factor and threshold voltage are proportional to  $1/\sqrt{WL}$ . Thus, it is a traditional approach to improve transistor matching by increasing the sizing. An alternative approach is redundancy, where a large number (*N*) of devices are built and the best one is chosen, which consumes *N* times the area. In contrast, SES exploits combinational redundancy by selecting *k* devices out of *N* devices, resulting in an exponential increase in the number of available combinations  $C_N^k$ . SES has been demonstrated to lower CMOS offset by multiple orders of magnitude at a relatively low circuit overhead [18,19,20,21]. A similar technique can be used to fine tune MEMS resonators, since the variations in the device performance are affected by random variations. However, from the statistical study of the resonators in the experimental fabrication process, systematic variations dominate the on-wafer center frequency variation. In a production environment, although the equipment would be better controlled and trim techniques would be put in place to reduce the systematic process variation, to precisely control each individual device is time consuming. The original SES approach needs to be extended to solve the problem.

For the original SES methodology, the distribution of the combined k elements is created by the random variation of the equally sized N elements. A large number of combinations aggregated around the nominal design value with a deviation close to the random variation. This allows extremely high calibration resolution to be realized. However, since only the values from the random variations are present in the N sub-devices, the combined device parameter will not exceed the range of random variation. This would self-heal when the wafer-level variation is in the same range as the chip-level. However, in the presence of systematic variation, the calibration target window will deviate from the mean value on the chip. With no sub-device in the calibration window range, the calibration success rate drops rapidly.

#### **1.3 Proposed system and contributions**

Commonly used trimming techniques are effective for coarse  $f_0$  calibration, but they are costly to calibrate for each individual device. An SES based reconfigurable filter design can provide a fine calibration resolution, but the calibration range is limited. Based on these methods, this work assumes die to die variation is eliminated by coarse trimming and adopts extended the SES method to maintain fine resolution while enabling  $f_0$  reconfiguration over a relatively broad tuning range.

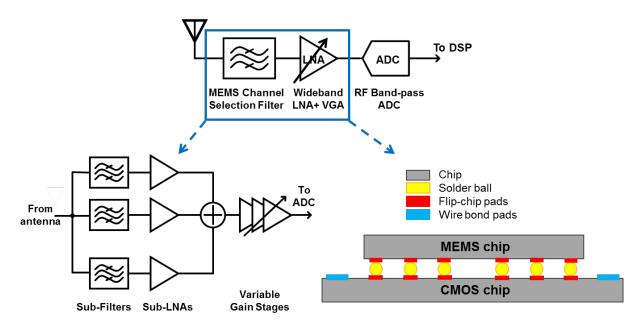

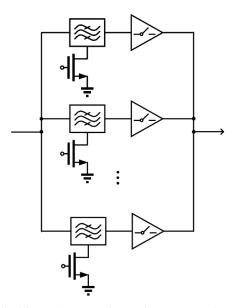

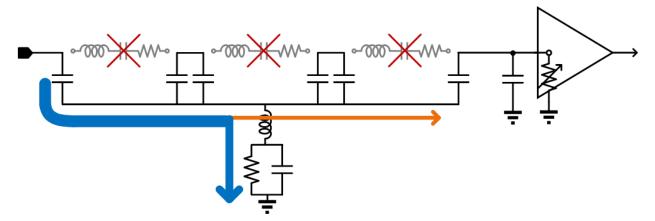

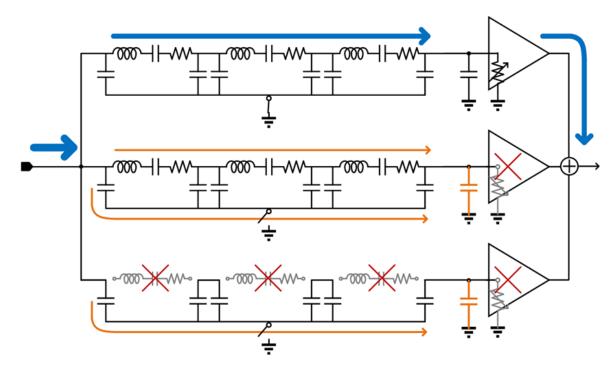

To realize the statistical selection for MEMS filters, a heterogeneously integrated receiver frontend system in Figure 1-6 is proposed. Figure 1-6 shows a receiver structure with a channel selection filter and a gain stage as the front-end of a direct sampling receiver. Without self-healing, the filter center frequency is prone to process variations. To implement self-healing, the filter is separated into an array of sub-filters. In the calibration phase, a sub-set of the sub-filters that meet the filter specifications are selected to function as a single filter. This implementation follows the self-healing method of Statistical Element Selection (SES) [17]. Adding selectability to a filter array, however, requires complex selection control circuitry. The switching control circuit needs to ensure uniform loading and minimized parasitic overhead. Therefore, the low noise amplifier (LNA) is separated in the receiver front-end into sub-LNAs, with each of the sub-LNAs serving as the switching components. A summing stage follows the array to sum signals from selected branches. After going through a variable gain amplifier, the signal is ready to be sampled through a band-pass sampling analog-to-digital converter (ADC). Parasitic capacitances and inductances from packaging are present at the interface between the sub-filters on the MEMS chip and the sub-LNAs on the CMOS chip. Since the performance of both the LNA and the filters is sensitive to these parasitics, flip-chip bonding for interconnection is used to reduce wiring parasitics.

Figure 1-6 Proposed receiver frontend.

Since the (E)SES method is suitable for most devices where the performance deviation is affected by random variation, this method has a wide application space in the future emerging technologies, especially with device scaling. This work presents high-yield AlN resonator filters as a specific and unique application of ESES. Process variation is an intrinsic challenge that inhibits the use of many types of MEMS high-Q filters in front-end subsystem in commercialized receivers. Improving the filter yield can unleash the power of these devices to improve real-world RF systems.

To achieve this goal, the following specific design and methodology contributions are needed to make these self-healing resonator arrays a reality:

1) ESES calibration design method for MEMS filters

GHz-level AIN MEMS resonator filters are the target of study to apply and demonstrate the extended Statistical Element Selection algorithm. The generalized design method optimizes yield for center frequency accuracy with minimum area overhead to overcome both systematic and random process errors. Since the ESES corrects center frequency errors resulting from location on the die, it is widely applicable to most MEMS filters whose center frequencies are sensitive to process variations including feature size lithography error, inhomogeneous metal deposition or

etching inaccuracies. This method works well with conventional trimming methods and improves fine frequency tuning efficiency for industrial mass production.

2) Ground switch for on/off function with uniform loading

Most applications of RF MEMS in SDR involve switching to alter the operating bands. Due to the relatively high resistance in CMOS transistors, any switch appearing on the signal path will contribute to insertion loss. An on/off ground switch is introduced as a new mechanism that avoids deterioration in the device power transfer arising from series switch control. By disconnecting the RF ground from the bottom electrode of the resonator, the two-port device cannot generate substantial internal electric fields for piezoelectric drive or sense, effectively turning off the resonator. The self-healing filter array employs this ground switching mechanism. S-parameter measurement for the on and off states provide characterization of isolation and validation of the overall effect on the array performance.

3) Multi-input single-output LNA to handle output coupling

To further limit deleterious impact of switching on insertion loss, this work will be the first to integrate circuit components that are already present in the common receiver architectures to perform switching on MEMS devices. The LNA serves both as an amplifier and a switch, which together with a summing circuit stage that follows it, aggregates signals from each of the selected bands. Summing electrically at the output stage of the LNA avoids electromechanical coupling at the output ports of the MEMS sub-filters. The co-design of the LNA and the filter interface takes both circuit components and the MEMS components into consideration so that the overall system achieves improved performance.

4) Instantiation in a CMOS-MEMS flip-chip process

IME will flip-chip bond the MEMS and CMOS chips, resulting in a minimal impact of capacitive and inductive parasitics by lowering the routing distances. A redistribution layer (RDL) is built in the IME process flow to further alleviate CMOS routing parasitics. This work is the

first time that this process is used for integrating MEMS devices with CMOS circuits. This approach allows for a MEMS chip that is larger than the CMOS chip.

### 2.1 ESES method

To increase the tuning range and to accommodate other dominant variation sources, the N subelements in SES can be sized non-uniformly. For this *extended* SES (ESES) method [22], the overall size of k elements already spans a range for the nominal case, and this range can be controlled by making the nominal sizes of the elements to be a design parameter. With random variation "designed in," the distribution of the overall size of k elements creates a wider calibration tuning range.

In applying the ESES method to AIN MEMS resonator filters to calibrate wafer level process variation, a tradeoff exists between tuning range and tuning resolution. According to the statistical measurement data, resonator center frequencies vary up to 10 MHz across the IME-fabricated wafers over mm-scale distances. To form a filter with smooth passband, the frequency interval between successive sub-filters needs to be less than 250 kHz. Covering a 10 MHz range with 250 kHz intervals would require 40 sub-filters. More sub-filters would be required considering the redundancy for higher yield. This brute-force approach significantly increases area overhead and the limitation motivates ESES as a good complementary technique to combine with wafer-scale trimming – i.e., coarsely trim to reduce wafer-level variation and use ESES for fine frequency calibration. Since the cost for trimming scales with accuracy, the implementation of ESES after trimming is proposed as a balanced solution for mass production.

To implement ESES, parameters for the "pseudo-variation" sequence in design of center frequencies in the array need to be determined. First, the sequence parameters (number of sub-filters N, frequency range  $F_{ps}$  and frequency values  $f_{0i}$  of sub-filters i = 1..N) of the pseudo-variation affects the calibration range and resolution. For a given value of N, a small interval ensures high calibration resolution and better success rate, but the total calibration range would be sacrificed. Optimization on these parameters is needed to maximize calibration yield in limited area overhead. Secondly, since the sub-filter center frequency will be affected by the filter location, the effectiveness of ESES will be influenced by the layout placement of the sub-filter pseudo frequency shifts. In one scenario, the filter pseudo frequency shift is opposite the geometrical process variation in frequency, which shrinks the calibration range. Conversely, if the filter pseudo frequency shift aligns with the geometrical process variation in frequency, the interval will be doubled, reducing the calibration resolution. Therefore, for a given pseudo-variation sequence, the placement of each pseudo frequency shift within the layout needs to be optimized.

## 2.2 ESES design optimization

#### 2.2.1 Filter and resonator statistical data collection

The center frequency  $(f_0)$  variation is systematically dependent on the filter location, and so the distribution of  $f_0$  has a geometrical dependence. The assumption of a normal distribution for  $f_0$  where all dies to have the same mean value across the wafer [4] does not properly represent the wafer-level statistical distribution.

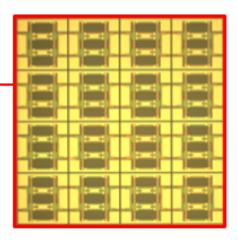

The testing structures to capture the wafer-level distribution are shown in Figure 2-1a. 16 identical two-port resonator filters were laid out in a 4×4 matrix on 2×2 mm<sup>2</sup> chips on a same wafer fabricated by A\*STAR Institute of Microelectronics (IME). The wafer-level  $f_0$  distribution with respect to location is shown in Figure 2-1b.

(a)

Figure 2-1 Wafer-level center frequency profile measurement.

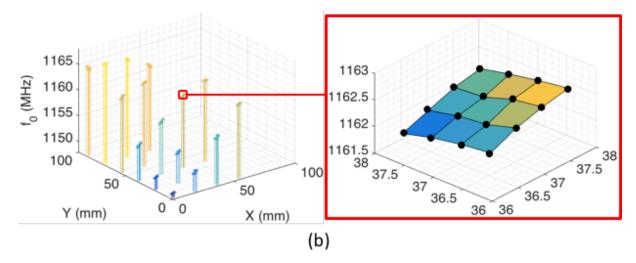

The gradient of center frequency gradually changes across the wafer, with smooth curvature. For a  $2\times 2$  mm single chip, the area is sufficiently small for the  $f_0$  gradient profile to be modeled as a plane (*i.e.*, linear variation). For any "random" chip on a wafer, the plane center frequency shift from the wafer mean  $(\Delta f_{0c})$  and the normal vector direction angles ( $\alpha$  and  $\beta$ ) are random variables (Figure 2-2).

Figure 2-2 Plane model for cell-level center frequency distribution.

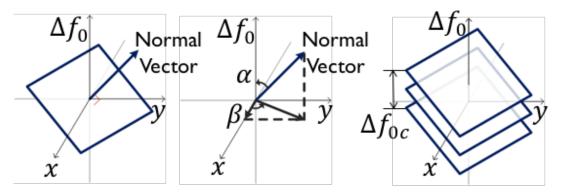

For all the 71 chips on the single wafer tested, these variables are extracted. A histogram of each measured variable are summarized in Figure 2-3.

Figure 2-3 Histogram of  $f_0$  plane parameters, taken from measurements.

The histograms indicate that  $\alpha$ ,  $\beta$  and  $\Delta f_{0c}$  may be modeled with a uniform distribution. Table 2-1 summarizes the distribution parameters, which is raw data taken from an un-trimmed wafer. In a production environment, the actual range of  $\Delta f_{0c}$  would be dependent on the accuracy of trimming.

| Table 2-1 Performance statistics | of standalone MEMS | filters for 1136 sa | imples measured across 71 dies. |

|----------------------------------|--------------------|---------------------|---------------------------------|

|                                  |                    |                     |                                 |

|                                                       | $f_0$ (MHz)                   | BW (MHz)                     | IL (dB)                 | OBR (dB) |

|-------------------------------------------------------|-------------------------------|------------------------------|-------------------------|----------|

| Mean                                                  | 1158                          | 2.75                         | 2.91                    | 20.1     |

| Standard Deviation                                    | Deviation 6.95                |                              | 0.187                   | 3.02     |

|                                                       | $\alpha$ (rad <sup>-1</sup> ) | $\beta$ (rad <sup>-1</sup> ) | $\Delta f_{0c}^*$ (kHz) | -        |

| Min                                                   | 0                             | $-\pi$                       | -450                    | -        |

| Max                                                   | 0.4                           | π                            | 450                     | _        |

| * Assumed $\Delta f_{0c}$ distribution after trimming |                               |                              |                         |          |

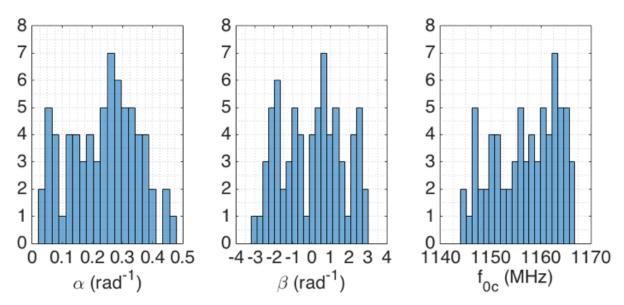

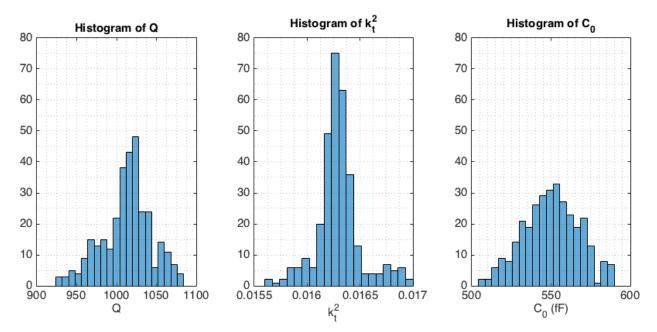

In order to simulation the statistical behavior of AlN resonator filters, the two-port network parameters of the filters need to be generated from lumped resonator circuit components  $R_m$ ,  $L_m$ ,  $C_m$  and  $C_0$ , which are variables following the statistical distribution determined by the statistical distribution of the resonator parameters  $f_0$ , Q,  $k_t^2$  and  $C_0$ . To get the statistics of these parameters, 19 4x4 resonator arrays on the same wafer were measured. The histograms of these parameters are shown in Figure 2-4. The statistics are shown in Table 2-2. From the histogram, the parameters  $Q, k_t^2$  and  $C_0$  follow normal distribution. The center frequency is dominated by systematic variations, but is also affected by random variations. To extract the random variation distribution, the center frequency data is extracted by subtracting the estimated geometric variation from the measured parameter. The residue would be the result of the random variation.

Figure 2-4 Histogram of resonator parameters, taken from measurements.

Table 2-2 Performance statistics of standalone MEMS resonator for 304 samples measured across 19 dies.

|                                                  | $f_0$ (MHz) | Q    | $k_t^2$ | $C_0$ (fF) |

|--------------------------------------------------|-------------|------|---------|------------|

| Pooled mean value                                | 1147        | 1013 | 1.63%   | 550.2      |

| Pooled standard deviation                        | 0.087*      | 31   | 0.021%  | 1.75       |

| * The standard deviation after linear regression |             |      |         |            |

Using the statistical model, the systematic and random variations of the resonator parameters are characterized. The total result would be the sum of both effects. Equations (2.1-(2.7 show the calculation for these parameters.

$$\alpha = \text{Uniform}(0, 0.4 \text{ rad}^{-1}) \tag{2.1}$$

$$\beta = Uniform(0, 2\pi) \tag{2.2}$$

(2, 2)

-

· ·

$(n \alpha)$

$(\mathbf{0}, \mathbf{7})$

$$df_0(x,y) = \frac{x + y \tan\beta}{\cot \alpha \sqrt{1 + \tan^2 \beta}}$$

(2.3)

$$Q = Norm(\mu_0, \sigma_0) \tag{2.4}$$

$$k_t^2 = Norm\left(\mu_{k_t^2}, \sigma_{k_t^2}\right) \tag{2.5}$$

$$C_0 = Norm(\mu_{C_0}, \sigma_{C_0}) \tag{2.0}$$

$$f_0 = Norm(\mu_{f_0}, \sigma_{f_0}) + df_0(x, y)$$

(2.7)

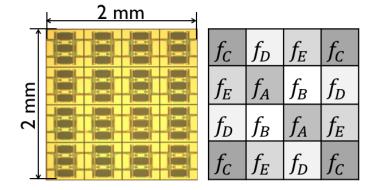

#### 2.2.2 Basic layout pattern

Since the normal vector angles  $\alpha$  and  $\beta$  follow a uniform distribution, the chances for either side of a chip to have higher  $f_0$  than the other is equal. To prevent the pseudo variation sequence from being offset by geometrical variation, it is preferable to duplicate all pseudo frequencies in the four sides of a chip. This leads to a centro-symmetric placement of the sub-filters. The filters are designed in a squared shape, so the most symmetrical placement for the *N* sub-filters would be when *N* is a square of an integer, and the *N* sub-filters are placed in an  $\sqrt{N} \times \sqrt{N}$  array. For the number of distinct frequencies, *N*/4 would ensure duplicating all pseudo-frequencies on the four sides. The smallest number meeting these requirements is N = 16. Figure 2-5 shows a pseudo-frequency placement for this configuration. With the resonator core and necessary peripheral pads and routing, each filter takes a 500×500 µm square, and the total chip area becomes 2×2 mm. The four filters in the center would not differ significantly even with

geometrical variation. Therefore, a fifth frequency is assigned in the center. The effectiveness of this layout placement is evaluated by sweeping the frequency values, as discussed in the next section.

Figure 2-5 Basic layout for ESES filter array.

#### 2.2.3 Layout placement rotations for a pseudo-variation sequence

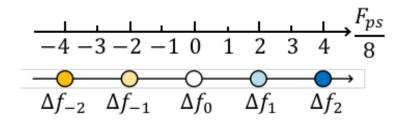

To optimize the layout placement for pseudo-variation, the success rate needs to be compared among different pseudo-variation sequences. To simplify the following, the pseudo frequencies are sorted in the sequence of their values:  $f_{-2} < f_1 < f_0 < f_1 < f_2$ . The pseudo range being the range of the values in the pseudo-variation sequence, can be expressed as  $F_{ps} = f_2 - f_{-2}$ . In the discussion, the frequency sequence is designed to center around the target frequency:  $f_{tar} = \frac{f_2 + f_{-2}}{2}$ . The selection of  $f_{-1}$ ,  $f_0$  and  $f_1$  can be any value within the range of  $[f_{-2}, f_2]$ . Enlisting all combinations would be impossible, but discretizing the interval and a search through all combinations leads to the optimized sequence. In this discussion, the range  $[f_{-2}, f_2]$  is evenly divided into 8 intervals. If we define the difference between each pseudo frequency and the target as:  $\Delta f_i = f_i - f_{tar}$ , i = -2, ... 2, the interval can be represented as in Figure 2-6 and all 35 combinations are listed in Table 2-3.

| Figure 2-6 Frequency interval for the pseudo frequency in ESES filter array.                |

|---------------------------------------------------------------------------------------------|

| Table 2-3 Combinations of frequency interval for the pseudo frequency in ESES filter array. |

| Unit: <b>F</b> <sub>ps</sub> / <b>8</b> |              |              |                 |              |              |                 |              |              |  |  |  |  |  |

|-----------------------------------------|--------------|--------------|-----------------|--------------|--------------|-----------------|--------------|--------------|--|--|--|--|--|

| $\Delta f_{-1}$                         | $\Delta f_0$ | $\Delta f_1$ | $\Delta f_{-1}$ | $\Delta f_0$ | $\Delta f_1$ | $\Delta f_{-1}$ | $\Delta f_0$ | $\Delta f_1$ |  |  |  |  |  |

| -3                                      | -2           | -1           | -3              | 1            | 2            | -2              | 2            | 3            |  |  |  |  |  |

| -3                                      | -2           | 0            | -3              | 1            | 3            | -1              | 0            | 1            |  |  |  |  |  |

| -3                                      | -2           | 1            | -3              | 2            | 3            | -1              | 0            | 2            |  |  |  |  |  |

| -3                                      | -2           | 2            | -2              | -1           | 0            | -1              | 0            | 3            |  |  |  |  |  |

| -3                                      | -2           | 3            | -2              | -1           | 1            | -1              | 1            | 2            |  |  |  |  |  |

| -3                                      | -1           | 0            | -2              | -1           | 2            | -1              | 1            | 3            |  |  |  |  |  |

| -3                                      | -1           | 1            | -2              | -1           | 3            | -1              | 2            | 3            |  |  |  |  |  |

| -3                                      | -1           | 2            | -2              | 0            | 1            | 0               | 1            | 2            |  |  |  |  |  |

| -3                                      | -1           | 3            | -2              | 0            | 2            | 0               | 1            | 3            |  |  |  |  |  |

| -3                                      | 0            | 1            | -2              | 0            | 3            | 0               | 2            | 3            |  |  |  |  |  |

| -3                                      | 0            | 2            | -2              | 1            | 2            | 1               | 2            | 3            |  |  |  |  |  |

| -3                                      | 0            | 3            | -2              | 1            | 3            |                 |              |              |  |  |  |  |  |

Considering the centro-symmetry property, there are 36 distinct rotations for such a configuration. The symmetrical passband of the filter allows further reduction of the number of independent rotations to 30 (Figure 2-7, Table 2-3).

Table 2-4 Combinations of frequency rotation for the pseudo frequency in the ESES filter array.

| Rotation | f <sub>A</sub>         | $f_B$    | fc    | Rotation | f <sub>A</sub> | $f_B$ | fc                     |

|----------|------------------------|----------|-------|----------|----------------|-------|------------------------|

| 11       | <i>f</i> <sub>-2</sub> | $f_{-1}$ | $f_0$ | 61       | $f_{-1}$       | $f_1$ | <i>f</i> <sub>-2</sub> |

| 12 | <i>f</i> <sub>-2</sub> | <i>f</i> <sub>-1</sub> | $f_1$                  | 62  | $f_{-1}$               | $f_1$                  | $f_0$                  |

|----|------------------------|------------------------|------------------------|-----|------------------------|------------------------|------------------------|

| 13 | <i>f</i> <sub>-2</sub> | <i>f</i> <sub>-1</sub> | $f_2$                  | 63  | <i>f</i> <sub>-1</sub> | $f_1$                  | $f_2$                  |

| 21 | <i>f</i> <sub>-2</sub> | $f_0$                  | <i>f</i> <sub>-1</sub> | 71  | $f_1$                  | $f_0$                  | $f_2$                  |

| 22 | <i>f</i> <sub>-2</sub> | $f_0$                  | $f_1$                  | 72  | $f_1$                  | $f_0$                  | <i>f</i> <sub>-1</sub> |

| 23 | <i>f</i> <sub>-2</sub> | $f_0$                  | $f_2$                  | 73  | $f_1$                  | $f_0$                  | <i>f</i> <sub>-2</sub> |

| 31 | <i>f</i> <sub>-2</sub> | $f_1$                  | <i>f</i> <sub>-1</sub> | 81  | $f_2$                  | <i>f</i> <sub>-1</sub> | $f_1$                  |

| 32 | <i>f</i> <sub>-2</sub> | $f_1$                  | $f_0$                  | 82  | $f_2$                  | <i>f</i> <sub>-1</sub> | $f_0$                  |

| 33 | <i>f</i> <sub>-2</sub> | $f_1$                  | $f_2$                  | 83  | $f_2$                  | $f_{-1}$               | <i>f</i> <sub>-2</sub> |

| 41 | <i>f</i> <sub>-2</sub> | $f_2$                  | <i>f</i> <sub>-1</sub> | 91  | $f_2$                  | $f_0$                  | $f_1$                  |

| 42 | <i>f</i> <sub>-2</sub> | $f_2$                  | $f_0$                  | 92  | $f_2$                  | $f_0$                  | <i>f</i> <sub>-1</sub> |

| 43 | <i>f</i> <sub>-2</sub> | $f_2$                  | $f_1$                  | 93  | $f_2$                  | $f_0$                  | <i>f</i> <sub>-2</sub> |

| 51 | $f_{-1}$               | $f_0$                  | <i>f</i> <sub>-2</sub> | 101 | $f_2$                  | $f_1$                  | $f_0$                  |

| 52 | $f_{-1}$               | $f_0$                  | $f_1$                  | 102 | $f_2$                  | $f_1$                  | <i>f</i> <sub>-1</sub> |

| 53 | <i>f</i> <sub>-1</sub> | $f_0$                  | $f_2$                  | 103 | $f_2$                  | $f_1$                  | <i>f</i> <sub>-2</sub> |

| 11                                                    | 12                                                    | 13                                                    | 61                                                    | 62                                                    | 63                                                    |

|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| 21                                                    | 22                                                    | 23                                                    | 71                                                    | 72                                                    | 73                                                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| 31                                                    | 32                                                                                                                                                                           | 33                                                    | 81                                                                                                                                                                   | 82                                                                                                                                                                          | 83                                                    |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  | $\begin{array}{c cccc} f_1 & f_{-2} & f_0 & f_1 \\ f_0 & f_2 & f_{-1} & f_{-2} \\ \hline f_{-2} & f_{-1} & f_2 & f_0 \\ \hline f_1 & f_0 & f_{-2} & f_1 \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| 41                                                    | 42                                                                                                                                                                           | 43                                                    | 91                                                                                                                                                                   | 92                                                                                                                                                                          | 93                                                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                        | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| 51                                                    | 52                                                                                                                                                                           | 53                                                    | 101                                                                                                                                                                  | 102                                                                                                                                                                         | 103                                                   |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccc} f_1 & f_2 & f_{-2} & f_1 \\ \hline f_{-2} & f_{-1} & f_0 & f_2 \\ \hline f_2 & f_0 & f_{-1} & f_{-2} \\ \hline f_1 & f_{-2} & f_2 & f_1 \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                | $\begin{array}{c ccccc} f_{-1} & f_{-2} & f_0 & f_{-1} \\ f_0 & f_2 & f_1 & f_{-2} \\ \hline f_{-2} & f_1 & f_2 & f_0 \\ \hline f_{-1} & f_0 & f_{-2} & f_{-1} \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Figure 2-7 Frequency rotation for the pseudo frequency in the ESES filter array.

#### 2.2.4 Monte Carlo simulation for success rate evaluation

For each rotation and interval combination, the success rate is evaluated through Monte Carlo simulation. For each run, the resonator parameters  $f_0$ , Q,  $k_t^2$  and  $C_0$  are generated from the statistical model. The lumped circuit components  $R_m$ ,  $L_m$  and  $C_m$  are then calculated from the resonator parameters. Using the circuit components, the two-port network parameters of a resonator are calculated. In this thesis, the two-port network matrix is denoted with a bolded initial letter: **S** for S-parameters, **Y** for Y-parameters and **T** for transmission matrix (2.8). The subscript denotes the circuit component associated with the parameter: **S**<sub>Filter</sub> denotes the S-parameters of the filter.

$$\mathbf{S} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix}, \mathbf{Y} = \begin{bmatrix} Y_{11} & Y_{12} \\ Y_{21} & Y_{22} \end{bmatrix}, \mathbf{T} = \begin{bmatrix} A & B \\ C & D \end{bmatrix}$$

(2.8)

According to two-port network theorems [26], cascading the transmission matrices of the three seriesconnected resonators provides the Y parameters of the sub-filter (2.9) and (2.10). After the Y parameters of N subfilters are established, all  $C_N^k$  combinations are simulated. For each combination, Y parameters of the selected k sub-filters are added to form the Y parameters of the combined filter. Transformation of Y parameters to S parameters give the simulated filter parameters  $f_0$ , BW, IL, OBR and in-band ripple values.

$$\mathbf{T}_{\text{SubFilter}} = \mathbf{T}_{\text{Resonator},1} \times \mathbf{T}_{\text{Resonator},2} \times \mathbf{T}_{\text{Resonator},3}$$

(2.9)

$$\mathbf{Y}_{\text{Filter}} = \sum_{i=1}^{k} \mathbf{Y}_{\text{SubFilter},i} \tag{2.10}$$

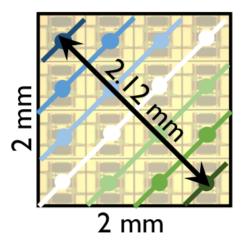

The success rate (i.e., performance yield) is evaluated with passing criteria. Under the assumption that the wafer has been trimmed so that the wafer variation matches chip variation, the largest  $f_0$  variation slope 0.48 MHz/mm measured in Figure 2-8 represents the worst-case scenario on the wafer. For a 2 mm by 2 mm chip, the largest variation occurs when the slope is in the diagonal of the square (Figure 2-8). The largest  $f_0$  variation on a single chip is around 900 kHz. Thus the maximum value for the frequency center shift  $\Delta f_{0c}$  is ±450 kHz. All filters on the same elevation will have same geometrical variation. With the 7 level elevations in the 4×4 filter array, the largest  $f_0$  interval will be 140 kHz. This variation is large compared to the deviation of the other filter parameters (BW, IL, OBR). Therefore, the target for ESES calibration is healing the  $f_0$  deviation.

Figure 2-8 A 4×4 sub-filter array on a 2 mm by 2 mm die with center frequency pseudo-variation.

As shown in Table 2-5, the tolerance of the center frequency is set to be  $\pm 20$  kHz, which is 3.5 times less than the  $f_0$  interval of 140 kHz and 22.5 times less than the center shift  $\Delta f_{0c}$ . In the center frequency target, the center shift is reflected in the range of targets. In order to cover the wafer level variation, the center frequency for the chip should be able to meet a tuning range equal to the variation.

|           | <i>f</i> <sub>0</sub> (MHz) | BW (MHz) | IL (dB)   | OBR (dB) |

|-----------|-----------------------------|----------|-----------|----------|

| Target    | 1158 + (-0.45: 0.02: 0.45)  | 2.75     | < 2.91 dB | > 20 dB  |

| Tolerance | ±0.020                      | ±0.1     | _         | _        |

Table 2-5 Targets for success rate in Monte Carlo simulation.

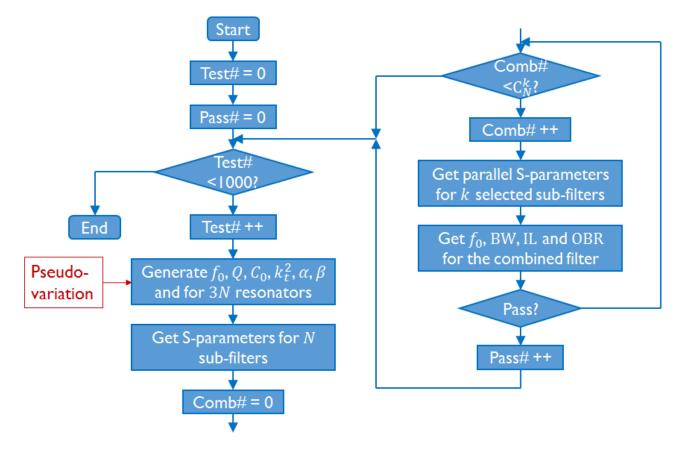

Figure 2-9 Flow chart for Monte Carlo Simulation

Figure 2-9 shows the flow chart for Monte Carlo simulation. First, the resonator parameters are generated from the statistical model. After calculating the lumped circuit model parameters, the resonator s parameters are reached. Cascading three resonator transmission matrices results in a filter transmission matrix. With all *N* sub-filters calculated, all  $C_N^k$  combinations of filter parameters are achieved through adding up the *k* Y parameters. For each combination, the four filter parameters are evaluated using the passing criteria until one combination passes or all combinations have been tried out. After running 100 tests, the success rate for the filters can be calculated by dividing the successful number of tests by 1000. Since for each set of tests, a different pseudo-variation array is inserted, the success rate can be used to evaluate the pseudo-variation effect in improving success rate. By selecting the pseudo-variation with the highest success rate, the pseudo-variation array is optimized.

#### 2.2.5 Optimization of pseudo-variation sequence

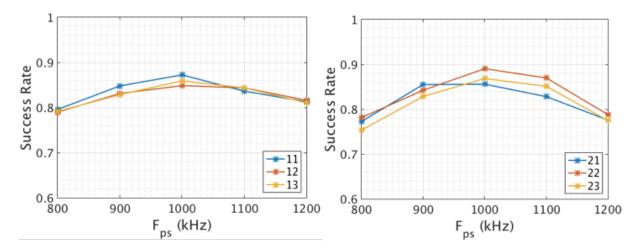

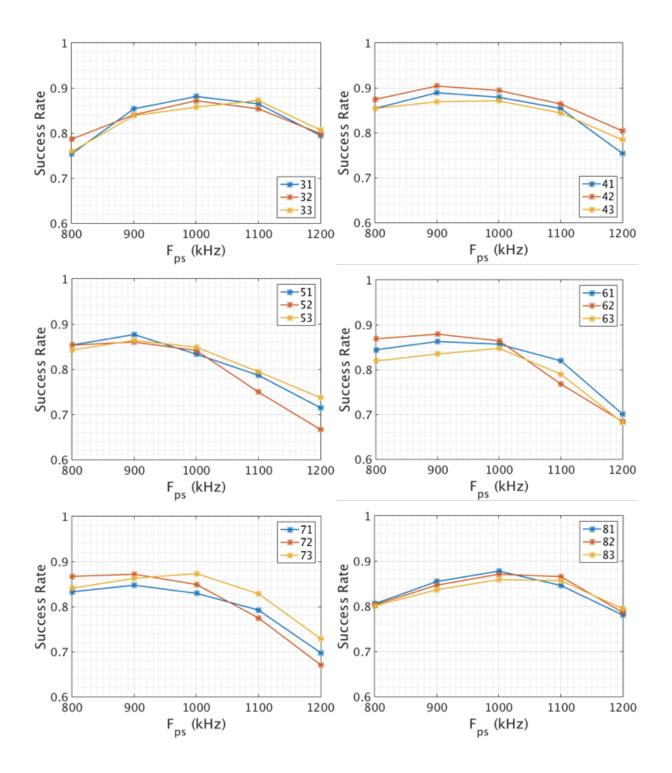

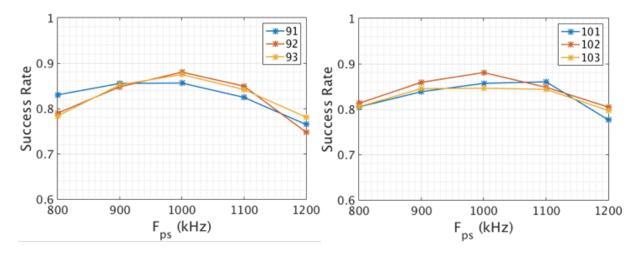

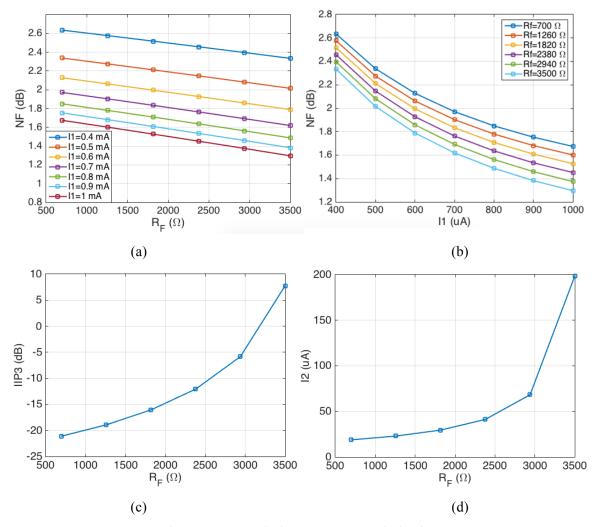

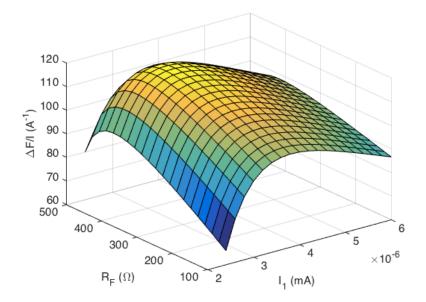

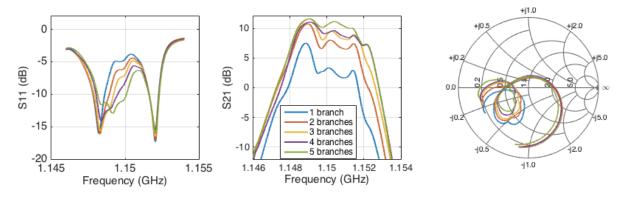

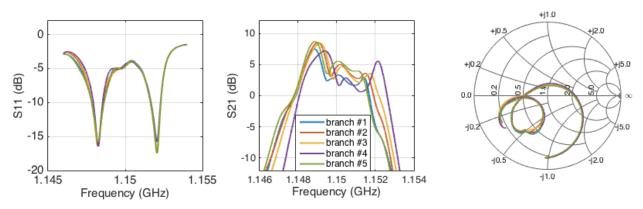

From the discussion in the previous section, the success rate of a pseudo-variation layout depends on the pseudo-range  $F_{ps}$ , the  $f_0$  interval, and the rotation. The multi-parameter optimization problem is solved in this work by sweeping the 6 pseudo-ranges  $F_{ps}$ , the 30 rotations and the 35 interval combinations to find the best parameter set. Figure 2-10 shows the success rate at each rotation with  $F_{ps}$ from 900 to 1300 kHz. Each point is the best success rate among all interval combinations.

Figure 2-10 Success rate at each rotation with  $F_{ps}$  from 800 to 1200 kHz. Table 2-3 and figure 2-6 define the rotations specified in the legends.