# SRAM reliability improvement using ECC and circuit techniques

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

**Electrical and Computer Engineering**

#### MARK P. MCCARTNEY

B.S.E., COMPUTER ENGINEERING, CASE WESTERN RESERVE UNIVERSITY

M.S., ELECTRICAL AND COMPUTER ENGINEERING, CARNEGIE MELLON UNIVERSITY

CARNEGIE MELLON UNIVERSITY

PITTSBURGH, PA

DECEMBER, 2014

2014 Mark P. McCartney (mpm@alumni.cmu.edu)

Some rights reserved. This work is licensed under the Creative Commons Attribution-ShareAlike 4.0 International License. To view a copy of this license, visit http://creativecommons.org/licenses/by-sa/4.0/.

**Keywords:** SRAM, memory, reliability, safety, error control coding, ECC, cyber-physical systems, CPS, erasure-based error control coding, EB-ECC, erasure, runtime erasure detection, ternary-output sense amplifier, TOSA, wordline assertion comparator, WLAC

Dedicated to my brother,

"Because your own strength is unequal to the task, do not assume that it is beyond the powers of man; but if anything is within the powers and province of man, believe that it is within your own compass also."

Marcus Aurelius

my mother,

"Being human always points, and is directed, to something or someone, other than oneself – be it a meaning to fulfill or another human being to encounter. The more one forgets himself – by giving himself to a cause to serve or another person to love – the more human he is."

Viktor Frankl

and my father.

"We make out of the quarrel with others, rhetoric, but of the quarrel with ourselves, poetry." William Butler Yeats

#### **Abstract**

Reliability is of the utmost importance for safety of electronic systems built for the automotive, industrial, and medical sectors. In these systems, the embedded memory is especially sensitive due to the large number of minimum-sized devices in the cell arrays. Memory failures which occur after the manufacture-time burnin testing phase are particularly difficult to address since redundancy allocation is no longer available and fault detection schemes currently used in industry generally focus on the cell array while leaving the peripheral logic vulnerable to faults. Even in the cell array, conventional error control coding (ECC) has been limited in its ability to detect and correct failures greater than a few bits, due to the high latency or area overhead of correction [43]. Consequently, improvements to conventional memory resilience techniques are of great importance to continued reliable operation and to counter the raw bit error rate of the memory arrays in future technologies at economically feasible design points [11, 36, 37, 53, 56, 70].

In this thesis we examine the landscape of design techniques for reliability, and introduce two novel contributions for improving reliability with low overhead.

To address failures occurring in the cell array, we have implemented an **erasure-based ECC scheme** (**EB-ECC**) that can extend conventional ECC already used in memory to correct and detect multiple erroneous bits with low overhead. An important component of this scheme is the method for detecting erasures at runtime; we propose a novel **ternary-output sense amplifier** design which can reduce the risk of undetected read latency failures in small-swing bitline designs.

While most study has focused on the static random access memory (SRAM) cell array, for high-reliability products, it is important to examine the effects of failures on the peripheral logic as well. We have designed a **wordline assertion comparator** (WLAC) which has lower area overhead in large cache designs than competing techniques in the literature to detect address decoder failure.

#### Acknowledgments

My deepest gratitude goes to my advisor and committee chair Ken Mai for providing me the opportunity to pursue graduate research and for his countless hours spent refining and revising my work. He has guided my progress through a shift in research area and shared his wealth of expertise in SRAM and digital circuit design. He has a unique ability to imbue his students with a sense of hope and purpose.

I am also very grateful to my committee members Prof. James Hoe, Prof. Andrzej Strojwas, and Dr. Alexander Hoefler for reviewing my proposal and dissertation and providing their feedback. Their time and flexibility made this possible.

My parents and my brother lent their unfailing support and attention during these years. I would like to thank them for always being there for me.

I had many productive discussions with my co-authors and colleagues Dr. Mudit Bhargava, Dr. Umut Arslan, Dr. Jangwoo Kim, Weinan Ma, Craig Teegarden, Çağla Çakır, Burak Erbağcı, Dr. Yu Cai, Yun Du, Nail Etkin Can Akkaya, Ray Carley, and Rachel Dondero. Their input improved the quality of my work and my life outside of work. We shared long hours together collaborating on tapeouts and papers, and the camaraderie will be remembered long after the PCBs are discarded. Special thanks to Mudit Bhargava for our long conversations and his technical advice which proved invaluable to my research and understanding. His selfless effort in the custom design and layout of the core SRAM on the EB-ECC testchip was a major contribution to the design. Special thanks also to Craig Teegarden and Çağla Çakır who did tireless work on the custom design and layout of the CAM on the EB-ECC testchip.

During my time in Pittsburgh, I've had the fortune of crossing paths with a number of people who enriched my life: Dr. Jason Brown, Dr. Jeff Nelson, Osei Poku, Juvyrose Santos, Esq., Dr. Kai Yu, Sonia Singhal, Naresh Bhatti, Matt Beckler, Kaship Sheikh, Ekin Sümbül, Kevin Biswas, Eric Menendez, Vitaliy Gleyzer, Brandon Mendoza, and Dr. Patrick Bourke, among others too numerous to list here. Thank

you all for your encouragement; I relished our time together and look forward to continued friendship and correspondence.

The staff at CMU are some of the kindest and most professional people I've ever met. I am profoundly appreciative of the efforts of Dr. Michele Keffer, Elaine Lawrence, Judy Bandola, Samantha Goldstein and all of the administrative staff in the ECE department for handling so many concerns and making life run more smoothly for all graduate students.

I am thankful for the inspiration of my undergraduate advisor Dr. Daniel Saab, whose guidance led me to graduate school in the first place and who always made time for my questions.

This work was financially supported in part by the Semiconductor Research Corporation and Freescale Semiconductor. While working at Freescale in Austin, Texas, I was managed by John Eagan and mentored by Alexander Hoefler, whose guidance clarified the need for reliability and safety guarantees in cyber-physical systems, providing the inspiration to focus on a practically useful set of objectives, which proved to be a turning point in my research. The completion of this dissertation owes much to that collaboration.

## **Contents**

| Te | erms and abbreviations x |              |                                       |      |  |  |  |

|----|--------------------------|--------------|---------------------------------------|------|--|--|--|

| 1  | Intr                     | Introduction |                                       |      |  |  |  |

| 2  | Bacl                     | kground      | l                                     | 4    |  |  |  |

|    | 2.1                      | Memo         | ry system                             | . 4  |  |  |  |

|    |                          | 2.1.1        | SRAM cell array                       | . 5  |  |  |  |

|    |                          | 2.1.2        | SRAM peripheral circuitry             | . 7  |  |  |  |

|    | 2.2                      | Error r      | mechanisms in memory                  | . 8  |  |  |  |

|    |                          | 2.2.1        | Hard errors                           | . 9  |  |  |  |

|    |                          | 2.2.2        | Soft errors                           | . 10 |  |  |  |

|    |                          | 2.2.3        | Parametric variability                | . 13 |  |  |  |

|    | 2.3                      | Error r      | manifestations and cell failure types | . 14 |  |  |  |

|    |                          | 2.3.1        | Cell array                            | . 14 |  |  |  |

|    |                          | 2.3.2        | Peripheral circuitry                  | . 20 |  |  |  |

|    | 2.4                      | Summ         | ary                                   | . 23 |  |  |  |

| 3  | Con                      | vention      | al reliability techniques             | 25   |  |  |  |

|    | 3.1                      | Read/v       | vrite bias assist techniques          | . 25 |  |  |  |

|    | 3.2                      | Cell ch      | noice (6T/8T)                         | . 26 |  |  |  |

|    | 3.3                      | Cell si      | zing                                  | . 27 |  |  |  |

|   | 3.4  | Error control coding                    | 8  |

|---|------|-----------------------------------------|----|

|   |      | 3.4.1 Conventional ECC overheads        | 9  |

|   |      | 3.4.2 Multi-bit ECC                     | 1  |

|   |      | 3.4.3 Vertical parity                   | 5  |

|   | 3.5  | Redundancy                              | 6  |

|   | 3.6  | Peripheral logic fault detection        | 7  |

|   | 3.7  | Summary                                 | 9  |

| 4 | Cell | array protection 4                      | 10 |

|   | 4.1  | Erasure coding theory                   |    |

|   | 4.2  | Erasure detection                       |    |

|   | 4.3  | Erasure correction                      |    |

|   | 4.4  | Offline erasure detection               |    |

|   | 4.4  |                                         |    |

|   | 4.3  | Runtime erasure detection               |    |

|   |      | 4.5.1 Ternary-output sense amplifier    |    |

|   |      | 4.5.2 Overhead                          |    |

|   |      | 4.5.3 Simulation methodology            |    |

|   |      | 4.5.4 Results                           | 5  |

|   | 4.6  | Summary                                 | 8  |

| 5 | Peri | pheral circuitry protection 6           | 3  |

|   | 5.1  | Particle strike locality                | 3  |

|   | 5.2  | Peripheral logic fault detection        | 7  |

|   |      | 5.2.1 Wordline assertion comparator     | 9  |

|   |      | 5.2.2 Results                           | 3  |

|   | 5.3  | Summary                                 | 5  |

| 6 | Prot | otype testchip with erasure-based ECC 7 | 6  |

|   | 6.1  | Core memory                             | 7  |

|   |      |                                         |    |

| Bil | ibliography 96 |          |                                                                     |    |  |

|-----|----------------|----------|---------------------------------------------------------------------|----|--|

| A   | Metl           | hodolog  | y.                                                                  | 95 |  |

| Ap  | appendices     |          |                                                                     |    |  |

|     |                | 7.2.3    | Soft-decision decoding beyond read latency erasures                 | 93 |  |

|     |                | 7.2.2    | Peripheral logic protection                                         | 93 |  |

|     |                | 7.2.1    | Implications of erasure coding with multiple error correcting codes | 92 |  |

|     | 7.2            | Future   | research directions                                                 | 92 |  |

|     | 7.1            | Contrib  | butions                                                             | 91 |  |

| 7   | Cone           | clusions | s and future work                                                   | 91 |  |

|     | 6.7            | Summa    | ary                                                                 | 89 |  |

|     | 6.6            | Testing  | g                                                                   | 88 |  |

|     |                | 6.5.3    | Architectural latency overhead                                      | 87 |  |

|     |                | 6.5.2    | Local array overhead                                                | 87 |  |

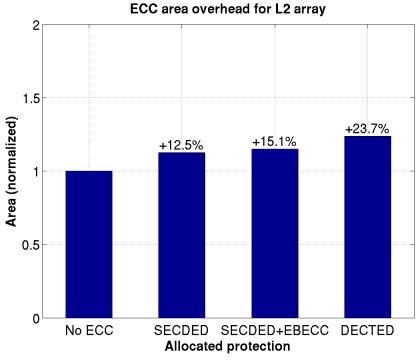

|     |                | 6.5.1    | Area overhead of EB-ECC                                             | 85 |  |

|     | 6.5            | System   | n overheads                                                         | 85 |  |

|     | 6.4            | Synthe   | sized logic and test modes                                          | 81 |  |

|     | 6.3            | Supple   | mental memories                                                     | 80 |  |

|     | 6.2            | ROM a    | address bits                                                        | 79 |  |

# **List of Figures**

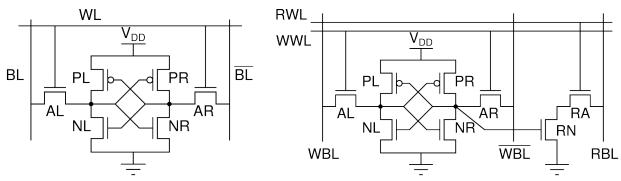

| 2.1 | SRAM cells                                                                                            | 6  |

|-----|-------------------------------------------------------------------------------------------------------|----|

| 2.2 | Simplified flow diagram of SRAM. Central boxes represent memory cells. Bit-                           |    |

|     | line can be single-ended or a pair of differential bitlines                                           | 6  |

| 2.3 | The failure rate over the product lifecycle is frequently depicted by this "bathtub                   |    |

|     | curve". Broad categories of failure sources are shown above the curve, while                          |    |

|     | lifecycle phases and conventional countermeasures are shown below                                     | 9  |

| 2.4 | Energetic particle strike causing current to flow across nominally off NFET until                     |    |

|     | charge dissipates                                                                                     | 12 |

| 2.5 | Careful layout including mirrored or common centroid configurations can min-                          |    |

|     | imize systematic variation, and is commonly employed in analog cells such as                          |    |

|     | the sense amplifier                                                                                   | 13 |

| 2.6 | 6T cell failure types. Mismatched transistors and/or another fault within a cell                      |    |

|     | can cause failure in cell operation (initialized as $V_L = V_{DD}, V_R = V_{SS}$ )                    | 15 |

| 2.7 | Depiction of read latency and critical $t_{WL \to SAE}$ delay. If $\Delta V_{BL} < V_{offset}$ at the |    |

|     | time of SAE, the value on the bitlines is incorrectly sensed and a read latency                       |    |

|     | failure will occur.                                                                                   | 17 |

| 2.8 | Static noise margin measurements [69]                                                                 | 18 |

| 2.9 | Failures occurring in the data path may be detectable or correctable by ECC;                          |    |

|     | failures occurring in the address path are commonly neither detectable nor cor-                       |    |

|     | rectable by ECC and so must be dealt with through other means                                         | 21 |

| 2.10 | Address decoder failure types                                                                              | 22 |

|------|------------------------------------------------------------------------------------------------------------|----|

| 3.1  | SRAM cells                                                                                                 | 27 |

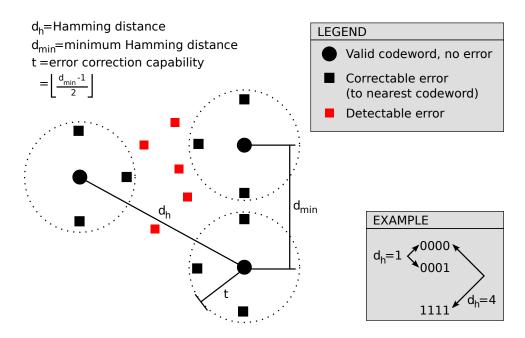

| 3.2  | Hamming spheres illustrate the limitations of error detection and correction.                              |    |

|      | Each sphere, centered on a codeword, contains a number of vectors which are                                |    |

|      | a maximum Hamming distance t from it and are thus correctable. Vectors out-                                |    |

|      | side the sphere are detectable as errors. Note that vectors which have more than t                         |    |

|      | bits changed (distance) from their correct codeword may fall in the wrong sphere                           |    |

|      | and thus be miscorrected. This represents an undetected error.                                             | 29 |

| 3.3  | Hamming sphere representation of ECC of various correction capacities. Black                               |    |

|      | bits represent message word bits, blue bits represent added parity bits, black cir-                        |    |

|      | cles represent codewords, black squares represent correctable errors, red squares                          |    |

|      | represent detectable errors, and the dotted circles represent decoding spheres                             |    |

|      | whose radius is $t = \lfloor (d_{min} - 1)/2 \rfloor$ . Comparison of (n, k) codes from $d_{min}$ =2 to 4. | 30 |

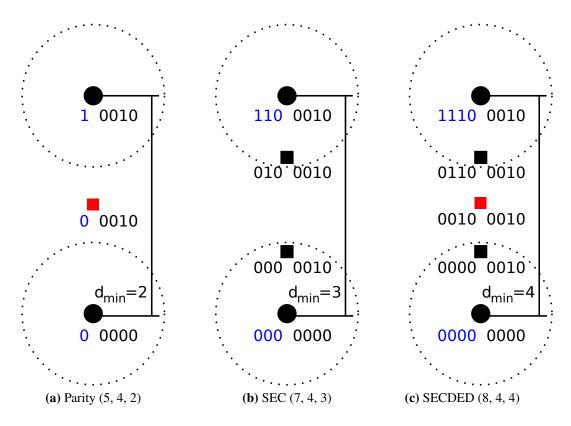

| 3.4  | Decoder for (72, 64) SECDED ECC, minimum Hamming distance $d_{min}=4$                                      | 32 |

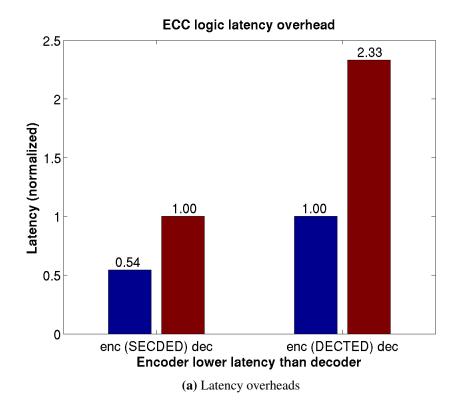

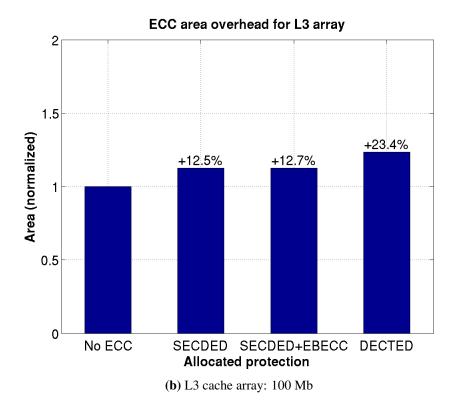

| 3.5  | Normalized overheads of ECC encoder/decoder: data from Table 3.1 [53]                                      | 33 |

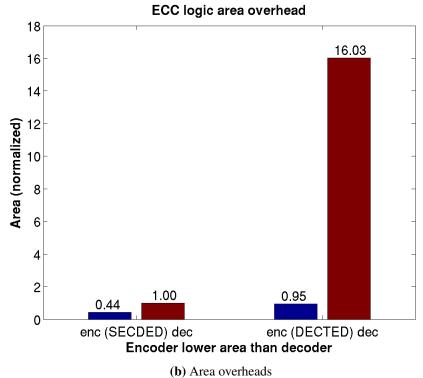

| 3.6  | Illustration of area overheads. ECC encode/decode logic has fixed area regard-                             |    |

|      | less of array size, whereas parity/check bit storage has area overhead proportional                        |    |

|      | to the array capacity and thus does not diminish in importance for a larger mem-                           |    |

|      | ory. Fixed area overheads and their relative area difference between single error                          |    |

|      | correcting, double error detecting (SECDED) and double error correcting, triple                            |    |

|      | error detecting (DECTED) logic not to scale (see Figure 3.5)                                               | 34 |

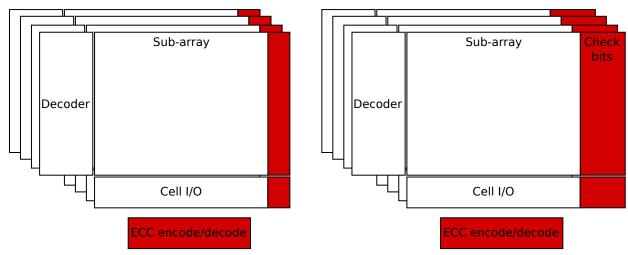

| 3.7  | 2D coding / vertical parity illustration. When the horizontal ECC detects an un-                           |    |

|      | correctable error, the controller initiates a vertical parity recovery process. Note                       |    |

|      | that the combination of a one-bit hard error and one-bit soft error can both be cor-                       |    |

|      | rected, allowing for use of a word with a manufacture-time failure or marginal                             |    |

|      | operation condition. [35]                                                                                  | 35 |

| 3.8  | WL encoder enables detection of most common address decoder faults [82]                                    | 38 |

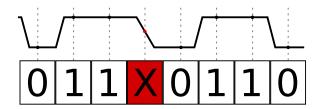

| 4.1  | Illustration of an erasure (denoted by X) in a serial data stream. The dotted         |    |

|------|---------------------------------------------------------------------------------------|----|

|      | vertical lines indicate sampling intervals; when the signal's slew rate is poor or    |    |

|      | the sampling interval is timed at a point when the signal is still transitioning from |    |

|      | one rail to the other, the digital value cannot be reliably sensed and an erasure is  |    |

|      | detected                                                                              | 41 |

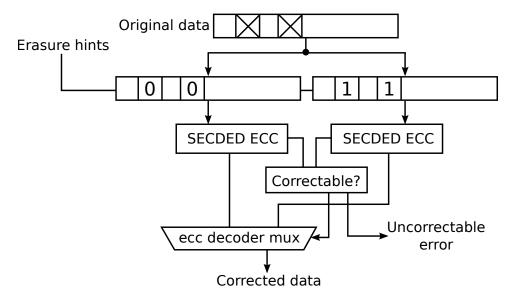

| 4.2  | Correction mechanism with erasures (number of random errors $e=0$ , number            |    |

|      | of erasures $f=2$ , number of additional detectable errors $g=1$ ) [37]               | 43 |

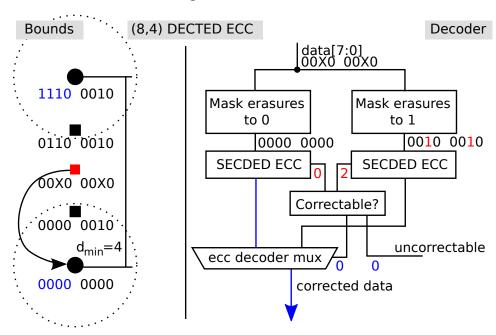

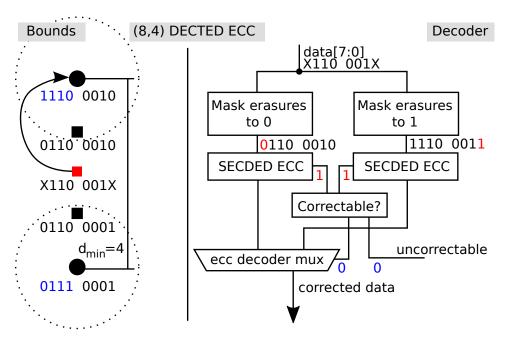

| 4.3  | Correction of a two-bit erasure pattern: with the erasures masked to 0, the correct   |    |

|      | codeword is revealed (0 bits in error are detected by the SECDED ECC unit); on        |    |

|      | the other hand, with the erasures masked to 1, 2 bits in error are detected by the    |    |

|      | SECDED unit and thus the 0-masked word is muxed to the corrected data output.         | 44 |

| 4.4  | Correction of a two-bit erasure pattern: with the erasures masked to 0, the SECDED    |    |

|      | corrects a single-bit error. The same occurs with the erasure masked to 1, and so     |    |

|      | either output is the properly corrected data word.                                    | 45 |

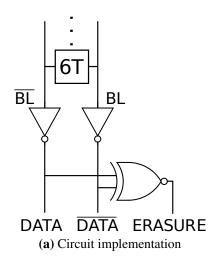

| 4.5  | Runtime erasure detection circuit for access/read latency failures [37]. This de-     |    |

|      | sign is suitable for full-swing bitlines                                              | 47 |

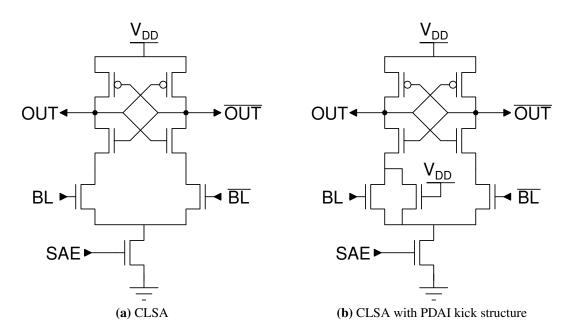

| 4.6  | Current-latching sense amplifier and parallel device assist implementation (PDAI)     |    |

|      | kick structure [5]                                                                    | 49 |

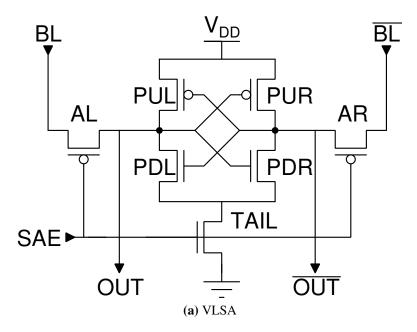

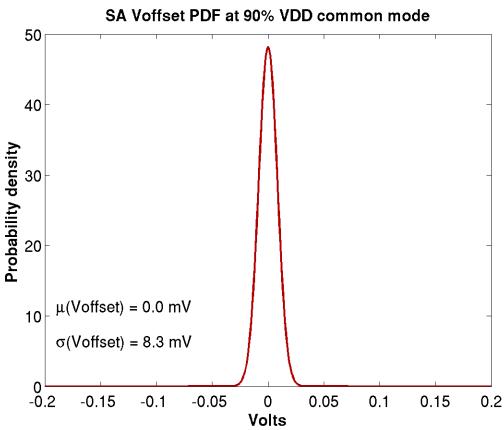

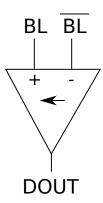

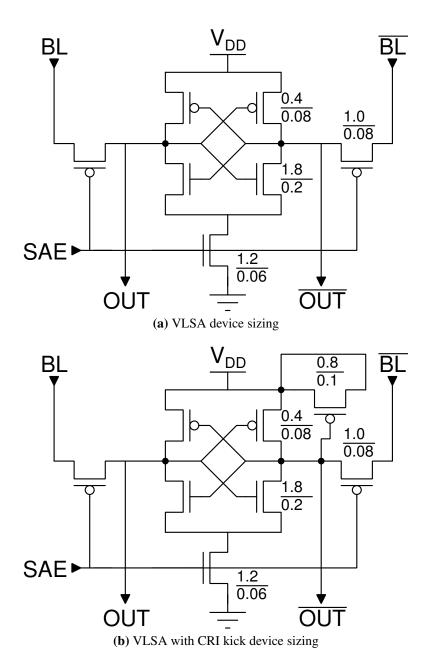

| 4.7  | Voltage-latching sense amplifier and offset probability density function (PDF)        | 50 |

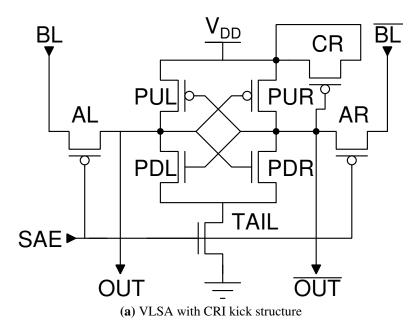

| 4.8  | Voltage-latching sense amplifier with capacitive resist implementation (CRI) kick     |    |

|      | structure and offset PDF                                                              | 51 |

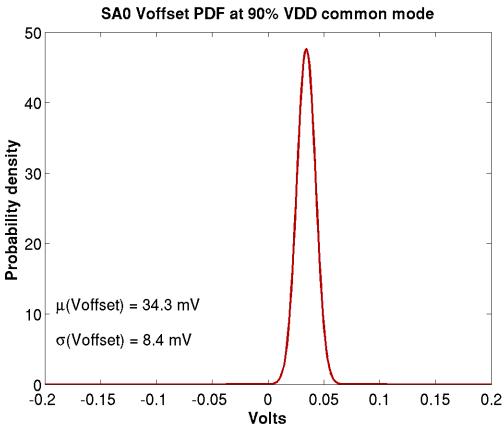

| 4.9  | Symbolic representation of voltage-latching sense amplifier (VLSA) with CRI           |    |

|      | kick in same configuration as Figure 4.8                                              | 52 |

| 4.10 | Sense amplifier sizing; all measurements in microns.                                  | 53 |

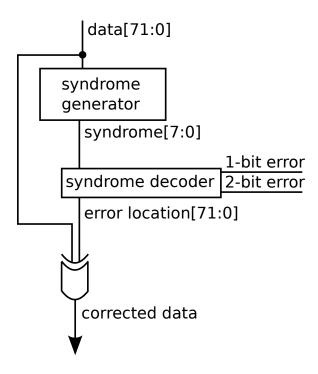

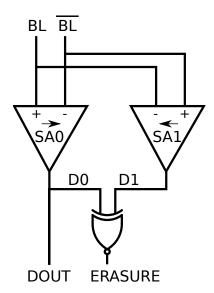

| 4.11 | Ternary-output sense amplifier (TOSA) block diagram. Each sense amp's input-          |    |

|      | referred offset is "kicked" away from 0 in opposite directions                        | 54 |

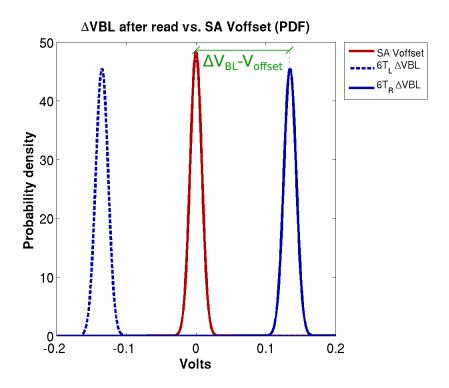

| 4.12 | PDF of the sense amplifier's input-referred offset compared with the bitline dif-  |    |

|------|------------------------------------------------------------------------------------|----|

|      | ferential developed after 300 ps of wordline assertion by the worst-case (lowest   |    |

|      | ION) cell in the 128-cell column. $V_{DD}$ =1.08V, T=27° C                         | 57 |

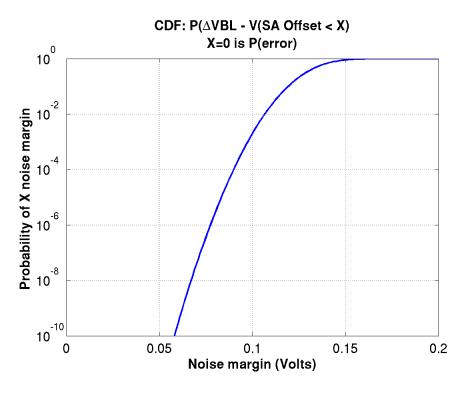

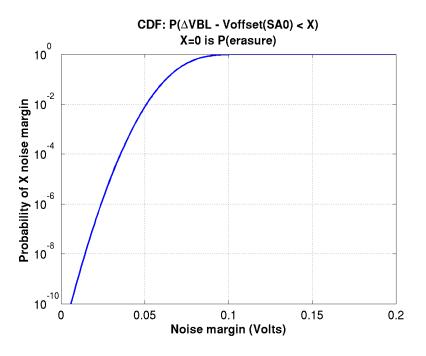

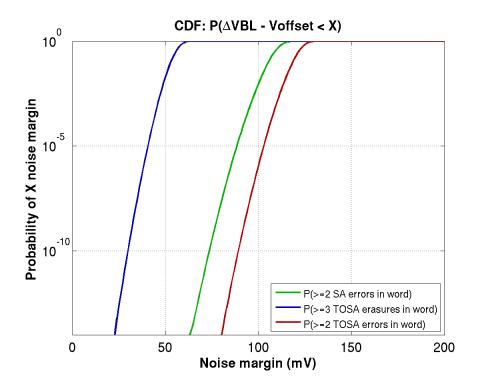

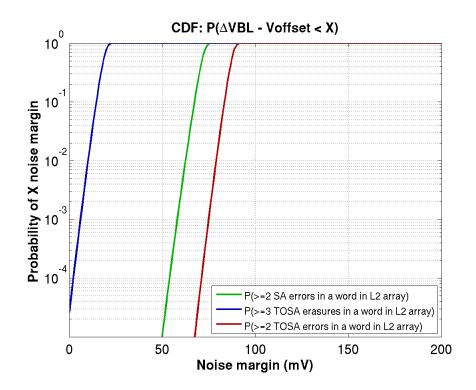

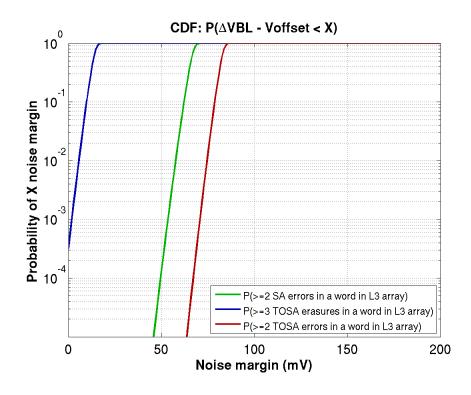

| 4.13 | Cumulative distribution function (CDF) of 6T cell bitline swing vs. sense ampli-   |    |

|      | fier offset, $V_{DD}$ =1.08V, T=27° C                                              | 57 |

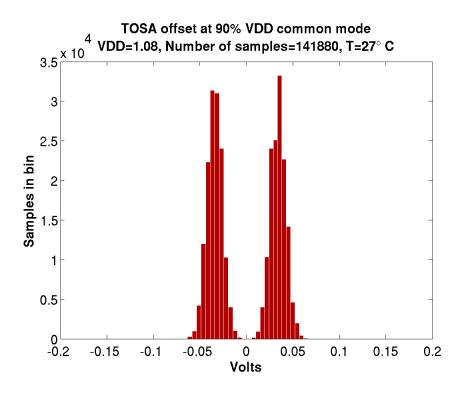

| 4.14 | Histogram of ternary output sense amplifier offsets, $V_{DD}$ =1.08V, T=27° C      | 58 |

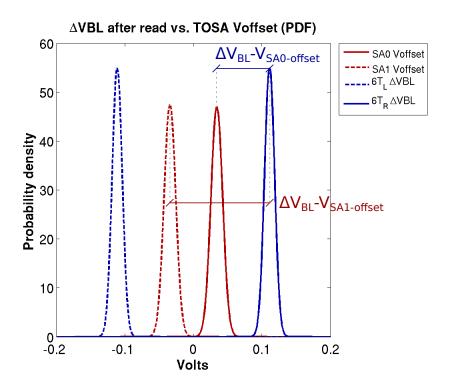

| 4.15 | PDF of each of the TOSA's input-referred offsets compared with the bitline dif-    |    |

|      | ferential developed after 300 ps of wordline assertion by the worst-case (lowest   |    |

|      | ION) cell in the 128-cell column. Note that the mean bitline differential is lower |    |

|      | than in Figure 4.12 due to the increased capacitance on the bitline from the extra |    |

|      | sense amplifier (SA). $V_{DD}$ =1.08V, T=27° C                                     | 59 |

| 4.16 | CDF of 6T cell bitline swing vs. TOSA offsets. This indicates the likelihood of    |    |

|      | detectable erasure. $V_{DD}$ =1.08V, T=27° C                                       | 59 |

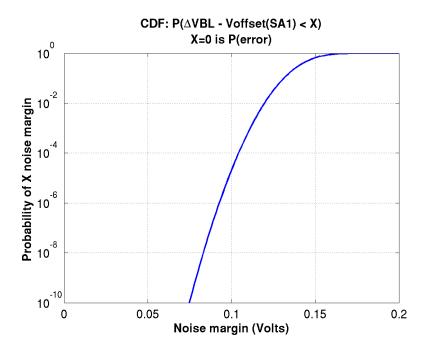

| 4.17 | CDF of 6T cell bitline swing vs. TOSA offsets. This indicates the likelihood of    |    |

|      | undetectable error. $V_{DD}$ =1.08V, T=27° C                                       | 60 |

| 4.18 | CDF of 6T cell bitline swing vs. SA and TOSA offsets. This indicates the like-     |    |

|      | lihood of uncorrectable error in a 72-bit word with SECDED ECC. $V_{DD}$ =1.08V,   |    |

|      | T=27° C                                                                            | 60 |

| 4.19 | CDF of 6T cell bitline swing vs. SA and TOSA offsets. This indicates the           |    |

|      | likelihood of uncorrectable error in an 8Mb L2 SRAM with SECDED ECC.               |    |

|      | $V_{DD}$ =1.08V, T=27° C                                                           | 61 |

| 4.20 | CDF of 6T cell bitline swing vs. SA and TOSA offsets. This indicates the           |    |

|      | likelihood of uncorrectable error in a 100Mb L3 SRAM with SECDED ECC.              |    |

|      | $V_{DD}$ =1.08V, T=27° C                                                           | 61 |

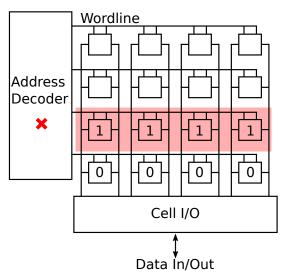

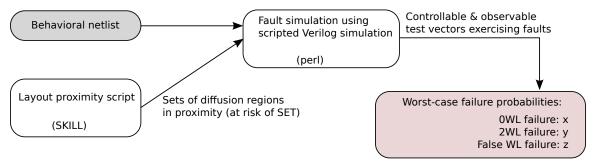

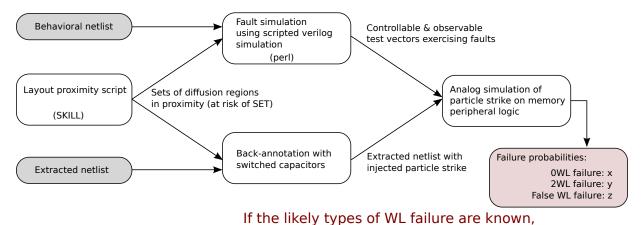

| 5.1  | Particle strike effect study: Process                                              | 64 |

| 5.2  | Fault simulation: example                                                          | 65 |

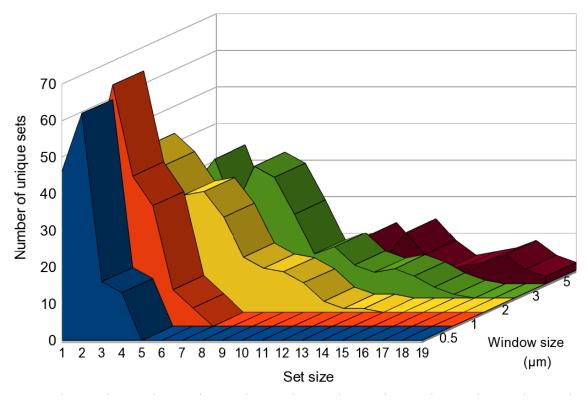

| 5.3  | Layout proximity: number of unique sets, by number of nodes per set, found in         |    |

|------|---------------------------------------------------------------------------------------|----|

|      | each window size                                                                      | 66 |

| 5.4  | Layout proximity: number of sets found in each window size                            | 66 |

| 5.5  | Results of an examination of layout proximity in an industrial SRAM row de-           |    |

|      | coder. 0.7 on y-axis of unweighted graph indicates 70% of sets manifested the         |    |

|      | failure type on the x-axis. The weighted graph multiplies this number by the pro-     |    |

|      | portion of failing patterns to total tested patterns, e.g., if 70% of sets manifested |    |

|      | a 1WL failure type and these sets on average demonstrated failure in 248/256          |    |

|      | patterns, the weighted probability would be 0.68                                      | 67 |

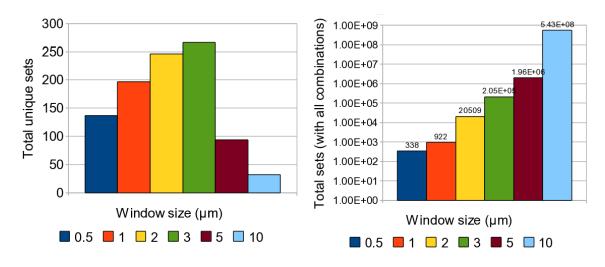

| 5.6  | Local area overhead of both read-only memory (ROM) address storage and word-          |    |

|      | line assertion comparator                                                             | 68 |

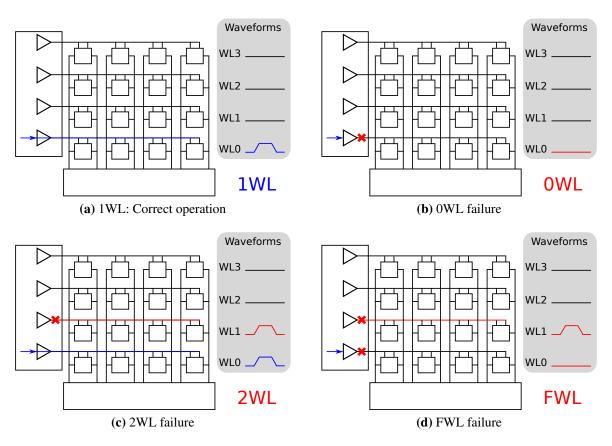

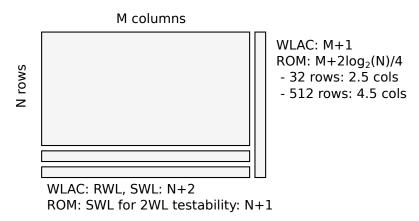

| 5.7  | WL assertion comparator enables detection of "no-row" or "multi-row" address          |    |

|      | decoder faults                                                                        | 69 |

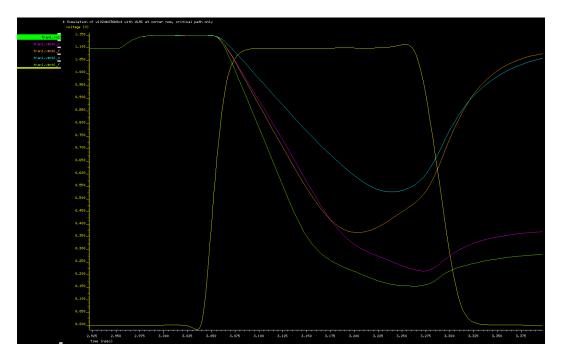

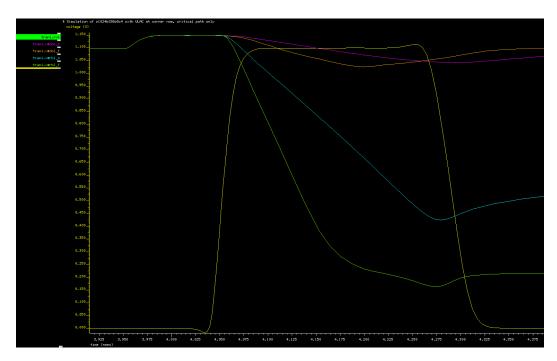

| 5.8  | Waveform showing correct operation detected by the wordline assertion com-            |    |

|      | parator (WLAC). Correct behavior is indicated when the check bitlines are be-         |    |

|      | low the reference ceiling and above the reference floor, i.e., check bitline ceiling  |    |

|      | (CBLC) < reference bitline ceiling (RBLC) and check bitline floor (CBLF) >            |    |

|      | reference bitline floor (RBLF). Legend: yellow = RWL, pink = CBLC, orange =           |    |

|      | RBLC, blue = CBLF, green = RBLF                                                       | 71 |

| 5.9  | Waveform showing no wordline (0WL) failure mode detected by the WLAC.                 |    |

|      | The incorrect behavior is detected, as the check bitlines are above the reference     |    |

|      | ceiling, i.e., CBLC > RBLC. Legend: yellow = RWL, pink = CBLC, orange =               |    |

|      | RBLC, blue = CBLF, green = RBLF                                                       | 72 |

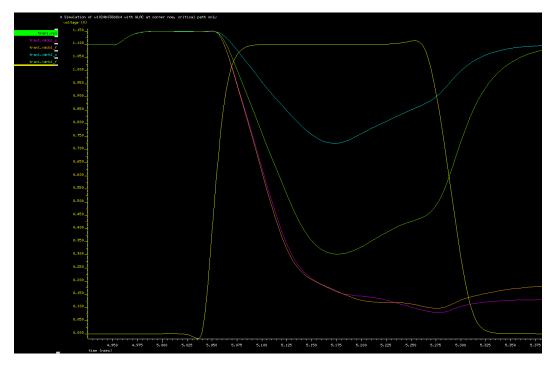

| 5.10 | Waveform showing multiple wordline (2WL) failure mode detected by the WLAC.           |    |

|      | The incorrect behavior is detected, as the check bitlines are below the reference     |    |

|      | floor, i.e., CBLF < RBLF. Legend: yellow = RWL, pink = CBLC, orange =                 |    |

|      | RBLC, blue = CBLF, green = RBLF                                                       | 72 |

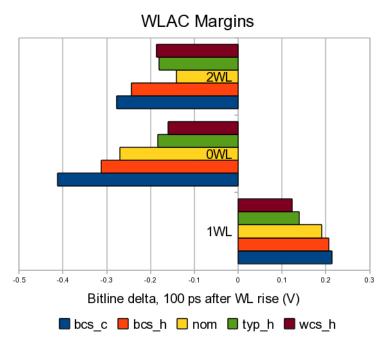

| 5.11 | Comparison of margins across corners                                              |

|------|-----------------------------------------------------------------------------------|

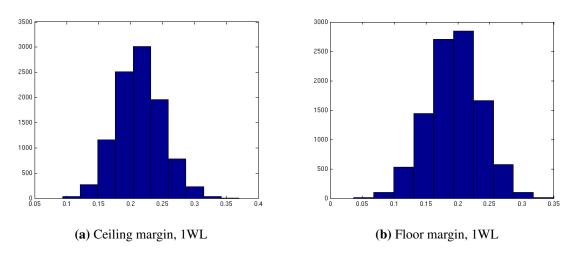

| 5.12 | WLAC margins: correct operation. Ceiling pair: $\mu=213mV$ ; $\mu-4\sigma=92mV$   |

|      | Floor pair: $\mu = 195 mV$ ; $\mu - 4\sigma = 35 mV$                              |

| 5.13 | WLAC margins: failing operation. Ceiling pair: $\mu = -270mV; \mu + 4\sigma =$    |

|      | $-197mV$ Floor pair: $\mu = -154mV$ ; $\mu + 4\sigma = -43mV$                     |

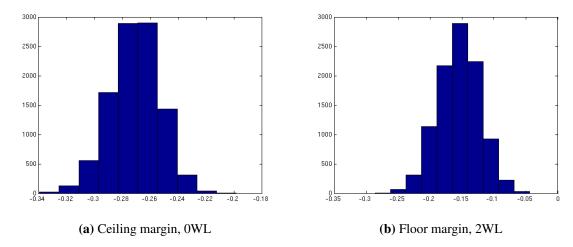

| 6.1  | Top-level layout of testchip on 55nm bulk complementary metal-oxide-semiconductor |

|      | (CMOS) process, containing a core SRAM, the novel erasure-based error con-        |

|      | trol coding (EB-ECC) modules, and built-in self-test (BIST) circuitry necessary   |

|      | to test the functionality of the design                                           |

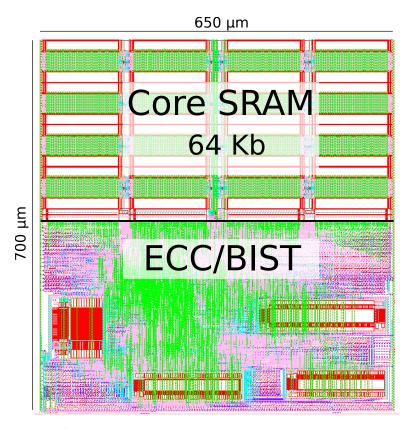

| 6.2  | Enlarged view of synthesized ECC, BIST logic, and supplemental memories 78        |

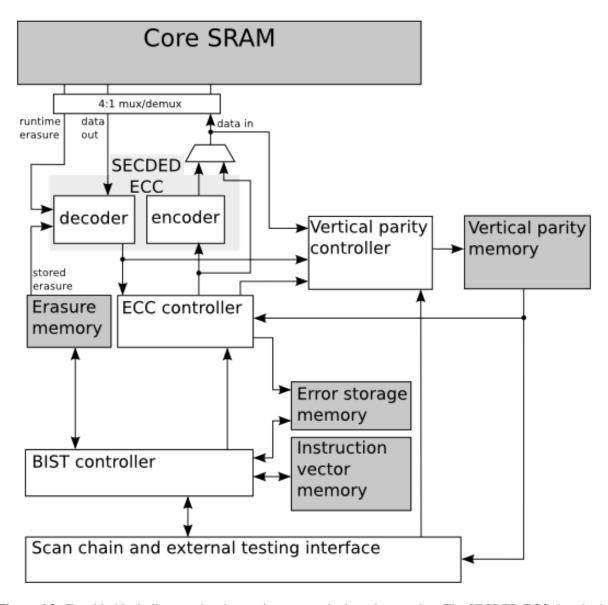

| 6.3  | Testchip block diagram showing testing support logic and memories. The SECDED     |

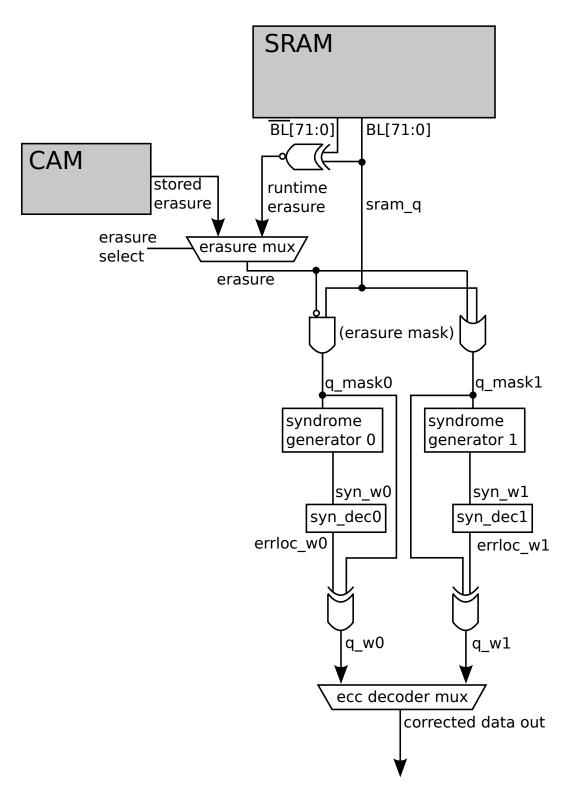

|      | ECC decoder in the shaded region is shown in greater detail in Figure 6.4 82      |

| 6.4  | ECC datapath showing erasure masking and SECDED decoding circuits 83              |

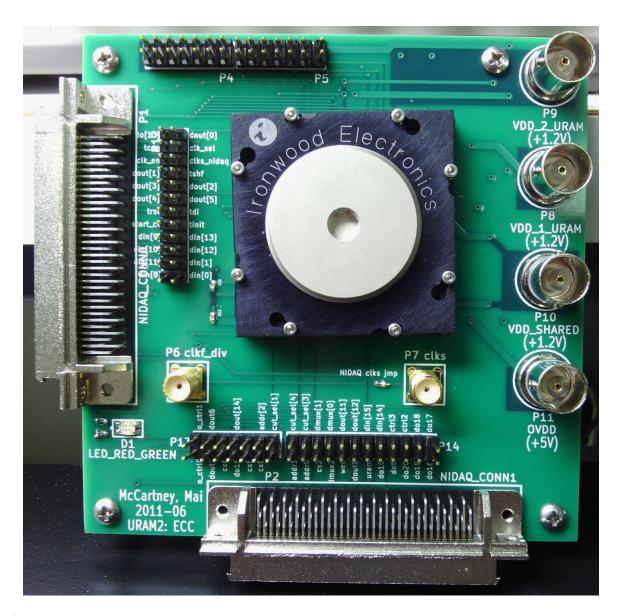

| 6.5  | PCB with socket and all components populated, disconnected from the DAQ           |

|      | board and power supplies                                                          |

| 6.6  | Practical area overhead for a typical L2 and L3 array. Sizes selected based on    |

|      | Intel Xeon 7100 dual-core (65nm) [13]                                             |

| 7.1  | Flowchart of full particle strike study                                           |

## **List of Tables**

| 3.1 | ECC encoder/decoder latency and area overheads in IBM 90nm bulk CMOS                         |    |

|-----|----------------------------------------------------------------------------------------------|----|

|     | process with 64-bit data word, $\tau_{FO4}$ =39 ps, and $\lambda$ =40 nm [53]                | 32 |

| 3.2 | ECC encoder/decoder latency and area overheads estimated by scaling in ST                    |    |

|     | 65nm bulk CMOS process with 64-bit data word, $\tau_{FO4}$ =31 ps, and $\lambda$ =30 nm [53] | 32 |

| 4.1 | Potential implementations of a Hamming code with minimum distance 4. The                     |    |

|     | SECDED implementation is commonly used, but with a source of erasure hints,                  |    |

|     | two bits flagged as erasures can be corrected and an additional random bit error             |    |

|     | detected                                                                                     | 42 |

| 6.1 | Testchip detail                                                                              | 78 |

| 6.2 | Area breakdown of testchip                                                                   | 85 |

## List of terms and abbreviations

$\tau_{FO4}$  delay for a fanout-of-4 inverter. xviii, 32

**0WL** no wordline. xvi, 22, 23, 62, 63, 67–71, 73

**2WL** multiple wordline. xvi, 22, 23, 62, 63, 67–71, 73

BISR built-in self-repair. 8, 10, 24, 89

**BIST** built-in self-test. xvii, 3, 8, 10, 24, 35, 74–76, 78, 83, 86, 87, 89

**CAM** content-addressable memory. vii, 3, 43, 73, 78, 79, 86, 88

**CBL** check bitline. 67, 68

**CBLC** check bitline ceiling. xvi, 68–70

**CBLF** check bitline floor. xvi, 68–70

**CDF** cumulative distribution function. xv, 19, 53, 54, 56–59

**CLSA** current-latching sense amplifier. 47

**CMOS** complementary metal-oxide-semiconductor. xvii, 71, 73–75

**CRI** capacitive resist implementation. xiv, xv, 47, 49–51

**DAQ** data acquisition. xvii, 82

**DECTED** double error correcting, triple error detecting. xiii, 31, 32, 34, 40, 42, 83, 85

**DMR** dual modular redundancy, in which two redundant versions of a system operate in lockstep, declaring an error if they disagree. 31, 35 **DRAM** dynamic random access memory. 4

**EB-ECC** erasure-based error control coding. vii, xvii, 2, 74, 75, 83, 85

**ECC** error control coding. v, x, xii–xv, xvii, xviii, 2, 3, 8, 10, 20, 21, 28–34, 36, 39, 42, 47, 52, 54, 58, 59, 65, 71, 73, 74, 76, 78–81, 83, 85–87

**eDRAM** embedded dynamic random access memory. 4, 5

**FWL** false wordline. 22, 23, 62, 73

**GWF** gate work function. 13

**HCI** hot-carrier injection. 7, 8, 10, 27

**HSNM** hold static noise margin. 18, 19

LDPC low-density parity check. 91

**LER** line-edge roughness. 13

**MC** Monte Carlo. 19, 50, 52, 71

MLC multi-level cells. 91

**NBTI** negative-bias temperature instability. 8, 10

**NFET** n-channel field-effect transistor. xii, 6, 12, 16, 17, 67

**OPC** optical proximity correction. 9

**PCB** printed circuit board. vii, xvii, 82

**PDAI** parallel device assist implementation. xiv, 47

**PDF** probability density function. xiv, xv, 48, 49, 53, 55, 56

**PFET** p-channel field-effect transistor. 6

**POST** power-on self test. 43

**RBL** reference bitline. 67, 68

**RBLC** reference bitline ceiling. xvi, 68–70

**RBLF** reference bitline floor. xvi, 68–70

**RDF** random dopant fluctuation. 13

**ROM** read-only memory. xvi, 3, 36, 66, 69, 73, 77–79, 86, 87

**RSNM** read static noise margin. 18, 19

**SA** sense amplifier. 53, 54

**SECDED** single error correcting, double error detecting. xiii–xv, xvii, xviii, 30–32, 34, 40–43, 53, 54, 58, 59, 71, 77–81, 83, 85–87

**SET** single event transient. 11, 62, 71

**SEU** single event upset. 11, 20, 23, 61

**SNM** static noise margin. 18

**SOI** silicon on insulator. 25

**SRAM** static random access memory. v, vii, xii, xiii, xv–xvii, 2–8, 11, 14, 19, 20, 23, 25–28, 31, 34, 39, 47, 58–62, 65, 66, 74, 75, 77, 79, 87, 89, 91

**TDDB** time-dependent dielectric breakdown. 10, 26

**TMR** triple modular redundancy, in which three redundant versions of a system vote to decide the correct output. 31, 35

TOSA ternary-output sense amplifier. xv, 38, 46, 52–54, 59, 85

**VLSA** voltage-latching sense amplifier. xv, 47–51

WBWL wrong-block wordline. 23, 62, 63, 73

**WLAC** wordline assertion comparator. xvi, xvii, 3, 68–73

WM write margin. 18, 19

## Chapter 1

### Introduction

Microelectronics have become ubiquitous in modern society, and their functionality is rapidly overtaking many of the tasks of which previously only humans were capable. While this development promises to bring the exponential growth curve of Moore's law<sup>1</sup> [49, 50] to bear in new environments, there is a challenge in designing computer systems for reliability. For safety-critical tasks in the automotive, industrial, and medical sectors, both software and hardware must be guaranteed to operate exactly according to the designers' intent, or to fail safely with advance warning. Many of these safety-critical systems can be classified as cyber-physical systems, which are "engineered systems that are built from, and depend upon, the seamless integration of computational algorithms and physical components." [54]. Each component of the hardware design must be designed for reliability to mitigate the risks inherent in systems which perform tasks interacting with humans in their physical environment, such as self-driving cars, robotic assembly equipment, or life-sustaining implantable medical devices. One important component of any hardware design is its memory system, which stores and retrieves the instructions and data that control the operation of the cyber-physical system.

In microprocessors and systems-on-a-chip (SoCs), the embedded memory system plays a significant role in the overall system performance, area, and power. In modern microprocessors

<sup>&</sup>lt;sup>1</sup>Gordon Moore originally predicted in 1965 that the number of transistors on a die would double every year; this was revised by Moore in 1975 to a density-doubling period of 24 months with a performance-doubling period of 18 months, and has held remarkably consistent up to the present day.

and SoCs, the cache hierarchy is often in the critical path of the design, can utilize 25-50% of the die area [1, 13, 20, 40, 62], and can consume an appreciable fraction of the total power. Thus, the reliability and yield of the memory system is crucial to the reliability and yield of the entire system. However, as process technologies scale, ensuring reliability is becoming increasingly difficult due to a number of factors including process variability, susceptibility to energetic particle strikes, and aging.

In this thesis, we examine the landscape of design techniques for reliability, and introduce two novel contributions for improving reliability with low overhead, these being an erasure-based error control coding (EB-ECC) scheme with runtime erasure detection, and address decoder failure detection by wordline assertion comparator. To better understand the practical implications of these techniques, we have fabricated a prototype testchip containing early versions of EB-ECC (including vertical parity protection [35, 45]) and address decoder failure detection.

First, we provide background on static random access memory (SRAM) and its role within the memory hierarchy, the ways in which it can fail and the manner in which those failures manifest in both the cell array and the peripheral circuitry. By so doing, we supply the groundwork to evaluate our novel contributions for detecting and correcting these errors.

In Chapter 3 we present a review of conventional reliability/resiliency techniques. We focus on the following techniques which have received wide industry acceptance: read/write bias assist, 6T/8T cell choice, cell sizing, error control coding (ECC), and redundancy. Since the novel techniques developed by the thesis contributions are mostly orthogonal to these conventional techniques, with the exception of the 8T cell which is incompatible with our designs for runtime erasure detection, our discussion of them is qualitative in nature. In Chapter 4 we present our work in cell array protection with EB-ECC. By identifying erasures, or the locations of bits likely to be failing, we can double the number of bits correctable by the ECC being used. This is a widely-known concept in communications, but to the best of our knowledge has not been realized for the purpose of improving SRAM reliability in the literature. The challenge of using erasures in SRAM is in their identification; we present low-cost solutions for both runtime detection and

offline storage of erasures.

In Chapter 5 we discuss peripheral logic fault detection and present our wordline assertion comparator (WLAC) design. We evaluate the differences between an existing technique and our novel technique, generating enough information to allow designers to make a decision as to which scheme is suitable for a memory with given array size and specifications. The WLAC design has area overhead advantages over the current state-of-the-art address decoder failure detection design of read-only memory (ROM) address storage for large SRAM sub-arrays.

Finally, in Chapter 6 we present a testchip implementation of a few of the above reliability techniques on a 55nm bulk CMOS process. The fabricated testchip contains the first implementation of vertical parity and erasure coding in SRAM and thus represents an important step in the understanding of the technique's requirements and overheads at the circuit level. The testchip's erasure coding scheme is designed with two sources of erasures: an on-die content-addressable memory (CAM) which can be loaded with detected erasure locations for offline erasure storage, as well as full-swing bitline read latency failure detection circuits which provide run-time erasure hints to the ECC decoder. All these separate options can be toggled via scan-chain-controlled on-die built-in self-test (BIST).

## Chapter 2

## **Background**

In the introduction, we provided motivation and context for the thesis; in this chapter, we discuss fundamental aspects of SRAM design, and the choices designers make to attain yield and reliability. We cover the causes and ways in which memories can fail to provide the groundwork to evaluate our novel contributions for detecting and correcting these errors. Classifications of both types of failures and the various components of memories where these failures may occur are presented.

#### 2.1 Memory system

In computer systems, the memory system is organized in a hierarchy in order to maximize system performance under cost constraints. The top level of this hierarchy is fast and small, while the bottom level is slow and large. They work together to give the illusion of being both fast and large by the process of caching, or keeping in the top levels of the cache hierarchy data which will be used in the near future. The cache hierarchy is divided between on-chip (embedded) and off-chip memory. The embedded memory space is currently dominated by SRAM because of its logic process compatibility and low latency, while off-chip memory is dominated by dynamic random access memory (DRAM) due to its density which reduces cost. Embedded dynamic random access memory (eDRAM) is also a commonly-used on-chip memory type for last level

caches due to its density advantages over SRAM, though it requires additional fabrication steps. Recently, designers have had such strong demand for more capacity and bandwidth that they have packaged a separate eDRAM die alongside the CPU connected through on-package IO [22, 40].

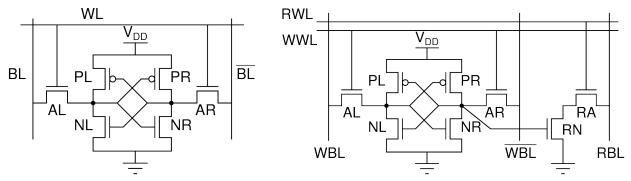

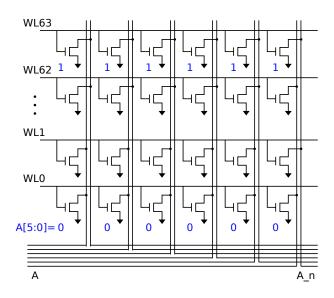

#### 2.1.1 SRAM cell array

The fundamental element of SRAM is the cell, which contains bistable latching circuitry of two cross-coupled inverters with two access transistors (Figure 2.1a). These cells are arranged in two-dimensional arrays for compactness and simple access; a row of cells in the horizontal dimension share a wordline, while a column of cells in the vertical dimension share two or more bitlines (Figure 2.2). Under this arrangement, when the access devices of a row are turned on via a single wordline being asserted, each cell on that wordline is exposed to the bitlines, and can either perform a read or a write, depending on the state of the bitlines while the wordline is asserted. To perform a read, the bitlines are reset to  $V_{DD}$  prior to wordline assertion and then left floating. Thus, one of the bitlines will be pulled down by the cell's pulldown device and access device. This voltage difference between the bitlines can then be sensed by peripheral circuits. To perform a write, one bitline is driven to  $V_{DD}$  while the other is driven to  $V_{SS}$  by write drivers, and the wordline is asserted. When the access devices turn on, the cell's internal storage nodes will be overwritten to match the voltages on the bitlines.

Many variants on this basic six-transistor (6T) design exist to satisfy various requirements such as reliability, multiple-port access, or higher performance. Of these variants, we will focus on the 8T cell (Figure 2.1b) as it is most commonly employed to improve reliability over the 6T cell while maintaining similar area efficiency or incurring a small area overhead [14, 28]. When using the 8T cell without column multiplexing and operating on a single word per cycle, the read and write operations are separated and can be optimized separately, eliminating the 6T cell's conflict between improving read stability and writeability. Thus the original 6T portion of the 8T cell can be optimized for writeability without the concern that a read will disturb the value on the storage nodes. There are situations in which designers will still choose to

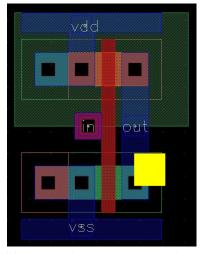

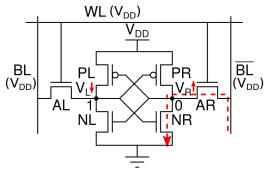

AL/AR), pullup PFET (PL/PR) and pulldown NFET (NL/NR) pair forming bistable storage nodes.

(a) 6T cell with access device pair (left/right: (b) 8T cell. Added devices are read access (RA) and read pulldown (RN), while interconnect consists of write wordline (WWL) and read wordline (RWL), as well as differential write (WBL/ $\overline{WBL}$ ) and single-ended read (RBL) bitlines.

Figure 2.1: SRAM cells

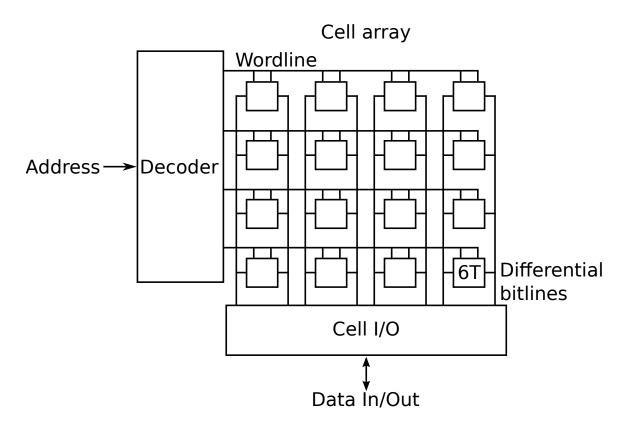

Figure 2.2: Simplified flow diagram of SRAM. Central boxes represent memory cells. Bitline can be single-ended or a pair of differential bitlines.

use column multiplexing with an 8T cell, however, which restores the risk of a read disturb on a write. In systems where the 8T cell's multi-port functionality is used to support a read and write in the same cycle, column muxing might be useful to the designer, particularly if the application does not require high density. Reducing the device sizing in the 8T cell to attain high density exacerbates the cell margins. The use of hot-carrier injection (HCI) techniques can make column muxing with 8T cells more desirable [26], but such a scheme has (to the best of our knowledge) yet to find commercial viability, perhaps due to the extra required manufacture-time testing burden.

#### 2.1.2 SRAM peripheral circuitry

The peripheral circuits mentioned earlier consist of all the circuitry required to access the cells. We can categorize this logic into three paths: the address path, which drives the signals from the input address to the wordlines; the data path, which drives the signals from the bitlines to the input/output data ports; and the control path, which drives the command ports which indicate a read or a write to the local arrays. Since a memory may consist of several arrays of cells, an address decoder is required to determine which wordline in which array should be accessed and assert it. The remaining ports of the cell are the bitlines, which are controlled at the array periphery by reset devices, write drivers, and a sense amplifier to amplify the differential voltage on the bitlines to a digital data output. In the case of a single-ended bitline design, the sense amplifier may be replaced by an inverter.

Since the SRAM cell's devices are near-minimum sized for density while the wordline driver's devices can be sized quite large, it is in the designers' interest to minimize the bitline capacitance to reduce latency, while the wordline capacitance is not as critical a node. Thus, to improve the aspect ratio of the local cell array by reducing the bitline length while increasing the wordline length, column interleaving/multiplexing is commonly employed. It has additional benefits as well: it allows a relaxed 2, 4, or 8 cell pitch for shared bitline I/O circuits such as a large sense amplifier which would otherwise be quite difficult to lay out in a single SRAM cell's pitch. In

addition, interleaving the columns of the SRAM spreads the bits of a single word apart so that an energetic particle strike of a certain radius is far less likely to upset multiple bits of the same word. For instance, a particle strike which would impact 3 bits of a word in an array without column interleaving would impact 1 bit in 3 separate words in an array with 4-way column interleaving, which can be corrected by a low-cost single-bit error-correcting code.

#### 2.2 Error mechanisms in memory

Errors in memory can be detected via testing when the product is manufactured; in the case of these manufacture-time errors, there are multiple options. In situations where the error is minor, only affecting a single bit cell in a row or column of the memory, the error can be repaired by replacing it with a redundant row or column [24, 34]. If the error is sensitive to voltage or timing, it may be possible to employ product binning, configuring it to operate at a higher voltage, slower frequency, or even disabling portions of the memory so that the product can still be sold as a lower-performance or lower-capacity, less expensive option. In the worst case, if errors are caught at manufacture-time and cannot be dealt with through any other means, the product can be discarded before it reaches the consumer.

Errors that occur after manufacture-time testing are more pernicious and there are fewer options available to address them. BIST and built-in self-repair (BISR) mechanisms, or else some means of prevention, must be implemented to handle these run-time failures. Techniques to prevent failures, or to detect and correct them, provide a much-needed capability to the designer of reliable memory systems.

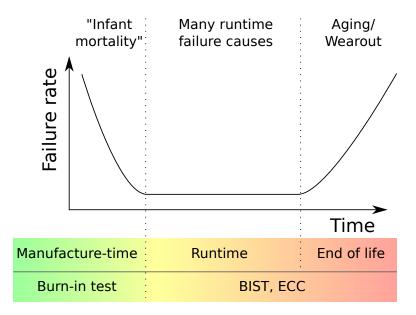

The well-known bathtub curve (Figure 2.3) illustrates the phases of product lifetime and the failure rate during those phases. Infant mortality failures in microelectronics are handled with burn-in test, while errors at runtime which can be caused by particle strikes, aging and wearout including HCI, negative-bias temperature instability (NBTI), electromigration, are handled with BIST and ECC among other countermeasures.

Errors can be coarsely classified along two orthogonal axes as either permanent (hard) or

**Figure 2.3:** The failure rate over the product lifecycle is frequently depicted by this "bathtub curve". Broad categories of failure sources are shown above the curve, while lifecycle phases and conventional countermeasures are shown below.

non-permanent  $(soft)^1$  and as occurring at either manufacture-time or during runtime [8]. We classify some common causes of errors along with conventional countermeasures here.

#### 2.2.1 Hard errors

Hard errors which occur at manufacture-time may be caused by variability; process or mask defects such as particle/occlusion during fabrication which can cause bridge, stuck-at, or open faults. Conventional countermeasures include redundancy, disabling, or post-silicon tuning. At a lower level than these countermeasures, manufacturing defects are minimized by process engineers who employ computational techniques such as optical proximity correction (OPC) and tweak the design rules to limit the use of layout features which, during process characterization, display poor yield [59, 64]. One example of design rule constraints in modern process generations is that polysilicon gate direction is constrained to run in one direction in some designs, and for memory circuits where matching is very important, polysilicon gate lengths have

<sup>&</sup>lt;sup>1</sup>Non-permanent errors can be further classified as transient if their cause is environmental or intermittent if their cause is non-environmental, but we do not make this distinction here.

been constrained to the same value within the cell array. The number of these design rules has been growing at a rapid pace in recent years as process engineers seek to simultaneously fully exploit the next process node's reduced-size geometry and limit the accompanying increase in manufacture-time errors. Recent research has presented a path away from this increasing design rule complexity by proscribing a limited set of regular pattern constructs or templates with which a wide variety of designs, including memory, can be synthesized. This differs from traditional standard-cell synthesized layouts in the way it minimizes the number of unique patterns, effectively making logic gates as regular and printable as memory [29, 51].

Hard errors occurring at run-time may be caused by energetic particle strikes which induce latch-up leading to thermal runaway, device aging/wearout including NBTI, time-dependent dielectric breakdown (TDDB), HCI, electromigration, or other causes. Conventional countermeasures include BIST/BISR, and ECC.

#### 2.2.2 Soft errors

Soft errors are generally regarded as a phenomena which becomes apparent at run-time – at manufacture-time, if an error has occurred, is detected, and cannot be dealt with through one of the countermeasures mentioned above, the faulty product should not be shipped. Run-time soft errors may be caused by energetic particle strike including cosmic rays or  $\alpha$ -particles; temperature variation; leakage; noise including power supply voltage droop, electromagnetic interference, capacitive coupling, or thermal noise; hazards and races due to poor design of critical timing paths; variation/physical irregularity in circuitry due to line edge roughness, random dopant fluctuation or other causes. Conventional countermeasures for these errors include bit interleaving in memory, ECC, fault detection, and read/write assist.

The energetic particle strike failure mechanism deserves further attention because it can often overcome designers' attempts to address it through design solutions.

#### **Energetic particle strikes**

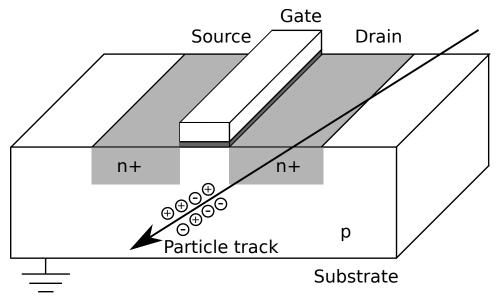

When an energetic particle strikes the silicon substrate, it excites electrons, separating positively charged ions and negatively charged electrons in the substrate via electronic stopping power. The energetic particle can be an alpha particle, which consists of two protons and two neutrons carrying a positive charge and represented by  $\alpha$  or  $\alpha^{2+}$ ; it may also be a neutron created through the interaction of energetic cosmic rays with the Earth's atmosphere [18, 19, 83]. Electronic stopping power describes the energy loss of this energetic charged particle due to collisions with bound electrons in the substrate [30]. In the absence of a significant electric field nearby, the positive and negative charges will recombine. However, if this ionization occurs at a sensitive location near a transistor's channel, the electric field between the drain and body of the transistor separates the positive and negative charge carriers, preventing the recombination; next, the charge collected by the junction results in a transient current in the struck transistor from the substrate to the drain node (Figure 2.4). This is known as a single event transient (SET). Eventually, the charges dissipate and normal operation is restored, but the glitch may propagate if the disturbance is large enough in voltage and time. If the SET causes an incorrect value to be latched at some later node, it is then referred to as a single event upset (SEU). If an energetic particle were to strike a latch or an SRAM cell directly, it could easily cause a SEU without requiring the glitch to propagate through logic.

We present a study of particle strike locality in Section 5.1. Our investigation determines the potential functional fault modes resulting from energetic particle strikes on the address decode logic of an industrial design in the 40nm node. The study specifies the types of faults which will occur given a particle strike in a particular area of the physical layout. The analysis serves to guide our study of which techniques are the most effective at handling these faults given their overhead.

(a) Profile view of NFET and particle strike. When an energetic particle strikes the silicon substrate, the electric field between the drain and body of the transistor separates the positive and negative charge carriers, preventing recombination; next, the charge collected by the junction results in a transient current in the struck transistor from the substrate to the drain node.

**(b)** Layout view: yellow region indicates particle strike

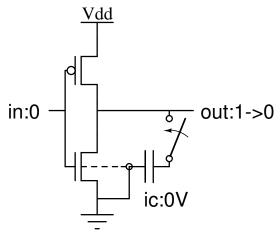

(c) Circuit diagram showing model of particle strike: switched capacitor between transistor drain and body with initial condition of 0 V potential.

Figure 2.4: Energetic particle strike causing current to flow across nominally off NFET until charge dissipates.

#### 2.2.3 Parametric variability

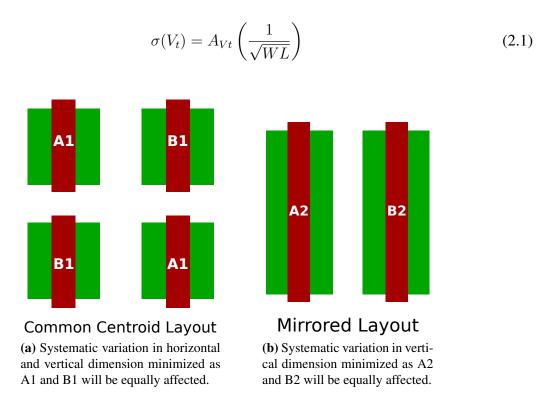

One major contributing cause of both hard and soft errors in memory is the difference in parameters (such as threshold voltage  $V_t$ ) of two identically designed transistors. The root causes of these parametric variations include gate work function (GWF) or oxide thickness variation, line-edge roughness (LER), and random dopant fluctuation (RDF) [16], which are exacerbated as transistor area decreases [57, 58]. Specifically,  $V_t$  variation due to RDF in the channel has been empirically shown to be inversely proportional to the square root of the channel area in the well-known Pelgrom model [58], reproduced in Equation 2.1. Note that this form of the Pelgrom model assumes two identically-drawn transistors in close proximity; devices farther from each other will suffer further mismatch due to global phenomena. In this equation,  $\sigma(V_t)$  represents standard deviation of the device's threshold voltage,  $A_{Vt}$  represents the area proportionality constant specific to the process technology, and W and L refer to the device's width and length.

**Figure 2.5:** Careful layout including mirrored or common centroid configurations can minimize systematic variation, and is commonly employed in analog cells such as the sense amplifier.

This difference in parameters can cause the difference in latency between the worst and best

cell to increase, and cause matching between devices in the cell to suffer and thus impact memory yield, reliability, and performance, since all these characteristics of a memory depend on its worst cell (after redundancy replacement). Device matching depends also on relative location; systematic variability sources may cause a gradient of a particular parameter across the die or wafer leading one side of a nominally matched pair of transistors to be consistently higher or lower in the parameter than the other. Careful layout including mirrored or common centroid configurations (see Figure 2.5) can minimize this systematic variation, and is commonly employed in analog cells such as the sense amplifier.

Additionally, researchers have proposed techniques for better matching of sensitive matched-pair transistors in analog applications through post-silicon statistical element selection rather than simple up-scaling of device sizing [4, 5, 31]. While incurring overheads due to the test-ing/configurability and non-volatile storage requirements, this improves reliability and yield in segments of the design which are highly sensitive to parametric variability.

We will describe the effects of parametric variability further in the next section, explaining how errors manifest in SRAM.

#### 2.3 Error manifestations and cell failure types

Given that the aforementioned error mechanisms afflict embedded memory, there are a number of ways in which memory can fail. An understanding of these error manifestations is prerequisite to preventing, detecting, or correcting them. As before, we separate our discussion into two areas: the cell array and peripheral circuitry.

#### 2.3.1 Cell array

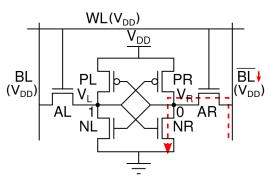

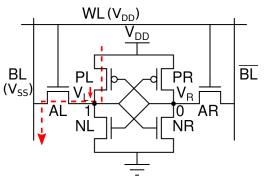

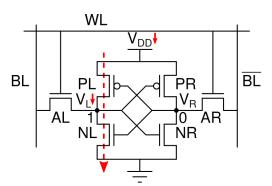

There are four primary failure types associated with the cell and its local periphery: read disturb failure, write failure, access failure, and retention (hold) failure [36, 37, 52, 76] (Figure 2.6).

In general, the bitline capacitance is much greater than the cell's internal storage node ca-

(a) Read disturb failure: Cell upsets when  ${\cal V}_L$  drops to  ${\cal V}_{SS}.$

(c) Read latency failure: Cell fails to read when  $\overline{BL}$  drops too slowly

(b) Write failure: Cell fails to upset when  $V_L$  drops too slowly

(d) Hold failure: Cell loses its value when  $V_{DD}$  drops too low and/or noise occurs at cell storage nodes

Figure 2.6: 6T cell failure types. Mismatched transistors and/or another fault within a cell can cause failure in cell operation (initialized as  $V_L = V_{DD}$ ,  $V_R = V_{SS}$ ).

pacitance, so when the wordline turns on the access transistor and the current flows from the bitline through the pulldown transistor, the internal storage node holding a 0 bumps up through voltage division over the two transistors. A read disturb failure may occur if this voltage rises far enough to turn on the opposite side's pulldown transistor (see Figure 2.6a). In designs which employ column multiplexing, a read disturb failure can occur during a write cycle, as there are cells activated by the wordline which are not intended to be written. These cells are generally referred to as "half-selected cells", as they are selected by the same wordline as the word activated for a write, but their bitlines remain charged or are left to float, rather than being driven for a write as those of the correctly column multiplexed bitlines. While there does not yet appear to be a consensus on terminology for this event in the literature, in this thesis we will describe this as a "half-select disturb failure". It has also been referred to in the literature as a partial write disturbance (PWD).

A write failure occurs when the cell retains its value instead of the expected behavior of being overwritten by a wordline pulse with bitlines split (see Figure 2.6b). Prior to the wordline assertion, the storage nodes are held at their values by the cross-coupled inverters. Normally, the large capacitance ratio between the bitline capacitance and the internal storage node capacitance and the low resistance of the activated access transistor is sufficient to overcome the drain current of pullup device PL and pull down the internal storage node  $V_L$ . However, if mismatch causes the access device AL to have a higher resistance than average or the pullup device PL to have a higher drain current than average, the node  $V_L$  may not be pulled below the trip point of PR/NR before the wordline is de-asserted and thus the cell's value will not be overwritten.

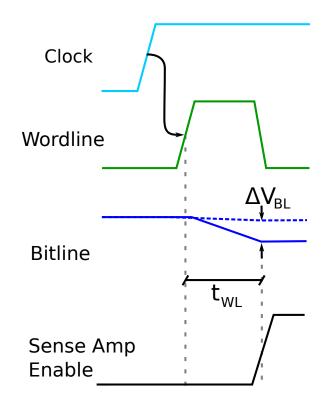

A read latency failure, also known as an access failure, occurs when the cell's read current is insufficient to meet the design's timing requirements (read latency) (see Figures 2.7 & 2.6c). Within the cell which suffers from read latency failure, this may occur due to the access or pulldown NFETs having lower drain current than average due to a number of causes (see Section 2.2.1). But the failure cannot always be diagnosed as being caused solely due to variation within the cell; at the level of a single column, the leakage of other cells on the bitline may

reduce the bitline differential due to the access NFETs having higher leakage current than average. Finally, the sense amplifier measuring the bitline differential of the column may suffer from mismatch in its nominally symmetrical structure causing input-referred offset.

In an equation, the requirement is shown in Equation 2.2, where N is the number of cells in a column,  $T_{WL\to SAE}$  is the time between wordline assertion and sense amplifier enable assertion (the time the 6T cell has to produce a voltage differential on the bitlines), and  $C_{BL}$  is the bitline capacitance.

$$|V_{SAoffset}| < \frac{(ION - (N-1) * IOFF) * T_{WL \to SAE}}{C_{BL}}$$

(2.2)

Figure 2.7: Depiction of read latency and critical  $t_{WL \to SAE}$  delay. If  $\Delta V_{BL} < V_{offset}$  at the time of SAE, the value on the bitlines is incorrectly sensed and a read latency failure will occur.

A hold failure, also known as a data retention failure, occurs when a cell loses its stored value after a period of time in which it is not accessed (see Figure 2.6d). It is often precipitated by a reduced cell supply voltage or noise on the internal storage nodes.

To quantify the manufacture-time yield of a memory design or the reliability of a cell during

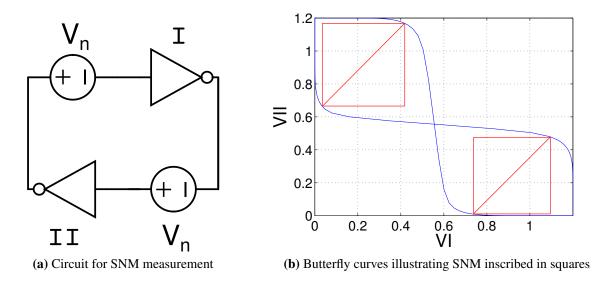

operation, we can measure cell metrics through simulation. Each metric indicates the magnitude of event or disturbance from nominal behavior which would have to occur at a certain point in the cell (or local to it) which would induce the failure type. For example, one commonly cited cell metric is the static noise margin (SNM), which quantifies cell stability and can be determined graphically by plotting the voltage transfer characteristics of the two cross-coupled inverters and measuring the sides of the largest squares inscribed between them [69]. The smaller of the two maximum squares' sides represents the cell's SNM. This plot is commonly known as the butterfly curve (see Figure 2.8). The read static noise margin (RSNM) and hold static noise margin (HSNM) describe versions of the SNM measured with the cell's access transistors turned on and off, respectively [52].

Figure 2.8: Static noise margin measurements [69]

The write margin (WM) can be determined in two ways. First, by setting both bitlines opposite the values stored at the cell's storage nodes (in Figure 2.6,  $BL = V_{DD}$ ,  $\overline{BL} = V_{SS}$ ) and sweeping the wordline from  $V_{SS}$  to  $V_{DD}$  to find the voltage at which the cell upsets, and subtracting this voltage from  $V_{DD}$  (as a more writeable cell should have a higher margin) [21, 72]. Second, by initializing the wordline and both bitlines to  $V_{DD}$  and sweeping the bitline on the side of the storage node initialized to  $V_{DD}$  to  $V_{SS}$  to find the voltage at which the cell upsets [23, 84].

This second measurement is also referred to as the write-trip point. Dynamic analysis of SRAM cells has found that the former static method of determining write margin (by sweeping the wordline from  $V_{SS}$  to  $V_{DD}$ ) correlates best with the dynamic write time metric [74].

The metrics of RSNM, HSNM, and WM can be classified as functional noise margins; if any are below 0 due to manufacture-time variation, or some run-time disturbance exceeds the margin, the cell will fail to function due to read disturb failure, hold failure, or write failure. On the other hand, performance metrics of the cell include read current and leakage current observed at the bitline when the wordline is asserted or de-asserted. These are also significant to reliability, since one cell's poor read current can cause read latency failure, while an array's large leakage current may cause supply droop or exceed power requirements for the design. Measuring cell current is an indirect way of measuring the read latency independent of cell array choices such as bitline capacitance, which depends on column height and sense amplifier choice among other options. These measurements, specifically the ratio of read current to leakage current or more directly the read latency if the cell array choices are known, can generate a figure of merit which defines the risk of an access failure.

Unlike functional metrics, performance metrics cannot determine a cell failure independent of other array decisions and specifications. In order to conclude that a cell's read current is below the passing threshold and would suffer an access failure, a threshold must be established, and sometimes this threshold can be adjusted at manufacture-time using product binning or after manufacture-time using configurable self-timing [4]. But if a cell suffers a read disturb failure (which upsets the stored value of the cell), this happens regardless of conventional array design decisions.

The average value of each metric across process and mismatch variations can be determined statistically for a given cell design and technology via Monte Carlo (MC) analysis. More importantly, the cumulative distribution function (CDF) of the metric can also be determined, allowing designers to give an expected yield figure for a memory of a given size, provided that the model files are accurate. MC analysis can estimate mean and standard deviation from a sample within

a confidence interval given a certain number of samples. The 99.7% ( $3\sigma$ ) confidence interval for a sample drawn from a normally-distributed population is defined by Inequality 2.3, where  $\bar{x}, \sigma, N, \mu$  are defined as the sample mean, sample standard deviation, sample size and population mean, respectively [15, 65].

$$\bar{x} - 3\frac{\sigma}{\sqrt{N}} \le \mu \le \bar{x} + 3\frac{\sigma}{\sqrt{N}}$$

(2.3)

#### 2.3.2 Peripheral circuitry

While most study has focused on the SRAM cell array, for high-reliability products, it is important to examine the effects of failures on the peripheral logic as well. Unlike in the cell array, where a failure in a storage element can cause immediate corruption of data, SEUs in the SRAM peripheral logic aren't generally able to cause an error in isolation. Rather, the effects of the SEU depend on the location as well as state of the memory at the time of the upset.

Failures occurring in certain segments of the peripheral logic manifest in ways unlike those which occur in the cell array. As classified in Section 2.1.2, the data path drives the signals from the bitlines to the input/output data ports. A particle strike or other failure mode affecting a portion of the data path would result in a disturbance to one or more bits of a word as opposed to the entire word (see Figure 2.9a). In such a situation, the resulting failure effects resemble those of a failure in the cell array. As such, these can be handled by the same techniques which handle failures in the array itself, such as ECC. Of course, not all failures are preventable or even detectable. The address path drives the signals from the input address to the wordlines/column select. A particle strike or other failure mode affecting a portion of the address path may manifest in a distinct way which is more challenging to detect. Since the final outputs of the address decoder are wordline and column select signals, the failure manifestations generally involve suppression of the intended wordline/column select signal and/or activation of an unintended wordline/column select signal. Since these failure manifestations involve the entire word rather than just a part of it, and could conceivably result in an undetectable failure (see Figure 2.9b).

(a) Data path failure: one or more columns may have their data corrupted, similar to a failure somewhere in the cell array. These types of failures have conventionally been handled using interleaving and ECC.

**(b)** Address path failure: another wordline whose data is opposite that of the intended wordline is asserted in error, potentially causing the entire word to be read incorrectly, but since the data from the aggressor wordline is a valid codeword, ECC will not detect that an error has occurred.

**Figure 2.9:** Failures occurring in the data path may be detectable or correctable by ECC; failures occurring in the address path are commonly neither detectable nor correctable by ECC and so must be dealt with through other means.

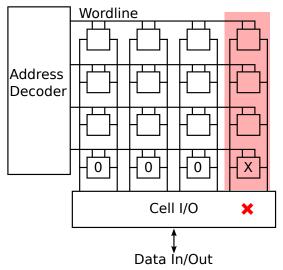

Figure 2.10: Address decoder failure types.

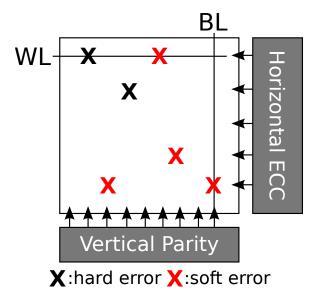

The address decoder can fail in one of three ways:

- 1. 0WL failure (see Figure 2.10b): The desired wordline is not asserted, and no other wordline is asserted. Essentially the assertion of the wordline is suppressed.

- 2. Wrong-row failure: The desired wordline is not asserted, but one or more other wordlines is asserted. This type of failure has two sub-types depending on the proximity of the desired wordline to the improperly asserted wordline. If the two wordlines are in the same block, we term this a FWL (see Figure 2.10d). Otherwise, we term this a wrong-block wordline (WBWL). Sometimes we also refer to a WBWL failure as a "1WL" failure when we're examining the failures within a single block. The "1WL" terminology indicates a failure where the expected behavior was 0 wordlines in the block asserted but the actual behavior was 1 wordline in the block asserted.

- 3. 2WL failure (see Figure 2.10c): The desired wordline is asserted, but one or more other wordlines is asserted as well, which may cause contention on a read and data corruption on a write.

For simplicity, the terms "row" and "wordline" are used to refer to the address decode path's output; it should also be noted that the column select suffers from the same failure types.

Information on fault modes potentially resulting from these SEUs and their relative likelihood could guide designers in handling these faults using techniques which are most effective given their overhead. We present a study of particle strike locality in an industrial address decoder in Section 5.1. Additionally, we discuss conventional techniques for detecting peripheral logic failure in Section 3.6 and propose a new technique with lower area overhead for large cache designs in Section 5.2.

### 2.4 Summary

In this chapter we've discussed the basic structures of SRAM design: an overview of the 6T and 8T cell options, the array structure, and the peripheral circuitry. Failure causes and symp-

toms are examined, with a particular emphasis on failures which may occur at runtime, since BIST/BISR is generally limited in scope compared to testing and repair which can be performed at manufacture-time. The issues of parametric variability and functional noise margin are problems facing designers which cause difficulty maintaining strong guarantees of reliability. Next, we discuss conventional reliability techniques in Chapter 3 and novel reliability techniques in Chapters 4 and 5.

# **Chapter 3**

# Conventional reliability techniques

There exist a multitude of published memory design techniques which are employed to improve reliability/resiliency; of these, a subset have been adopted into wide commercial use. We discuss six of the most common solutions; specific implementations of these solutions differ in their overhead and efficacy so our discussion here is qualitative.

For the purposes of this thesis, what we consider to be a "reliability technique" is any circuit-level design choice which reduces the likelihood of a failure condition (or improves reliability) at the cost of some quantifiable increase in overhead, whether that be latency, area, or power. The limitation of circuit-level choices ensures that these techniques can be employed by the designer freely even after the technology decisions have been made relating to process steps which may improve reliability such as the use of silicon on insulator (SOI) to limit the effects of energetic particle strikes. These process-level choices are beyond the scope of this thesis.

# 3.1 Read/write bias assist techniques

Bias assist techniques modify one or more of the SRAM cell's ports ( $V_{DD}$ ,  $V_{SS}$ ,  $V_{BL}$ ,  $V_{WL}$ ,  $V_{body}$ ) in order to reduce overall cell failure probability or increase cell read or write margins. Overcoming the inherent tradeoff between read stability/writeability generally requires designers to carefully choose their assist ports in combination with cell array architecture, because most

modifications that improve read stability hurt writeability and vice versa. This is not an issue in single-ported cell arrays which have no column muxing/interleaving since in each cycle, only a read or a write occurs in a given word, and thus the read bias assist can be limited to cells active during a read, and similarly for the write bias assist.

To improve read latency and reduce failure rate, many designers have chosen to implement a form of read assist circuitry which boosts cell supply voltage or under-drives the wordline to limit cell upset during read [6, 60, 84].

Conversely, to improve write performance and reduce failure rate, many designers have chosen to implement a form of write assist circuitry which collapses the cell supply voltage, boosts the wordline voltage, or drives the low bitline voltage below ground, to ensure the cell is properly written [6, 79]. Often these two assist techniques go hand-in-hand; the same supply node is chosen to be adjusted in opposite directions for a read or a write, or else one node is adjusted for read assist while the other is adjusted adversely for write assist [32].

One potential limiting factor with using negative bitline (NBL) as a write assist technique is that of a long-term reduction in reliability due to larger than VDD bias across the gate oxide, leading to potential BTI and TDDB issues. However, recent work has asserted that this is not a concern based on results of burn-in testing on VDDmin shift and standby leakage increase [17]. The only other caveat is a reported high energy overhead [85].

Body biasing has also been employed to reduce the impact of process variation, but it is generally used as a process-calibration method to recenter a design whose transistors' threshold voltage is skewed far from the modeled value.

# **3.2** Cell choice (6T/8T)

While the 6T SRAM cell (Figure 3.1a) has become the de facto standard in traditional designs (not including sub-threshold memory designs), in recent years the 8T SRAM cell (Figure 3.1b) has been commonly used to reduce failures and thus increase reliability, as well as separating the read and write paths in the cell so that optimization of read and write are no longer mutually

(a) 6T cell: High density and differential read bitlines, but inherent read stability/writeability tradeoff in design.

**(b)** 8T cell: reduced vulnerability to read disturb.

Figure 3.1: SRAM cells

exclusive [14, 28]. The read stability failure mode (Figure 2.6a) is completely removed (rendered identical to the hold stability failure mode) since the read bitline (RBL) no longer interacts with the cell's storage nodes. However, due to the risk of half-selected cells being upset on a write, column muxing might not be desirable for designers when using 8T cells. There are situations in which designers will still choose to use column multiplexing with an 8T cell, however, which restores the risk of a read disturb on a write. In systems where the 8T cell's multi-port functionality is used to support a read and write in the same cycle, column muxing might be useful to the designer, particularly if the application does not require high density. Reducing the device sizing in the 8T cell to attain high density exacerbates the cell margins. The use of HCI techniques can make column muxing with 8T cells more desirable [26], but such a scheme has (to the best of our knowledge) yet to find commercial viability, perhaps due to the extra required manufacture-time testing burden.

# 3.3 Cell sizing

One simple method of diminishing error likelihood from several different sources is to increase cell size by increasing transistor width, particularly access and pulldown transistors [33]; this increases area and power overhead but may improve latency. As discussed in Section 2.2.3,

since the standard deviation of the threshold voltage and thus performance of each transistor in the cell is inversely related to its area [58], matching should improve as transistor size and thus cell size increases. This reduces failures due to variability, which can be a major contributor to failure even if it is not able to induce a failure by itself. However, increasing cell sizing limits density and is thus an undesirable solution for on-die last-level caches where high density is required.

# 3.4 Error control coding