# Hardware-Entangled Inherently Secure Field Programmable Gate Arrays

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

Electrical and Computer Engineering

BURAK ERBAĞCI

B.S., ELECTRONICS ENGINEERING, SABANCI UNIVERSITY

M.S., ELECTRICAL AND ELECTRONICS ENGINEERING, EPFL

M.S., Electrical and Computer Engineering, Carnegie Mellon University

CARNEGIE MELLON UNIVERSITY PITTSBURGH, PA

DECEMBER, 2018

© 2018 Burak Erbağcı

All Rights Reserved

#### Abstract

Field programmable gate arrays (FPGAs) are one of the most attractive programmable platforms because they combine the flexibility of software programmed CPUs and the performance and efficiency of custom ASICs. FPGAs enable rapid prototyping and development of complex ASICs and facilitate deployment of embedded systems with performance nearing ASICs. Consequently, FPGAs are now the workhorses behind a broad variety of applications including aerospace, supercomputing, high-speed signal processing, and cryptography. Additionally, FPGAs are a highly attractive implementation platform for secure systems due their lack of application design information at manufacture-time, which mitigates the risk if the supply chain is compromised. Cryptographic applications and security protocols can be efficiently implemented on FPGAs and they can easily be modified in the field unlike their ASIC counterparts.

The configuration bitstream is a persistent source of security vulnerability in FPGA designs. The possible compromise of configuration data by the attacker poses significant threats for deployed systems in the field. These threats include cloning the FPGA configuration for use in counterfeit/unauthorized systems, modifying the FPGA configuration to increase side-channel emissions, and adding malicious Trojan hardware into the compromised design. To ensure design protection, FPGA manufacturers have implemented bitstream encryption and authentication, flash FPGAs, and active defense mechanisms for FPGA test and support circuits. However, these security measures can be circumvented in a number of ways, which includes direct probing the key storage, side-channel attacks on the bitstream decryption logic, and attacks on the test and verification support circuits. Furthermore, as is common with hardware implementations, cryptographic systems implemented on FPGAs leak in-advertent side-channel information (i.e., power, timing, electromagnetic emissions) that can be exploited by an attacker to bypass the security of the algorithms. One

highly effective and easy-to-mount side-channel attack is power analysis, which exploits the data-dependent power consumption in the hardware. Hiding and masking countermeasures seek to achieve resistance against power side-channel attacks at the expense of significant timing, area, and energy overheads; however, these techniques are vulnerable against a number of successful side-channel attacks.

In this thesis, we present a secure hardware-entangled FPGA design in order to address these FPGA security concerns. The proposed FPGA design never stores the configuration data in the clear, even at the lowest level of the hardware. We deeply hardware-entangle both the reconfigurable logic and interconnect by one-time pad encrypting the bitstream using a secret die-specific response. Physical unclonable functions (PUFs) are used in the implementation as a mechanism to generate this secret response. By leveraging our recent work in efficient PUF design with both low VLSI overheads (i.e., area, power, delay) and strong security metrics (i.e., randomness, uniqueness, reliability), we tightly integrate a PUF bit with every configuration bit. This has significant security benefits that include high resistance to probing attacks and unique per-die configuration bitstreams. Also, PUFs can be fired on-the-fly during FPGA operation for enhanced security against probing attacks. In addition to bitstream protection, the proposed FPGA fabric has resistance to power analysis attacks embedded within the reconfigurable fabric that enables side-channel secure operation. The fabric uses post-charged dynamic logic with self-timed discharge operation to ensure secure operation of user designs. Hardware-entangled secure FPGAs are a promising alternative to layering countermeasures on top of insecure conventional-off-the-shelf (COTS) FPGAs.

#### Acknowledgments

During my long years at CMU I had the opportunity to work and collaborate with many wonderful people and without their support and help this journey would not have been possible. I would like to express my deepest gratitude to my advisor and committee chair Prof. Ken Mai for his guidance and support from the very first moment I started my CMU journey. Not only his vast technical knowledge, but also his approachability, insightfulness, and enthusiasm make him a unique mentor and a role model who I have looked up to since I met him. My time as a graduate student at CMU has been an amazing experience and I owe it to his unique ability to inspire his students with a sense of hope and purpose that kept me motivated. When I look back, I feel accomplished and confident about my technical skills and I am extremely grateful for everything he taught me during my time as a graduate student.

I am also very grateful to my committee members Prof. James Hoe, Prof. Yusuf Leblebici, Prof. Patrick Schaumont and Dr. Mudit Bhargava for reviewing my proposal and dissertation and providing their valuable feedback. Their time and flexibility made this thesis possible. I also acknowledge the funding from DARPA (Contract #FA8650-18-1-7814) that supported this work.

I would like to specially thank to Prof. Yusuf Leblebici. I consider myself extremely fortunate to have known him since my undergraduate years. His mentorship and support have always inspired me to learn more and make me a better researcher.

Special thanks to Dr. Mudit Bhargava for his technical insight and advice that proved invaluable to my research and understanding. I was very fortunate to work with him in our research group. He is also an exceptional friend and I learned a lot from him both professionally and personally.

I have been very fortunate to learn a lot from many amazing professors at CMU. I would like to specially thank to Prof. Larry Pileggi and Prof. Andrzej Strojwas for many interesting lectures and their support. The staff at CMU are some of the kindest and most professional people I have ever met. I am profoundly appreciative of the efforts of Judy Bandola, Nathan Snizaski and all of the administrative staff in the ECE department for handling so many concerns and making life run more smoothly for all graduate students.

I had a great pleasure working with many wonderful and smart people in our research group. I'm very grateful for their input and company that improved the quality of my work and my life outside of work. Thank you so much, Dr. Mudit Bhargava, Dr. Mark McCartney, Dr. Yu Cai, Dr. Cagla Cakir, Craig Teegarden, Nail Etkin Can Akkaya, Raymond Carley, Onur Kibar, Prashant Mohan, Rachel Dondero.

I would like to specially thank to Nail Etkin Can Akkaya for his selfless efforts in the custom design of my *flip-flops*. He helped me countless times and all the pieces he designed in all my testchips worked well (thank God). He has also been an exceptional friend who I have relied on so many times. He was generous enough to have me as a guest at his place during the last couple of months of my time in Pittsburgh. I am extremely grateful to him for everyhing he has done for me.

During my time at CMU, I have been lucky enough to have a great circle of friends. Each and every one of them made my CMU journey priceless. Yunus Emre Kesim, Dr. Engin Burak Anil, Omer Ozdemir, Ece Isenbike Ozalp, Dr. Batuhan Arisoy, Dr. Abhishek Sharma, Dr. Mohammed Omar Darwish, Sungho Kim, Dr. Mazen Soliman, Xiaoliang Li, Dr. Yigit Isbiliroglu, Meric Isgenc, Dr. Emrullah Korkmaz, Dr. Bekir Bediz, Dr. Recep Onler, among others too numerous to list here. Thank you all for your encouragement; I relished our time together and look forward to continued friendship and correspondence.

I would like to specially thank to Yunus Emre Kesim. He is a true friend who has inspired and supported me in numerous ways both professionally and personally. I had many challenges along the way and he helped me selflessly countless times. I am extremely grateful to him for everything he taught me. During my time in Pittsburgh, I've had the fortune of crossing paths with a number of people who enriched my life: Busra Tugce Susam, Peren & Mert Hasanreisoglu, Dr. Tekin Kose, Yassin Khalifa, Firat Alemdar, Mustafa Kemal Ozkan, Cengiz Erdogan, Cody Martin. Thank you all for your friendship. I truly enjoyed our time together and look forward to continued friendship.

Special thanks to Busra Tugce Susam for being a caring and supportive friend. She also happens to be an excellent cook who fed me countless times when I was too busy and forgot to eat. I enjoyed her company and friendship so very much.

I would like to specially thank to Peren and Mert. I consider myself blessed to have known them. They both are incredible friends who have always supported me. I cannot thank them enough.

I would like to specially thank to Erdem family: Oznur, Bilge, Selcuk, and Ceyhun Erdem. They have always been my second family here in Pittsburgh and supported me the entire time. I am very grateful and very lucky to have them in my life.

I would like to specially thank to Dr. Ercument Cicek. Although our paths crossed in undergradute years, we became close friends following his move to Pittsburgh. Then he moved back to Turkey but that did not prevent us from being very good friends. Despite the time difference and thousands of miles between us, he has always been there for me both professionally and personally. I do not think I can ever thank him enough for everything he has done for me. He is a true friend and an exceptional person.

I would like to express my gratitude to Dr. Tugce Yazicigil and Dr. Eymen Kurdoglu for their support, friendship, and inspiration. I would also like to thank my close friends: Dr. Gozen Koklu, Dr. Ali Galip Bayrak, Pinar Kaynak, Emrah & Dr. Damla Tas, Dr. Anil Yuce, H. Can Yener, T. Zafer Ozcan. Thousands of miles between us did not prevent them from supporting me. I am extremely grateful. I would like to express my deepest gratitude to my girlfriend, Dr. Kelly Dickson, for her patience and endless support. She has been the most caring and supportive girlfriend I could ever ask for. She kept me going and motivated especially when things were not going great with the testchip. I am extremely grateful to her for everthing she has done for me: sitting in the lab with me, helping with soldering, listening, motivating me, and unconditionally supporting me. I sincerely do not think I can ever thank her enough for all these.

Last and foremost, I would like to express my deepest gratitude and my endless love to my family. My parents, Derya and Abdulkadir, and my brother, Cagri, provided me with everything I needed to get to where I am today and encouraged me to chase my dreams. I owe everything I accomplished to them. Their incredible support, unconditional love, and interest in my academic career made all these possible. I cannot thank them enough for always being there for me. I wish my grandmother was still alive to see this moment. I humbly dedicate my work to my beloved family and my grandparents.

# Contents

| 1 | Intro | oductio | n                                                | 2  |

|---|-------|---------|--------------------------------------------------|----|

|   | 1.1   | Motiva  | ation                                            | 2  |

|   | 1.2   | Secure  | ed vs. Secure FPGA                               | 3  |

|   | 1.3   | Disser  | tation Organization                              | 5  |

| 2 | Bacl  | kground | d                                                | 6  |

|   | 2.1   | The In  | ternals of an FPGA                               | 6  |

|   |       | 2.1.1   | FPGA Configuration Storage                       | 8  |

|   |       | 2.1.2   | Reconfigurable Logic                             | 8  |

|   |       | 2.1.3   | Reconfigurable Interconnect                      | 9  |

|   | 2.2   | Revers  | se-Engineering Attacks and Countermeasures       | 11 |

|   |       | 2.2.1   | Reverse-Engineering Attacks                      | 11 |

|   |       | 2.2.2   | Countermeasures                                  | 12 |

|   | 2.3   | Side-C  | Channel Analysis Attacks and Countermeasures     | 13 |

|   |       | 2.3.1   | Side-Channel Analysis Attacks                    | 13 |

|   |       | 2.3.2   | Countermeasures                                  | 14 |

|   | 2.4   | FPGA    | Security                                         | 16 |

|   |       | 2.4.1   | Design Protection against Reverse-Engineering    | 16 |

|   |       | 2.4.2   | Side-Channel Analysis Resistant Secure Operation | 18 |

|   | 2.5   | Summ    | ary                                              | 19 |

| 3 | Har         | dware-l  | Entanglement for FPGA Design Protection        | 20         |

|---|-------------|----------|------------------------------------------------|------------|

|   | 3.1         | Attack   | er Model                                       | 20         |

|   | 3.2         | Conce    | pt                                             | 21         |

|   | 3.3         | System   | n Design and Use                               | 23         |

|   | 3.4         | Impler   | nentation                                      | 25         |

|   |             | 3.4.1    | Physical Unclonable Functions                  | 25         |

|   |             | 3.4.2    | Hot-Carrier Injection                          | 26         |

|   |             | 3.4.3    | Improved HCI-SA PUF Design                     | 28         |

|   | 3.5         | Experi   | mental Methodology                             | 30         |

|   |             | 3.5.1    | FPGA Architecture                              | 30         |

|   |             | 3.5.2    | VTR and COFFE Tool Flow                        | 31         |

|   |             | 3.5.3    | Architectures                                  | 32         |

|   |             | 3.5.4    | Benchmark Applications                         | 33         |

|   | 3.6         | Experi   | mental Results                                 | 33         |

|   |             | 3.6.1    | Area Results                                   | 33         |

|   |             | 3.6.2    | Timing Results                                 | 34         |

|   |             | 3.6.3    | Power Results                                  | 35         |

|   |             | 3.6.4    | Overheads                                      | 35         |

|   | 3.7         | Securi   | ty Evaluation                                  | 36         |

|   |             | 3.7.1    | Security Metric                                | 36         |

|   |             | 3.7.2    | IC De-camouflaging Attacks                     | 37         |

|   |             | 3.7.3    | Physical Attacks                               | 38         |

|   |             | 3.7.4    | Tool Chain Security                            | 40         |

|   | 3.8         | Summ     | ary                                            | 42         |

| 4 | Pow         | or Sido. | Channel Attack Resistant FPGA Fabric           | 43         |

| 7 | <b>4</b> .1 |          | harged Dynamic Logic with Self-timed Discharge | <b>4</b> 3 |

|   | 7.1         | 4.1.1    | PCDL-STD Gate Operation                        |            |

|   |             | 7.1.1    |                                                | +J         |

|   |      | 4.1.2   | Chaining PCDL-STD Gates                               | 46  |

|---|------|---------|-------------------------------------------------------|-----|

|   |      | 4.1.3   | The Caveat: Avoiding Potential PCDL-STD Timing Issues | 48  |

|   | 4.2  | Secure  | FPGA Tile                                             | 49  |

|   |      | 4.2.1   | Logic Cluster                                         | 52  |

|   |      | 4.2.2   | Connection Block                                      | 60  |

|   |      | 4.2.3   | Switch Box                                            | 61  |

|   | 4.3  | Experi  | mental Results                                        | 65  |

|   |      | 4.3.1   | VLSI Overhead                                         | 65  |

|   |      | 4.3.2   | Power Side-Channel Analysis Evaluation                | 70  |

|   | 4.4  | Summa   | ary                                                   | 72  |

| 5 | Secu | ıre FPG | A Testchip                                            | 73  |

|   | 5.1  |         | hip Overview                                          | 73  |

|   | 5.2  |         | Configuration Circuitry                               | 76  |

|   | 5.3  |         | frastructure                                          | 78  |

|   |      | 5.3.1   | Input Test Structures                                 | 78  |

|   |      | 5.3.2   | Output Test Structures                                | 81  |

|   |      | 5.3.3   | Clocking                                              | 83  |

|   | 5.4  | Measu   | rement Results                                        | 83  |

|   |      | 5.4.1   | Benchmark Measurements                                | 84  |

|   |      | 5.4.2   | PUF Measurements                                      | 90  |

|   | 5.5  | Power   | Side-Channel Analysis Security Evaluation             | 96  |

|   |      | 5.5.1   | Attack Methodology                                    | 97  |

|   |      | 5.5.2   | Attack Equipment and Setup                            | 97  |

|   |      | 5.5.3   | Attack Results                                        | 99  |

|   | 5.6  | Summa   | ary                                                   | 103 |

|   |      |         |                                                       |     |

| Appendices                                      | 107 |

|-------------------------------------------------|-----|

| A DPA Attack Results For All Modes of Operation | 107 |

| Bibliography                                    | 113 |

# **List of Figures**

| 1.1 | FPGA hardware entanglement concept                                                   | 4  |

|-----|--------------------------------------------------------------------------------------|----|

| 2.1 | Architecture of a typical island-style FPGA                                          | 7  |

| 2.2 | A 2-input LUT configured as an AND gate                                              | 9  |

| 2.3 | FPGA interconnect architecture                                                       | 10 |

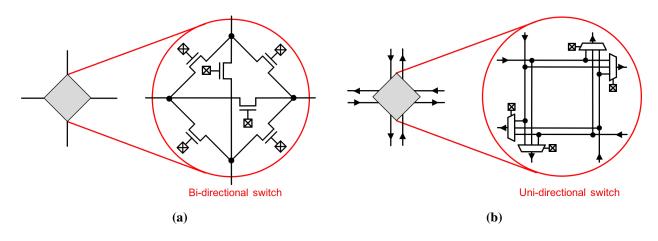

| 2.4 | Bi-directional vs. uni-directional switches                                          | 11 |

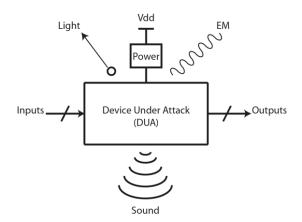

| 2.5 | Side-channel emissions from device under attack                                      | 13 |

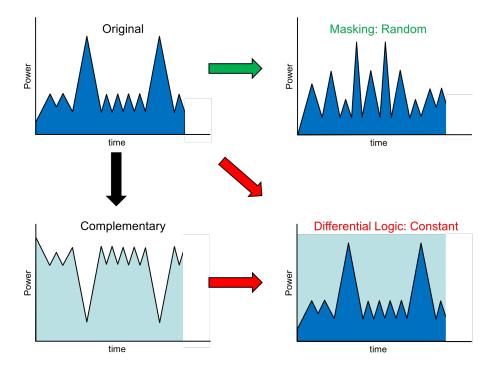

| 2.6 | Masked logic vs. differential logic to achive power side-channel analysis resistance | 15 |

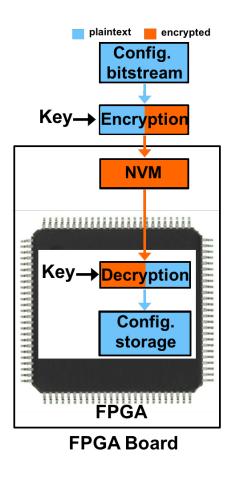

| 2.7 | Bitstream encryption scheme for protection against reverse-engineering attacks .     | 17 |

| 2.8 | Double Wave Dynamic Differential Logic (D-WDDL) route preserving design              |    |

|     | duplication                                                                          | 19 |

| 3.1 | Hardware-entanglement of a 3-input LUT block                                         | 22 |

| 3.2 | System design and use of hardware-entanglement scheme                                | 24 |

| 3.3 | Hot-carrier injection phenomenon                                                     | 27 |

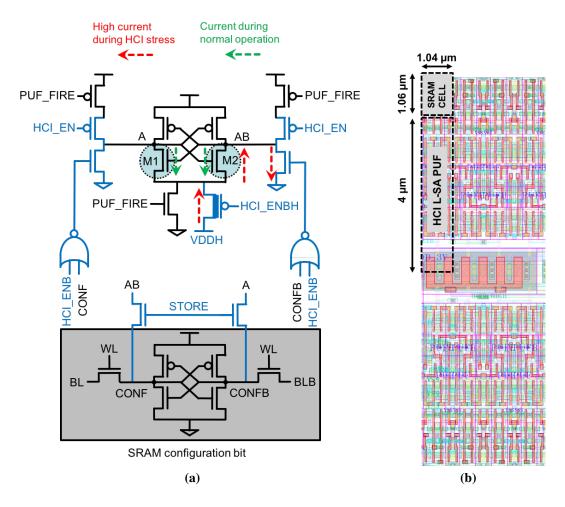

| 3.4 | Improved HCI SA PUF design                                                           | 29 |

| 3.5 | Island-style FPGA architecture                                                       | 32 |

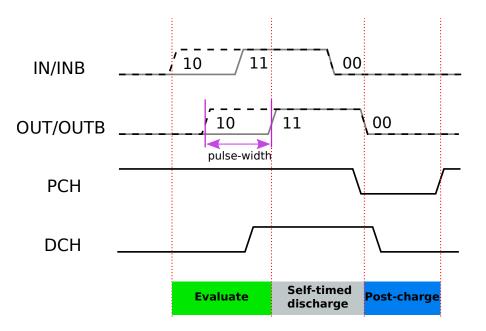

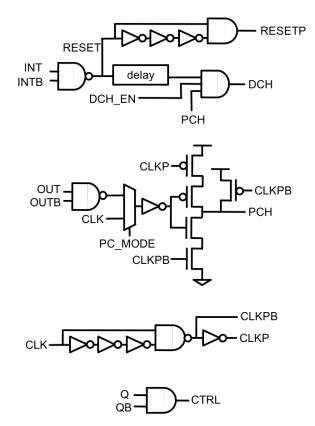

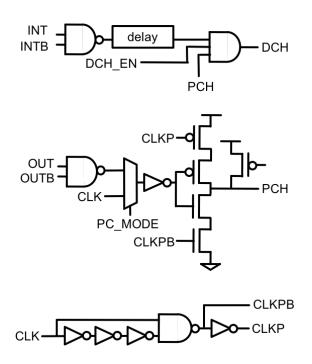

| 4.1 | PCDL-STD logic and control signals                                                   | 44 |

| 4.2 | A PCDL-STD 2:1 MUX and and the control logic                                         | 45 |

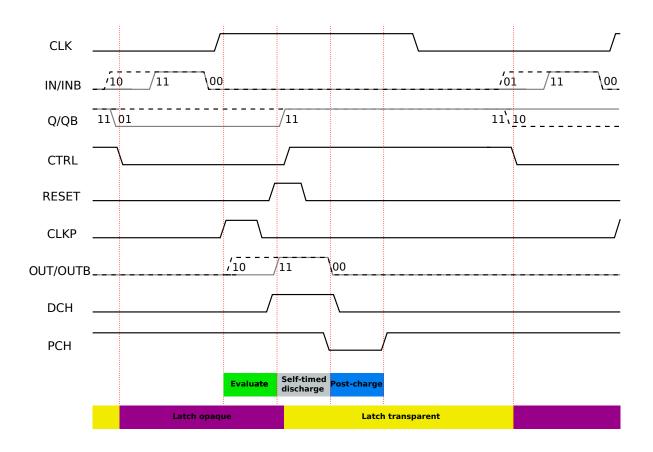

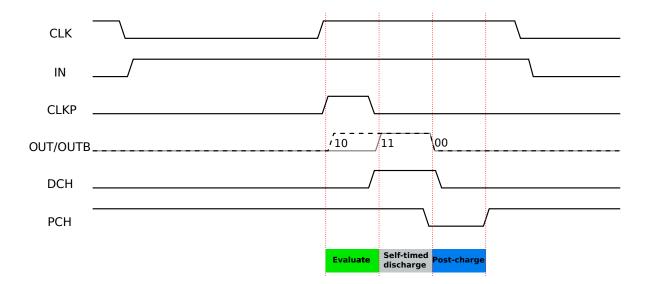

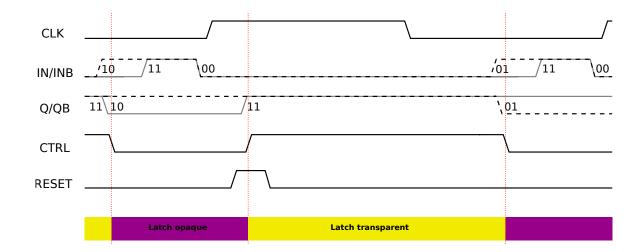

| 4.3 | Timing diagram of a PCDL-STD 2:1 MUX                                                 | 46 |

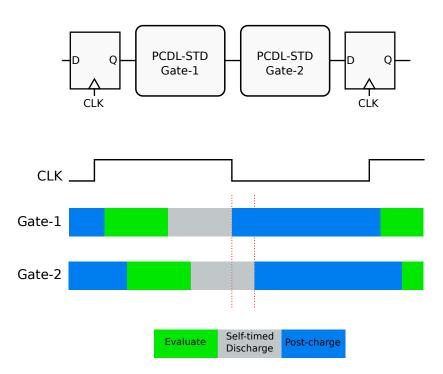

| 4.4 | Simplified timing diagram of a chain of two PCDL-STD gates                           | 47 |

| 4.5  | FPGA tile block diagram                                                       | 49 |

|------|-------------------------------------------------------------------------------|----|

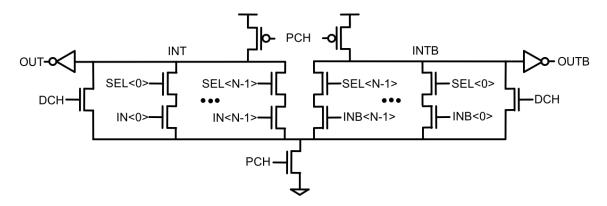

| 4.6  | Schematic of a PCDL-STD N:1 MUX                                               | 51 |

| 4.7  | PCDL-STD control logic with different operating modes                         | 51 |

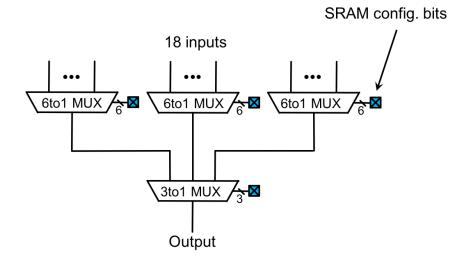

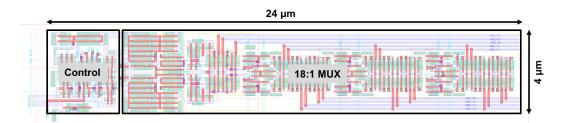

| 4.8  | Layout capture of BLE and LUT input crossbar multiplexers                     | 52 |

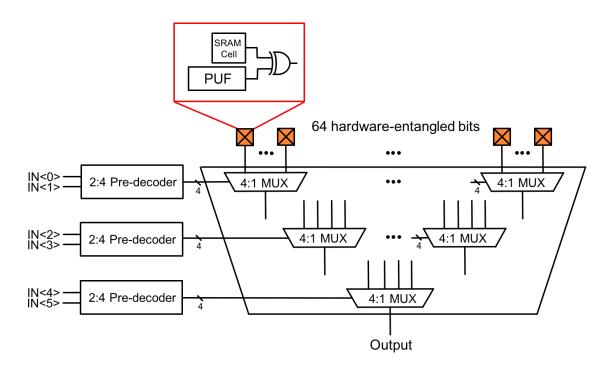

| 4.9  | Block diagram of 6-input LUT                                                  | 53 |

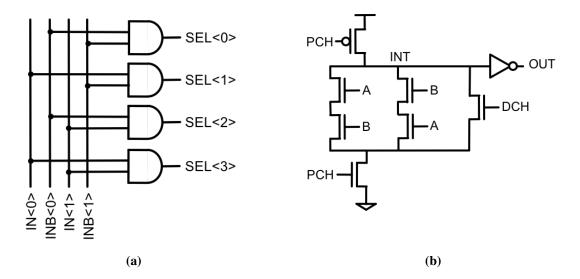

| 4.10 | 2:4 pre-decoder structure used to generate 4x one-hot encoded select signals  | 53 |

| 4.11 | Input crossbar MUX architecture                                               | 54 |

| 4.12 | PCDL-STD N:1 MUX with inherent latching capability                            | 55 |

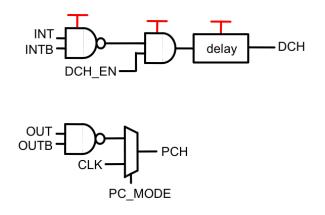

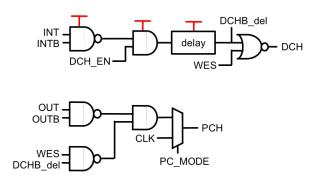

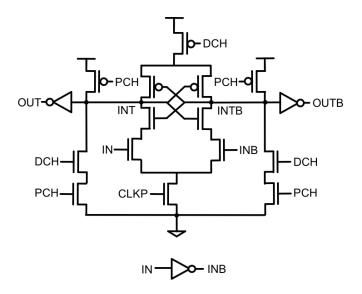

| 4.13 | PUF activation signal generation                                              | 56 |

| 4.14 | Secure PCDL-STD flip-flop schematic                                           | 56 |

| 4.15 | Secure PCDL-STD flip-flop control logic                                       | 57 |

| 4.16 | Timing diagram of a secure PCDL-STD flip-flop                                 | 59 |

| 4.17 | Connection block MUX architecture                                             | 60 |

| 4.18 | Layout capture of a CB 18:1 MUX                                               | 60 |

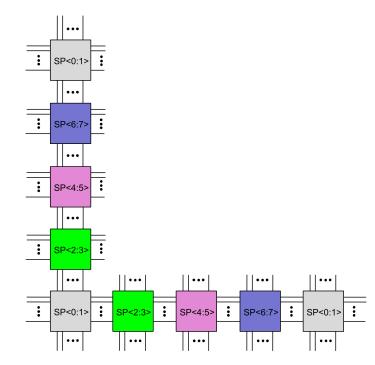

| 4.19 | Detailed view of a switch point in the programmable interconnect              | 62 |

| 4.20 | The order of different switch point patterns in the programmable interconnect | 63 |

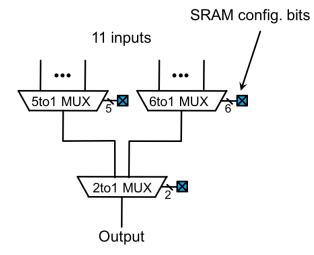

| 4.21 | The architecture of SB 11:1 MUX                                               | 63 |

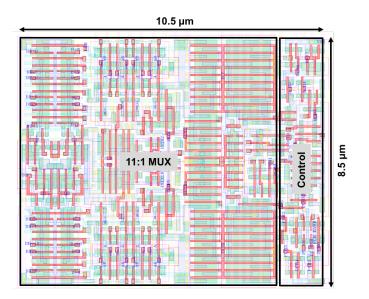

| 4.22 | Layout capture of a SB 11:1 MUX                                               | 64 |

| 4.23 | Modified control logic used in SB MUX                                         | 64 |

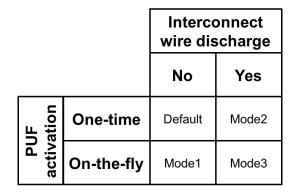

| 4.24 | Operating modes of secure FPGA                                                | 65 |

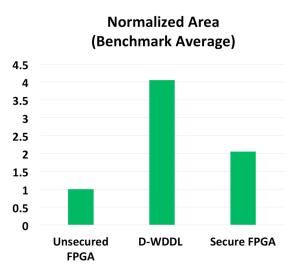

| 4.25 | Area comparison results for unsecured FPGA, D-WDDL and secure FPGA            | 66 |

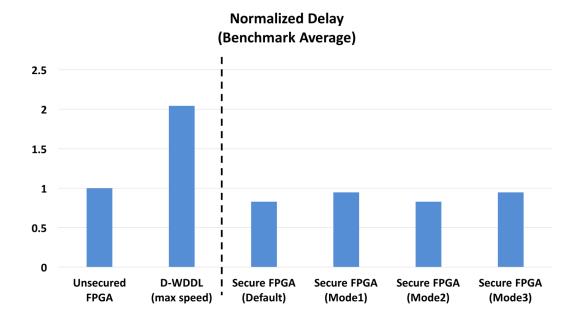

| 4.26 | Timing comparison results for unsecured FPGA, D-WDDL and secure FPGA $$ .     | 67 |

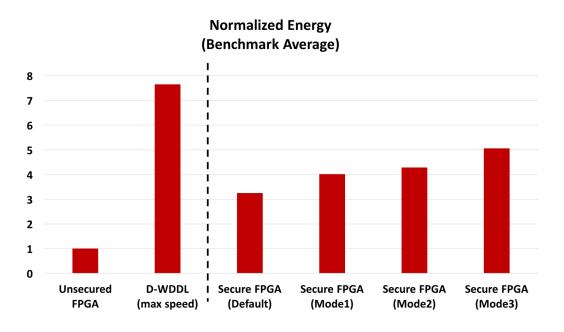

| 4.27 | Energy comparison results for unsecured FPGA, D-WDDL and secure FPGA          | 68 |

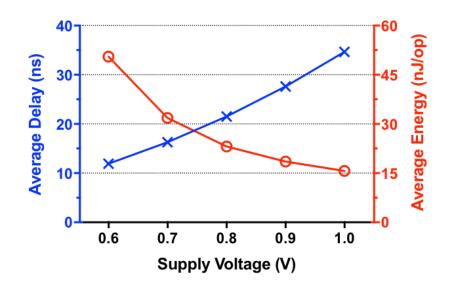

| 4.28 | Energy vs. delay across a supply voltage range of 0.6-1V                      | 69 |

| 4.29 | Energy-delay product across a supply voltage range of 0.6-1V                  | 69 |

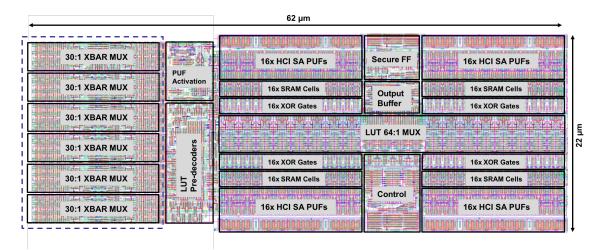

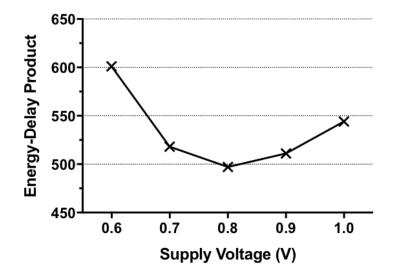

| 5.1  | Secure FPGA prototype testchip dieshot                                        | 74 |

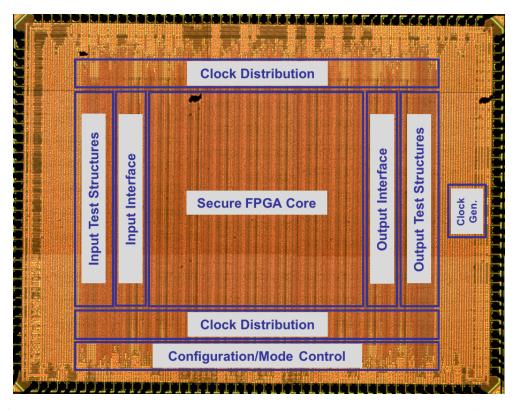

| 5.2  | Top level block diagram of the testchip                                       | 75 |

|      |                                                                               |    |

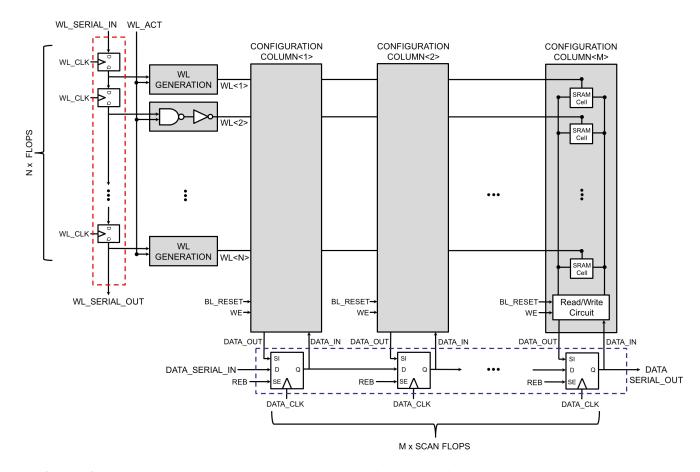

| 5.3  | Overall structure of FPGA programming circuitry                                 | 77  |

|------|---------------------------------------------------------------------------------|-----|

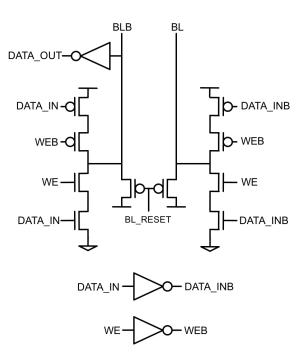

| 5.4  | The schematic of read/write circuit used in each configuration column           | 78  |

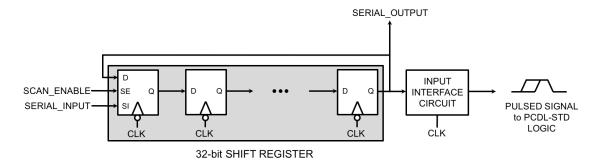

| 5.5  | Input test structures to test secure FPGA at speed                              | 79  |

| 5.6  | Input interface circuits between input registers and the secure FPGA            | 79  |

| 5.7  | Control logic of input interface circuits                                       | 80  |

| 5.8  | Timing diagram of input test structures                                         | 80  |

| 5.9  | Output test structures to test secure FPGA at speed                             | 81  |

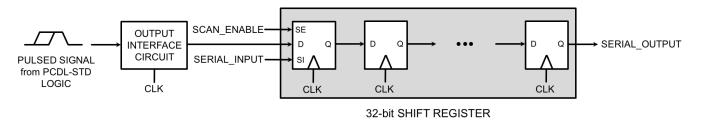

| 5.10 | Output interface circuits between the secure FPGA and output registers          | 82  |

| 5.11 | Timing diagram of output test structures                                        | 82  |

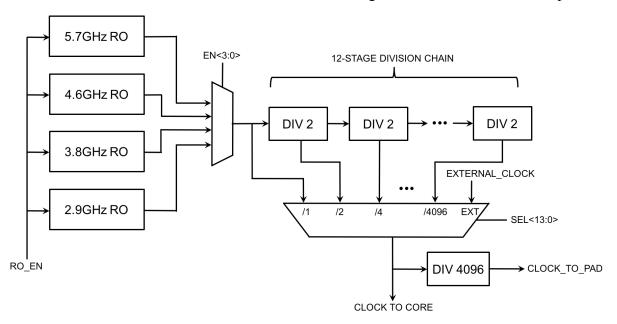

| 5.12 | Programmable on-chip ring-oscillator based clock generator                      | 83  |

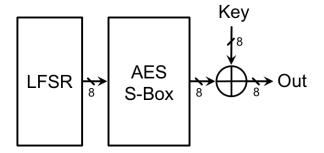

| 5.13 | Sample security primitive implemented on secure FPGA testchip                   | 84  |

| 5.14 | Operating modes of secure FPGA testchip                                         | 84  |

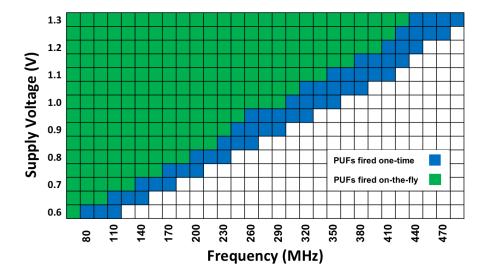

| 5.15 | Shmoo plot of the benchmark circuit implementation on the secure FPGA           | 85  |

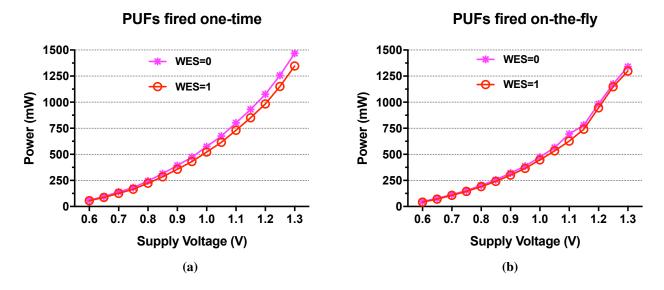

| 5.16 | Measured dynamic power consumption vs. supply voltage                           | 86  |

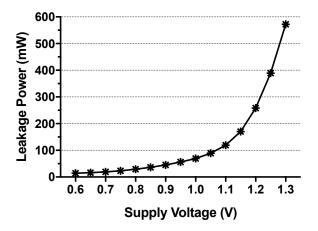

| 5.17 | Measured leakage power consumption vs. supply voltage                           | 87  |

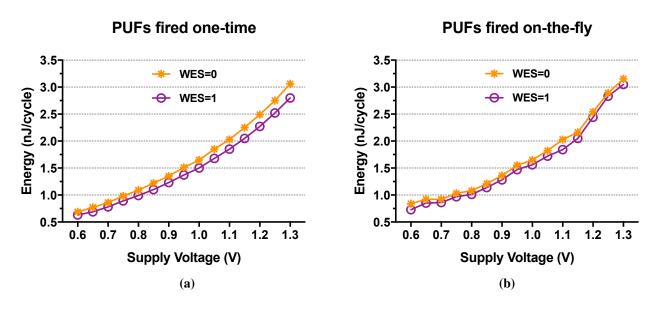

| 5.18 | Energy consumption per clock cycle for all operating modes                      | 87  |

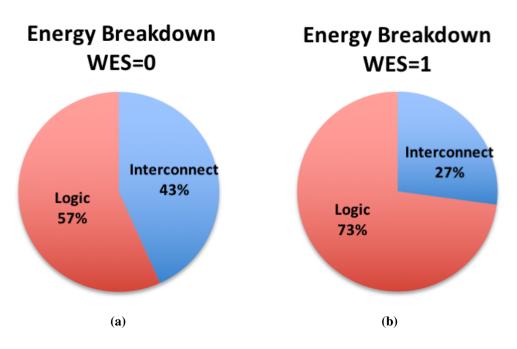

| 5.19 | Energy consumption breakdown for when PUFs are fired one-time                   | 88  |

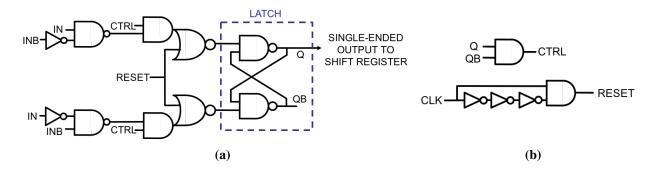

| 5.20 | Energy consumption breakdown for when PUFs are fired on-the-fly                 | 88  |

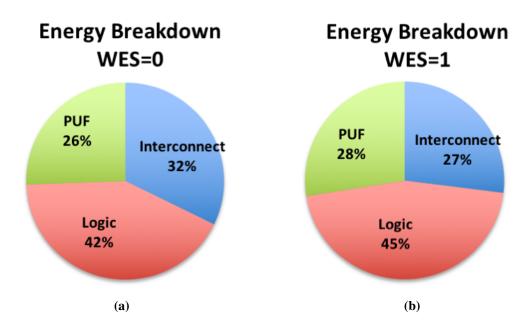

| 5.21 | Energy-delay product scaling with supply voltage                                | 89  |

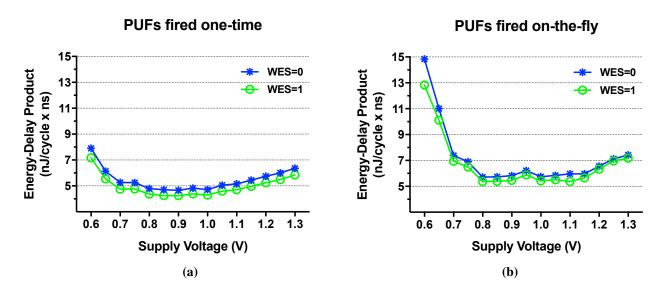

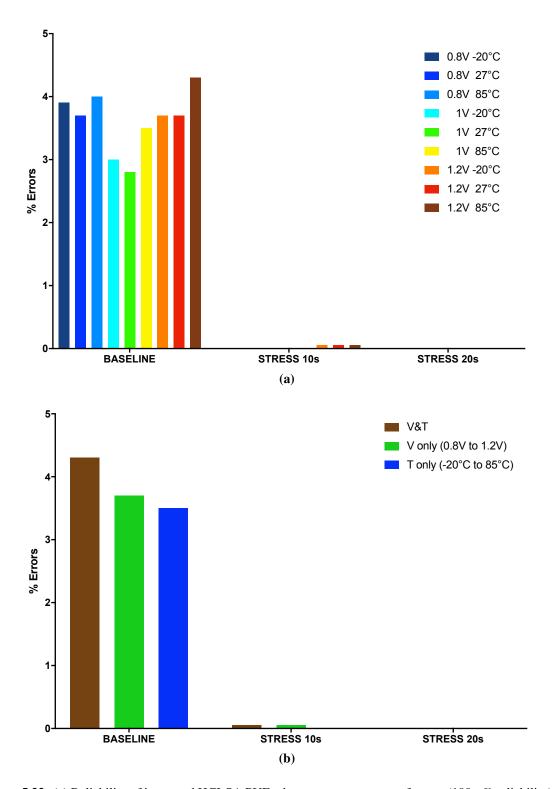

| 5.22 | Reliability of improved HCI-SA PUFs                                             | 92  |

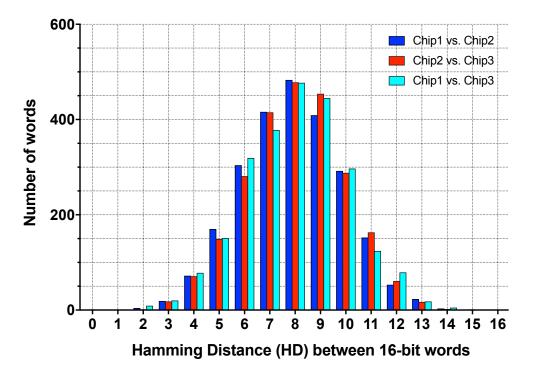

| 5.23 | Histogram of Hamming distance of 16-bit HCI-SA PUF responses from 3 chips .     | 94  |

| 5.24 | Re-programming HCI-SA PUFs with an HCI stress in the opposite direction         | 96  |

| 5.25 | Measurement and test setup for the DPA attack mounted on the secure FPGA fabric | 98  |

| 5.26 | Measuring the DUA current with a small resistor                                 | 99  |

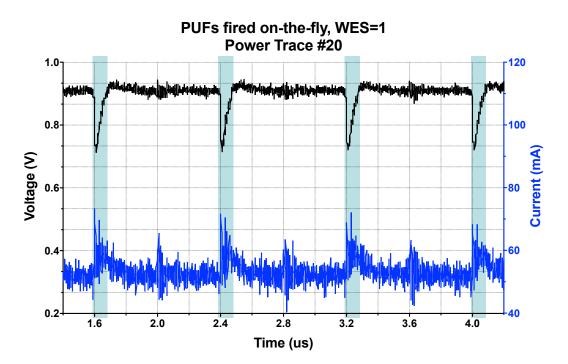

| 5.27 | Measured power trace (i.e., voltage and current) for Mode1 with on-the-fly PUF  |     |

|      | firing and WES=1                                                                | 100 |

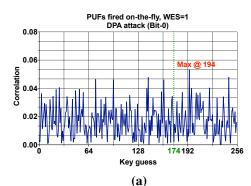

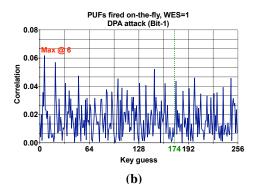

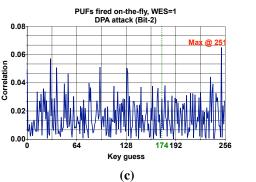

| 5.28 | DPA attack in Mode1, where the PUFs are fired on-the-fly and the interconnect   |

|------|---------------------------------------------------------------------------------|

|      | discharge is turned off                                                         |

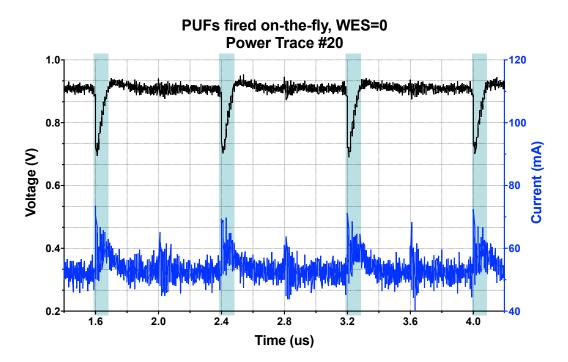

| A.1  | Measured power trace (i.e., voltage and current) for Mode1 with on-the-fly PUF  |

|      | firing and WES=0                                                                |

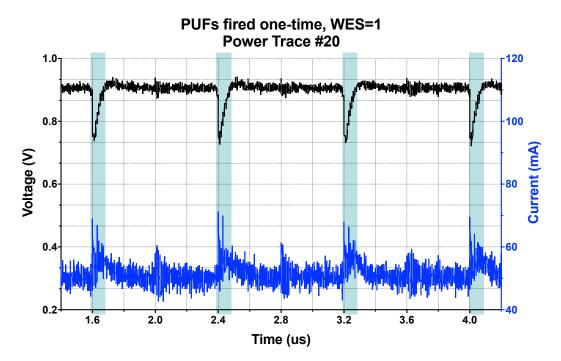

| A.2  | Measured power trace (i.e., voltage and current) for the default mode with one- |

|      | time PUF firing and WES=1                                                       |

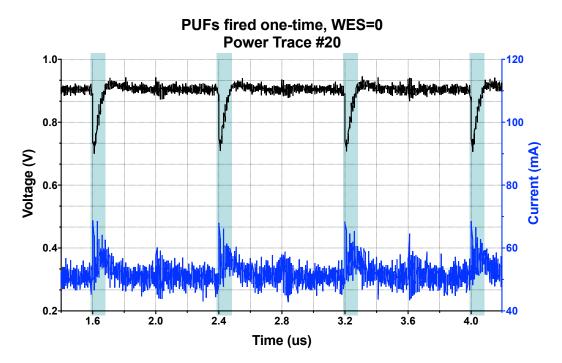

| A.3  | Measured power trace (i.e., voltage and current) for Mode2 with one-time PUF    |

|      | firing and WES=0                                                                |

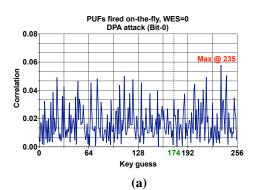

| A.4  | DPA attack in Mode3, where the PUFs are fired on-the-fly and the interconnect   |

|      | discharges                                                                      |

| A.5  | DPA attack in Mode2, where the PUFs are fired one-time and the interconnect     |

|      | discharges                                                                      |

| A.6  | DPA attack in the default mode, where the PUFs are fired one-time and the in-   |

|      | terconnect discharge is turned off                                              |

# **List of Tables**

| 2.1 | FPGA configuration storage options    8                                             |

|-----|-------------------------------------------------------------------------------------|

| 3.1 | Tile area breakdown    34                                                           |

| 3.2 | Benchmark timing results                                                            |

| 3.3 | Benchmark power results                                                             |

| 3.4 | Security comparison summary                                                         |

| 4.1 | State encoding for PCDL-STD control logic                                           |

| 4.2 | FPGA architecture parameters                                                        |

| 4.3 | FPGA multiplexers                                                                   |

| 4.4 | NED values for different FPGA building blocks                                       |

| 5.1 | Technology and testchip features                                                    |

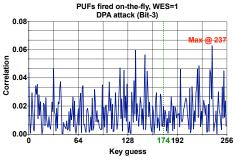

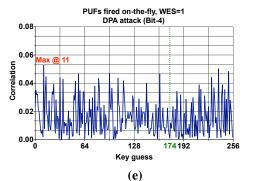

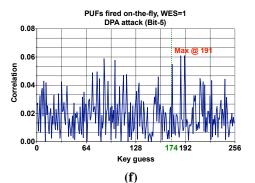

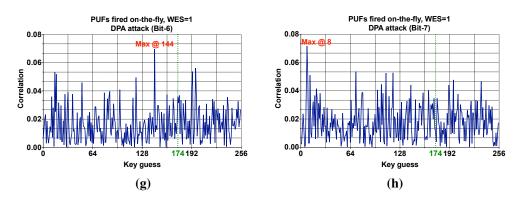

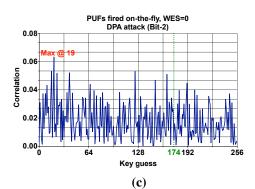

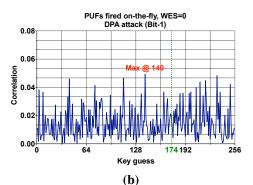

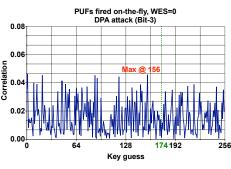

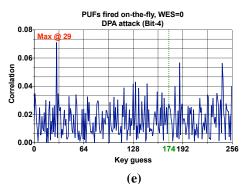

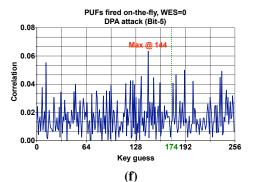

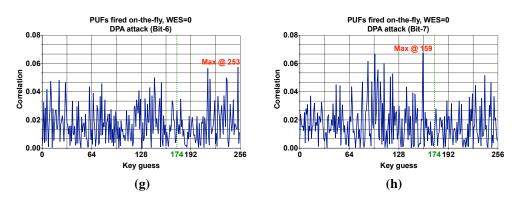

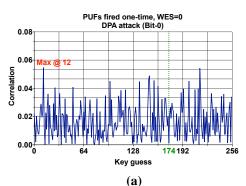

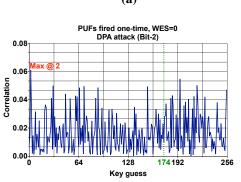

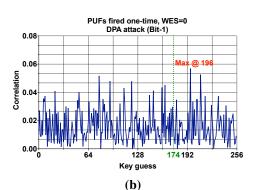

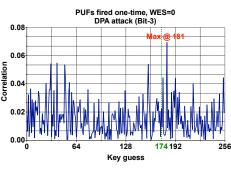

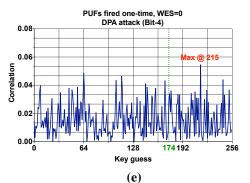

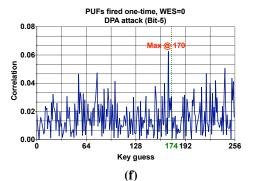

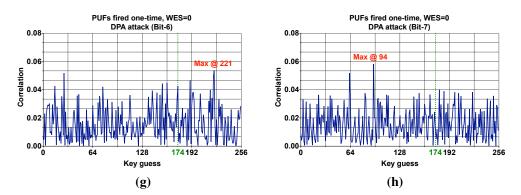

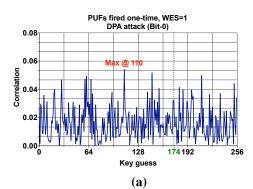

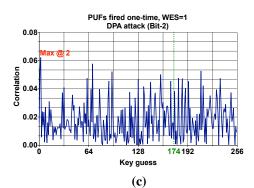

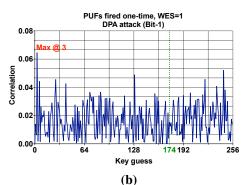

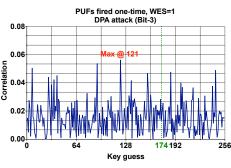

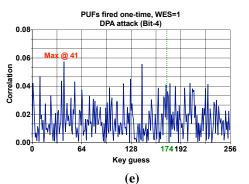

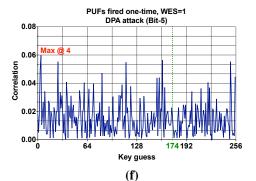

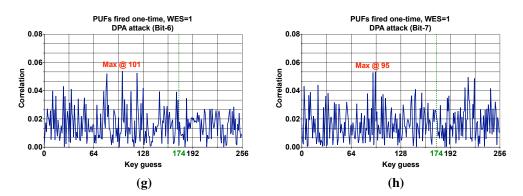

| 5.2 | Correlation analysis for DPA attacks on each bit (PUFs fired on-the-fly, WES=1) 102 |

| 5.3 | DPA attack results for each operating mode                                          |

"Nihil actu secure."

# Chapter 1

# Introduction

## 1.1 Motivation

As process technologies scale down to nanometer-regime, the long development time and high non-recurring engineering costs associated with modern integrated circuit design are becoming increasingly infeasible for all but the highest-volume parts. These factors have pushed many system designers to use programmable ICs, rather than costly, complex, custom ASICs. Field programmable gate arrays (FPGAs) are one of the most attractive programmable platforms, because they occupy middle ground between CPUs and custom ASICs, offering much of the flexibility of software programmed CPUs, but still achieving much of the performance and efficiency of custom ASICs. FPGAs enable rapid prototyping and development of complex ASICs and facilitate deployment of embedded systems with performance nearing ASICs. Consequently, FPGAs are widely used in a broad variety of applications including aerospace, supercomputing, high-speed signal processing, and cryptography [1].

The reconfigurable structure of FPGAs makes them a highly attractive implementation platform for secure systems due to their lack of application design information at manufacture-time, which mitigates risk in the event of compromise of the supply chain. Cryptographic applications and security protocols are efficiently implemented on FPGAs and are easily modified in the field unlike their ASIC counterparts. While this reconfigurability is useful for designers, it creates a new set of vulnerabilities for FPGA designs. A persistent source of security vulnerability in FPGA designs is the configuration bitstream. Although the actual design content is hidden until programming, the bitstream is required to configure an FPGA and needs to be protected against reverse-engineering. Possible compromise of configuration data by the attacker poses significant threats for deployed systems in the field. These threats include cloning the FPGA configuration for use in counterfeit/unauthorized systems, modification of the FPGA configuration to increase side-channel emissions, and adding malicious Trojan hardware into the compromised design [1, 2].

Another important FPGA security concern is the secure operation of FPGA designs running in the fabric. As is common with any other hardware implementations, cryptographic systems on FPGAs leak inadvertent side-channel information (i.e., power, timing, electromagnetic emissions etc.) that are exploited by the attacker to bypass the security of the algorithms [3, 4, 5]. One highly effective and easy-to-mount side-channel analysis (SCA) attack is power analysis, which exploits the data-dependent power consumption in the hardware [4, 6, 7].

### **1.2 Secured vs. Secure FPGA**

FPGA security concerns are addressed at different levels of abstraction that includes software/algorithm, register-transfer level (RTL), and hardware level depending on the countermeasure. In order to ensure bitstream protection, FPGA manufacturers have implemented various countermeasures within the standard FPGA design flow at both software/algorithm and hardware levels that includes bitstream encryption [1, 2, 8, 9]. However, these security measures can be circumvented in a number of ways that includes side-channel analysis (SCA) attacks on the bitstream decryption logic [1, 2, 10]. The job of the attacker is made simpler by the fact that the encryption key consists of relatively small number of bits (e.g., 128b keys in Microsemi FPGAs [9], 256b keys and 57b device ID in Xilinx FPGAs [8]) and that the bitstream decryptor is a single, identifiable point of attack. The fundamental problem is that the design configuration

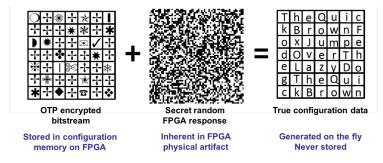

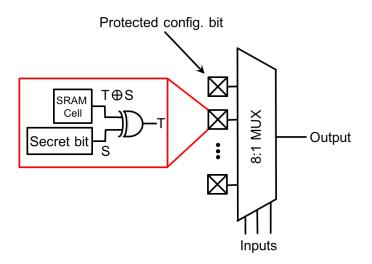

**Figure 1.1:** FPGA hardware entanglement concept using one-time pad encryption of the configuration bitstream using a secret die-specific response as the codebook.

data is stored in the clear at some level of hardware.

Secure operation is mainly addressed at the register-transfer-level (RTL) by layering countermeasures on an unsecured conventional-off-the-shelf (COTS) FPGA [6, 11, 12, 13, 14, 15, 16] instead of at the hardware level, since doing so requires modification on the FPGA fabric. These countermeasures achieve resistance against power SCA attacks at the expense of significant timing, area, and enery overheads [6, 11, 12, 13, 14, 15, 16]. Additionally, these techniques often require significant rework in the standard tool/programming flow since they involve low-level manipulation and relocation of logic on the FPGA fabric.

In this thesis, we present a *secure* FPGA design, wherein the hardware security features are implemented in the FPGA itself, rather than at the tool/application level. We alter the FPGA fabric itself in order to build security features. By this method, the FPGA is hardened in a virtually user-transparent manner. More specifically, we protect bitstream by hardware-entangling the configuration deep in the hardware with a secret die-specific response. This is equivalent to a one-time pad encryption of the true configuration data using the secret die-specific response as the codebook (Figure 1.1). Hence, the proposed FPGA design never stores the configuration data in the clear, even at the lowest level of the hardware. Furthermore, we also address one of the most common side-channel vulnerabilities, power side-channel, by using a side-channel resistant logic embedded in the fabric. This is a circuit-level hiding countermeasure employed in the fabric to reduce side-channel information leakage. We show that the hardware-entangled secure FPGA design is more efficient for iso-security against the existing countermeasures.

### **1.3 Dissertation Organization**

In Chapter 2, we provide background on the fundamentals of FPGA. We review the internal structure and security features of FPGAs with special attention to the major security concerns of bitstream protection and secure operation.

In Chapter 3, we discuss a novel hardware-entanglement method for FPGA bitstream protection against reverse-engineering attacks. We quantitatively evaluate area, performance, and power overheads of the hardware-entangled scheme, as well as evaluate the security benefits.

In Chapter 4, we introduce a secure FPGA fabric that employs a novel post-charged differential dynamic logic style with self-timed discharge (PCDL-STD) to achieve side-channel analysis (SCA) resistant secure operation. We compare VLSI metrics of the secure FPGA tile (i.e., area, delay, energy) against a reference unsecured static FPGA tile and the D-WDDL countermeasure layered on this unsecured FPGA. We also evaluate power SCA resistance of the secure PGA tile using the metric of normalized energy deviation (NED).

Finally, in Chapter 5, we present the implementation of the prototype testchip implementation for a proof-of-concept for our secure FPGA design. We describe the testchip details and present the measured silicon results, which includes benchmark implementation, PUF reliability analysis, power-SCA resistance evaluation.

# Chapter 2

## Background

In the introduction, we provided motivation and context for the thesis. In this chapter, we pave the way to FPGA security. First, we discuss the fundamentals of FPGA, cover the basic structure, and describe the programmable logic and interconnect. Then, we shift our focus to security by reviewing reverse-engineering attacks and their countermeasures. Next, we cover side-channel analysis (SCA) attacks and their countermeasures. Then, we discuss the security implications of reverse-engineering and SCA attacks to FPGA. Finally, we review the major FPGA security concerns of bitstream protection and side-channel resistant secure operation.

## 2.1 The Internals of an FPGA

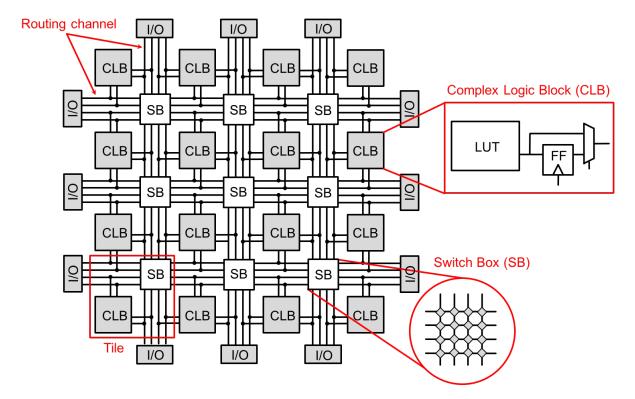

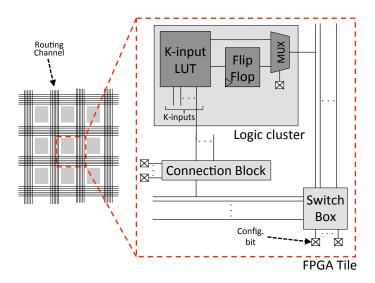

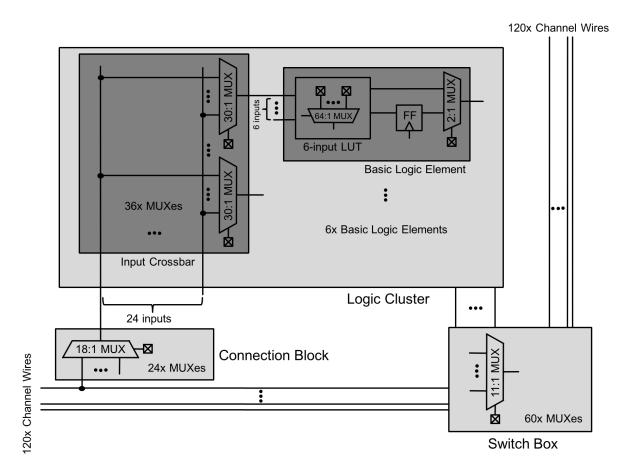

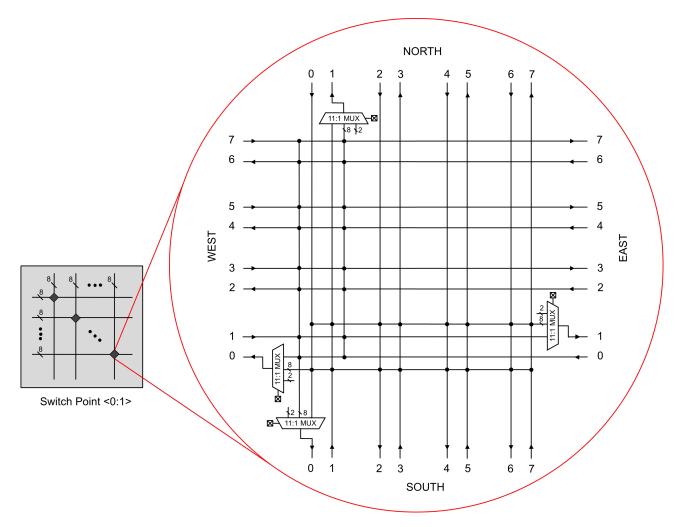

Figure 2.1 shows the basic architecture of a typical island-style FPGA that consists of identical tiles. Each tile consists of a Configurable Logic Block (CLB) and Switch Box (SB). Each CLB contains a look-up table (LUT) that is configured to implement a logic function. The interconnect is programmed to connect CLBs together in order to implement more complicated circuits on an FPGA.

The stream of data that specifies how the LUTs and the interconnect should be programmed in order to implement a benchmark circuit is referred to as a configuration bitstream. The FPGA configuration bitstream can be stored in a number of ways. FPGAs are usually categorized with respect to their configuration storage options (i.e., SRAM-based, flash, anti-fuse.). In the following, we describe different FPGA configuration options and how an FPGA is programmed by the user.

**Figure 2.1:** Architecture of a typical island-style FPGA. Configurable logic blocks (CLBs) are islands surrounded by routing channels. Each CLB contains a look-up table (LUT) that is configured to implement a logic function. The interconnect is also reconfigurable and it connects CLBs together to implement more complicated circuits on FPGA.

#### 2.1.1 FPGA Configuration Storage

| Storage Option | Re-configurable | Non-volatile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No extra<br>process steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No external<br>NVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLASH          | ✓               | <ul> <li>Image: A set of the set of the</li></ul> | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Image: A set of the set of the</li></ul> |

| Antifuse       | ×               | <ul> <li>Image: A start of the start of</li></ul> | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Image: A set of the set of the</li></ul> |

| SRAM           | ✓               | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>Image: A set of the set of the</li></ul> | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 2.1: FPGA configuration storage options

Both the reconfigurable logic and interconnect are programmed by the user based on their desired application via the configuration bitstream. The user writes an RTL description of the application that is converted into the configuration bitstream by FPGA-vendor-supplied CAD tools, which have detailed information regarding the FPGA internal structure embedded into them. The user can also input some low-level information regarding desired performance, power, and block placement to guide the final configuration.

The configuration bitstream of the FPGA can be stored in a number ways. Table 2.1 compares FLASH, antifuse, and SRAM configuration storage options. For example, FLASH FPGAs use a non-volatile memory (NVM) to store the configuration bitstream on the FPGA die. Antifuse FPGAs are also non-volatile but they use fuses that can be set one-time, hence they cannot be reconfigured. On the other hand, most sytems use volatile SRAM cells as the configuration storage due to high costs for an integrated NVM/logic fabrication process. These SRAM-based FPGAs require a separate NVM chip on the board, typically FLASH memory, as the FPGA die itself does not contain any NVM. At system power-up, the configuration bitstream is transferred to SRAM configuration storage bits on the FPGA from the NVM to configure the reconfigurable logic and interconnect. For the remainder of the thesis, we will focus on SRAM-based FPGAs.

#### 2.1.2 Reconfigurable Logic

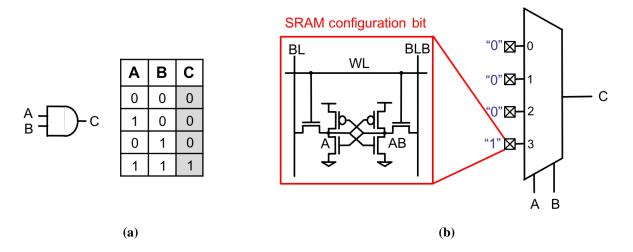

FPGA can be configured to look like any arbitrary set of interconnected logic gates. These logic gates are implemented by using look-up tables (LUTs) on the FPGA fabric. Each LUT is very generic because it can implement any k-input function ( $2^{2^k}$  possible functions). A k-input LUT

consists of an N:1 multiplexer (MUX), where  $N=2^k$ , and N configuration bits. Each configuration bit corresponds to a different output row in the truth table.

**Figure 2.2:** (a) 2-input AND gate and its truth table. (b) 2-input LUT that is configured to implement an AND gate. 6T-SRAM cells are used to store LUT configuration bits.

Any logic gate with a corresponding truth table can be mapped into an FPGA by programming the LUTs with the appropriate truth table. For example, a two-input LUT that is configured to implement an AND gate is shown in Figure 2.2b. An AND gate outputs logic-1 only when both the inputs are logic-1 (i.e., A = 1 and B = 1), otherwise the output is logic-0 (Figure 2.2a). Therefore, the logic-1 that is stored in the configuration bit 3 is selected at the LUT output when both A and B are logic-1. For all other input combinations, the LUT output is logic-0. Any other logic function can be programmed in similar fashion.

#### 2.1.3 Reconfigurable Interconnect

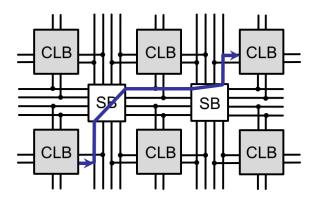

Each CLB contains a LUT that can be configured to implement any logic function. More complex circuits are implemented by connecting multiple CLBs via the programmable interconnect. An example connection between two CLBs via two programmed SBs is illustrated in Figure 2.3. Only length-1 (i.e., wires that only connect neighboring SBs) wires are shown for simplicity, but commercial FPGAs typically have routing tracks of varying lengths that connect distant SBs.

Called segmented architecture, these tracks are shown to lead to a higher density, performance, and energy efficiency [17, 18, 19, 20].

An SB is formed when a horizontal and vertical routing channel intersect as shown in Figure 2.1. It contains a matrix of switches that interconnect wires. This structure allows nets to turn corners or extend farther down the routing channel [17]. A full crossbar implementation in a switch matrix (SM) requires  $N^2$  connections [1, 20, 21]. Despite the higher flexibility/routability, full crossbar SM increases both the SB area and the number of configuration bits to program the SB [17, 18, 22]. Sparse SMs, on the other hand, are smaller at the cost of reduced flexibility/routability. There is a trade-off between the flexibility/routability and area efficiency of SM implementation.

**Figure 2.3:** FPGA interconnect architecture. Each CLB implements a logic gate. More complex circuits are implemented by connecting multiple CLBs via the programmable interconnect. An example connection between two CLBs via two programmed SBs is highlighted in blue.

Switch design is very critical for modern FPGAs because the area is dominated by the interconnect (i.e., 80-90% FPGA area in the interconnect); the interconnect accounts for most of the FPGA's delay and energy [20, 21]. Designers explored different SM designs to have a high flexibility/routability while maximizing the area efficiency [18, 22, 23]. Switches, which influence the flexibility/routability, can either be bi-directional or uni-directional. Figure 2.4a shows a bi-directional switch that consists of tri-state drivers (i.e., pass transistors). Channel wires can be driven from both sides of the pass transistors. In contrast, Figure 2.4b shows a uni-directional switch that replaces tri-state drivers with regular drivers and the channel wires are driven in one direction. Uni-directional switches are shown to be more efficient in terms of area, performance,

**Figure 2.4:** (a) A bi-directional switch that consists of tri-state drivers (i.e., pass transistors). (b) a uni-directional switch in which tri-state drivers are replaced with regular drivers. Note that two sets of wires for are shown in each direction: (1) incoming and (2) outgoing. Uni-directional switches are shown to be more efficient in terms of area, performance, and energy [17].

## 2.2 Reverse-Engineering Attacks and Countermeasures

#### 2.2.1 Reverse-Engineering Attacks

A myriad of security vulnerabilites can be exposed via the reverse-engineering of the integrated circuits (ICs) contained in electronics systems. The goal of IC reverse-engineering is to uncover the functionality and internal structure (e.g., gate netlist, circuit schematic, layout, manufacturing process details) of the chip via techniques such as depackaging/delayering, high-resolution imaging, probing, and side-channel examination. With this knowledge, an attacker can mount various attacks more efficiently (e.g., fault injection, side-channel), clone/counterfeit the design possibly with hardware Trojans inserted, and discover trade secrets (e.g., proprietary algorithms, hard-coded keys and instruction sequences) [24, 25, 26, 27, 28]. A number of commercial entities, such as ChipWorks [29] and TAEUS [30], routinely reverse-engineer chips on even the most advanced process technologies.

#### 2.2.2 Countermeasures

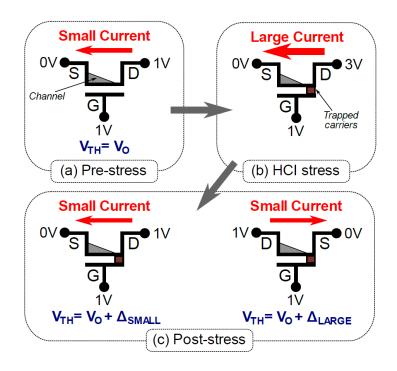

To combat reverse-engineering, researchers have proposed a number of countermeasures that include gate camouflaging wherein an attacker cannot discern the functionality of a particular logic gate based solely on its observable physical characteristics. One proposed camouflaging technique by Rajendran et al. uses a mix of dummy and real vias/contacts to obscure the gate function [31]. Another technique from SypherMedia [32] uses look-alike gates made with special structures requiring special layers, DRC waivers, and other low-level process manipulations. The security of these camouflaging techniques relies on the limited ability of the attacker to distinguish between real and dummy structures. However, delayering and imaging capabilities of state-of-the-art reverse-engineering are likely advanced enough to not be fooled by such structures [29, 30]. Alternatively, Erbagci et al. proposed using threshold voltage  $(V_{TH})$  defined (TVD) camouflaged gates [33] that use different  $V_{TH}$  transistors, but with identical layouts, to determine the logic gate function. Every TVD logic gate has the same physical layout and is one-time mask programmed with different threshold implants for different boolean functions. Akkaya et. al. proposed a post-manufacturing programmable version of TVD logic (PMP-TVD) to obscure the design IP from an untrusted foundry and to combat reverse-engineering [34]. Intentional hot-carrier injection (HCI) is used to program PMP-TVD gates with different threshold voltages [34].

Other than obscuring the logical functionality at the layout level, researchers have proposed transformations on the register transfer level (RTL) hardware description language (HDL) (e.g., Verilog, VHDL) to make reverse-engineering more challenging [35, 36]. As these synthesized designs often have significant whitespace, researchers have also proposed adding unused dummy gates and interconnections [37]. These countermeasures are in an arms race against reverse-engineering tools that offer significant capabilities to descramble obfuscated designs [29, 38, 39, 40, 41, 42, 43].

Adding gates with some form of reconfigurability has also been offered as a way to conceal design intent from reverse-engineer threats. These methods typically require a memory element

in order to store the configuration in working designs in the field [38, 44, 45]. Thus, even if the basic design database does not contain the design information, the deployed systems do and thus are vulnerable to reverse-engineering.

### **2.3** Side-Channel Analysis Attacks and Countermeasures

#### 2.3.1 Side-Channel Analysis Attacks

Side-channel analysis (SCA) attacks target inadvertent information leakage in physical implementations rather than the weaknesses of cryptographic algorithms (Figure 2.7). One highly effective and easy-to-mount SCA attack is power analysis, which exploits the data dependent power consumption in the hardware [4, 6, 7]. Types of power analysis include simple power analysis (SPA), differential power analysis (DPA), correlation power analysis (CPA), and leakage power analysis (LPA). All of these attacks have different requirements and limitations.

Figure 2.5: Side-channel emissions from device under attack (DUA): optical, power, electromagnetic (EM), and acoustic [46].

SPA attacks focus on the use of visual inspection techniques to identify relevant power fluctuations during cryptographic operations [4]. Hence, SPA attacks often require detailed knowledge about the implementation of the cryptographic algorithm that is executed by the device-underattack (DUT). Alternatively, DPA attacks do not require detailed knowledge about the attacked device. However, more power traces are required by DPA attacks because they use statistical analysis and error correction techniques to extract information correlated to secret keys [4]. CPA attacks involve the evaluation of the degree of correlation between variations within the set of measurements [4]. LPA attacks exploit the dependence of leakage current of the circuits on their inputs, rather than the dynamic power [47]. Among the types of power analysis, DPA is the most prevalent and effective according to research on various crypto-systems in [4, 16, 48, 49].

#### 2.3.2 Countermeasures

Hiding and masking countermeasures seek to achieve resistance against power SCAs at the expense of significant timing, area, and energy overheads [6, 11, 12, 13, 14, 15, 50, 51]. As illustrated in Figure 2.6, masking logic seeks to remove the correlation between the input data and side-channel emissions from intermediate values by using a random mask at the selected nodes in a specific design. However, the success of masked logic is limited because it is vulnerable against a number of successful higher order power SCAs [52, 53, 54]. Hiding technique decreases the signal-to-noise ratio (SNR) by either increasing the noise or reducing the signal. One method to reduce SNR is to make the side-channel emissions independent of the data being processed.

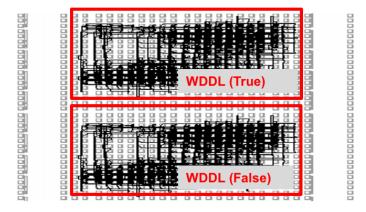

Various logic families achieve low side-channel leakage. One common use is dynamic differential pre-charge logic (DDPL), wherein a single switching event per clock cycle is guaranteed independent of input data [14, 50, 51, 55, 56]. For instance, wave dynamic differential logic (WDDL) uses traditional static CMOS gates to produce complementary versions of every output, and each output is pre-charged to ensure every output transitions exactly once in each clock cycle. In WDDL, a design is duplicated into a true and a complementary part by restricting the set of logic for each part to AND- and OR-gates to avoid glitches. These two parts are dual and one can be derived from the other by inverting the inputs and changing AND-gates to OR-gates, vice versa. The precharge phase of WDLL is unique such that a block in WDDL precharges without disturbing a global precharge signal to each individual gate as is normally done in DDPL [15]. Since WDDL consists of AND- and OR-gates, whenever the inputs of these gates are logic-0,

**Figure 2.6:** Masked logic vs. differential logic to achive power side-channel analysis resistance [16]. Masked logic seeks to remove the correlation between the input data and side-channel emissions from intermediate values by using a random mask at the selected nodes in a design. Differential logic, on the other hand, seeks to to make the side-channel emissions independent of the data being processed.

the output will be logic-0 as well. During the precharge phase, all of the inputs of a WDDL design are set to logic-0 and each individual gate will eventually have all its inputs and outputs at logic-0. This allows the precharge wave propagation throughout the combinational gates. At the same time, the data rate is halved since every evaluation cycle is followed by a logic-0 propagation. WDDL has significant overheads (i.e., up to 4x, 3x, 3.5x in area, delay, energy, respectively [14]). Furthermore, differences in output loading between complementary outputs and internal switching differences can cause data-dependent power consumption, which can be exploited by power SCAs [16, 57].

In order to remove the requirement for equal loading, an unconditional discharge phase on differential outputs is introduced. For example, Three-phase Dual-Rail Pre-charge Logic (TDPL) has a three-phase operation, in which (1) precharge and (2) evaluation phases are followed by (3) an unconditional discharge phase [51]. However, this requires complex three-phase clock generation and distribution that makes TDPL vulnerable to attacks on the clocking infrastructure. An

attacker can potentially alter the clock generation to separate the discharge phase from the evaluate phase (or even completely eliminate it), which bypasses the countermeasure [55]. Hence, a self-timed version of TDPL (ST-TDPL) has been introduced [55]. ST-TDPL uses a single clock, versus three in conventional TDPL, thus eliminating the need for complicated three-phase clock generation and distribution. In a chain of ST-TDPL gates, each gate controls the discharge phase of the previous stage. Each stage discharges once the following stage completes the evaluation. However, with the increased gate fan-out, this hand-shake mechanism between the stages complicates the design of ST-TDPL gates.

Switch-Capacitor Logic (SCL) uses a different hiding approach. In this scheme, the internal power supply is isolated with a large capacitor rather than modifying each logic gate to decrease data-dependent power consumption [58]. It has three phases of operation: (1) precharge, (2) evaluation, and (3) discharge. During precharge, the capacitor is charged to VDD from the global power supply of the chip. During evalution, the capacitor disconnects from the power supply and the circuit draws current from the capacitor. During discharge, the capacitor is shunted to a consistent reference voltage. Hence, the SCL circuit uses a constant amount of power even with the use of standard CMOS logic gates [58]. However, if the attacker surpasses the protection, the sensitive circuit will be unprotected. SCL also incurs significant area, delay, and energy overheads [58].

## 2.4 FPGA Security

#### 2.4.1 Design Protection against Reverse-Engineering

The underlying platform for FPGA does not reveal information about the actual design until programming. Hence, the physical attacks discussed in Section 2.2 are irrelevant at the time of manufacturing. However, the configuration bitstream has the sensitive design information and needs to be protected against reverse-engineering during all stages from bitstream generation to device programming.

**Figure 2.7:** Bitstream encryption scheme for protection against reverse-engineering attacks. At the time of bitstream generation in the CAD tool, the user inputs an encryption key that is used to encrypt the configuration data and the encrypted bitstream is stored in NVM on the FPGA board. The same key is used for decryption during the programming [2]. The plaintext and the encrypted bitstream are shown in blue and orange, respectively.

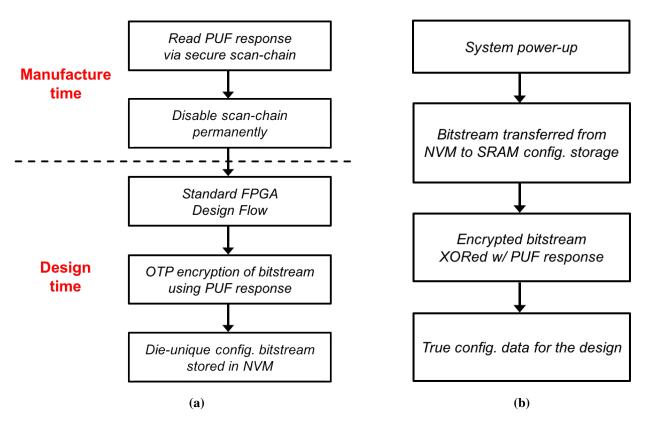

FPGA manufacturers have implemented various countermeasures in the standard FPGA design flow [1]. Among these are bitstream encryption, bitstream authentication/validation, active defense mechanisms on FPGA test and support circuits, and flash FPGAs. At the time of bitstream generation in the CAD tool, the user inputs an encryption key that is used to encrypt the configuration data [2]. The same encryption key is stored on the FPGA in a small amount of non-volatile memory (e.g., using e-fuses) or a battery-backed volatile memory [8] for decryption.

However, the decryptor block remains vulnerable to both direct probing of key storage and SCA attacks, in which the encryption key can be successfully extracted [1, 2, 10, 59, 60, 61]. Furthermore, despite the bitstream encryption, the plaintext configuration bitstream is stored in the lowest level of hardware (i.e., configuration storage on FPGA die) that can be potentially extracted with low-level probing techniques [10, 62, 63, 64, 65].

A unique device ID can be used to validate the bitstream on the FPGA (e.g., a 57b device ID along with 64-byte factory flash ID used in Xilinx FPGAs [8]). Bitstream encryption is used in conjunction with bitstream encryption to prevent any unauthorized access to FPGA. Further, active defense mechanisms can monitor and protect the testing and programming ports [8]. In FLASH FPGAs, there is no optical difference after configuration, which makes direct probing attacks highly complex [2].

#### 2.4.2 Side-Channel Analysis Resistant Secure Operation

The majority of power SCA resistant logic families discussed earlier cannot be ported directly to FPGA due to problems with flow and integration. Hence, the options to implement SCA-resistant circuits on FPGA are very limited. WDDL is a representative example of such circuits. Tiri et. al. proposes a synthesis flow to implement WDDL circuits on FPGA [15]. This technique combines standard FPGA building blocks to make secure compound standard cells with low power side-channel leakage.

Any imbalance or asymmetry between the routings of complementary parts can be exploited to decrease power side-channel resistance of WDDL [16, 57]. However, balancing differential nets is not a trivial task; it requires precise control over the placement and routing of the complementary parts on the FPGA. The techniques to address routing problems include double-WDDL (D-WDDL) [16], seperated-DDL [66], and divided backend multiplication [67]. These techniques involve low-level manipulation and relocation of logic on the FPGA fabric, hence require a rework in the tool/programming flow.

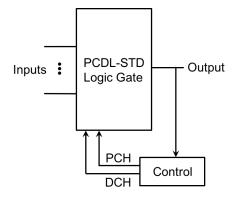

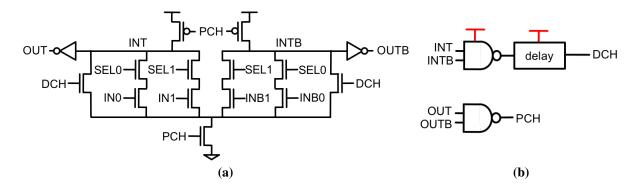

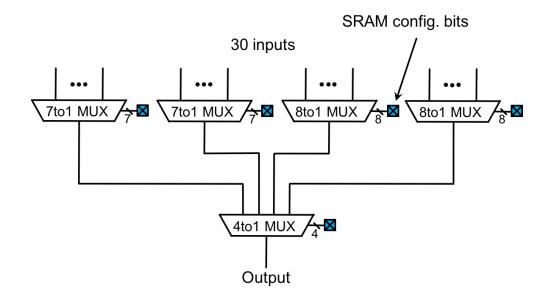

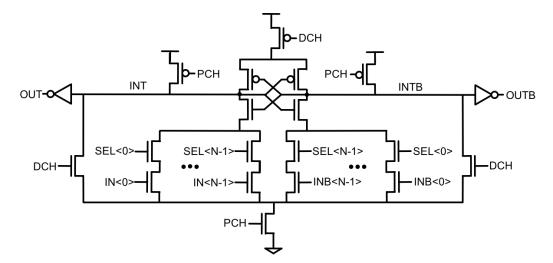

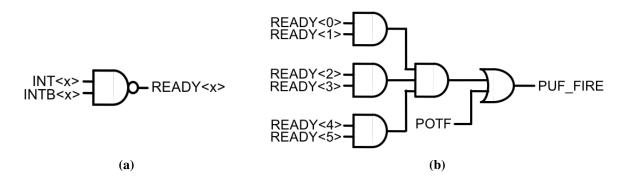

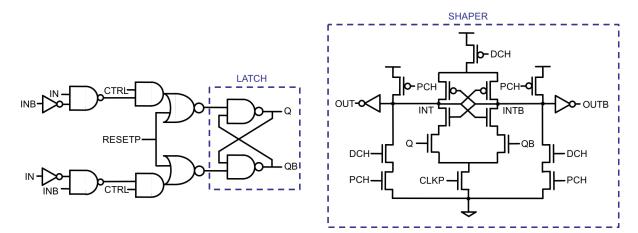

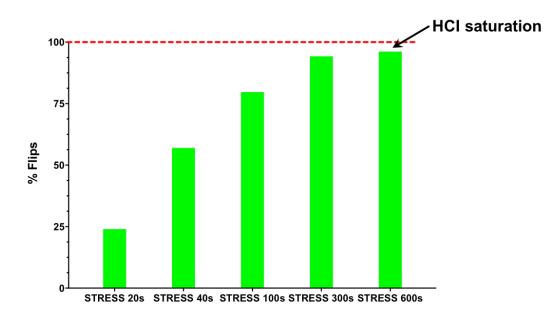

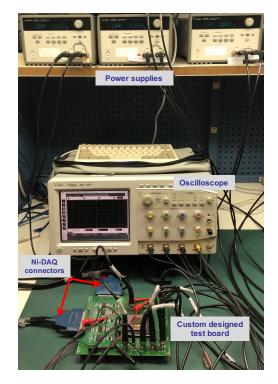

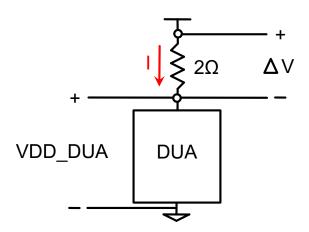

**Figure 2.8:** Double Wave Dynamic Differential Logic (D-WDDL) route preserving design duplication. Dual WDDL modules (i.e., true and false) with precisely matched routing are generated for power SCA resistance [16].