### A Formal Approach to Memory Access Optimization: Data Layout, Reorganization, and Near-Data Processing

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

#### BERKIN AKIN

B.S., Electrical and Electronics Engineering, Middle East Technical University M.S., Electrical and Computer Engineering, Carnegie Mellon University

Carnegie Mellon University Pittsburgh, PA, USA

July 2015

### **Abstract**

The memory system is a major bottleneck in achieving high performance and energy efficiency for various processing platforms. This thesis aims to improve memory performance and energy efficiency of data intensive applications through a two-pronged approach which combines a formal representation framework and a hardware substrate that can efficiently reorganize data in memory.

The proposed formal framework enables representing and systematically manipulating data layout formats, address mapping schemes, and memory access patterns through permutations to exploit the locality and parallelism in memory. Driven by the implications from the formal framework, this thesis presents the HAMLeT architecture for highly-concurrent, energy-efficient and low-overhead data reorganization performed completely in memory. Although data reorganization simply relocates data in memory, it is costly on conventional systems mainly due to inefficient access patterns, limited data reuse, and roundtrip data traversal throughout the memory hierarchy. HAMLeT pursues a near-data processing approach exploiting the 3D-stacked DRAM technology. Integrated in the logic layer, interfaced directly to the local controllers, it takes advantage of the internal fine-grain parallelism, high bandwidth and locality which are inaccessible otherwise. Its parallel streaming architecture can extract high throughput from stringent power, area, and thermal budgets.

The thesis evaluates the efficient data reorganization capability provided by HAMLeT through several fundamental use cases. First, it demonstrates software-transparent data reorganization performed in memory to improve the memory access. A proposed hardware monitoring determines

inefficient memory usage and issues a data reorganization to adapt an optimized data layout and address mapping for the observed memory access patterns. This mechanism is performed transparently and does not require any changes to the user software—HAMLeT handles the remapping and its side effects completely in hardware. Second, HAMLeT provides an efficient substrate to explicitly reorganize data in memory. This gives an ability to offload and accelerate common data reorganization routines observed in high-performance computing libraries (e.g., matrix transpose, scatter/gather, permutation, pack/unpack, etc.). Third, explicitly performed data reorganization enables considering the data layout and address mapping as a part of the algorithm design space. Exposing these memory characteristics to the algorithm design space creates opportunities for algorithm/architecture co-design. Co-optimized computation flow, memory accesses, and data layout lead to new algorithms that are conventionally avoided.

## Acknowledgement

I owe all my success to my great advisors Professor James Hoe and Professor Franz Franchetti. Their support, advice and expertise made this work possible, I am very thankful for their time and effort. James has tremendous experience and expertise in addition to his great personality and sense of humor. Although this thesis was "done in his head" long before, it took me a while to "make it perfect". Franz is one of the smartest people that I have ever met. He always had brilliant ideas and creative solutions in every subject. Our long and productive discussions, which are made enjoyable thanks to his unique wit, contributed to a huge portion of this thesis. To me both James and Franz are both excellent advisors and good friends.

I would like to thank my thesis committee members Professor Larry Pileggi and Professor Steve Keckler. Larry provided me great support and feedback throughout my PhD life including my thesis. I'm thankful to him for giving me the opportunity to access the state-of-the-art silicon technology and also teaching me how to use it. His collaboration and efforts were really valuable to me. Steve provided helpful feedback, constructive discussions and great architecture insights which made this thesis possible. I'm grateful for his time and effort.

This work was partially sponsored by the Defense Advanced Research Projects Agency (DARPA) PERFECT program under agreement HR0011-13-2-0007. I'm thankful for their generous supports to fund this research.

I'd like to also thank all the SPIRAL and CALCM team members in CMU. First, I'm thankful to Peter Milder for introducing me to his hardware infrastructure in SPIRAL, and for his help and collaboration during my first years in CMU. I'd like to also thank Michael Papamichael and Gabe Weisz for their company in the office and in various conferences, and also for their useful discussions on a lot of research or non-research topics. Special thanks to Michael for his suggestions on a lot of "how to fix a VW Golf" topics. I had the honor to work with great lab mates, researchers and post-docs in SPIRAL and CALCM including Nikos Alachiotis, Christos Angelopoulos, Kevin Chang, Eric Chung, Qi Guo, Yoongu Kim, Peter Klemperer, Bob Koutsoyannis, Tze Meng Low, Joe Melber, Marie Nguyen, Eriko Nurvitadhi, Thom Popovici, Fazle Sadi, Lavanya Subramanian, Richard Veras, Yu Wang, Guanglin Xu, Jiyuan Zhang, Zhipeng Zhao, Qiuling Zhu, and many more.

I would like to also thank excellent professors in CMU that I got a chance to meet and work together. Especially, I'd like to thank Professor Onur Mutlu for teaching me advanced computer architecture, Professor Jose Moura and Professor Markus Puschel for our collaborations in SPIRAL, special thanks to Markus for being a great host in Zurich.

I thank all of the brilliant ECE staff, especially Claire Bauerle and Samantha Goldstein who made administrative tasks run smoothly.

I feel lucky to be around great friends and fellow graduate students in Pittsburgh. There are too many to list but special thanks go to Ekin Sumbul and Cagla Cakir for their answers to my yet another circuits questions, and to Onur Albayrak, Melis Hazar, Meric Isgenc, Tugce Ozturk, Mert Terzi, Sercan Yildiz, and many more. Thank you all for making the life here so much fun.

Trying to push processing "near" memory was a bit difficult, when I was "far away" from my family. I cannot express with words my gratefulness to my parents Adil Akin and Leyla Akin, and my sister Gizem Akin. Although they will not understand much of it, this thesis would be impossible without their love and support.

Finally, I'd like to thank Sila Gulgec, my "home" here, for her continuous love and support. She was always with me both in the most stressful and the happiest times throughout this journey. This thesis would be meaningless without her.

## **Contents**

| 1 | Intr | oduction                                       | 1  |

|---|------|------------------------------------------------|----|

|   | 1.1  | Motivation                                     | 1  |

|   | 1.2  | Thesis Approach and Contributions              | 3  |

|   | 1.3  | Thesis Organization                            | 6  |

| 2 | Bacl | kground                                        | 9  |

|   | 2.1  | The Main Memory System                         | 9  |

|   |      | 2.1.1 DRAM Organization and Operation          | 9  |

|   |      | 2.1.2 3D-stacked DRAM Technology               | 14 |

|   | 2.2  | Hitting the Memory and Power Walls             | 18 |

|   | 2.3  | Near Data Processing                           | 20 |

|   |      | 2.3.1 3D Stacking Based Near Data Processing   | 21 |

|   |      | 2.3.2 Hardware Specialization for NDP          | 22 |

|   | 2.4  | Data Layout and Reorganization                 | 23 |

| 3 | A Fo | ormal Approach to Memory Access Optimization   | 29 |

|   | 3.1  | Mathematical Framework                         | 29 |

|   |      | 3.1.1 Formula Representation of Permutations   | 30 |

|   |      | 3.1.2 Formula Identities                       | 33 |

|   | 3.2  | Permutation as a Data Reorganization Primitive | 34 |

|   | 3.3  | Index Transformation                           | 35 |

|   | 3.4  | A Fori  | nula Rewrite System for Permutations            | 40 |

|---|------|---------|-------------------------------------------------|----|

|   |      | 3.4.1   | Permutation Rewriting                           | 41 |

|   |      | 3.4.2   | Labelled Formula                                | 42 |

|   |      | 3.4.3   | Case Study                                      | 43 |

|   | 3.5  | Practic | cal Implications                                | 45 |

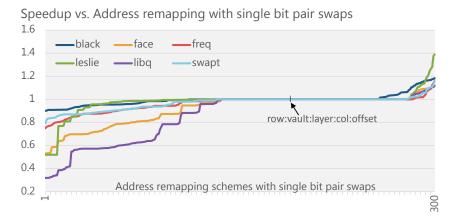

|   | 3.6  | Spiral  | Based Toolchain                                 | 47 |

| 1 | HAI  | MLeT A  | Architecture for Data Reorganization            | 49 |

|   | 4.1  | Data F  | Reorganization Unit                             | 50 |

|   |      | 4.1.1   | Reconfigurable Permutation Memory               | 51 |

|   |      | 4.1.2   | DMA Units                                       | 56 |

|   | 4.2  | Addre   | ss Remapping Unit                               | 58 |

|   |      | 4.2.1   | Bit Shuffle Unit                                | 59 |

|   |      | 4.2.2   | Supporting Multiple Remappings                  | 59 |

|   | 4.3  | Config  | guring HAMLeT                                   | 61 |

| 5 | Fun  | dament  | al Use Cases                                    | 65 |

|   | 5.1  | Auton   | natic Mode                                      | 65 |

|   |      | 5.1.1   | Changing Address Mapping                        | 67 |

|   |      | 5.1.2   | Physical Data Reorganization                    | 67 |

|   |      | 5.1.3   | Memory Access Monitoring                        | 69 |

|   |      | 5.1.4   | Host Application and Reorganization in Parallel | 70 |

|   | 5.2  | Explic  | it Mode                                         | 71 |

|   |      | 5.2.1   | Spiral Based Toolchain                          | 72 |

|   |      | 5.2.2   | Explicit Memory Management                      | 73 |

| 6 | Syst | em Arc  | hitecture and Integration                       | 75 |

|   | 6.1  | Memo    | ry Side Architecture                            | 76 |

|   |      | 6.1.1   | Interface and Design Space                      | 76 |

|   |      | 6.1.2    | Implementing Memory Access Monitors                      | 80  |

|---|------|----------|----------------------------------------------------------|-----|

|   | 6.2  | Handli   | ng Parallel Host Access and Reorganization               | 82  |

|   |      | 6.2.1    | Block on Reorganization (BoR)                            | 83  |

|   |      | 6.2.2    | Access on Reorganization (AoR)                           | 83  |

|   |      | 6.2.3    | Handling Memory Coherence                                | 86  |

|   | 6.3  | Host A   | architecture/Software Support                            | 89  |

|   |      | 6.3.1    | Memory Management for NDP                                | 90  |

|   | 6.4  | Putting  | g It Together                                            | 92  |

| 7 | Eval | luation  |                                                          | 95  |

|   | 7.1  | Experi   | mental Procedure                                         | 96  |

|   |      | 7.1.1    | 3D-stacked DRAM Modeling                                 | 96  |

|   | 7.2  | Autom    | atic Mode                                                | 98  |

|   |      | 7.2.1    | Dynamic Data Reorganization Overview                     | 98  |

|   |      | 7.2.2    | Address Remapping: Manual Search vs. Hardware Monitoring | 100 |

|   |      | 7.2.3    | Tuning the DRU Design Parameters                         | 103 |

|   |      | 7.2.4    | Multi-program Workloads                                  | 106 |

|   |      | 7.2.5    | Host Access and Data Reorganization in Parallel          | 108 |

|   | 7.3  | Explic   | it Mode                                                  | 115 |

|   |      | 7.3.1    | Accelerating Common Data Reorganization Routines         | 115 |

|   |      | 7.3.2    | Near-memory vs. On-chip                                  | 119 |

|   |      | 7.3.3    | Offload and Reconfiguration Overhead                     | 120 |

|   | 7.4  | Hardw    | are Synthesis                                            | 122 |

|   |      | 7.4.1    | Reconfigurable Permutation Memory                        | 122 |

|   |      | 7.4.2    | Overall System                                           | 123 |

| 8 | Co-c | optimizi | ng Compute and Memory Access                             | 125 |

|   | 8.1  | Fast Fo  | ourier Transform                                         | 126 |

|   | 82   | Machi    | na Madal                                                 | 120 |

|     | 8.3              | Block Data Layout FFTs                  |                                                |     |  |

|-----|------------------|-----------------------------------------|------------------------------------------------|-----|--|

|     | 8.4              | Formally Restructured Algorithms        |                                                |     |  |

|     | 8.5              | Algorithm and Architecture Design Space |                                                |     |  |

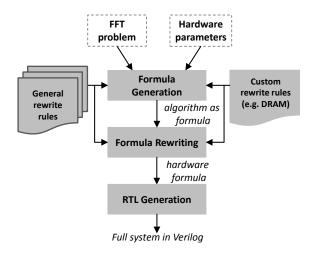

|     |                  | 8.5.1                                   | Automated Design Generation via Spiral         | 136 |  |

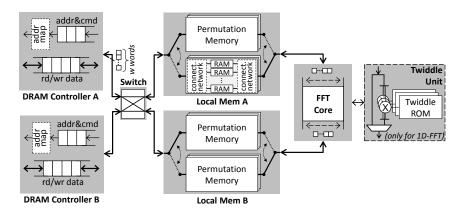

|     |                  | 8.5.2                                   | Formula to Hardware                            | 137 |  |

|     |                  | 8.5.3                                   | Design Space Parameters                        | 139 |  |

|     | 8.6              | Experi                                  | mental Results                                 | 140 |  |

|     |                  | 8.6.1                                   | Machine Model Based Evaluation                 | 140 |  |

|     |                  | 8.6.2                                   | Design Space Exploration                       | 142 |  |

|     |                  | 8.6.3                                   | Explicit Data Reorganization                   | 149 |  |

| 9   | Rela             | ted Wo                                  | rk                                             | 151 |  |

|     | 9.1              | Planar                                  | Near Data Processing                           | 151 |  |

|     | 9.2              | 3D-stac                                 | cking Based NDP                                | 152 |  |

|     | 9.3              | Softwa                                  | re Based Data Layout Transformation            | 154 |  |

|     | 9.4              | Hardwa                                  | are Assisted Data Reorganization               | 154 |  |

|     | 9.5              | Kronec                                  | ker Product Formalism for Hardware Design      | 156 |  |

| 10  | Conc             | clusions                                | and Future Directions                          | 157 |  |

|     | 10.1             | Future                                  | Directions                                     | 158 |  |

|     |                  | 10.1.1                                  | Data Reorganization for Irregular Applications | 158 |  |

|     |                  | 10.1.2                                  | General Purpose NDP                            | 158 |  |

|     |                  | 10.1.3                                  | Graph Traversal in 3D-stacked DRAM             | 160 |  |

| Bil | Bibliography 165 |                                         |                                                |     |  |

# **List of Figures**

| A single chip heterogeneous multicore computing system                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Overview of an off-chip planar DRAM module organization                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Locality/parallelism vs. bandwidth, power and energy tradeoffs for DDR3-1600           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| DRAM (1.5V, single rank, 8 bank, x8 width) [7]                                         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Various address mapping schemes including cache line interleaving (bank and chan-      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| nel) and row interleaving                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

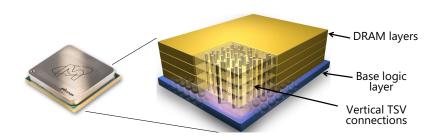

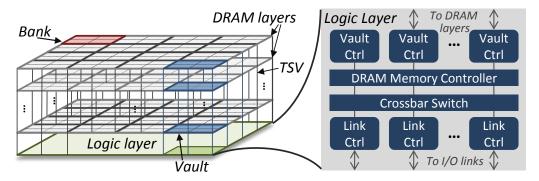

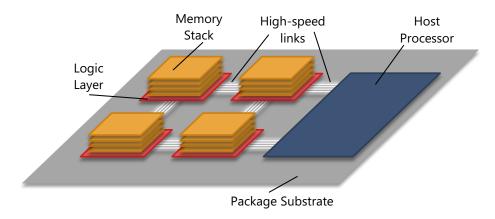

| Micron's hybrid memory cube (HMC). Reprinted from [94]                                 | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Overview of a HMC-like 3D-stacked DRAM [94]                                            | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

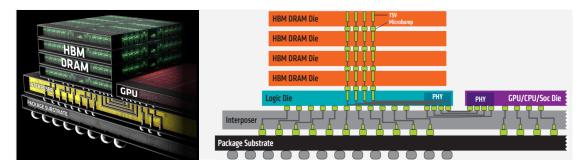

| AMD's high bandwidth memory (HBM). Reprinted from [1]                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

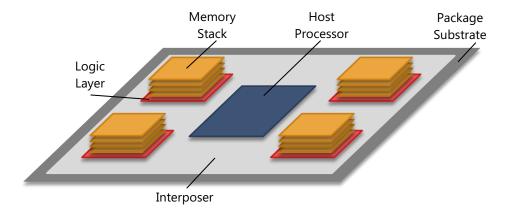

| System architecture using silicon interposer based connection                          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| System architecture using point-to-point SerDes based link connection                  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

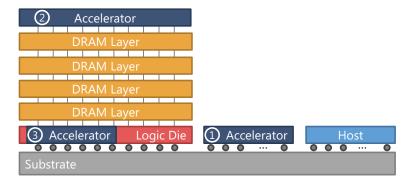

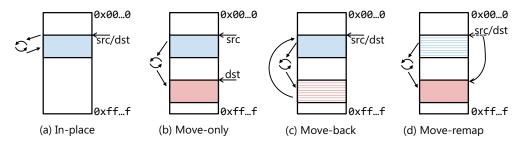

| Accelerator integration to a 3D-stacked DRAM: (1) Off-stack, (2) stacked as a sep-     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| arate layer, (3) integrated in the logic layer                                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

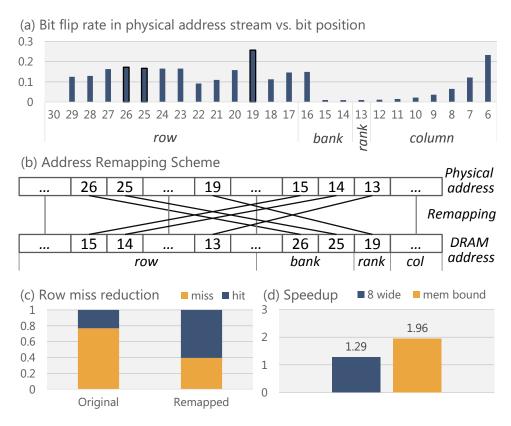

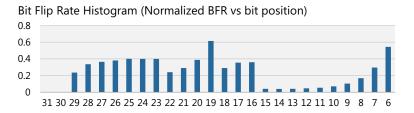

| (a) Normalized bit flip rate in the physical address stream, (b) simple address remap- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| ping scheme and (c) row buffer miss rate reduction via the address remapping and       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| (d) the resulting performance improvements for 8-wide and infinite compute power       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| systems for facesim from PARSEC                                                        | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

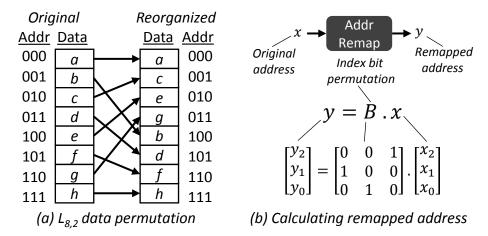

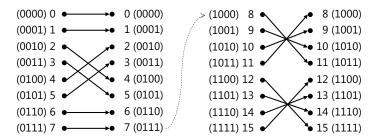

| An example data reorganization $(L_{8,2})$ on 8 elements and the corresponding address |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| remapping scheme                                                                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Dataflow representation of $(L_{4,2} \otimes I_2) \oplus (I_2 \otimes J_4)$            | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                                                                        | Overview of an off-chip planar DRAM module organization.  Locality/parallelism vs. bandwidth, power and energy tradeoffs for DDR3-1600 DRAM (1.5V, single rank, 8 bank, x8 width) [7].  Various address mapping schemes including cache line interleaving (bank and channel) and row interleaving.  Micron's hybrid memory cube (HMC). Reprinted from [94].  Overview of a HMC-like 3D-stacked DRAM [94].  AMD's high bandwidth memory (HBM). Reprinted from [1].  System architecture using silicon interposer based connection.  System architecture using point-to-point SerDes based link connection.  Accelerator integration to a 3D-stacked DRAM: (1) Off-stack, (2) stacked as a separate layer, (3) integrated in the logic layer.  (a) Normalized bit flip rate in the physical address stream, (b) simple address remapping scheme and (c) row buffer miss rate reduction via the address remapping scheme for facesim from PARSEC.  An example data reorganization (L <sub>8,2</sub> ) on 8 elements and the corresponding address remapping scheme. |  |

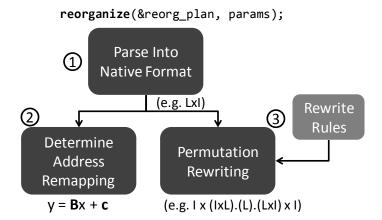

| 3.3  | Overview the mathematical framework toolchain                                           | 48 |

|------|-----------------------------------------------------------------------------------------|----|

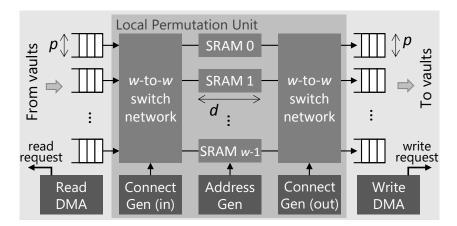

| 4.1  | Data reorganization unit (DRU).                                                         | 50 |

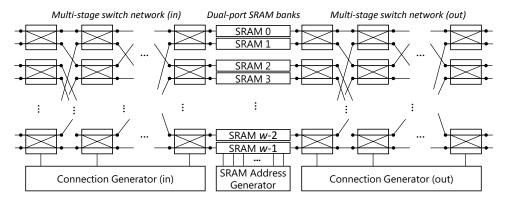

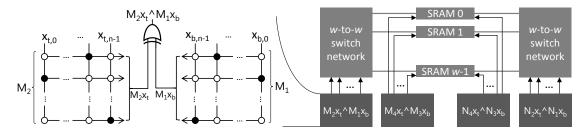

| 4.2  | Overview of the reconfigurable permutation memory                                       | 53 |

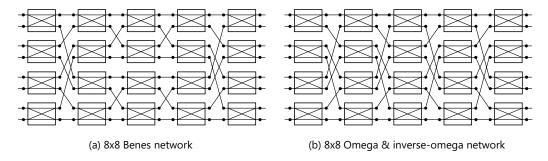

| 4.3  | Two examples for 8x8 rearrangeably non-blocking multi-stage switch networks             | 54 |

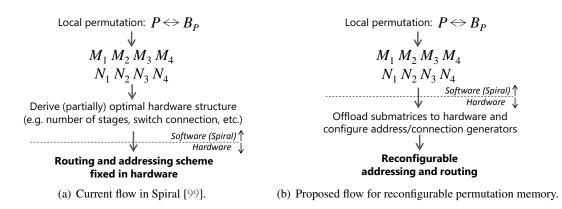

| 4.4  | Permutation memory compilation flow.                                                    | 55 |

| 4.5  | Detailed view of the SRAM address and connection generator units                        | 56 |

| 4.6  | DRAM address generator in a w-wide DMA unit                                             | 57 |

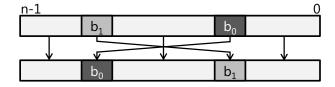

| 4.7  | Bit permutation of an example data reorganization                                       | 57 |

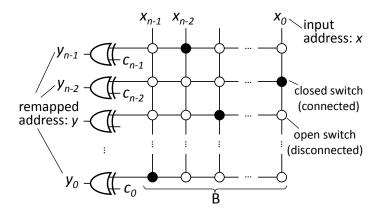

| 4.8  | Bit shuffle unit (BSU)                                                                  | 60 |

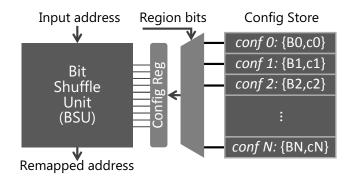

| 4.9  | Address remapping unit (ARU) supporting multiple address mappings for different         |    |

|      | memory regions.                                                                         | 61 |

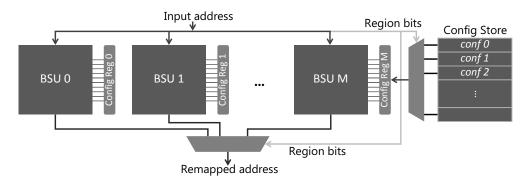

| 4.10 | ARU with multiple BSUs                                                                  | 61 |

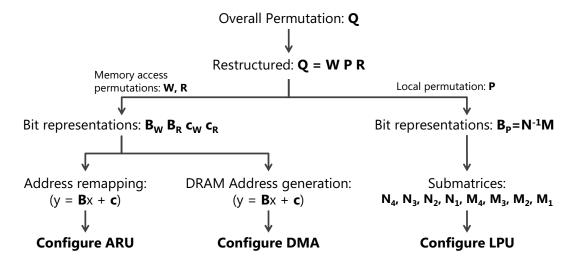

| 4.11 | From permutation specification to HAMLeT configuration                                  | 62 |

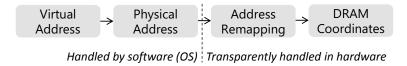

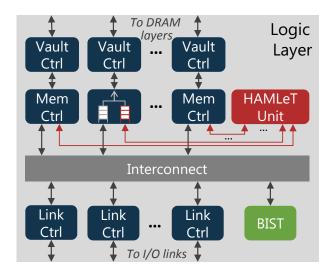

| 5.1  | Virtual address to DRAM coordinates (i.e. channel, bank, row, etc.) translation stages. | 67 |

| 5.2  | In-place and out-of-place data reorganization schemes                                   | 69 |

|      |                                                                                         |    |

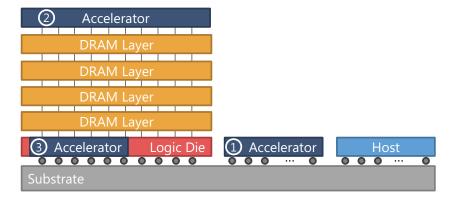

| 6.1  | Accelerator integration options to a 3D-stacked DRAM based system for near-data         |    |

|      | processing: (1) Off-stack, (2) stacked as a separate layer, (3) integrated in the logic |    |

|      | layer                                                                                   | 76 |

| 6.2  | Logic layer architecture for integrating HAMLeT into the 3D-stacked DRAM                | 79 |

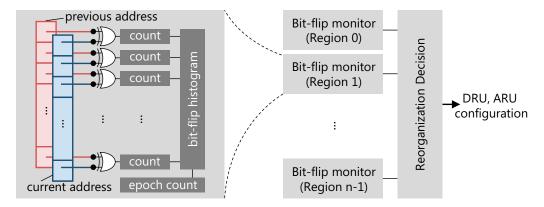

| 6.3  | Physical address bit-flip rate (BFR) monitoring unit for multiple memory regions        | 80 |

| 6.4  | An example bit-flip histogram of a memory access stream (facesim from PARSEC            |    |

|      | [32])                                                                                   | 81 |

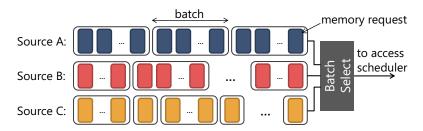

| 6.5  | Overview of the request batching with three sources                                     | 85 |

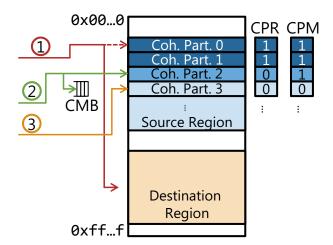

| 6.6  | Handling the host memory accesses in the multi-stage reorganization scheme              | 88 |

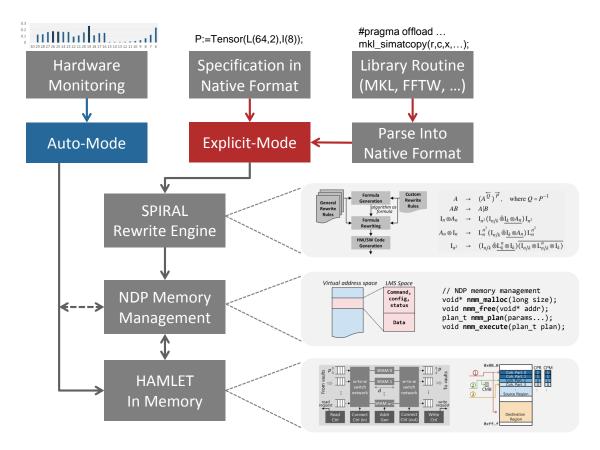

| 6.7  | Overall view of the fundamental use cases: From specification to in-memory reor-        |    |

|      | ganization                                                                              | 93 |

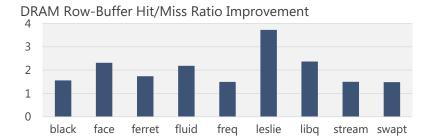

| 7.1  | Row buffer miss rate reduction via physical address remapping with data reorgani-   |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | zation                                                                              | 99  |

| 7.2  | Performance and energy improvements via physical address remapping with data        |     |

|      | reorganization.                                                                     | 100 |

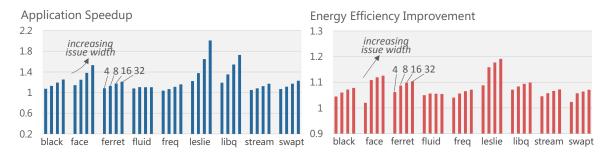

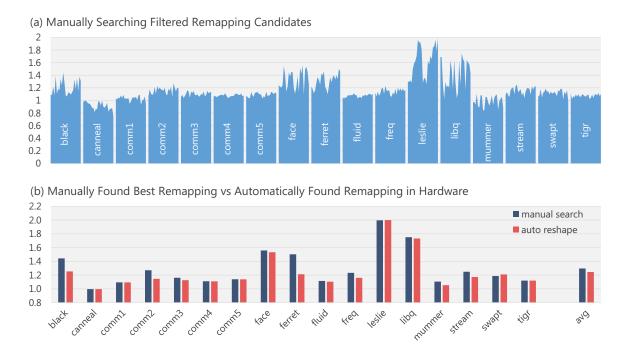

| 7.3  | Improvements with address remappings where only a single bit pair is swapped        | 101 |

| 7.4  | Comparing the best address remapping schemes that are manually searched and         |     |

|      | determined by hardware monitoring                                                   | 102 |

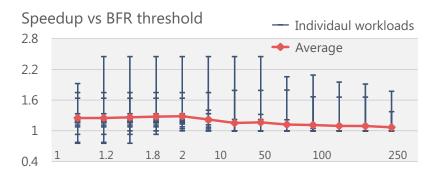

| 7.5  | Selecting an efficient BFR ratio threshold                                          | 103 |

| 7.6  | Selecting an efficient epoch length                                                 | 104 |

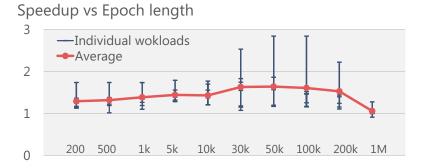

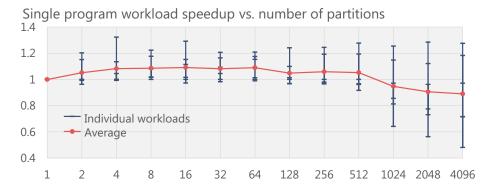

| 7.7  | Effect of number of memory partitions (1 to 4096) to the speedup for single program |     |

|      | workloads. (Normalized to no partitioning)                                          | 105 |

| 7.8  | Selecting an efficient partitioning scheme                                          | 106 |

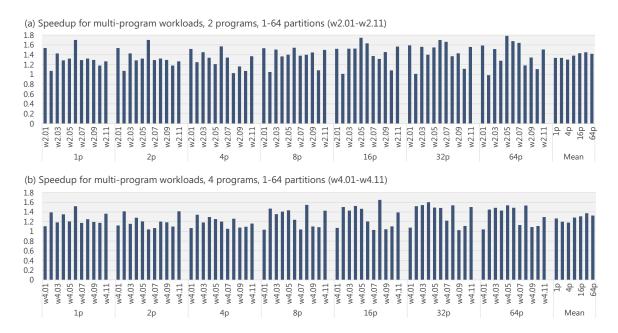

| 7.9  | Multi-programmed workloads with partitioned memory space                            | 108 |

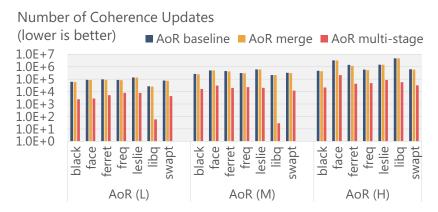

| 7.10 | Improvements in the number of in-memory coherence updates via merging and           |     |

|      | multi-stage reorganization schemes for different host priority levels               | 109 |

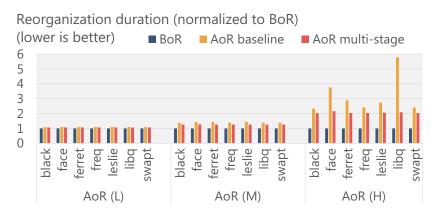

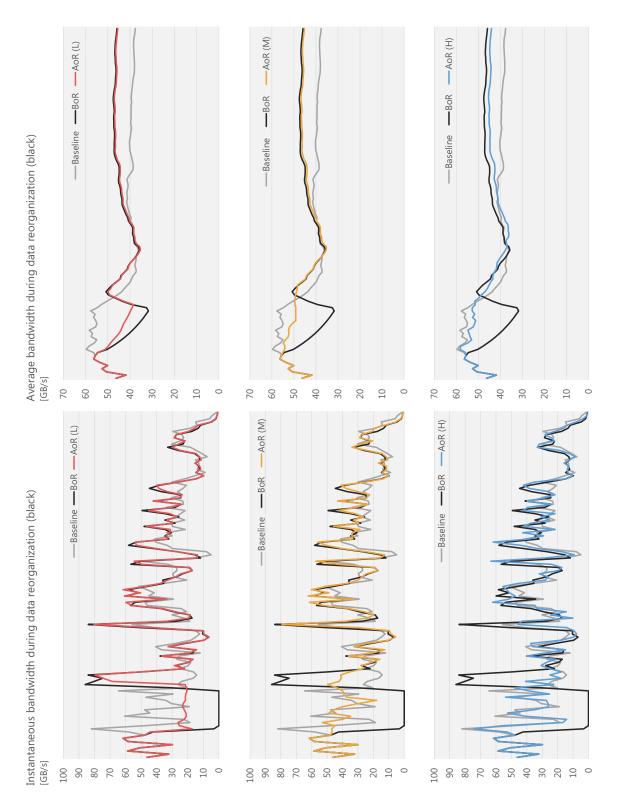

| 7.11 | Reorganization duration comparison for BoR and AoR. Both baseline AoR and           |     |

|      | multi-stage reorganization mechanisms are provided                                  | 110 |

| 7.12 | Instantaneous and average bandwidth utilization during baseline, BoR and AoR        |     |

|      | (low, medium and high host priority) for blackscholes                               | 112 |

| 7.13 | Instantaneous and average bandwidth utilization during baseline, BoR and AoR        |     |

|      | (low, medium and high host priority) for facesim                                    | 113 |

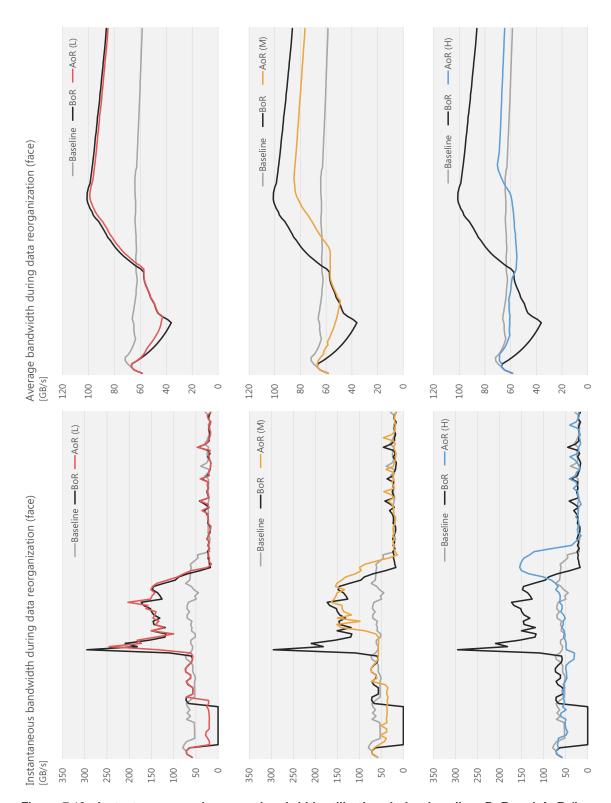

| 7.14 | Maximum slowdown during reorganization, and the overall speedup for BoR and         |     |

|      | AoR mechanisms.                                                                     | 114 |

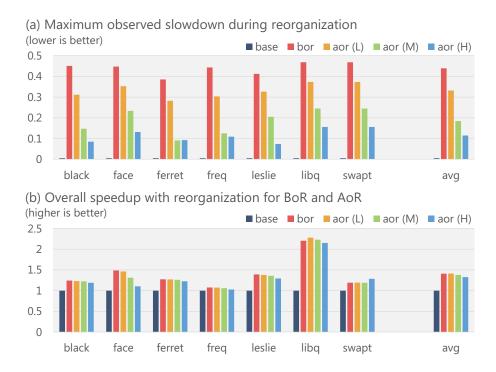

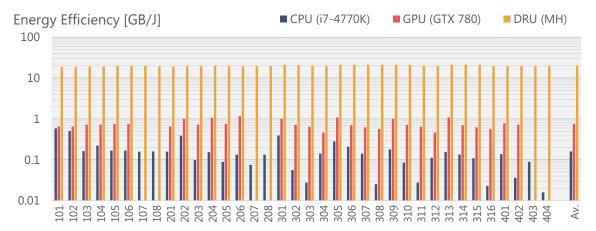

| 7.15 | Performance of the 3D-stacked DRAM based DRU (HAMLeT) is compared to op-            |     |

|      | timized implementations on CPU and GPU                                              | 117 |

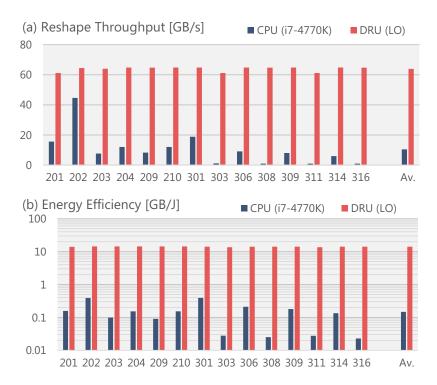

| 7.16 | Energy efficiency of the 3D-stacked DRAM based is DRU (HAMLeT) compared to          |     |

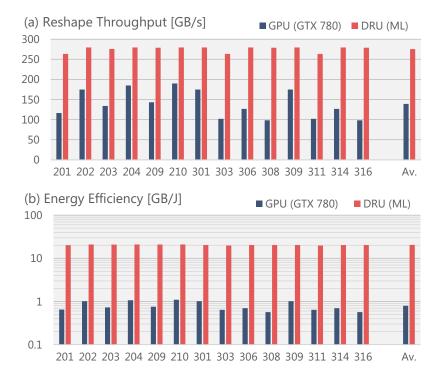

|      | optimized implementations on CPU and GPU                                            | 117 |

| 7.17 | DRU (HAMLeT) in LO configuration is compared to the CPU                             | 118 |

| 7.18 | DRU (HAMLeT) in ML configuration is compared to the GPU                              | 118 |  |

|------|--------------------------------------------------------------------------------------|-----|--|

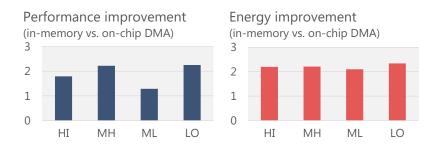

| 7.19 | .19 Comparison between the accelerator in-memory and on-chip as a memory controller  |     |  |

|      | based DMA                                                                            | 120 |  |

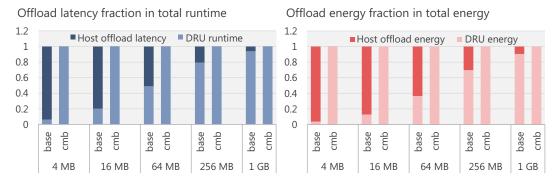

| 7.20 | Offload latency and energy fraction in the overall operation for baseline and coher- |     |  |

|      | ence optimized (using CMB) cases                                                     | 121 |  |

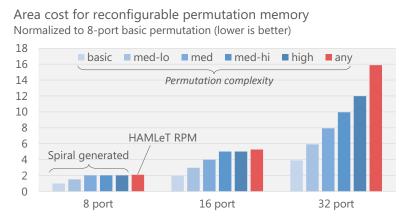

| 7.21 | Switch network and connection control hardware complexity for Spiral generated       |     |  |

|      | and reconfigurable permutation memory                                                | 123 |  |

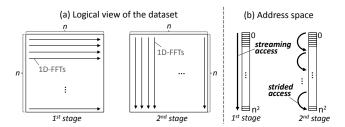

| 8.1  | Overview of row-column 2D-FFT computation in (8.3)                                   | 128 |  |

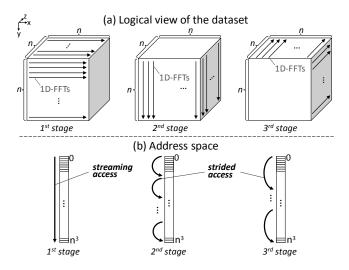

| 8.2  | Overview of 3D-decomposed 3D-FFT computation in (8.4)                                | 128 |  |

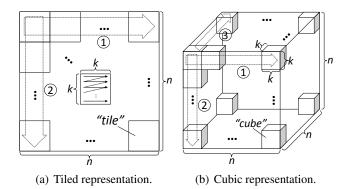

| 8.3  | Logical view of the dataset for tiled and cubic representation                       | 130 |  |

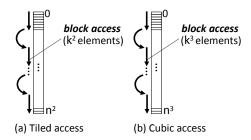

| 8.4  | Block accesses are demonstrated in address space                                     | 130 |  |

| 8.5  | Overview of the design generator tool                                                | 137 |  |

| 8.6  | Overall view of the targeted architecture                                            | 138 |  |

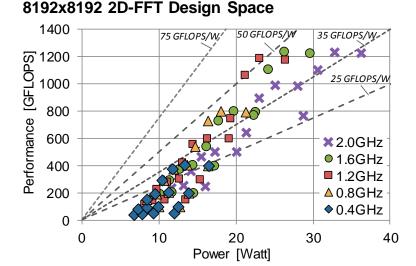

| 8.7  | Design space exploration for 2D-FFT with 3D-stacked DRAM. Isolines represent         |     |  |

|      | the constant power efficiency in Gflops/W (see labels)                               | 143 |  |

| 8.8  | Effect of tile size on performance and power efficiency for off-chip and 3D-stacked  |     |  |

|      | DRAM systems. (Rest of the parameters are fixed.)                                    | 144 |  |

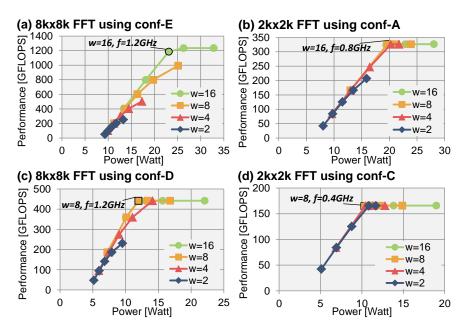

| 8.9  | Frequency (f) and streaming width (w) effects on power and performance for various   |     |  |

|      | problem/platform configurations (fixed tile size). Parameter combinations for the    |     |  |

|      | best design (GFLOPS/W) are labelled                                                  | 145 |  |

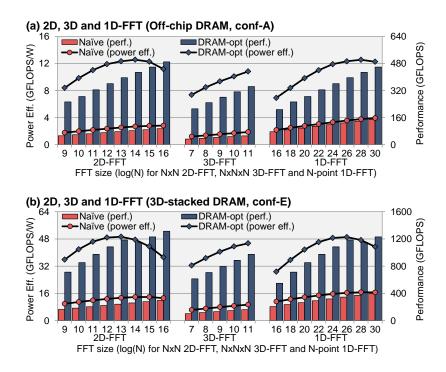

| 8.10 | Overall system performance and power efficiency comparison between naive and         |     |  |

|      | DRAM-optimized implementations for 1D, 2D and 3D FFTs using memory config-           |     |  |

|      | urations conf-A and conf-D respectively                                              | 147 |  |

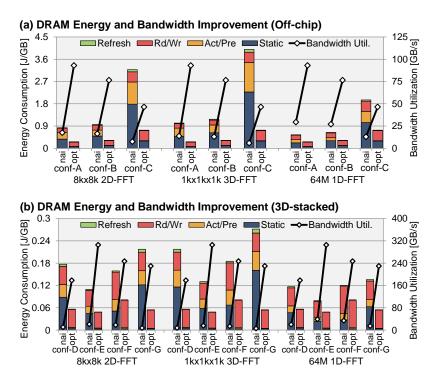

| 8.11 | DRAM energy and bandwidth utilization for naive (nai) and DRAM-optimized (opt)       |     |  |

|      | implementations of selected FFTs and memory configurations                           | 148 |  |

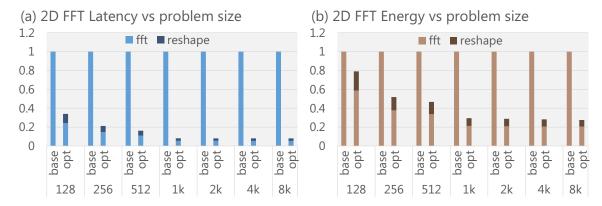

| 8.12 | Overall latency and DRAM energy improvement with data reorganization for 2D          |     |  |

|      | FFT using HAMLeT in the logic layer                                                  | 150 |  |

| 8.13 | Overall latency and DRAM energy improvement with data reorganization for 3D |     |  |

|------|-----------------------------------------------------------------------------|-----|--|

|      | FFT using HAMLeT in the logic layer                                         | 150 |  |

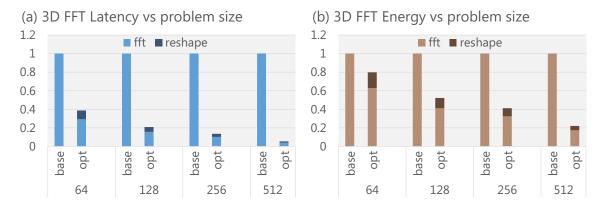

| 10.1 | Graph traversal progress in breadth first search                            | 160 |  |

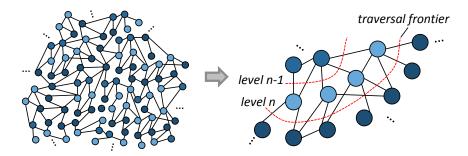

| 10.2 | Architectural overview of the traversal engine                              | 161 |  |

## **List of Tables**

| 2.1 | Comparison of 3D-stacked DRAM systems Wide IO2, HBM, HMC                                     | 17  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 3.1 | Summary of the address remapping rules                                                       | 40  |

| 3.2 | Basic formula identities                                                                     | 41  |

| 3.3 | Key permutation rewrite rules                                                                | 41  |

| 4.1 | Original and remapped locations for the bit permutation given in Figure 4.7                  | 58  |

| 6.1 | Algorithm for determining the BSU configuration and coherence update for the host            |     |

|     | memory accesses in the multi-stage reorganization scheme                                     | 89  |

| 7.1 | 3D-stacked DRAM low level energy breakdown                                                   | 96  |

| 7.2 | 3D-stacked DRAM configurations                                                               | 97  |

| 7.3 | Processor configuration                                                                      | 99  |

| 7.4 | Multi-programmed workloads                                                                   | 107 |

| 7.5 | Benchmark summary.                                                                           | 116 |

| 7.6 | HAMLeT power consumption overhead. HDL synthesis at 32nm                                     | 124 |

| 8.1 | Tiled mapping rewrite rules                                                                  | 133 |

| 8.2 | Cubic mapping rules. $R_j$ refers to the right hand side of $(j)$                            | 134 |

| 8.3 | Tiled 2D-FFT algorithm derivation steps. ( $R_9$ and $R_{10}$ are given in (9)-(10) in Table |     |

|     | 8.1.)                                                                                        | 134 |

| 8.4 | Tiled 1D-FFT algorithm derivation steps. ( $R_9$ and $R_{10}$ are given in (9)-(10) in Table   |     |

|-----|------------------------------------------------------------------------------------------------|-----|

|     | 8.1.)                                                                                          | 134 |

| 8.5 | Cubic 3D-FFT algorithm derivation steps. ( $R_{14}$ - $R_{16}$ are given in (14)-(16) in Table |     |

|     | 8.2.)                                                                                          | 135 |

| 8.6 | Performance results from Altera DE4. (GF = GFLOPS, TP = Theoretical peak)                      | 141 |

| 8.7 | Main memory configurations                                                                     | 146 |

### Chapter 1

## Introduction

#### 1.1 Motivation

Transistors continue to shrink in size with every new generation following the Moore's law, which suggests doubling the number of transistors on chip every 18 months. However, transistor threshold and supply voltages have not been scaling proportionally in the post Dennard era [43]. Future processing platforms are heading towards an energy constrained era, where parts of the chip, known as the dark silicon, are under-clocked or completely turned off to meet the power consumption limitations.

In addition to the stringent on-chip energy constraints, scaling trends for the DRAM technology and off-chip pin count do not match the transistor scaling trends, pointing towards the memory wall problem. This problem is exacerbated in the dark silicon era by multiple cores and on-chip accelerators sharing the main memory and demanding for more bandwidth. Memory bandwidth becomes a limiting factor to supply data for increasing number of on-chip compute units. Furthermore, memory energy consumption is another limiter for future processing platforms. Currently a 64-byte cache line size DRAM memory access consumes around 20–35 nJ (70 pJ/bit for DDR3, 40 pJ/bit for LPDDR2) which is orders of magnitude more energy than an on-chip double-precision

2 1.1. Motivation

fused multiply-add operation (50 pJ in 40nm) or a 64-byte on-chip SRAM access (110 pJ for 8 KB SRAM in 40nm) [56, 69, 77]. From a technology scaling standpoint, the DRAM memory system is a fundamental limiting factor both in terms of energy and bandwidth for future parallel processing platforms.

Moreover, with the emergence of the big data era, data intensive workloads require intensive memory usage. Limited data reuse, disorganized data placement, and inefficient access patterns in such workloads put a substantial pressure on the memory system. Due to large working sets and limited locality, these workloads require large roundtrip data movement between the processor and DRAM. It is reported that current systems spend significant energy and time on data movement. Specifically, for scientific, mobile and general-purpose workloads 28–40%, 35% and more than 50% of the total system energy is spent on data movement respectively [70, 91]. Although there are various disruptive memory technology developments such as 3D-stacked DRAM or wide I/O, promised energy and bandwidth potentials can only be achieved with the efficient use of the memory system.

Exploiting the memory level locality and parallelism is the key for efficiently utilizing the DRAM based main memories. There exists architectural mechanisms that aim to recover the lost parallelism and locality through reordering memory accesses by scheduling [101], distributing accesses by interleaving [118], or data prefetching to hide the memory latency [27]. These approaches are mainly limited with the size of reorder queues and none of them addresses the data placement problem. Compiler based code transformations, on the other hand, are limited with data dependencies lacking dynamic runtime information [42, 80, 112]. Data layout transformation via reorganizing data in memory aims the inefficient memory access pattern and the disorganized data placement issues at their origin. However, modern processing platforms lack the ability to perform efficient data layout transformations mainly due to roundtrip data movements and bookkeeping costs for remappings.

Moreover, the complex hierarchy of the memory is abstracted as a flat address space in the modern programming models. Low level memory system details including data layout, address mapping, and memory access behavior are not exposed to the users. Hence, programmers spend significant

manual effort to optimize the algorithmic behavior of the application for an improved memory access performance. Often times these algorithmic optimizations are specific to the platform's abstracted away memory hierarchy and architectural details, lacking portability.

Therefore, given the landscape for the future processing platforms, memory system should be a first class design consideration to achieve high performance and energy efficiency.

#### 1.2 Thesis Approach and Contributions

To achieve the desired first class design consideration of the memory system as a part of the high-performance and energy-efficient processing platforms, this thesis combines a formal abstraction framework and hardware/software mechanisms for optimizing the memory access. It focuses particularly on the following goals:

- A formal framework to represent and manipulate critical memory access optimizations through data layout, access pattern or address mapping transformations.

- An efficient hardware substrate that allows implementing formally represented optimizations such as changing the data layout and address mapping schemes, which are either fixed or very difficult to change dynamically in conventional processing platforms.

- Architectural/software mechanisms that utilize the developed hardware substrate to perform

the memory access optimizations either explicitly as a part of the application, or transparently

to improve the memory system performance.

- An algorithm/architecture co-design capability which enables co-optimizing computation flow, memory access and data layout where the memory system is exposed to the algorithm design space through the formal framework.

To achieve these high-level goals, this thesis makes the following main contributions:

A Formal Approach to Memory Access Optimization. From a mathematical standpoint, this thesis makes the key observation that manipulating the memory access patterns, data organization as well as address mapping schemes can be abstracted as permutations. The thesis demonstrates a formal framework based on tensor (Kronecker product) algebra that allows structured manipulation of permutations represented as matrices. This formal framework serves as a mathematical language to express the memory access optimizations as set of rewrite rules. This allows integration of these rules into an existing formula rewrite system called Spiral which enables automation [98]. Hence various implementation alternatives can be derived automatically to exploit the locality and parallelism potentials in memory.

HAMLeT Architecture for Data Reorganization. This thesis presents the HAMLeT (Hardware Accelerated Memory Layout Transform) architecture with the goal of highly-concurrent, low-overhead and energy-efficient data reorganization performed in memory. HAMLeT architecture is driven by implications and requirements from the permutation based mathematical framework. Parallel architecture with multiple SRAM blocks connected via switch networks performs high throughput local permutations. A configurable address remapping unit implements the derived affine index transformations for data reorganizations, which allows handling the address remapping completely in hardware. Memory access optimizations derived by the formal framework are directly mapped onto the HAMLeT architecture.

HAMLeT architecture is specifically tuned for near-data processing implementation using 3D-stacked DRAM. Integrated within 3D-stacked DRAM, behind the conventional interface, it not only minimizes the roundtrip data transfer but also utilizes high-bandwidth through-silicon via (TSV) based access and abundant parallelism provided by multiple layers/vaults/banks. Parallel streaming architecture can extract high throughput via simple modifications to the logic layer, keeping the DRAM layers unchanged. Overall, HAMLeT provides an efficient substrate for highly-concurrent, low-overhead and energy-efficient data reorganization performed in memory.

Software-transparent Data Reorganization. Taking the HAMLeT architecture as a substrate that enables very efficient data reorganizations, we demonstrate a software-transparent data reorganization performed in runtime. In this operation, the memory controller determines a disorganized data placement by monitoring the physical address stream. It uses HAMLeT to change the data layout and the address mapping. Reorganized data layout leads to better utilization of memory locality and parallelism, which improves the host processor performance. This thesis demonstrates series of hardware/software mechanisms to perform these operations, and their side effects, efficiently in memory.

**Explicit Data Layout Transformation.** As another fundamental use case, this work focuses on offloading and accelerating common data reorganization routines observed in high-performance computing libraries (e.g., matrix transpose, scatter/gather, permutation, pack/unpack, etc.) using the HAMLeT architecture. This gives the ability to efficiently perform data layout and address mapping transformations from the software, exposing these critical memory optimizations to the programmers. Furthermore, the thesis demonstrates special software/hardware mechanisms to handle the offloading and coherence management efficiently for the targeted near-data processing architecture.

Block Data Layout FFTs: Co-optimization of Computation, Memory Access and Data Layout. For certain types of problems, the separation of the computation and memory access is very difficult due to the interdependent nature of the two. This thesis also analyzes such a problem, fast Fourier transform (FFT), where the high-performance and energy-efficient implementations require a co-optimization between computation, memory access and data layout. Using the tensor based formal framework as a unifying representation, compute data flows, memory access patterns and data layouts are co-optimized as a part of the algorithm design space, where the customized block data layouts and their address remapping are achieved by utilizing the HAMLeT architecture.

#### 1.3 Thesis Organization

The rest of this dissertation is organized as follows.

First, Chapter 2 gives the background on the fundamental concepts that the thesis builds upon. It introduces the modern memory system organization, operation and various DRAM technologies including planar and stacked DRAMs. It further introduces the near-data processing (NDP) systems then elaborates on 3D-stacked DRAM based NDP alternatives. Furthermore, it gives a background on data reorganization operation and its capabilities.

Next, Chapter 3 presents the mathematical framework used to describe and manipulate critical memory system optimizations, most importantly data reorganization and address remapping. It demonstrates various test cases that manipulate permutations for transforming data layouts, access patterns and address mappings.

Then, Chapter 4 introduces the HAMLeT architecture for efficient data reorganization and address remapping in memory. It demonstrates the micro-architecture of the fundamental components in the HAMLeT, namely data reorganization unit (DRU) and address remapping unit (ARU).

Chapter 5 demonstrates two fundamental use cases for the highly-concurrent, energy-efficient and low-overhead data reorganization performed in memory. It describes the software-transparent and explicit operations. It also poses the critical architectural and software support required for these modes of operations.

Next, Chapter 6 presents the system architecture and integration. It first presents the near-data processing architecture exploiting the 3D-stacked DRAM technology. Then, focuses on host/HAMLeT integration issues such as parallel host and HAMLeT memory accesses, in-memory coherence management, and software offload mechanisms for explicit operation.

Chapter 7 provides an experimental evaluation for the fundamental use cases of the 3D-stacked DRAM based implementation of the HAMLeT architecture. It provides the modeling and simulation details for the 3D-stacked DRAM based architecture. Then it demonstrates detailed analysis for

improvements and overheads of the data reorganization for both explicit and transparent operation. The evaluations are concluded by hardware synthesis results to analyze power and area cost of the fundamental components of the HAMLeT architecture.

Then, Chapter 8 demonstrates a case where the critical details of the memory system optimizations are considered as a part of the algorithmic optimizations. Specifically, it presents a co-optimization of computation, memory access and data layout through block data layout FFT implementations which exploits the dynamic data layout operation.

Finally, following the related work in Chapter 9, Chapter 10 offers conclusions and future directions.

## Chapter 2

## **Background**

#### 2.1 The Main Memory System

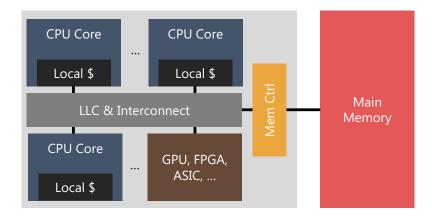

The main memory is becoming increasingly critical bottleneck in achieving high performance and energy efficiency for various computing platforms. This problem, also known as the memory wall, is further exacerbated in the dark silicon era by multiple cores and on-chip accelerators (such as GPU, FPGA, ASIC cores) sharing the main memory and demanding more memory bandwidth. A single chip heterogeneous multicore computing system is demonstrated in Figure 2.1. Even though, emerging technologies including 3D-stacked DRAM address the main memory bottleneck by providing more bandwidth while consuming less energy, in practice, the offered high performance and energy efficiency potentials is only achievable via the efficient use of the main memory. In this section, a detailed description about the fundamental operation of the DRAM based main memory systems is followed by the 3D-stacked DRAM technology.

#### 2.1.1 DRAM Organization and Operation

DRAM is a dynamic random access memory which has been adopted as the main memory in almost all of the computing platforms ranging from mobile, desktop, graphics processors up to supercom-

Figure 2.1: A single chip heterogeneous multicore computing system.

puters. DRAM memory cell has a very simple structure—a single transistor connected to a capacitor forms a single bit storage. This allows DRAM to achieve very high density. However, DRAM is a volatile memory so the contents of the memory cells leak over time. They have to be refreshed periodically to keep the stored values.

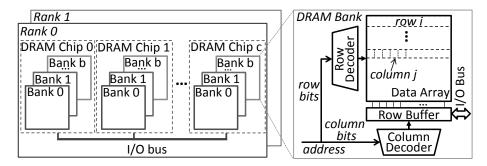

As shown in Figure 2.2, DRAM modules are divided hierarchically into (from top to bottom): ranks, chips, banks, rows, and columns. Each rank is constructed out of multiple DRAM chips. DRAM chips within a rank contributes to a portion of the DRAM word; they are accessed parallel in lock-step to form a whole memory word. Each bank within a DRAM chip has a *row buffer* which is a fast buffer holding the most recently accessed row (or page) in the bank. If the accessed bank and row pair are already active, i.e. the referenced row is already in the row buffer, then a *row buffer hit* occurs reducing the access latency considerably. In this case only the CAS (column address strobe) command is sent to access a column out of the active row. On the other hand, when a different row in the active bank is accessed, a *row buffer miss* occurs. In this case, the DRAM array is *precharged* and the newly referenced row is *activated* in the row buffer, increasing the access latency and energy consumption. Furthermore, when the accessed row buffer is not active then the DRAM array stays precharged which is called a *closed row*. An access to such bank still requires the activate command before the target row can be accessed. Therefore, to minimize the energy consumption and to achieve the maximum bandwidth from DRAM, one must minimize the row buffer misses. In other words, one must reference all the data from each opened row before switching to another row by

Figure 2.2: Overview of an off-chip planar DRAM module organization.

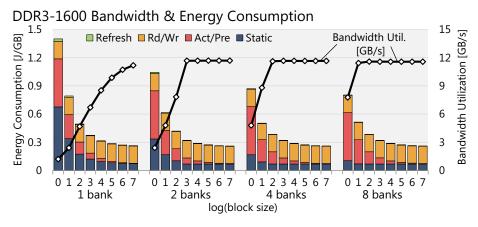

Figure 2.3: Locality/parallelism vs. bandwidth, power and energy tradeoffs for DDR3-1600 DRAM (1.5V, single rank, 8 bank, x8 width) [7].

exploiting the spatial locality in the row buffer.

In addition to the row buffer locality (RBL), bank level parallelism (BLP) has a significant impact on the DRAM bandwidth and energy utilization. Given that different banks can operate independently, one can overlap the latencies of the row precharge and activate operations with the data transfer on different banks. BLP enables high bandwidth utilization even if the RBL is not fully utilized provided that the accesses are well distributed among banks. However, frequently precharging and activating rows in different banks increase the power and total energy consumed.

Figure 2.3 demonstrates the impact of RBL/BLP on DRAM bandwidth, power and energy consumption. In this experiment contiguous blocks of data are transferred from DRAM, where adjacent blocks are perfectly distributed among different banks. Therefore, the size of the data block corresponds to the number of elements referenced from an opened row. In Figure 2.3 we observe that the

achieved bandwidth increases with RBL (i.e. size of the data blocks) and/or BLP (i.e. number of banks to which the data blocks are distributed). If the BLP is limited (e.g. accesses are concentrated on a single bank), then RBL must be maximized to reach the maximum bandwidth. On the other hand, if the blocks are well distributed among banks, the maximum bandwidth can be reached with smaller block sizes, but with the cost of additional bank precharge/activate operations. Figure 2.3 also shows the energy consumption in Joules/GByte which corresponds to the total energy spent in transferring unit GB of data. Both BLP and RBL decrease total static energy by transferring the same amount of data faster, yet RBL is the key to reduce the total activate/precharge energy.

Access Scheduling. DRAM memory controllers implement access scheduling to maximize the system throughput by exploiting RBL and BLP. Considering the latency disparity of different commands in the DRAM and the capability of handling multiple requests concurrently, memory access scheduling can improve the overall performance by reordering the requests. Prioritizing the row-hit requests, i.e. first-ready first-come-first-served (FR-FCFS) [101], batch scheduling [86] or stall-time fair scheduling [87] are among widely adopted scheduling mechanisms. A limitation of the memory access scheduling to optimize for the system throughput is the limited size request queues of the memory controller. Reordering capability in the memory controller is limited with the total number of on-the-fly requests in the scheduling queues. Access scheduling does not address the inefficient memory access issue at its origin. It only helps to reclaim some of the lost parallelism/locality by reordering requests in a limited window.

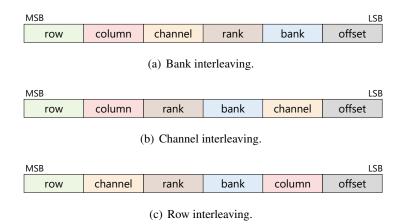

**Address Mapping.** As described previously, DRAM memory modules consist of several hierarchical units such as channels, ranks, banks, rows and columns. Hence a particular location in the DRAM memory system is described by these *coordinates*. However, the main memory is abstracted with a flattened linear address space. The memory controller implements an address mapping scheme that maps this linear physical address space into the DRAM coordinates. In other words, the address mapping determines the DRAM coordinates, i.e. channel, rank, bank, row, column, of a memory accesses. Address mapping scheme determines how physically contiguous data,

Figure 2.4: Various address mapping schemes including cache line interleaving (bank and channel) and row interleaving.

from the processors abstraction, are actually laid out in the DRAM. Hence, it is an important factor in determining the DRAM parallelism and locality utilization.

Most widely used address mapping policies include row (page) and cache line interleaving schemes. Row interleaving scheme interleave consecutive cache lines first into a row from a bank, then interleave the rows among banks and channels. Whereas, cache line interleaving scheme places consecutive cache lines into consecutive banks, ranks or channels. Example address mapping schemes bank interleaving, channel interleaving and row interleaving are shown in Figure 2.4(a), Figure 2.4(b) and Figure 2.4(c) respectively. Row interleaving is optimized for locality hoping that sequential accesses exhibit spatial locality where sequential locations in the address space are mapped to the same row. Hence an application that exhibits spatial locality can enjoy row buffer hits, improving the memory access performance. On the other hand, cache line interleaving is optimized for parallelism where consecutive locations in the address space are scattered to different banks aiming to increase the bank level parallelism. There are various hybrid approaches and sophisticated address mapping techniques, such as permutation based interleaving [118], that aim to exploit the memory parallelism and locality better. Moreover, application-specific efficient address mapping schemes can be determined via profiling.

Figure 2.5: Micron's hybrid memory cube (HMC). Reprinted from [94].

Figure 2.6: Overview of a HMC-like 3D-stacked DRAM [94].

#### 2.1.2 3D-stacked DRAM Technology

3D-stacked IC is a broad term covering systems where multiple dies and/or wafers are stacked vertically. In the 3D-stacked DRAM technology, multiple DRAM dies and/or logic die(s) are stacked on top of each other and connected by vertical through silicon vias (TSV). TSVs allow connection through the wafer or die substrate where the active layer of the die can communicate vertically. Multiple such dies are connected using micro-bumps. By sidestepping the I/O pin count limitations, dense TSV connections allow high bandwidth and low latency communication within the stack. There are examples of 3D-stacked DRAM technology both from industry such as Micron Hybrid Memory Cube (HMC) [94], JEDEC standard High Bandwidth Memory (HBM) [16], Tezzaron Di-RAM [11], and from academia [49, 71].

**Hybrid Memory Cube (HMC).** Figure 2.5 shows the overview of the Hybrid Memory Cube (HMC). HMC features multiple DRAM dies and a base logic die which implements control units as well as high-speed serial communication interfaces as shown in Figure 2.6.

It consists of multiple layers of DRAM (currently 4 to 8 DRAM layers are planned) where each layer also has multiple banks. A vertical slice of stacked banks (or groups of two banks) form a structure called *vault*. HMC 2.0 features 32 vaults. Each vault has its own independent TSV bus and vault controller [65]. This enables each vault to operate in parallel similar to independent channel operation in conventional DRAM based memory systems. We will refer to this operation as *inter vault parallelism*.

Moreover, the TSV bus has very low latency that is much smaller than the typical tCCD (column to column delay) values [38, 111]. This allows time sharing the TSV bus among the layers via careful scheduling of the requests which enables parallel operation within the vault (e.g. [120]). We will refer to this operation as *intra vault parallelism*.

HMC is not a JEDEC standard. Instead of the conventional DDR standard, it has a serial communication interface. Serializer/deserializer (SerDes) units in the logic layer used to interface to off-stack, implementing a packet-based network communication. Despite its complexity, this interface allows direct short-reach links eliminating the need for silicon interposer. Currently 10, 12.5 and 15 Gb/s data rate lanes are planned where each link features 16 lanes and logic layer implements 4 to 8 links. 15 Gb/s lane configuration with 8 links can reach up to 480 GB/s aggregate off-stack bandwidth.

HMC can achieve very high energy-efficiency as well compared to conventional DRAM modules. It is reported that the overall energy efficiency is 10.48 pj/bit including DRAM access, TSV transfer and SerDes based I/O [65]. 6.78 pj/bit accounts for the logic layer which combines the SerDes and controller units. This is a significant improvement when compared to 70 pj/bit energy efficiency of the DDR3 and 18-22 pj/bit energy efficiency of the GDDR5 [65, 89].

Furthermore, the base logic layer implements memory/vault controllers that schedule the DRAM commands while obeying the timing/energy constraints. This allows less complex memory controller on the host side. Data switching between vaults and I/O links is achieved by a crossbar interconnect. Typically, these native control units do not fully occupy the logic layer and leave a real estate that could be taken up by custom logic blocks [65]. However, the thermal and power

Figure 2.7: AMD's high bandwidth memory (HBM). Reprinted from [1].

constraints limit the complexity of the custom logic.

**High Bandwidth Memory (HBM).** As shown in Figure 2.7, High Bandwidth Memory (HBM) integrates multiple DRAM dies and an optional logic die by using TSVs and micro-bumps. Dense TSV connections at the base layer are directly connected to the host processor, as opposed to the HMC system. This connection is implemented through a silicon interposer substrate. HBM is a standardized interface adopted by JEDEC [16].