# OPTIMIZING IC TESTING FOR DIAGNOSABILITY, EFFECTIVENESS AND EFFICIENCY

Cheng Xue

#### A DISSERTATION

submitted to the Department of Electrical and Computer Engineering of Carnegie Mellon University in partial fulfillment of the requirement for the degree of

**DOCTOR OF PHILOSOPHY**

Pittsburgh, PA Feb 2016 Copyright © Feb 2016

Cheng Xue

All rights reserved

# Acknowledgement

First of all, I would like to thank my academic advisor, Prof. Shawn Blanton. I came to Carnegie Mellon University as a master student with no background in chip testing and very few research experience. Prof. Blanton spent much of his precious time teaching me everything from scratch and helped me switch to the doctoral program I always dreamed for. Thanks to his constant support, I overcame many difficulties and gradually become more confident and self-oriented. His detailed feedback to my writings and presentation is beneficial not only to my research work but also to my future career. I also learned a lot from his meticulous attitude toward research planning and conducting.

I would like to thank other members in my doctoral committee. Prof. Xin Li helped me decide the mathematical model used in the defect level prediction work, and also suggested multiple ways to better present the experiment results of the test reordering work. Prof. Andrzej Strojwas helped me view how each work in my thesis can be used in production testing under different yield or production volume conditions. Dr. Anne Gattiker helped me find a way to connect each work in my thesis together as a contribution to test development. Dr. Xiaochun Yu helped me define the optimization goal for the test reordering work, and recommended multiple improvements for the delay fault model evaluation work.

Special thanks to Brion Keller from Cadence. Throughout my doctoral program he provided constant support by answering my questions regarding to the commercial ATPG tool developed by Cadence. The delay fault model evaluation and defect level prediction work cannot be finished in a timely manner without his help. I would also like to thank other people from industry – Rao Desineni, John Carulli, Enamul Amyeen, Bruce Cory, Phil Nigh, Ken Butler, Darrel Carder and Matt Grady – for answering a survey related to the test reordering work.

Another special thanks to Yen-tzu Lin, who kindly teach me the basics of ATPG tools, script language and many useful tricks in linux. I would like to thank other former and current ACTL members

including Jason Tam, Matthew Beckler, Osei Poku, John Porche, Mike Wang, Ben Niewenhuis, Zeye Liu, Jaime Kang, Yang Xue for their various help to my research and life. I also need to thank Shupeng Sun and Fa Wang from Prof. Xin Li's group for answering many questions from me about algorithms and machine learning.

This thesis work is supported by National Science Foundation, Semiconductor Research Corporation and Information and Communication Technologies Institute – CMU/Portugal. I appreciate the financial support from all the sponsors.

Finally, I need to thank my parents for financially supporting me to come to Carnegie Mellon as a master student. Their priceless love always accompanies me along this long journey.

### **Abstract**

Chip testing is an important step of integrated circuits ("chip") manufacturing. It involves applying tests to each manufactured chip using expensive testers (automatic test equipment) to identify and reject bad (malfunctioning) chips. Various types of manufacturing defects (shorts, disconnects, missing vias, etc.) can occur during fabrication and cause a chip to malfunction. Testing not only needs to verify every gate, cell, interconnect, etc. are operational as expected, but also needs to help identify and analyze existing manufacturing defects so that improvements in fabrication, design and even test can be made in a timely manner.

The cost of developing high-quality tests is being driven up by the increasing complexity of defect behaviors. New processing technologies introduce new types of defects, some of which only occur in certain circuit/layout configurations. It is no longer possible to detect all types of defects using only conventional stuck-at tests. More sophisticated fault models and test metrics have been developed to guide the test development toward better defect detection, but they also require a significantly larger volume of tests to achieve acceptable coverage. Test engineers need to reduce test volume in order to save test cost (i.e., achieving high test *efficiency*), and at the same time prevent most bad chips from escaping test (i.e., achieving high test *effectiveness*). The ability to diagnose a failing chip precisely and accurately (*diagnosability*) also depends on the tests applied. This important characteristic of test is often downplayed in production testing, but could be very important during yield ramp-up for quickly discovering major yield-loss contributors. In this dissertation, four new methods are developed to improve the state of the art for test development, either in terms of diagnosability, test effectiveness or test efficiency. These methods can be used in conjunction, or individually for achieving a specific prioritized, goal in test development.

First, a test-reordering method is developed to improve the diagnosability of production tests. To our knowledge, this is the first-ever work that examine the impact of test order on logic diagnosis. Due to

constraints such as limited test time or tester memory, a commonly-used practice during production testing is to only record the first few failing tests or pins for a failing chip. This recording of an incomplete tester response adversely affects the outcome of diagnosis because less information is provided for diagnosis. The proposed test-reordering method tries to find an optimal test ordering that can better distinguish stuck-at faults when recorded tester response is incomplete. Since the set of candidate defect sites is typically obtained based on stuck-at faults, faults that are distinguished from each other are unlikely to become the candidate defect site at the same time, which leads to better outcome for diagnosis.

Second, a fault-model evaluation method (DELAY-METER) is developed to improve test effectiveness. Various delay fault models are proposed in previous work to capture defects that escape slow-speed testing, but which models should be used to guide the generation of tests for at-speed testing remain an open question. The conventional method is to evaluate fault-model effectiveness using test experiments involving actual fabricated chips, in other words, tests are developed using various fault models and applied to a population of chips to determine which tests are best at detecting defects. Alternatively, DELAY-METER evaluates the effectiveness of delay fault models using readily-available fail data from production testing, so that an optimal mix of delay fault models can be chosen for at-speed testing.

Third, a defect-level prediction model (the DDP model) is developed to balance test effectiveness and test efficiency. Defect level (DL) represents the fraction of defective chips among all chips that pass tests. However DL is difficult to measure directly and be able to predict during test development is of critical importance. Conventional DL prediction models become insufficient when tests are generated from multiple fault models. The DDP model learns the defect detection probability (DDP) of multiple fault models from diagnosis, and combines it with the coverages of multiple fault models to provide a more accurate prediction. The more accurate prediction of DL by the DDP model thus enables a better trade-off analysis between test effectiveness and test efficiency.

Finally, a test-selection method is developed to improve test efficiency. Test time reduction (TTR) is a focus of research in test development to save test cost and improve test efficiency. One method for TTR involves identifying a subset of tests from a large baseline test set. Test selection can be performed based on actual tester data measured from tested chips, or data taken from the simulation of the circuit design that has

faults/defects injected. Previous work that uses simulation for test selection are only applied to archaic benchmark circuits that are too small to be meaningful. A one-pass test-selection method is developed in this dissertation that identifies a subset of tests that maximize fault-model coverage while requiring relatively limited CPU time and memory.

To demonstrate the practical utility of the four methods developed in this dissertation, several real designs from industry are used in various experiment. Specifically, an ASIC and GPU designs and test data taken from a large population of actual fabricated chips are used to experiment the proposed test-reordering method and test-selection method. Experiments results demonstrate the improvement in diagnosability and test efficiency, respectively. The same ASIC design and test data is not only used by DELAY-METER to evaluate the effectiveness of different delay fault models, but also used by the DDP model as both a training data for building a DL-prediction model, and a verification data for verifying the prediction accuracy.

# **Contents**

| Acknowledgement                                                        | I   |

|------------------------------------------------------------------------|-----|

| Abstract                                                               | III |

| Contents                                                               | VI  |

| List of Tables                                                         | IX  |

| List of Figures                                                        | XI  |

| Chapter 1 Introduction                                                 | 1   |

| 1.1 Test Reordering for Improving Diagnosability                       | 4   |

| 1.2 Delay Fault Model Evaluation for Improving Effectiveness           | 6   |

| 1.3 Defect Level Prediction for Balancing Effectiveness and Efficiency | 8   |

| 1.4 Test Selection for Improving Efficiency                            | 9   |

| 1.5 Dissertation Organization                                          | 11  |

| Chapter 2 Test Reordering for Improving Diagnosability                 | 12  |

| 2.1 Background                                                         | 12  |

| 2.2 Methodology                                                        | 14  |

| 2.2.1 Incomplete Tester Response                                       | 15  |

| 2.2.2 Intuition of Test Reordering                                     | 16  |

| 2.2.3 One-Pass Test-Reordering Flow                                    | 17  |

| 2.3 Experiments                                                        | 20  |

| 2.3.1 Setup                                                            | 21  |

| 2.3.2 IBM ASIC Experiment Result                                       | 22  |

| 2.3.2 NVIDIA GPU Experiment Result                                     | 27        |

|------------------------------------------------------------------------|-----------|

| 2.3.3 Discussion                                                       | 29        |

| 2.4 Summary                                                            | 30        |

| Chapter 3 Delay Fault Model Evaluation for Improving Effectiveness     | 31        |

| 3.1 Background                                                         | 31        |

| 3.2 DELAY-METER                                                        | 33        |

| 3.2.1 Tester Response Data Pre-processing                              | 34        |

| 3.2.2 Suspect Region Identification                                    | 35        |

| 3.2.3 Effective Fault Selection                                        | 35        |

| 3.2.4 Fault Model Evaluation                                           | 37        |

| 3.3 Experiment                                                         | 39        |

| 3.4 Discussion                                                         | 42        |

| 3.5 Summary                                                            | 43        |

| Chapter 4 Defect Level Prediction for Balancing Effectiveness and Effi | ciency 44 |

| 4.1 Background                                                         | 44        |

| 4.2 The DDP model                                                      | 46        |

| 4.2.1 Defect Detection Probability (DDP)                               | 46        |

| 4.2.2 Approximating Chip DDP                                           | 47        |

| 4.2.3 Approximating Chip-population DDP                                | 48        |

| 4.2.4 DL Prediction using a Single Fault Model                         | 49        |

| 4.2.5 DL Prediction using Multiple Fault Model                         | 51        |

| 4.3 Experiment                                                         | 53        |

| 4.3.1 Virtual Experiment                                               | 53        |

| 4.3.2 Silicon Experiment                          |  |

|---------------------------------------------------|--|

| 4.3.3 Comparison with Quadratic Programming       |  |

| 4.3.4 Discussion                                  |  |

| 4.4 Summary                                       |  |

| Chapter 5 Test Selection for Improving Efficiency |  |

| 5.1 Background                                    |  |

| 5.2 Methodology61                                 |  |

| 5.2.1 Test Selection for Maximizing Coverage      |  |

| 5.2.2 Maximum- <i>K</i> Coverage Problem          |  |

| 5.2.3 One-pass Test Selection                     |  |

| 5.3 Experiment                                    |  |

| 5.3.1 IBM ASIC Experiment                         |  |

| 5.3.2 NVIDIA GPU Experiment                       |  |

| 5.3.3 Comparison with LP and ILP                  |  |

| 5.3.4 Discussion                                  |  |

| 5.4 Summary                                       |  |

| Chapter 6 Conclusion and Future Work80            |  |

| 6.1 Dissertation Contribution80                   |  |

| 6.2 Future Work                                   |  |

| Dibliography:                                     |  |

# **List of Tables**

| Table 1: The average, median and maximum number of failing tests per chip recorded in the tester response                 |

|---------------------------------------------------------------------------------------------------------------------------|

| from six industrial designs aimed at various technology nodes                                                             |

| Table 2: A diagnosis example where $f_Y$ is the sole diagnosis candidate in (a) when full tester response is              |

| provided, but in (b) incomplete tester response causes all three faults $f_X$ , $f_Y$ and $f_Z$ to become diagnosis       |

| candidates17                                                                                                              |

| Table 3: A diagnosis example where $f_Y$ is the sole diagnosis candidate when either (a) full tester response or          |

| (b) incomplete tester response is provided, diagnostic resolution is no longer affected in this ordering17                |

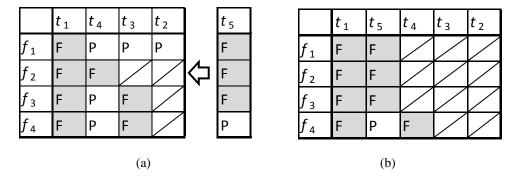

| Table 4: An example showing the change of fault simulation responses (a) before and (b) after a new test $t_5$            |

| is inserted into a test sequence $(t_1, t_4, t_3, t_2)$ , when $N = 2$ .                                                  |

| Table 5: Calculation of ADR for all possible points for $t_5$ ( $N=2$ ). The first two tests that detect each fault after |

| $t_5$ is inserted at each insertion point are listed. The last two insertion points have the lowest ADR and become        |

| the ideal insertion points                                                                                                |

| Table 6: Comparison of diagnostic resolution and diagnosis accuracy achieved from the original sequence                   |

| and the reordered sequence for the IBM virtual failing chip population                                                    |

| Table 7: Comparison of the number of chips with perfect diagnostic resolution and with accurate diagnosis                 |

| before and after reordering for IBM chips injected with a specific type of virtual defect (SSL, MSL, bridge               |

| or input-pattern)                                                                                                         |

| Table 8: Comparison of the number of chips with diagnostic resolution $\leq 5$ and with accurate diagnosis                |

| before and after reordering for IBM chips injected with a specific type of virtual defect (SSL, MSL, bridge               |

| or input-pattern)                                                                                                         |

| Table 9: Comparison of diagnostic resolution and diagnosis accuracy achieved from the original sequence                   |

| and the reordered sequence of tests for the NVIDIA failing chip population28                                              |

| Table 10: Comparing the fault simulation and tester responses for classifying effective and ineffective faults.           |

|                                                                                                                           |

| 37                                                                                                                        |

| Table 11: A summary of DELAY-METER application to several delay-fault models                                              |

| Γable 13: Comparison of the one-pass method with LP and ILP in terms of the number of detected stuck-at |  |

|---------------------------------------------------------------------------------------------------------|--|

| Faults, the CPU time and memory usage                                                                   |  |

# **List of Figures**

| Figure 1: Test optimization methods developed in this thesis (shaded) used in a test development flow 3             |

|---------------------------------------------------------------------------------------------------------------------|

| Figure 2: The flow diagram of the one-pass test-reordering method.                                                  |

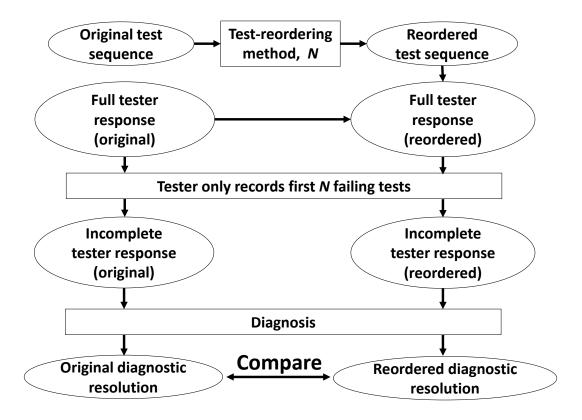

| Figure 3: Experiment flow diagram comparing the diagnostic resolution achieved using the original sequence          |

| and the reordered sequence of tests.                                                                                |

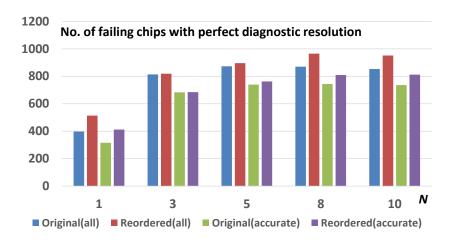

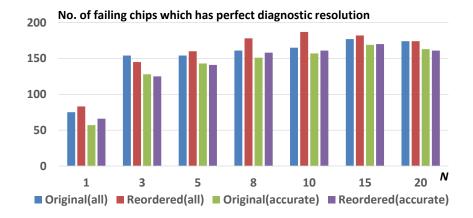

| Figure 4: Comparison of the number of failing chips with perfect resolution (all) and also with accurate            |

| diagnosis (accurate) between the original sequence and the reordered sequence for the IBM virtual failing           |

| chip population                                                                                                     |

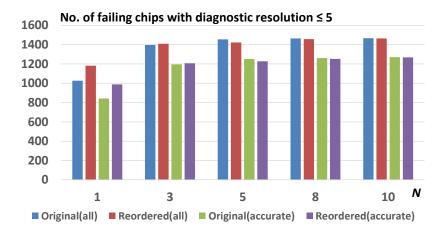

| Figure 5: Comparison of the number of failing chips with diagnostic resolution ≤ 5 (all) and also with accurate     |

| diagnosis (accurate) between the original sequence and the reordered sequence for the IBM virtual failing           |

| chip population                                                                                                     |

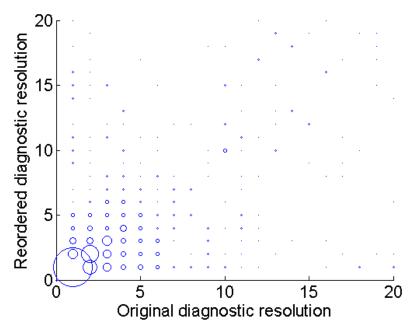

| Figure 6: Scatter plot comparing the diagnostic resolution of the original sequence (X axis) and the reordered      |

| sequence (Y axis) for each IBM virtual failing chip when $N = 10$ . The size of a circle represents the number      |

| of failing chips with a specific pair of X-Y values for original-reordered diagnostic resolutions25                 |

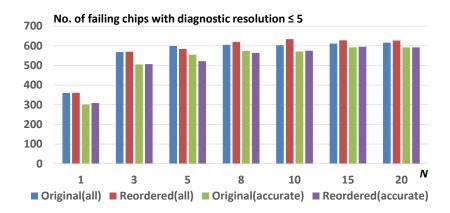

| Figure 7: Comparison of the number of failing chips with perfect resolution (all) and also with accurate            |

| diagnosis (accurate) between the original sequence and the reordered sequence of tests for the NVIDIA               |

| failing chip population                                                                                             |

| Figure 8: Comparison of the number of failing chips with diagnostic resolution ≤ 5 (all) and also with accurate     |

| diagnosis (accurate) between the original sequence and the reordered sequence for the NVIDIA failing chip           |

| population                                                                                                          |

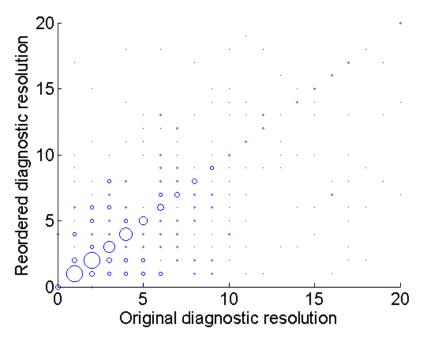

| Figure 9: Scatter plot comparing the diagnostic resolution of the original sequence (X axis) and the reordered      |

| sequence (Y axis) for each NVIDIA failing chip with both resolution $\leq$ 20, when $N = 10$ . The size of a circle |

| represents the number of failing chips with a specific pair of X-Y values for two diagnostic resolutions29          |

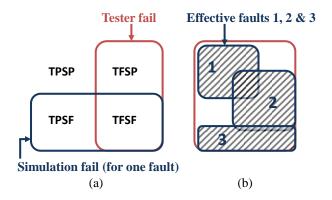

| Figure 10: Comparison between the tester response and the simulation result for (a) one fault and (b) three         |

| effective faults                                                                                                    |

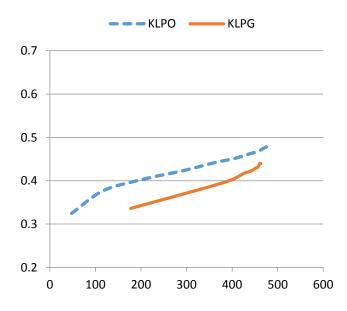

| Figure 11: Average Effectives for KLPC and KLPC as a function of number of paths selected                           |

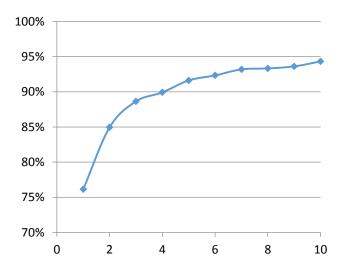

| Figure 12: Percentage of the 703 chips that have effectiveness $> 0$ for the N-detect TDF metric41                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------|

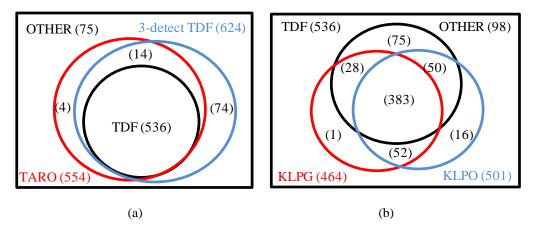

| Figure 13: Venn diagrams showing the number of chips with effectiveness greater than zero for (a) TDF, 3-                                      |

| detect TDF and TARO, and (b) TDF, KLPG and KLPO42                                                                                              |

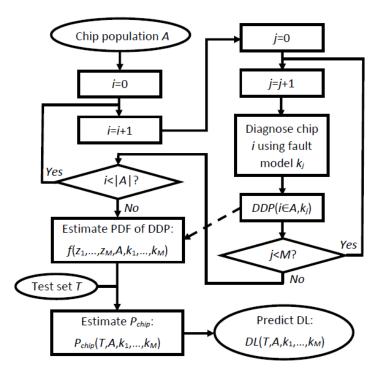

| Figure 14: The flow diagram for predicting DL for test set $T$ , using chip population $A$ and $M$ fault models                                |

| $\{k_1,\ldots,k_M\}.$                                                                                                                          |

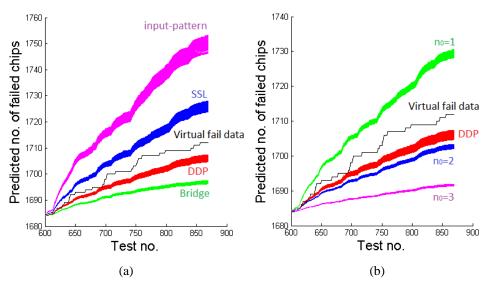

| Figure 15: The cumulative number of detected defective chips at each test predicted by (a) the DDP model                                       |

| and the W&B model, (b) the DDP model and the S&A model. The actual number of detected defective chips                                          |

| counted from the virtual fail data is also plotted. The spread for prediction results from an assumed yield that                               |

| range from 0.7 to 0.99                                                                                                                         |

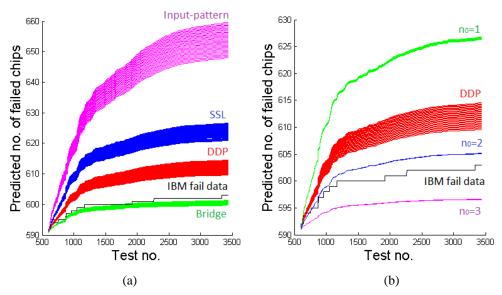

| Figure 16: The cumulative number of detected defective chips at each test predicted by (a) the DDP model                                       |

| and the W&B model, (b) the DDP model and the S&A model. The actual number of detected defective chips                                          |

| counted from the IBM fail data is also plotted. The spread for prediction results from an assumed yield that                                   |

| range from 0.7 to 0.99                                                                                                                         |

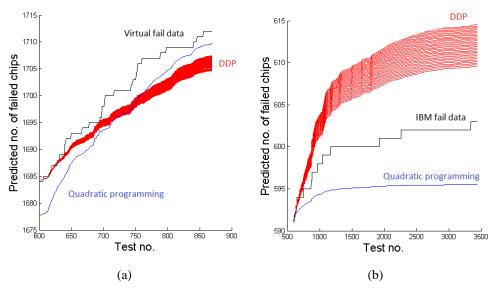

| Figure 17: The cumulative number of detected defective chips predicted by a best-fit 2nd-degree polynomial                                     |

| and the DDP model for the data of the virtual experiment (a) and the silicon experiment (b). The polynomial                                    |

| is learned from the training data by solving a quadratic-programming formulation. The spread for prediction                                    |

| of the DDP model results from an assumed yield that range from 0.7 to 0.99                                                                     |

| Figure 18: Flow describing how a limited number ( $\leq K$ ) of tests are selected from the baseline test set $T$ using                        |

| the one-pass method                                                                                                                            |

| Figure 19: The <i>Detection</i> array, the <i>NumFaults</i> hash table and the <i>SelectedTest</i> list when three tests $t_1$ , $t_2$ and     |

| t <sub>3</sub> are currently selected                                                                                                          |

| Figure 20: The one-pass method evaluates whether a new test $t_4$ should be inserted (a) after $t_1$ , and (b) after                           |

| $t_2$ . (c) Insertion after $t_2$ results in the updated <i>Detection</i> array, <i>NumFaults</i> hash table and the <i>SelectedTest</i> list. |

| 66                                                                                                                                             |

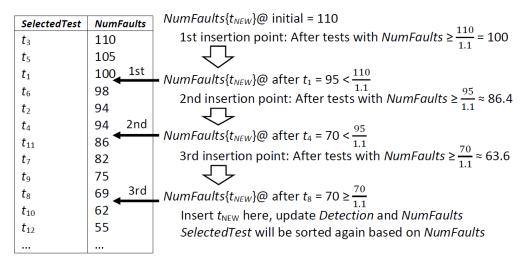

| Figure 21: The one-pass method finds the insertion points for a new test $t_{NEW}$ when $\beta=1.1$ . $t_{NEW}$ is inserted to                 |

| the <i>SelectedTest</i> list at the third insertion point                                                                                      |

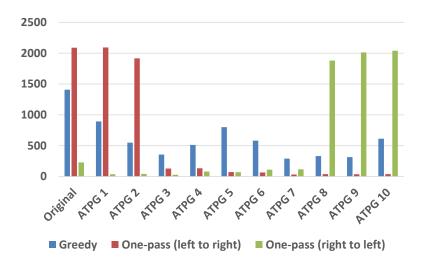

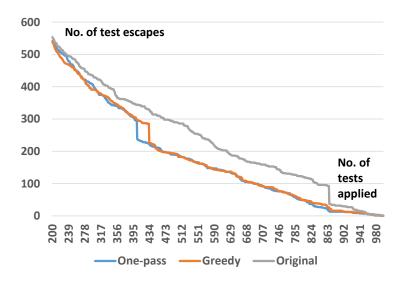

| Figure 22: The distribution of tests selected by the greedy algorithm and the one-pass method. Test sets are                                   |

| processed by the one-pass method in an order that is either from left to right or from right to left                                           |

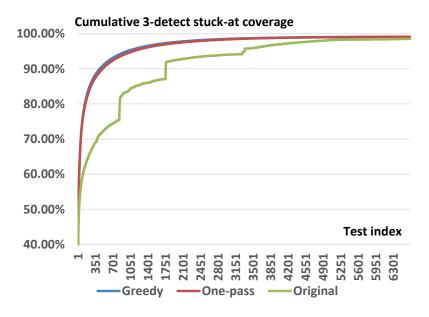

| Figure 23: The cumulative 3-detect stuck-at coverage achieved by the tests selected by the greedy algorithm,    |

|-----------------------------------------------------------------------------------------------------------------|

| by the one-pass method and the baseline test set (i.e., the original test set and the additional 10 ATPG runs). |

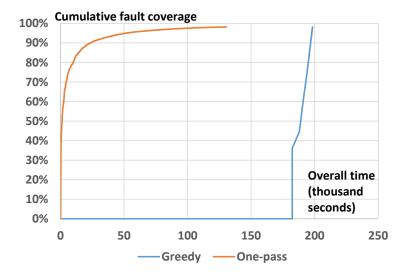

|                                                                                                                 |

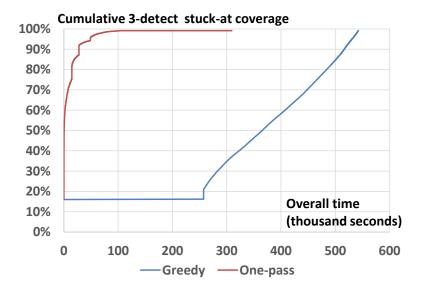

| Figure 24: The cumulative 3-detect stuck-at coverage of the tests selected by the greedy algorithm and the      |

| one-pass method as a function of the overall time                                                               |

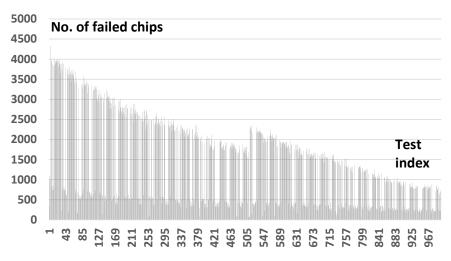

| Figure 25: The number of failed chips detected by each test                                                     |

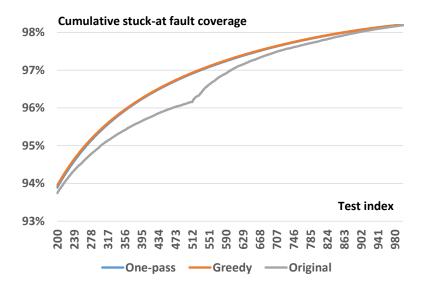

| Figure 26: The cumulative stuck-at fault coverage of tests selected by the one-pass method, by the greedy       |

| algorithm and the original test ordering                                                                        |

| Figure 27: The number of test escapes among the 12,127 failed chips when only a subset of selected tests is     |

| applied on the tester                                                                                           |

| Figure 28: The cumulative stuck-at coverage of the tests selected by the greedy algorithm and the one-pass      |

| method as a function of the overall time                                                                        |

# **Chapter 1 Introduction**

With continued scaling propelled by process-technology advancements, integrated circuits ("chips") can be manufactured with higher transistor density, which enables electronic devices to be made smaller, more capable, and require less power to operate. However, the increased complexity of a chip also drives up the cost of test development [1][2]. Chip testing is an important step of manufacturing especially when it involves applying tests to each fabricated chip using expensive testers (automatic test equipment) to identify and reject bad chips. Developing high-quality tests is crucial for chip manufacturers as it ensures the quality of shipped chips and prevents the additional cost of packaging, shipping and returning bad chips that escape. High-quality tests should not only reduce test cost without compromising the quality of shipped chips [Die-level], but also provide essential feedback for understanding the characteristics of manufactured chips [2].

The cost of developing high-quality tests is being driven up by the increasing complexity of defect behaviors. First, the uptick in design-process interaction leads to the prevalence of systematic defects, which occur due to certain circuit/layout configurations such as high pattern density, close pattern proximity, or particular layout geometries [2]. The complexity of systematic defects may lead to such a rarity of their occurrence that they may only be found after a sufficient number of chips are produced [3]. Second, increased process variability and circuit sensitivity cause defects that were once benign to become "killer defects" [2]. Experiment data shows that chips have become more and more sensitive to subtle defects, i.e., defects that only cause a small amount of additional delay compared to the clock-cycle time [4]. Finally, new processing technologies introduce new types of defects, such as various reliability issues related to TSVs (through-silicon vias) in 3D-integrated chips [5-7].

There is past work on generating high-quality tests that can be categorized into four major categories: diagnosability [21-25], test effectiveness [29-37], test efficiency [18-20] and test-yield loss [8-10]. Test yield loss refers to the good chips (i.e., chips that satisfy all specifications) that should have therefore

passed the testing process but instead have failed and are discarded due to some non-idealities in testing. Minimizing test-yield loss can reduce the overall manufacturing cost, but is not the focus of this dissertation. This dissertation instead presents new methods for use in test development that either improves diagnosability, test effectiveness or test efficiency. The new methods can be used in conjunction, or individually for achieving a specific, prioritized goal for a certain phase of test development.

Diagnosability reflects the capability to diagnose the exact point of failure within a chip that did not pass the testing process [11]. High diagnosability enables fast analysis of failing locations, behaviors and causes. Improvements in the manufacturing process, the design or even the testing process itself can then be made accordingly to improve the yield and/or the quality of the fabricated chips. Diagnosability is especially important for chips produced in state-of-the-art technologies, which can contain systematic and design dependent defects [12]. Production tests, those used during high-volume manufacturing, however are typically optimized for test efficiency (short test time) not for diagnosability [11]. Because the large number of chips that fail during high-volume production provide valuable information for yield learning and two new methods developed in this thesis work, the necessity of techniques that enhance the diagnosability of production tests becomes obvious.

Test is effective if it detects defects affecting chips. Higher effectiveness means more defects are detected during testing, which in turn prevents bad chips from escaping to customers. Reduced test escape ensures the quality of shipped chips and minimizes the additional cost of handling custom returns. Conventional test-escape prediction models [13-15] state that the probability of defect detection increases as fault coverage increases, in other words, tests that detect more faults have higher test effectiveness. However, as today's chip manufacturers typically employ many different types of tests (e.g., stuck-at tests, bridge tests, input-pattern tests, etc.), some defects are only detectable by certain test types while others are detectable with more than one test type [16]. For example, an open defect on an interconnect between library cells can be detected by stuck-at, bridge and input-pattern tests, while an open defect within a library cell may only be detectable by input-pattern tests. To find a combination of tests with the highest effectiveness, the test engineer has to determine (i) what type of test needs to employ, and (ii) what test coverage to achieve for

each type. These decisions are also subject to revision throughout the entire product cycle in response to changes in manufacturing processes, thus necessitating a model to provide guidelines.

Test efficiency is inversely proportional to the cost associated with testing. Test cost is typically determined by the volume of test data, since higher test-data volume requires increased tester time and memory [17]. By reducing test-data volume, test efficiency is improved and test cost is saved. However, test-data volume continues to grow as chip complexity increases, due to the fact that there are more defect mechanisms to consider and more devices to test [17]. Test efficiency can be improved by removing tests or selecting a subset of tests from the original test set. For example, a widely-used method for improving test efficiency is to fault-simulate tests in a reverse order and remove tests that do not detect any new faults. Silicon data also shows many tests do not uniquely detect defects, and thus can be discarded without any impact to test escape [18-20]. Therefore, there is potential for developing techniques that improve test efficiency without sacrificing test effectiveness.

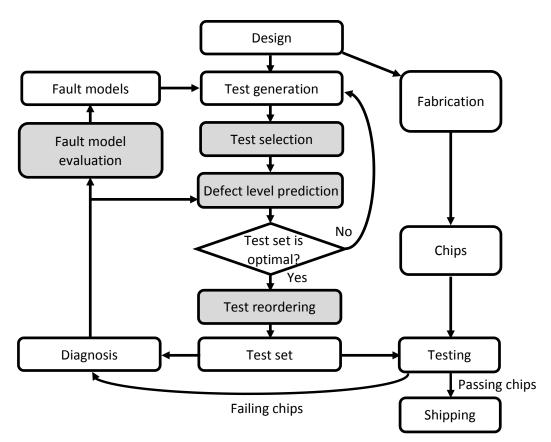

Figure 1: Test optimization methods developed in this thesis (shaded) used in a test development flow.

Figure 1 demonstrates how the four new methods developed in this thesis optimize test quality in a typical test development flow. The shaded bubbles represent steps where a newly-developed method is used. After a set of tests is generated using an ATPG (automatic test pattern generation) tool for a given circuit design based on some selected fault models, a test-selection work (Section 1.4 and Chapter 5) is developed to select a subset of tests with maximum test coverage to improve test efficiency. Then a defect level prediction work (Section 1.3 and Chapter 4) evaluates the test effectiveness of the selected tests by predicting defect level using test coverages from multiple models and diagnosis results of previously tested chips. Defect level prediction enables a trade-off analysis between test effectiveness and test efficiency. For example, test generation and selection may be retried multiple times with different settings until a test set with optimal effectiveness and efficiency is determined. Next a test reordering work (Section 1.1 and Chapter 2) finds an optimal test ordering that better distinguish fault behaviors in order to improve diagnosability. The reordered tests are applied to chips on a tester and the failing chips are sent to diagnosis. A fault model evaluation work (Section 1.2 and Chapter 3) is developed to find a mix of fault models with the highest test effectiveness using the diagnosis results for guiding test generation in the future. In the rest of this chapter, an overview is given for each of the four new methods developed in this thesis.

### 1.1 Test Reordering for Improving Diagnosability

Logic diagnosis is an important step for identifying the defect locations within failing chips. Precise identification of a defect location enables further analysis of the failure mechanisms using techniques like physical failure analysis (PFA), which provides important feedback for improving the fabrication process, the design and even test itself [21-22]. Compared with PFA, diagnosis is non-destructive and consumes less time and cost, thus can be performed on more failing chips. Diagnosis uses the tester response (fail logs collected from testers during the test of failing chips) as input data, and outputs one or more locations (wire, gate, etc.) typically called candidates, where defects are most likely located. Diagnostic resolution refers to the number of candidates associated with defect locations within a failing chip. Higher diagnostic resolution (few candidates) is desired because the success rate of PFA is inversely related to the number of possible defect locations. However, several issues make high-resolution diagnosis difficult to achieve. For one thing, the tests applied to each chip is just a fraction of all possible input combinations applicable to chip inputs,

thus inhibiting the full exploration of the behavior of a defect. In addition, not all failing tests and pins are recorded during production testing due to tester time or memory issues, both of which further reduces the amount of information provided for diagnosis.

Previous work on diagnostic ATPG, whose goal is to improve the diagnosability of production tests through the addition of tests that aim to distinguish fault locations [12][23-25]. In other words, the goal is to ensure that each fault has a unique simulation response, where the simulation response of a fault are to the tests and pins that fail when the fault is injected into the design and simulated using the tests as inputs. Although the final goal of diagnosis is to determine the site and nature of each defect, the set of candidate is typically obtained based on faults [12]. During a typical diagnosis flow, the simulation response of each fault within suspect sub-circuits are compared with the tester response, and faults whose simulation response best matches the tester response are reported as candidates. If many faults share the same simulation response and all match the tester response, they are all typically reported as diagnosis candidates, and the resulting resolution could be poor. Such an outcome can possibly be mitigated by adding extra tests that make the simulation response of each fault unique, so that some faults whose simulation response no longer match the tester response can be excluded from the candidate list.

Diagnosis using production tests is further complicated by the limited amount of response data collected by a tester. Due to limited test time or tester memory, a commonly-used practice during production testing is to only record the first few failing tests or pins of the tester response exhibited by a failing chip. When an incomplete tester response is used in diagnosis, the diagnosis tool can only use the tests up to and possibly including the last failing pattern. Diagnosis with an incomplete tester response intuitively degrades resolution, because fewer tests can be used distinguish faults.

Instead of adding tests to make faults distinguishable (i.e., diagnostic ATPG), this thesis proposes a new method that improves resolution through test reordering. The objective of this new method is to find a test ordering that makes more faults (SSL faults in particular) distinguishable from each other, under the assumption that a tester only records the first N failing tests for a failing chip. The intuition used in this test reordering approach is simply based on the fact that, because only the first N failing tests are used in diagnosis, tests that are better at distinguishing faults should be at the beginning of the reordered test sequence. The

reordering is accomplished using a one-pass flow to save CPU time and memory. Each test from the original test set is fault-simulated and inserted to an optimal location in the reordered test sequence one by one in a streaming fashion.

The diagnostic resolution improvement of the reordered test sequence is verified on two industrial designs, specifically, an IBM ASIC (10 million transistors) and an NVIDIA GPU (100 million transistors). Tester responses collected from the fault simulation results of 1,689 virtually injected defects and from the fail logs of 1,000 chips failed on testers are used as input data. For each failed chip, incomplete tester responses are generated for both the original test sequence and the reordered test sequence, by keeping only the tester responses of the first *N* tests while discarding the rest. Diagnosis is then performed using the incomplete tester responses to compare diagnostic resolution and accuracy between the original and the reordered test sequence. Experiment results show the number of failing chips with perfect diagnostic resolution is increased by 8.1% for IBM ASIC and 5.7% for NVIDIA GPU, while diagnosis accuracy is maintained.

### 1.2 Delay Fault Model Evaluation for Improving Effectiveness

As defect complexity increases, using only conventional stuck-at tests can lead to undesirable levels of escape [26]. To ensure test effectiveness, chip manufacturers typically employ many different types of tests. Each type of test is generated under the guidance of a fault model or a test metric, each of which is targeting the behavior of a certain type of defects. A fault model is simply an abstract of a defect type. Widely-used fault models include the single stuck-line (SSL) or stuck-at [1], bridge [27], transition-delay [28] and input-pattern [29] fault models. A test metric does not model a defect per se but instead specifies how tests should be generated for detecting defects. Examples of test metrics include N-detect [30], PAN-detect [31], KLPG [32] and TARO [33]. In this dissertation, test metric will not be distinguished from a fault model.

Identifying an optimal test set that achieves high effectiveness first requires one to select which fault models to employ for guiding test generation. There is no straightforward approach however for making this decision. Different designs and different fabrication processes may cause the occurrence of different types of defects, so the effectiveness of a fault model may vary. Effectiveness of a fault model equates to how well

tests generated under the guidance of the model can detect real defects. Tests generated from a fault model with higher effectiveness detect more defects and contribute to lower test escape. Accurate effectiveness evaluation allows test engineers to choose the proper mix of fault models for achieving a required quality level, instead of arbitrarily using tests from all possible fault models in some ad hoc fashion.

Conventionally, fault model effectiveness is measured through tester experiments involving real chips [4][34-36]. A tester experiment typically involves generating a separate set of tests for each fault model, followed by the application of each test set separately to a population of fabricated chips. The fault models are then typically evaluated and compared based on the number of failed chips detected by their corresponding tests sets. However tester experiments incur extra time and money and their results may not be accurate. The inaccuracy comes from the fact that most conventional tester experiments do not look into each failed chip and verify whether the defect behavior matches the faulty behavior predicted by the fault model. Some chips may be detected fortuitously but the fault model is still incorrectly credited with detection.

MEasuring Test Effectiveness Regionally (METER) [37] is an alternate, inexpensive approach to evaluate fault model effectiveness. METER only uses the fail logs collected from chips failed during production testing as input and evaluates fault models through diagnosis and fault simulation, so it does not need to rely on expensive tester experiments. Each failed chip is diagnosed to identify it suspect regions, i.e., regions that are believed to cause chip failures. Faults within suspect regions are simulated. A fault model is credited with high effectiveness if fault detection within suspect regions are correlated with defect detection. Compared with conventional tester experiments, METER provides a more thorough evaluation through diagnosis of each failed chip. However, the evaluation accuracy may be affected if diagnostic resolution is poor, but the approach is significantly better than conventional tester experiments.

This dissertation extends METER to the evaluation of several delay fault models (termed as DELAY-METER) used in at-speed testing, including TDF, N-detect TDF, TARO [33], KLPG [32] and KLPO (described in Chapter 3). Since certain types of defects (resistive open, resistive bridge, etc.) may escape tests that are applied at slow-speed (e.g., stuck-at tests), at-speed testing become mandatory in industry to maintain test quality [38]. DELAY-METER enables the evaluation of delay fault models even when the diagnostic resolution of delay defects is poor. DELAY-METER consists of four steps: (1) Tester response

data pre-processing; (2) Suspect-region identification; (3) Effective fault selection and (4) Fault model evaluation. The first step chooses the chips and tests that are suitable for evaluation. The second step identifies the suspect regions within each failed chip using a conservative diagnosis approach. The third step identifies effective faults within suspect regions whose detection is always accompanied with chip failure. The fourth and the final step evaluates the effectiveness of a fault model based on the simulation response of effective faults and the tester response of each failed chip. Experiment are performed using actual test data collected from an IBM ASIC. Effectiveness is measured and compared using all five delay fault models.

#### 1.3 Defect Level Prediction for Balancing Effectiveness and Efficiency

One important goal of test development is to strike a balance between test effectiveness and test efficiency. More specifically, to find a test set of small volume that achieves low test escape. Test escape is usually measured as defect level (DL), which represents the proportion of defective chips among all chips that pass testing. DL is usually expressed in units of DPPM (defective parts per million). Different products have different DL requirements, but test development follows similar scenarios: either minimize DL for a given constraint on test cost, or alternatively ensure that DL does not exceed some pre-determined threshold [39]. In either scenario, DL enables test engineers to estimate the return on investment for test generation effort in order to perform trade-off analysis [16]. However, DL is often hard to measure directly, and its exact number cannot be determined until all defective parts are returned by customers. One commonly-used solution is to build a model to predict DL based on the characteristics of the chip design and the tests applied that include, for example, yield and test coverage.

The most widely known DL-prediction models include the Williams & Brown [13] model and the Seth & Agrawal [14] model. Both models predict DL as a function of yield and fault coverage from a single fault model (in most cases, the SSL fault model). But both models become inadequent when tests are generated and combined from multiple fault models. For example, both models predict DL=0 when SSL fault coverage is 100%, which is not the case especially for modern fabrication technologies and chip designs. In other words, escape still occurs with 100% SSL fault coverage [26]. There is several recent work [15-16] however that take into account fault coverage from multiple models. But these approaches are either derived empirically, or weight each fault model equally.

In this work, we propose a new method (called the DDP model) that learns the defect detection probability (DDP) of fault models from the diagnostic results of failed chips, and predicts DL using both DDP and the coverage from multiple fault models. DDP is defined as the probability a defect is detected when all faults from a fault model are detected. Tester responses from failed chips are used as input data for the DDP model, and several widely-used fault models are chosen to predict DL. DDP is estimated for each chosen fault model and each failed chip in the input data through diagnosis and fault simulation. A probability density function (PDF) of DDP is then calculated using the estimated DDP of the chosen fault models and all failed chips. The learned PDF of DDP combined with yield can be used to predict DL of any given test set.

Virtual and actual chip experiments are conducted on an IBM ASIC design to verify the DL prediction accuracy of the DDP model. In each experiment, chips that fail before a "cutoff" test are used as training data to train a DL-prediction model. The trained model then predicts how many defective chips will be detected after the "cutoff" test. The prediction result is compared with the actual number of detected defective chips, and the prediction result of other DL-prediction models. Experiment results show the DDP model provides a more reliable prediction than conventional models.

### 1.4 Test Selection for Improving Efficiency

As chip manufacturers begin to use various sophisticated fault models to generate tests, the associated test cost also increases significantly. Many new fault models require a significantly larger number of tests to achieve acceptable coverage [36][40]. For example, a 6-detect SSL test set is more than three times larger than a conventional SSL test set [40]. Moreover, tests generated from multiple fault models are typically combined together, thus further exacerbating the issue with test-set size, since a larger test-set size leads to higher test cost. However it is observed that most defective chips can be made to fail with significantly fewer tests than the number typically applied [18][20]. If a subset of tests can be selected from a larger pool of tests while ensuring most defective chips are detected, test efficiency is improved without sacrificing test effectiveness. Solving this test-selection problem is the key objective of many published papers on test time reduction (TTR) [17][41-43] and adaptive testing [18-19][44].

Previous work on test-selection can be categorized into either silicon-based or simulation-based. Silicon-based test selection work [18][44] equates the number of failed chips detected by each test as effectiveness. Tests with low effectiveness are either eliminated or applied on a sample basis. Silicon-based test selection requires a large sample of tested chips as input data, which may not be available during the early stage of manufacturing. Simulation-based test selection work [41-43][45] calculates the effectiveness of each test from fault simulation, such as calculating N-detect coverage [45], or the defect-level contribution based on fault detection [43]. An optimal test set that achieves maximum effectiveness with a limited number of tests is selected using mathematical tools that solve linear programming (LP) or integer linear programming (ILP) formulations. However, previous simulation-based approaches are only applied to small benchmark circuits. Alternatively, when applied to large industrial circuits with larger test sets and fault sets, both the time and memory cost may increase significantly, which is demonstrated in the experiment results in Chapter 5.

Since many DL-prediction models [13-16] predict DL to decrease as fault coverage increases, this dissertation aims at selecting a subset of tests that achieve the highest fault coverage. The test-selection problem is NP-complete but can be modeled as a maximum-K coverage problem [46]. Motivated by online maximum-K coverage algorithms [47-48], a one-pass test-selection method is developed to provide a time-and-memory-efficient approach for selecting tests from a large pool of tests. The one-pass method processes one test at a time in a streaming fashion. After each test is fault-simulated, the one-pass method compares the simulated test with other selected tests, and decides whether the test should be kept or discarded. Unlike previous methods, the one-pass method does not need to keep fault simulation results of all tests in memory, and only needs to processes each test once, resulting in low computation and memory complexity. Experiments are performed to select tests for two large industrial circuits and two benchmark circuits. The selected tests are compared in terms of fault coverage with tests selected using the greedy algorithm, an LP-based approach, and tests selected based on the original ordering Experiment results demonstrate that the one-pass method selects tests with coverage that virtually matches a greedy algorithm (less than 0.01% coverage difference), but uses less time (reduced by 2X) and memory (reduced by 20X to 200X).

### 1.5 Dissertation Organization

The rest of the dissertation is organized as follows: Chapter 2 describes a one-pass test-reordering method developed to improve diagnosability of production tests. Chapter 3 describes DELAY-METER, a method used to evaluate the effectiveness of delay fault models based on diagnosis. Chapter 4 describes the DDP model, a model that predicts DL from diagnosis data and fault coverages of multiple fault models. Chapter 5 describes a one-pass test-selection method developed to select a subset of tests for achieving maximum fault coverage. Chapter 6 concludes the contribution of this thesis and provides topics for future work.

# **Chapter 2 Test Reordering for Improving**

# **Diagnosability**

Improving diagnosability using production tests is very important because: (i) High diagnosability enables fast analysis of failing locations, behaviors that leads to valuable feedback for achieving fast yield ramp-up. (ii) The large number of chips that fail during high-volume production enable the extraction of information that is statistically-significant for yield learning. (iii) Production tests are typically optimized for defect detection, not for diagnosis. For example, not all failing tests and pins are recorded in the tester response of a failing chip, which makes diagnosis more difficult. In this chapter, a test-reordering method is developed to improve the diagnosability of production tests when the recorded tester response is, by design, incomplete. To our knowledge, this is the first-ever work that examines the impact of test order on logic diagnosis. The experiments uses test data taken from both virtual and real failing chips of two industrial designs to verify the improvement of diagnosability stemming from a production test set that has been reordered using the method developed in this work. Experiment results show that the number of failing chips with perfect diagnostic resolution is increased by 8.3% and 5.1%, respectively, for two industrial designs after tests are reordered. The number of failing chips with diagnostic resolution ≤ 5 is increases by 1.9% and 1.5%, respectively, for the two designs. In all cases, diagnosis accuracy is also maintained.

### 2.1 Background

Logic diagnosis is an important first step for identifying the defect locations within a failing chips. Diagnosis uses a tester response (i.e., a fail log collected from a tester during the test of a failing chip) as input data, and produces one or more circuit locations (wire, gate, etc.) typically called candidates, where defects are believed to be most likely located. Diagnosis methods can be categorized into either cause-effect or effect-cause

methods [49]. Cause-effect diagnosis assumes a defect behaves like a fault from a given fault model. By comparing the simulated behavior of each fault (simulation response) with the measured tester response, faults whose simulation responses best match the tester response are reported as candidates. Effect-cause diagnosis, on the other hand, starts from failing outputs and reasons back through the chip design to identify lines that (if faulty) could have caused the failing outputs [49]. Most state-of-the-art diagnosis tools (including the commercial diagnosis tools used in this dissertation) use a combination of cause-effect and effect-cause approach to perform diagnosis. More specifically, regions where defects are possibly located are first identified using an effect-cause approach, then faults (typically SSL faults) within the identified regions are simulated and compared with the tester response to find and report candidates in a cause-effect manner.

Precise and accurate diagnosis enables further analysis of the failure mechanisms using techniques like physical failure analysis (PFA), which provides important feedback for improving the fabrication process, the design and even test itself. The precision of diagnosis is typically measured by diagnostic resolution. Diagnostic resolution refers to the number of candidates associated with defect locations within a failing chip. Higher diagnostic resolution (few candidates) is desired because the success rate of PFA is inversely related to the number of possible defect locations. The accuracy of diagnosis is also very important. Accuracy can be calculated in many ways, for example, as the fraction of failing chips whose candidates include the real defect locations. Inaccurate diagnosis leads to wasted efforts in PFA and may provide wrong feedback to manufacturing and testing. In this chapter, although not directly mentioned everywhere, improving diagnostic resolution is accompanied by a secondary goal of maintaining diagnosis accuracy.

There are many previous publications focused on improving diagnostic resolution. One approach is to improve the fault model or the algorithm used in diagnosis to deal with defects with complicated behaviors. For example, multiple-fault diagnosis [50][51] assumes the defects affecting a failing chip can cause multiple signal lines to be simultaneously faulty [49], and tries to identify diagnosis candidates by analyzing each failing test individually [50] or by simulating an unknown value (X) on each suspected location [51]. Physical-aware diagnosis [52] analyzes the logical values on signal lines in the physical or logical proximity to a faulty line to remove candidates that have inconsistent behaviors. Machine learning can also be used in

diagnosis [21] to predict whether a diagnosis candidate is true or false, with predicted false candidates discarded to improve diagnostic resolution.

An alternative approach to improve diagnostic resolution is to provide diagnosis with a better input data, for example, by applying extra tests or recording more tester response. Diagnostic ATPG [12][24] generates and applies extra tests to make faults distinguishable, in other words, the objective is to make the simulation response of each fault unique. Faults that are distinguished from each other are unlikely to become diagnosis candidates at the same time, which leads to higher diagnostic resolution. Due to limited tester time or memory, typically not all tester response is recorded when a chip failed, diagnostic resolution can be improved by collecting tester response in an "intelligent" way [53][54]. The work in [53] uses diagnosis results from previously tested chips to predict the amount of tester response that needs to be recorded. Alternatively, the work in [54] allows testers dynamically determine a subset of tests whose tester responses are recorded. Diagnostic resolution can also be improved through test reordering [55], by placing the tests with high scan-chain diagnosability at the beginning of a new ordering of tests to improve scan-chain diagnosis.

The test-reordering method developed in this chapter optimizes the recorded tester data for achieving a better diagnostic resolution. By reordering the tests to enable faults to have different simulation responses, diagnostic resolution can be improved when a limited tester response is recorded for each failing chip. The rest of the chapter is organized as follows: Section 2.2 introduces the test-reordering method. Section 2.3 provides experiment results verifying diagnostic resolution improvement for two industrial designs (an IBM ASIC and an NVIDIA GPU). Section 2.4 summarizes the chapter by reiterating the contributions of this work.

### 2.2 Methodology

This section introduces the test-reordering method and is organized as follows: Section 2.2.1 reviews the practice of collecting incomplete tester response in production testing, and how diagnostic resolution could be adversely affected. Section 2.2.2 provides an example how diagnostic resolution can be improved through test reordering. Finally, Section 2.2.3 describes the detailed one-pass flow for test reordering.

#### 2.2.1 Incomplete Tester Response

The chips that fail during high-volume production can provide valuable information for yield learning. However, the limited amount of information recorded for each failing chip makes diagnosis difficult. For better diagnostic resolution, it is desired that all tests are applied and the full tester response (all failing tests and output pins information) is recorded. However due to limited tester time and/or memory, typically only the tester response from a subset of tests (i.e., incomplete tester response) is recorded. Common practice is to record tester response for a failing chip on a first-come basis until the tester memory is full, from which point no more tester responses are recorded. This practice adversely affects diagnostic resolution since less information is provided to diagnosis [53]. As an alternative solution for improving diagnostic resolution, recent work has proposed "intelligent" ways for collecting a tester response, such as allowing testers to dynamically determine when to stop recording [53], or to select which test responses should be recorded [54]. However, these proposed approaches for tester-response collection require real-time computation on testers which are not yet commonplace. In this work, the tester response is assumed to be collected normally, that is, on a first-come basis.

| Design Technolog        |            | No. of recorded failing tests |        |     |

|-------------------------|------------|-------------------------------|--------|-----|

| Design                  | Technology | Average                       | Median | Max |

| NVIDIA GPU              | 90 nm      | 117                           | 93     | 655 |

| IBM                     | 130 nm     | 8.09                          | 6      | 20  |

| Freescale               | 55 nm      | 32.3                          | 10     | 255 |

| LSI                     | 110 nm     | 64.2                          | 61     | 200 |

| NVIDIA test chip        | 28 nm      | 47.9                          | 9      | 402 |

| <b>GLOBAL FOUNDRIES</b> | 28 nm      | 165                           | 159    | 276 |

Table 1: The average, median and maximum number of failing tests per chip recorded in the tester response from six industrial designs aimed at various technology nodes.

In order to find an optimal ordering for improving diagnostic resolution when an incomplete tester response is collected, certain assumptions need to be made concerning when a tester stops collecting data. This work assumes only the tester response from the first N failing tests is recorded. This assumption is a simplification of the common practice in tester response collection. In reality, the number of failing tests recorded for each failing chip may vary based on the size of tester memory and the number of failing output pins associated with each failing tests. Table 1 shows the average, median and maximum number of failing

tests per chip recorded in the tester response from six different industrial chip designs (tester responses are all collected on a first-come basis). An empirical value of N can be derived from the statistics of previously-tested chips based on the median values listed in Table 1. This simplified assumption, although not ideal, makes the test-reordering problem solvable in a reasonable amount of time using only the set of faults detected by each test, which can easily be acquired from fault simulation or a pass-and-fail fault dictionary.

#### 2.2.2 Intuition of Test Reordering

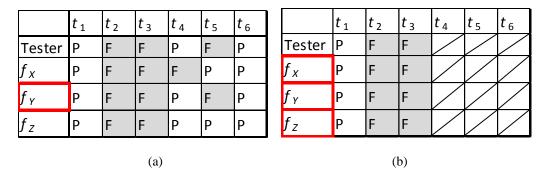

The goal of the test reordering work is to find an optimal ordering that make faults distinguishable when only the first N failing tests are recorded in the tester response. Making faults distinguishable is a goal pursued by previous work on diagnostic ATPG [12][24]. Diagnostic ATPG improves the diagnosability of production tests by adding extra tests that cause each fault to have a different, unique simulation response. Because the set of diagnosis candidates is typically obtained based on faults (in particular, SSL faults) [12], when the simulation responses of faults are different from each other, they are unlikely to become candidates for a given chip. Therefore the number of reported diagnosis candidates is effectively reduced and diagnostic resolution is improved. The proposed test-reordering work however does not use extra tests, it instead attempts to improve diagnostic resolution when fewer tests are provided for diagnosis due to an incomplete recording of a tester response. Using fewer tests in diagnosis may lead to poor diagnostic resolution, as illustrated in an example shown in Table 2. Assume six tests  $(t_1, t_2, ..., t_6)$  are applied to a chip on a tester, and the chip fails  $t_2$ ,  $t_3$  and  $t_5$ . The three failing tests are recorded as the tester response shown in the row "Tester" in Table 2(a). Three faults  $f_X$ ,  $f_Y$  and  $f_Z$  are simulated and compared with the tester response in causeeffect diagnosis (assuming only failing tests not failing pins are used in diagnosis).  $f_Y$  is identified as the sole diagnosis candidate because the simulation responses of  $f_X$  and  $f_Z$  do not match the tester response. Therefore, perfect diagnostic resolution is achieved in the example shown in Table 2(a). However, when N=2, which means the tester only records the first two failing tests  $t_2$  and  $t_3$ , the pass-and-fail information for tests after  $t_3$  is not recorded and cannot be used in diagnosis as shown in Table 2(b). As a result, all three faults  $f_X$ ,  $f_Y$ and  $f_Z$  become diagnosis candidates because their simulation responses now match the tester response for  $t_1$ ,  $t_2$  and  $t_3$ . In other words,  $f_X$ ,  $f_Y$  and  $f_Z$  cannot be distinguished using only  $t_1$ ,  $t_2$  and  $t_3$ , so the resulting diagnostic resolution in Table 2(b) is three, worse than the perfect resolution achieved in Table 2(a).

Table 2: A diagnosis example where  $f_Y$  is the sole diagnosis candidate in (a) when full tester response is provided, but in (b) incomplete tester response causes all three faults  $f_X$ ,  $f_Y$  and  $f_Z$  to become diagnosis candidates.

Table 3: A diagnosis example where  $f_Y$  is the sole diagnosis candidate when either (a) full tester response or (b) incomplete tester response is provided, diagnostic resolution is no longer affected in this ordering.

However, if tests are reordered to  $(t_1, t_4, t_5, t_2, t_3, t_6)$ , as shown in Table 3, then perfect resolution  $(f_Y)$  is the sole diagnosis candidate) is achieved using either the full tester response in Table 3(a), or the incomplete tester response (N=2) in Table 3(b). Both  $t_4$  and  $t_5$  provide vital information for distinguishing  $f_X$ ,  $f_Y$  and  $f_Z$  because they exhibit the difference in the simulation response of the three faults. By reordering  $t_4$  and  $t_5$  to the beginning of the reordered test sequence, the diagnostic resolution using incomplete tester response (N=2) is greatly improved from three in Table 2(b) to one in Table 3(b). This example demonstrates the intuition of the test-reordering method developed in this chapter.

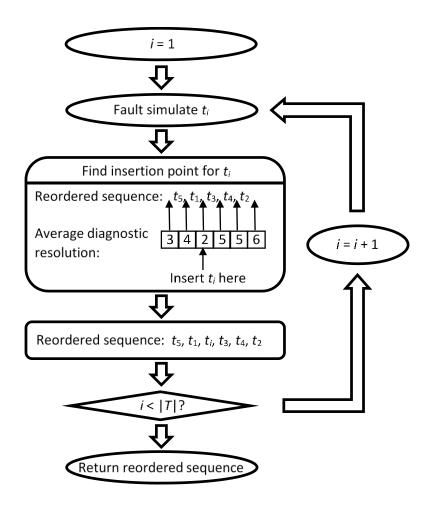

#### 2.2.3 One-Pass Test-Reordering Flow

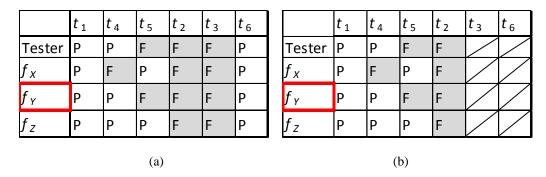

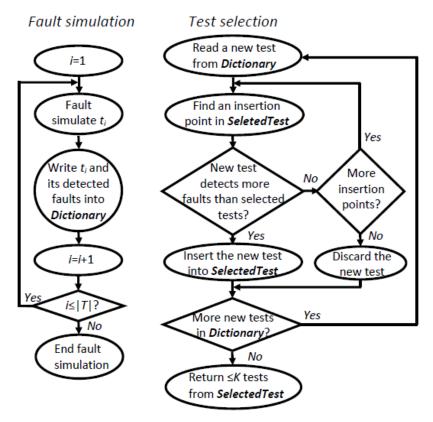

To save time and memory, tests are reordered in a one-pass approach as illustrated in the flow diagram in Figure 2. The input data of the test-reordering method is a test sequence consisting of T tests  $(t_1, t_2, ..., t_T)$  called here the *original sequence*, which could be a sequence of production tests generated from ATPG. Tests from the original sequence are fault simulated and processed by the test-reordering method one by one in a

streaming fashion. Assume  $t_1, t_2, ..., t_{i-1}$  have already been processed by the test-reordering method, and the |i-1| processed tests are reordered and placed in a new test sequence, called the *reordered sequence*. When the test-reordering method begins to process  $t_i$ , the first step is to fault simulate  $t_i$  and identify all faults detected by  $t_i$ . Then based on faults detected by previous tests  $t_1, t_2, ..., t_{i-1}$  and  $t_i$ , an optimal insertion point is found for  $t_i$  in the reordered sequence to minimize average diagnostic resolution (ADR, formally defined in the subsequent paragraph). After the insertion of  $t_i$  into the reordered sequence, the next test  $t_{i+1}$  is fault-simulated and inserted in the same way. After all T tests are inserted into the reordered sequence, test reordering is complete and the reordered sequence becomes the final test-reordering output. The benefit of this one-pass approach is that reordering can be performed simultaneously with fault simulation to save overall computation time cost. Moreover, after  $t_i$  is inserted into the reordered sequence, the fault simulation result of  $t_i$  can be deleted from memory. So throughout the test reordering process the memory requirement is low.

The process of finding an insertion point for  $t_i$  into the reordered sequence is to list all possible insertion points (i points), and find a point where if  $t_i$  is inserted, average diagnostic resolution (ADR) would be minimized, as illustrated in the center part of Figure 2. Under the assumption that only N tests are recorded in the tester response, and the defect behaves as an arbitrarily-selected fault from a fault set F, the value of ADR for a given test sequence s, ADR(s,N) is calculated as follows:

$$ADR(s,N) = \frac{\sum_{f_j \in F} |\forall f_k: \ f_k \in F \ and \ SR(f_k,s,N) = SR(f_j,s,N)|}{|F|} \tag{1}$$

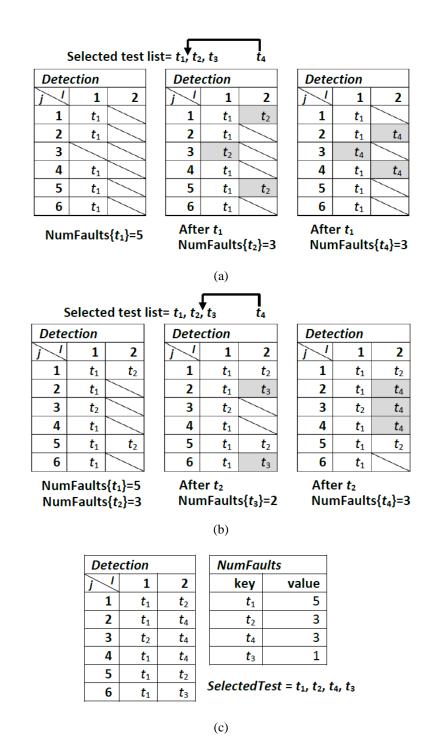

where SR(f, s, N) represents the first N failing tests in the simulation response of fault f in test sequence s, ADR(s, N) is the expected diagnostic resolution if the defect behaves like an arbitrarily-selected fault  $f_j$  in F, and only the first N tests are recorded in the tester response. Because in diagnosis, all faults ( $f_k$  in Equation 1) that have the same failing tests as  $f_j$  will be reported as candidates (assuming failing-pins information is not used in diagnosis). Consider an example shown in the left part of Table 4(a),  $s = (t_1, t_4, t_3, t_2)$ , N = 2, and  $F = \{f_1, f_2, f_3, f_4\}$ . For  $f_1$ , there is only one fault k=1 that satisfies both  $f_k \in F$  and  $SR(f_k, s, N=2)$  =  $SR(f_1, s, N=2)$ , because faults other than  $f_1$  have simulation responses different from  $f_1$ . However for  $f_3$ , there are two faults k=3 and k=4 which satisfy  $f_k \in F$  and  $SR(f_k, s, N=2) = SR(f_3, s, N=2)$ , because  $f_3$  and  $f_4$  have the same simulation responses. So ADR(s, N=2) = (1+1+2+2)/4 = 1.5.

Figure 2: The flow diagram of the one-pass test-reordering method.

Table 4: An example showing the change of fault simulation responses (a) before and (b) after a new test  $t_5$  is inserted into a test sequence  $(t_1, t_4, t_3, t_2)$ , when N = 2.

After a new test is inserted into a reordered sequence s, the new reordered sequence is named as s'.

The test-reordering method attempts to find an insertion point where ADR(s', N) can be minimized. As shown

in the right part of Table 4(a), a new test  $t_5$  detects three faults  $f_1$ ,  $f_2$  and  $f_3$  and has to be inserted into s. Table 4(b) shows SR(f, s', N=2) when  $t_5$  is inserted before  $t_4$  and after  $t_1$ ,  $s' = (t_1, t_5, t_4, t_3, t_2)$ . After the insertion of  $t_5$ , ADR(s', N=2) becomes larger than ADR(s, N=2), because  $f_1$ ,  $f_2$  and  $f_3$  now have the same SR(f, s', N=2) and are no longer distinguished from each other, which implies this insertion point might not be optimal. The calculation of ADR(s', N=2) for all possible insertion points where  $t_5$  can be inserted is shown in Table 5. SR(f, s', N=2) is listed for each fault and each possible s' after  $t_5$  is inserted. The insertion example shown in Table 4(b) corresponds to the second column in Table 5. Equivalent values for SR(f, s', N=2) are marked in the same color in Table 5. As can be seen, the last two insertion points "after  $t_3$ , before  $t_2$ " and "after  $t_2$ " cause the four faults to have three different values for SR(f, s', N=2) compared to other insertion points that only have  $\le 2$  different values for SR(f, s', N=2). In other words, these two insertion points make faults more distinguishable and become the ideal insertion points for  $t_5$ . The last row in Table 5 shows the calculation of ADR(s', N=2) for each insertion point. The last two insertion points have the lowest values for ADR(s', N=2), and the test-reordering method can choose either of them as an insertion point for  $t_5$ .

|       |                       | After t 1,            | After t 4,            | After t <sub>3</sub> , |                |

|-------|-----------------------|-----------------------|-----------------------|------------------------|----------------|

|       | Before t <sub>1</sub> | before t <sub>4</sub> | before t <sub>3</sub> | before t 2             | After t 2      |

| $f_1$ | $\{t_1,t_5\}$         | $\{t_1, t_5\}$        | $\{t_1, t_5\}$        | $\{t_{1},t_{5}\}$      | $\{t_1, t_5\}$ |

| $f_2$ | $\{t_1,t_5\}$         | $\{t_1,t_5\}$         | $\{t_1,t_4\}$         | $\{t_1,t_4\}$          | $\{t_1,t_4\}$  |

| $f_3$ | $\{t_1,t_5\}$         | $\{t_1,t_5\}$         | $\{t_1,t_5\}$         | $\{t_1,t_3\}$          | $\{t_1,t_3\}$  |

| $f_4$ | $\{t_{1},t_{4}\}$     | $\{t_1,t_4\}$         | $\{t_1,t_4\}$         | $\{t_1,t_4\}$          | $\{t_1,t_4\}$  |

|       | (3×3+1)/4             | (3×3+1)/4             | (2×2+2×2)             | (2×2+1+1)              | (2×2+1+1)      |

| ADR   | =2.5                  | =2.5                  | /4=2                  | /4=1.5                 | /4=1.5         |

Table 5: Calculation of ADR for all possible points for  $t_5$  (N=2). The first two tests that detect each fault after  $t_5$  is inserted at each insertion point are listed. The last two insertion points have the lowest ADR and become the ideal insertion points.

### 2.3 Experiments

This section presents the experiment results verifying the diagnostic resolution improvement of the test-reordering method on an IBM ASIC and an NVIDIA GPU. Section 2.3.1 describes the flow of both IBM ASIC and NVIDIA GPU experiments. Sections 2.3.2 and 2.3.3 present the IBM ASIC experiment results

and NVIDIA GPU experiment results, respectively. Section 2.3.4 provides further discussion about the experiments.

#### **2.3.1 Setup**

Two experiments are conducted to verify the diagnostic resolution improvement of the test-reordering method for two industrial designs, an IBM ASIC and an NVIDIA GPU. The setup of both experiments can be described using the flow diagram illustrated in Figure 3. The original sequence of tests for both experiments use the production tests generated from ATPG. The reordered sequence of tests are generated from the original sequence using the test-reordering method to optimize ADR for all collapsed SSL faults. Before test reordering, the value of N (the number of failing tests recorded by a tester) needs to be specified, because the calculation of ADR and the resulting reordered sequence are dependent on the choice of N. A number of different N values are investigated to verify the robustness of the test-reordering method. The major input data for diagnosis is the original full tester response, which is either collected from testing of actual chips or from the simulation of chips injected with virtual defects. Based on the reordered sequence, the original full tester response can be transformed into the reordered full tester response by changing the test indices. The original and reordered versions of incomplete tester responses can then be generated from the two versions of full tester responses, respectively, by emulating a tester that only records the first N failing tests of each failing chip. A commercial diagnosis tool is then used to diagnose the original and reordered incomplete tester response. Diagnostic resolution and accuracy are measured from diagnosis logs and compared.

Figure 3: Experiment flow diagram comparing the diagnostic resolution achieved using the original sequence and the reordered sequence of tests.

## 2.3.2 IBM ASIC Experiment Result

The IBM ASIC used in this experiment is manufactured in 130nm technology and contains about 10 million transistors. The total number of uncollapsed SSL faults is 4.4 million. The original sequence of tests includes 3,321 stuck-at tests generated by the ATPG tool Cadence® Encounter Test® that achieve more than 99% SSL fault coverage. The order of tests in the original sequence is the same as the order of tests applied during production testing. The original full tester response is generated from the fault simulation results of a population of 1,689 virtual failing chips. The virtual failing chip population is created by injecting various types of defects, including SSL, dominant bridge, AND/OR bridge, input-pattern and MSL (multiple stuck line), into each virtual failing chip, in order to ensure the virtual failing chip population resembles a realistic failing chip population.

|               | The number of failing chips that have K diagnosis candidates |               |              |             |             |              |             |             |             |           |  |

|---------------|--------------------------------------------------------------|---------------|--------------|-------------|-------------|--------------|-------------|-------------|-------------|-----------|--|

| К             | N                                                            | = 1           | N = 3        |             | N           | N = 5        |             | = 8         | N = 10      |           |  |

| ^             | Original                                                     | Reordered     | Original     | Reordered   | Original    | Reordered    | Original    | Reordered   | Original    | Reordered |  |

| 1             | 397                                                          | 511           | 811          | 812         | 870         | 889          | 867         | 960         | 850         | 946       |  |