# Digital Calibration Method for High Resolution in Analog/RF Designs

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

#### Renzhi Liu

B.S., Electronics Engineering and Computer Science, Peking University

Carnegie Mellon University

Pittsburgh, PA

July, 2015

To my dear wife, Liang

### **Acknowledgments**

First, I would like to thank my advisor Professor Larry Pileggi for all his support and continuous guidance throughout the past five years. He opened up a wide variety of research topics that I can explore during my early years at Carnegie Mellon University (CMU) and helped me find my research path that eventually leads to this dissertation.

Second, I would like to thank my co-advisor Professor Jeff Weldon. It was him who guided me to the RF circuit design in this dissertation, during which I gradually came up with the proposed digital calibration method.

Next, I would like to thank the rest of my dissertation committee members. Professor Jeyanandh Paramesh gave the lectures of the most valuable class to me at CMU, which was radio frequency integrated circuits design. This class shaped my research interests as well as my future career path. Dr. Gokce Keskin proposed the original design method on which my new method was based. His work inspired me during my graduate study and I became an early adopter of his proposed design method in one of my early chip design.

I would also like to thank my fellow lab members. Kaushik Vaidyanathan has patiently taught me, an analog circuit designer, how to do proper semi-custom digital circuit design. As a senior student to me, his advices also helped me to go through graduate student life as well as to find my career path. David Bromberg, Ekin Sumbul, Vanessa Chen and Vehbi Calyir entered the Ph.D. program at the same year as I did. I appreciate all the collaborations we have in classes as well as in research projects with the thoughtful discussions and sincere advices. I would also like to thank the rest of the current and past lab members in Professor Pileggi's group who overlapped with me: Andrew Phelps, Bishnu P Das, Cheng-Yuan Wen, Curtis Ratzlaff, Dan

Morris, Fazle Sadi, Jinglin Xu, Kuntal Shah, Meric Isgenc, Ozan Iskilibli, Qiuling Zhu, Rongye Shi, Shaolong Liu, Soner Yaldiz and Thomas Jackson. I treasure the years that we spent together at CMU.

The work presented in this dissertation was supported in part by the Intelligence Advanced Research Program Agency and Space and Naval War-fare Systems Center Pacific under Contract No. N66001-12-C-2008.

Last but not least, I would like to thank my parents. They have raised me as an individual that desires for knowledge and truth. I will be forever grateful for all the things they taught me and the characters they gave me.

Finally, I would like to give my deepest thanks to my beloved wife Liang Tang, although words cannot describe the magnitude of my gratitude here. It was a small probability event that we met each other at Peking University and then came to CMU together as graduate students. I cannot achieve anything without your help, your love and your sacrifice.

### **Abstract**

Transistor random mismatch continuously poses challenges for analog/RF circuit design for achieving high accuracy and high yield as the process technology advances. Existing statistical element selection (SES) design method can improve transistor matching property, but it falls short of being a general calibration method due to its limited calibration range.

In this dissertation, we propose a high resolution digital calibration method, called extended statistical element selection (ESES). As compared to the SES method, the ESES method not only provides wider calibration range, but also it results in higher calibration yield with same calibration resolution target. Two types of ESES based calibration application in analog/RF circuits are also proposed. One is current source calibration and the other is phase/delay calibration.

To verify this proposed digital calibration method in circuit implementation, we designed, fabricated and tested a wideband harmonic rejection receiver design. The receiver utilizes ESES-based gain and phase error calibration for improving harmonic rejection ratios. With the high calibration resolution provided by the ESES method, after calibration, we achieved best-in-class harmonic rejection ratios. To extend the application of the proposed method, we further designed a current-steering D/A data converter (CS-DAC). The CS-DAC utilizes ESES-based amplitude and timing error calibration for improving linearity performance. Simulation results showed that we can achieve more than one order of magnitude linearity improvement after performing ESES-based calibration in the CS-DAC.

## **Contents**

| 1 | I   | NTRODUCTION                                                         | 1    |

|---|-----|---------------------------------------------------------------------|------|

| 2 | В   | BACKGROUND                                                          | 4    |

|   | 2.1 | RANDOM MISMATCH IN CMOS TECHNOLOGY                                  | 4    |

|   | 2.2 | TRANSISTOR SIZING FOR MATCHING                                      | 5    |

|   | 2.3 | STATISTICAL ELEMENT SELECTION (SES) DESIGN METHODOLOGY              | 6    |

|   | 2.4 | CALIBRATION METHODS FOR CURRENT SOURCES AND PHASE DELAYS            | 7    |

|   | 2   | .4.1 Current Sources Calibration Methods                            | 7    |

|   | 2   | .4.2 Phase Delay Calibration Methods                                | 8    |

|   | 2.5 | SUMMARY                                                             | . 10 |

| 3 | H   | HIGH RESOLUTION CALIBRATION APPROACH                                | 11   |

|   | 3.1 | EXTENDED STATISTICAL ELEMENT SELECTION (ESES)                       | 11   |

|   | 3   | .1.1 Limitations of SES                                             | 11   |

|   | 3   | .1.2 ESES Method Overview                                           | . 13 |

|   | 3   | .1.3 ESES Calibration Resolution and Calibration Range Study        | . 15 |

|   | 3.2 | ESES-BASED HIGH RESOLUTION CURRENT CALIBRATION                      | . 26 |

|   | 3.3 | ESES-BASED HIGH RESOLUTION PHASE DELAY CALIBRATION                  | . 28 |

|   | 3.4 | SUMMARY                                                             | . 30 |

| 4 | Н   | HARMONIC REJECTION RECEIVER DESIGN                                  | . 31 |

|   | 4.1 | HARMONIC REJECTION RECEIVER OVERVIEW                                | . 31 |

|   | 4   | .1.1 Harmonic Rejection Scheme and Impacts of Gain and Phase Errors | . 31 |

|   | 4.1.2   | Previous Work on Achieving High HRR                            | 34 |

|---|---------|----------------------------------------------------------------|----|

|   | 4.2 ESI | ES-BASED HARMONIC REJECTION RECEIVER DESIGN                    | 36 |

|   | 4.3 CH  | P IMPLEMENTATION                                               | 38 |

|   | 4.3.1   | LNA Design                                                     | 38 |

|   | 4.3.2   | G <sub>m</sub> Stage with ESES-based Tunable Gain              | 39 |

|   | 4.3.3   | Passive Mixer Design                                           | 41 |

|   | 4.3.4   | TIA Design                                                     | 42 |

|   | 4.3.5   | Multi-phase LO Generator with ESES-based Tunable Phase         | 43 |

|   | 4.4 ESI | ES CALIBRATION PROCESS                                         | 46 |

|   | 4.4.1   | ESES Calibration for HR Receiver Overview                      | 46 |

|   | 4.4.2   | Even-order HRR Calibration Flow                                | 46 |

|   | 4.4.3   | 3 <sup>rd</sup> and 5 <sup>th</sup> Order HRR Calibration Flow | 47 |

|   | 4.5 HA  | RMONIC REJECTION RECEIVER TESTING                              | 49 |

|   | 4.5.1   | Measurement Setup                                              | 49 |

|   | 4.5.2   | Measurement Results                                            | 50 |

|   | 4.6 Sun | MMARY                                                          | 54 |

| 5 | CUR     | RENT-STEERING D/A CONVERTER DESIGN                             | 55 |

|   | 5.1 CUI | RRENT-STEERING DAC OVERVIEW                                    | 55 |

|   | 5.1.1   | Current-Steering DAC Linearity Enhancement Methods             | 55 |

|   | 5.1.2   | Previous Work on SES-based Current-Steering DAC                | 57 |

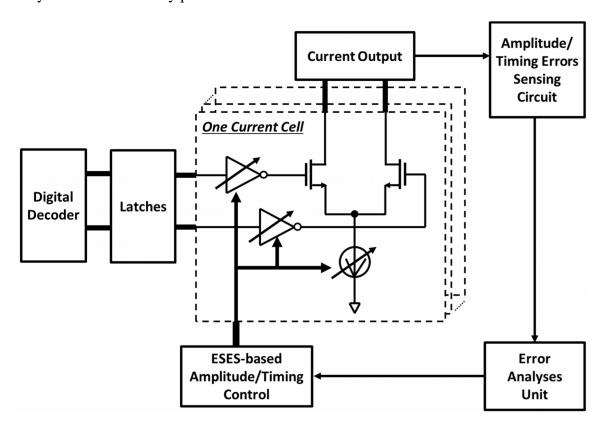

|   | 5.2 ESI | ES-BASED CURRENT-STEERING DAC DESIGN                           | 65 |

|   | 5.3 DES | SIGN IMPLEMENTATION                                            | 69 |

|   | 5.3.1   | Unary Current Cell Design with ESES-based Tunable Current      | 69 |

| RI | EFE | REN  | ICES                                                      | 85 |

|----|-----|------|-----------------------------------------------------------|----|

| 6  | C   | CONC | CLUSION AND FUTURE WORK                                   | 82 |

|    | 5.5 | SUM  | IMARY                                                     | 80 |

|    | 5.4 | SIM  | ULATION RESULTS                                           | 75 |

|    | 5.  | .3.3 | Error Sensing Circuit Design                              | 73 |

|    | 5.  | .3.2 | Latch Design with ESES-based Tunable Delay and Duty Cycle | 71 |

## **List of Figures**

| Figure 2.1 Current calibration circuit based on varying gate voltage [12]                                          |

|--------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 Conceptual circuit diagram of current calibration based on attaching extra current                      |

| source (a) method one (b) method two                                                                               |

| Figure 2.3 Current-starved inverter: (a) analog implementation; (b) digital implementation 9                       |

| Figure 2.4 Shunt-capacitor inverter: (a) analog implementation; (b) digital implementation 10                      |

| Figure 3.1 Design choices distributions w/o random variation: (a) SES method (b) ESES method.                      |

|                                                                                                                    |

| Figure 3.2 Design choices distributions w/ random variation: (a) SES method (b) ESES method.                       |

|                                                                                                                    |

| Figure 3.3 SES/ESES calibration failure rate vs. calibration target window when $T_{\text{offset}} = 016$          |

| Figure 3.4 SES/ESES calibration failure rate vs. calibration target window when $T_{offset} \!=\! \ _k 18$         |

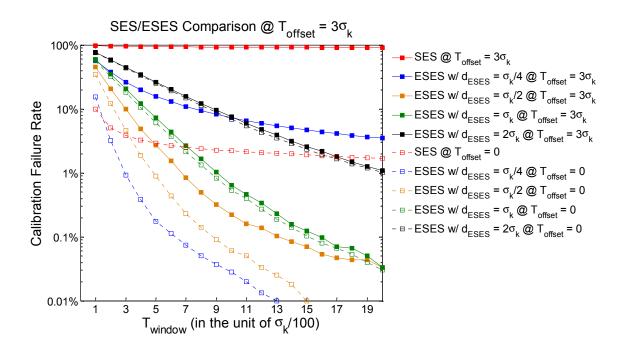

| Figure 3.5 SES/ESES calibration failure rate vs. calibration target window when $T_{\text{offset}} = 3$ k 19       |

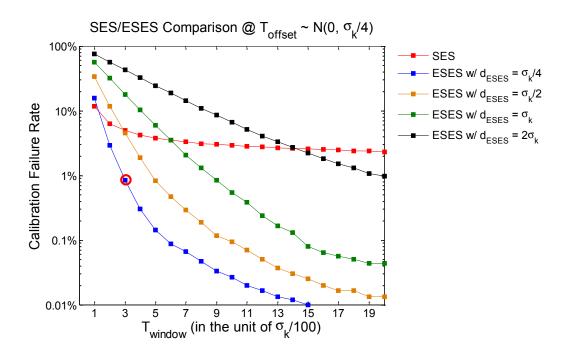

| Figure 3.6 SES/ESES calibration failure rate vs. calibration target window when $T_{\text{offset}} \sim N(0, 1)$   |

| k/4)                                                                                                               |

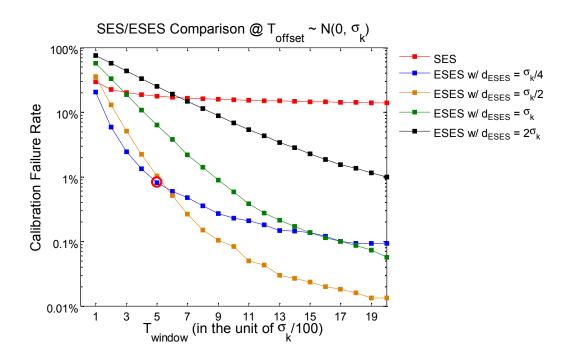

| Figure 3.7 SES/ESES calibration failure rate vs. calibration target window when $T_{\text{offset}} \sim N(0, 1)$   |

| k)21                                                                                                               |

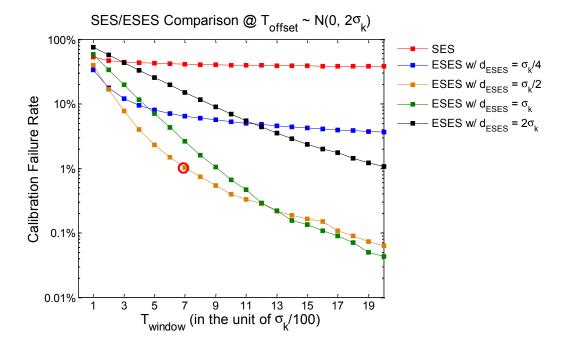

| Figure 3.8 SES/ESES calibration failure rate vs. calibration target window when $T_{\text{offset}} \sim N(0, 1)$   |

| 2 k)                                                                                                               |

| Figure 3.9 ESES calibration standard deviation reduction factor $R_{cal}$ vs. $_{T}$ with more than 99%            |

| calibration success rate                                                                                           |

| Figure 3.10 ESES calibration failure rate for various $a_{ESES}$ settings when $T_{offset} = 0$ , $d_{ESES} = k/4$ |

|                                                                                           | 24    |

|-------------------------------------------------------------------------------------------|-------|

| Figure 3.11 Conceptual circuit of ESES-based current calibration.                         | 26    |

| Figure 3.12 Conceptual circuit of ESES-based differential amplifier transconducta         | ance  |

| calibration.                                                                              | 27    |

| Figure 3.13 Conceptual circuit of ESES-based phase delay calibration: (a) tunable rising  | and   |

| falling edge; (a) tunable falling edge only.                                              | 28    |

| Figure 3.14 Conceptual circuits for high resolution phase delay calibration applications: | (a)   |

| differential signals calibration; (b) delay calibration of synchronous signals            | 29    |

| Figure 4.1 Reception of interference at LO harmonic frequencies for wideband receiver     | 32    |

| Figure 4.2 Reception of interference at LO harmonic frequencies for harmonic rejec        | ction |

| wideband receiver with gain errors and phase errors                                       | 33    |

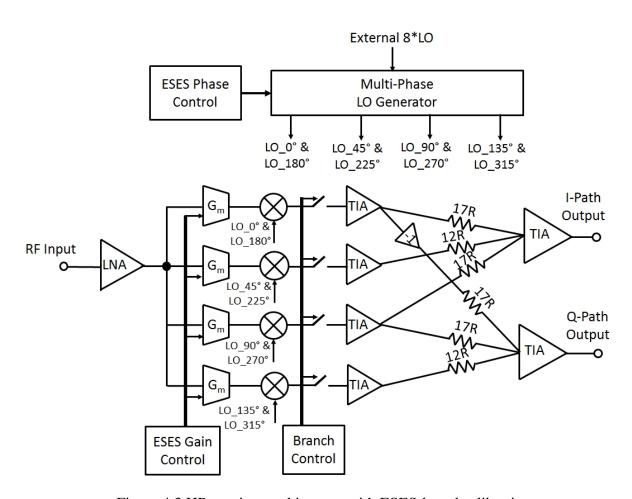

| Figure 4.3 HR receiver architecture with ESES-based calibration.                          | 37    |

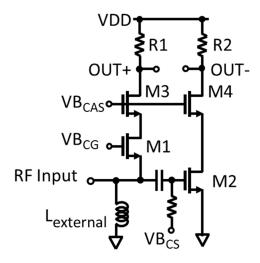

| Figure 4.4 LNA circuit design.                                                            | 38    |

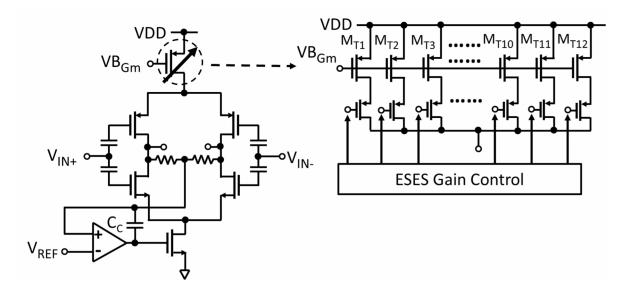

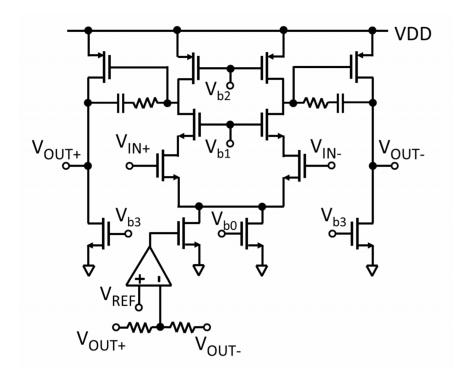

| Figure 4.5 G <sub>m</sub> stage with tunable gain.                                        | 40    |

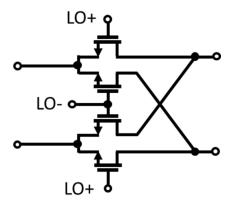

| Figure 4.6 Passive mixer circuit design.                                                  | 41    |

| Figure 4.7 TIA design.                                                                    | 42    |

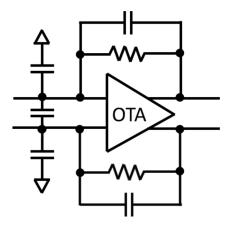

| Figure 4.8 OTA circuit design.                                                            | 43    |

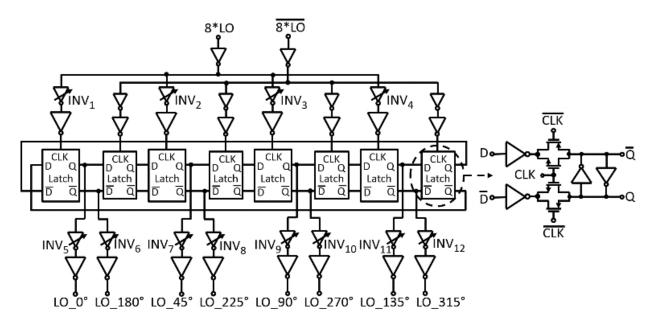

| Figure 4.9 Divide-by-8 multi-phase LO generator with tunable phase.                       | 44    |

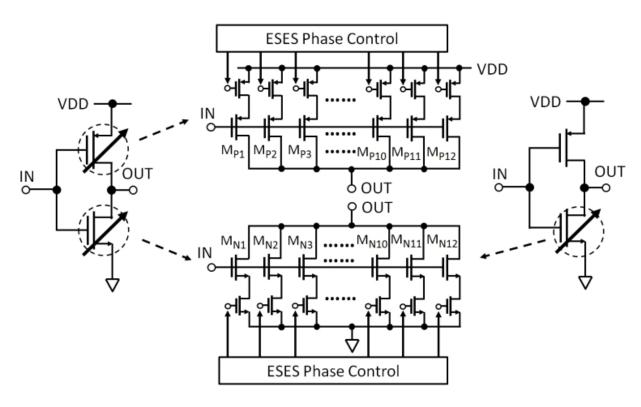

| Figure 4.10 Inverter design with tunable delay.                                           | 45    |

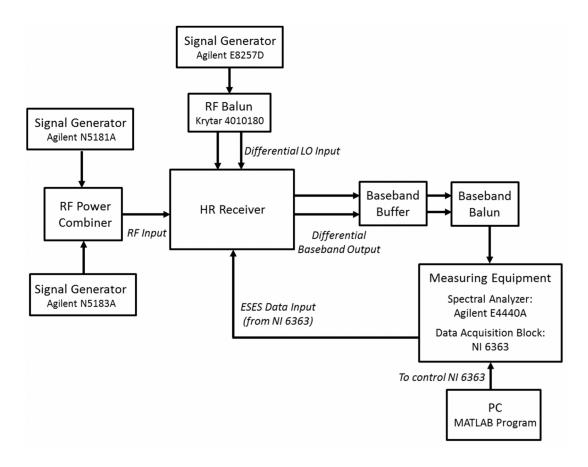

| Figure 4.11 Measurement setup diagram.                                                    | 49    |

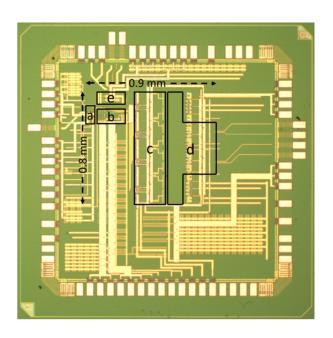

| Figure 4.12 Harmonic rejection receiver die photo (a. LNA; b. Gm stages; c. TIA branches  | s; d. |

| harmonic recombination for I/Q path; e. LO generator).                                    | 51    |

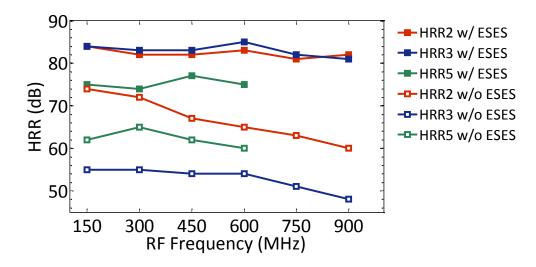

| Figure 4.13 HRR performance w/o and w/ ESES calibration.                                  | 52    |

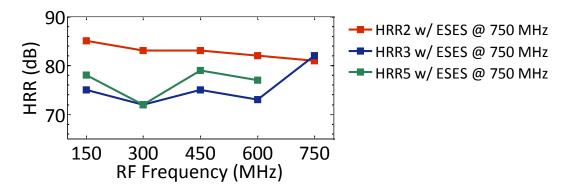

| Figure 4.14 HRR Performance after ESES-based calibration at 750 MHz                         | . 52 |

|---------------------------------------------------------------------------------------------|------|

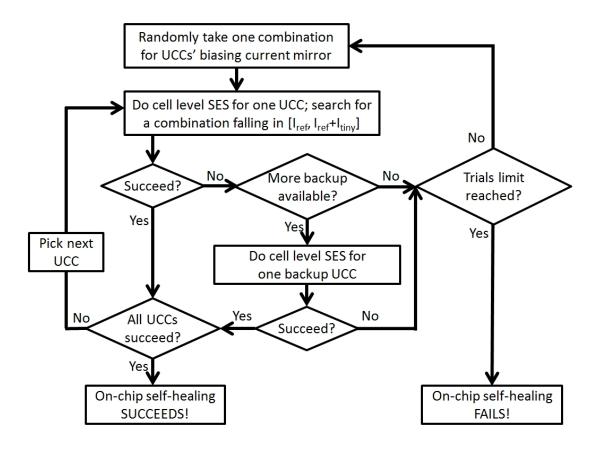

| Figure 5.1 Overall SES-based self-healing logic flow.                                       | . 59 |

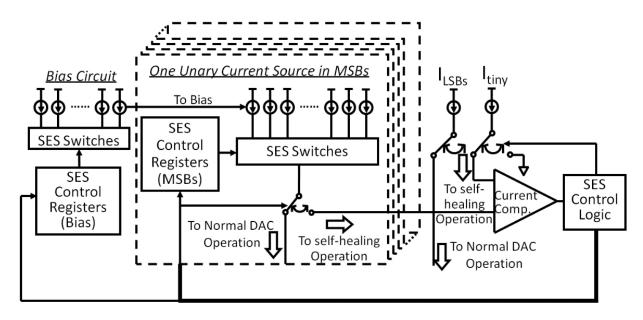

| Figure 5.2 System diagram of SES-based self-healing CS-DAC.                                 | . 60 |

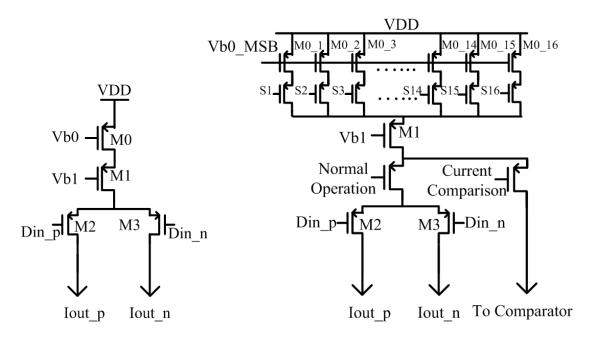

| Figure 5.3 (a) Typical UCC Design; (b) SES-based UCC Design.                                | . 61 |

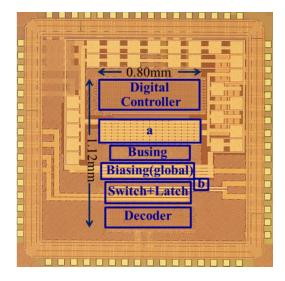

| Figure 5.4 Die photo of self-healing 14-bit CS-DAC. a. current source array + local biasing | g +  |

| dummies. b. current comparator                                                              | . 61 |

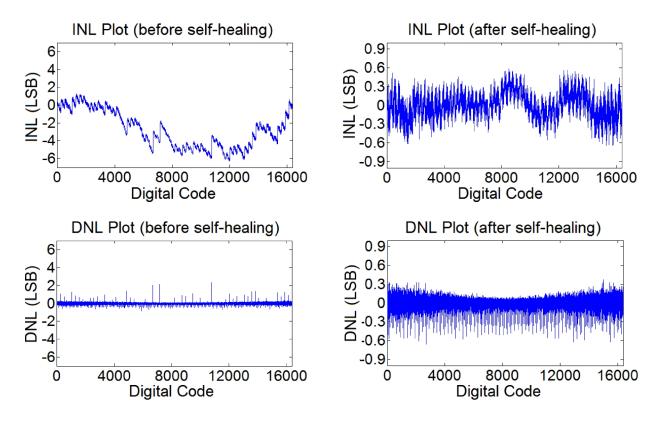

| Figure 5.5 INL, DNL plots before SES-based self-healing and after SES-based self-healing    | . 62 |

| Figure 5.6 Conceptual ESES-based CS-DAC design                                              | . 65 |

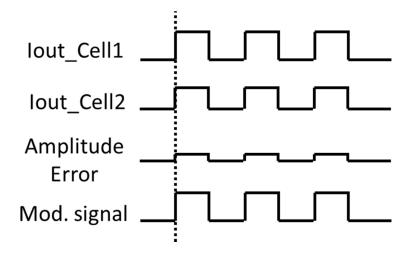

| Figure 5.7 Amplitude error sensing scheme.                                                  | . 66 |

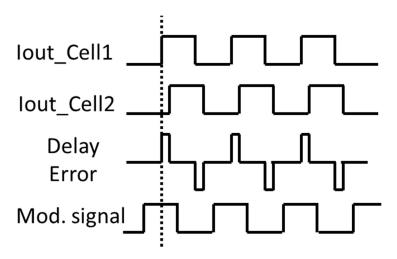

| Figure 5.8 Delay error sensing scheme.                                                      | . 67 |

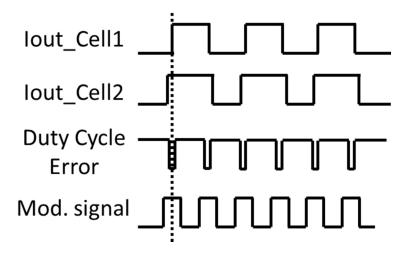

| Figure 5.9 Duty cycle error sensing scheme.                                                 | . 68 |

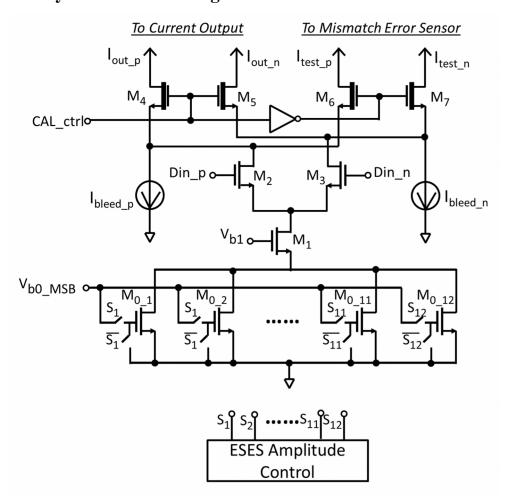

| Figure 5.10 ESES-based unary current cell Design.                                           | . 69 |

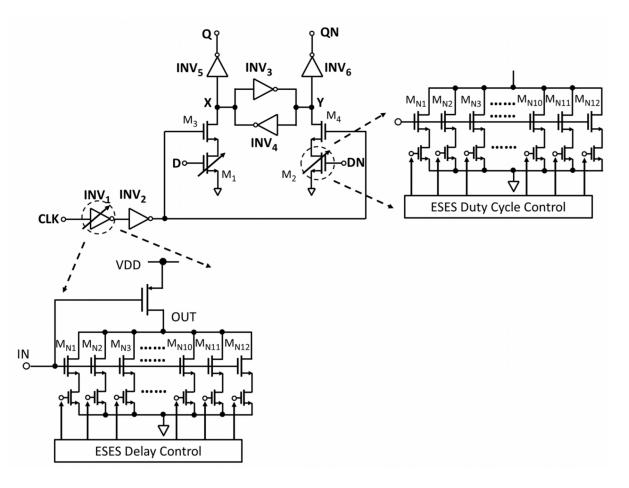

| Figure 5.11 ESES-based latch design with tunable delay and duty cycle.                      | . 72 |

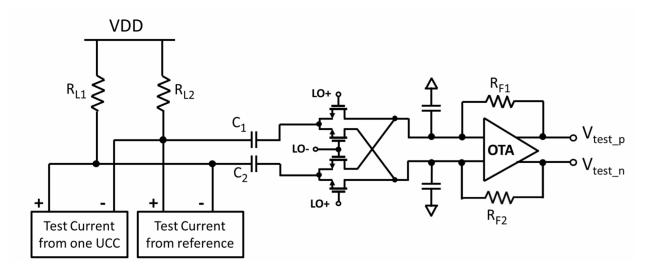

| Figure 5.12 Amplitude/timing error sensing circuit.                                         | . 73 |

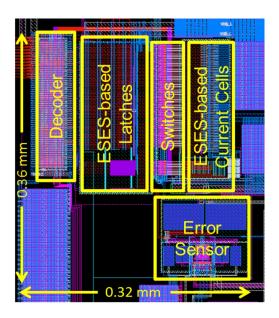

| Figure 5.13 Layout of the CS-DAC core circuit.                                              | . 75 |

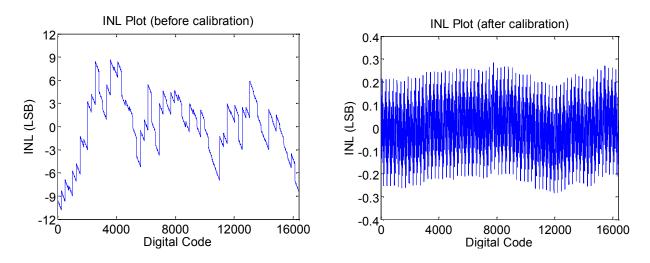

| Figure 5.14 INL plot before and after ESES-based calibration for one typical sample         | . 76 |

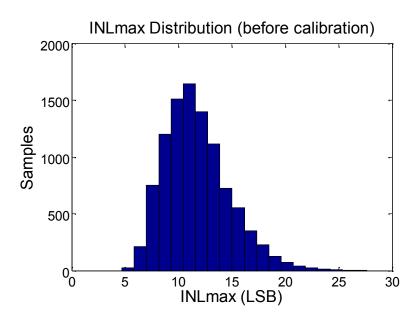

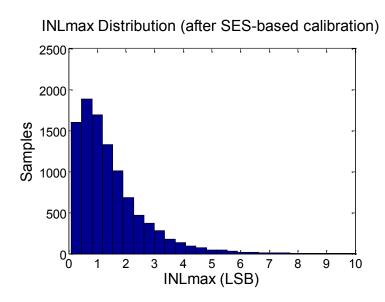

| Figure 5.15 INL <sub>max</sub> distribution before ESES-based calibration.                  | . 77 |

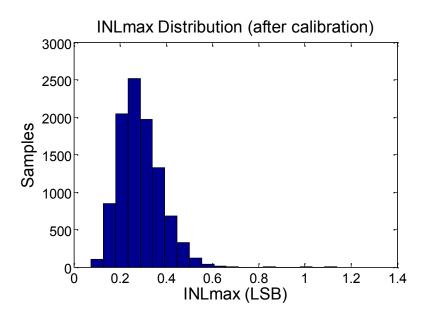

| Figure 5.16 INL <sub>max</sub> distribution after ESES-based calibration.                   | . 77 |

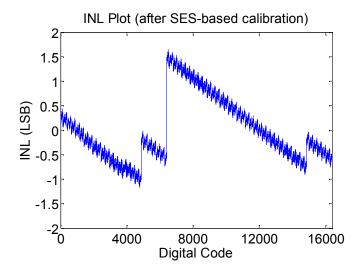

| Figure 5.17 INL <sub>max</sub> distribution after SES-based calibration                     | . 78 |

| Figure 5.18 INL plot after SES-based calibration for one typical sample                     | . 78 |

## **List of Tables**

| Table 4-1 Comparison with prior works.                                           | . 53 |

|----------------------------------------------------------------------------------|------|

| Table 5-1 Performance summary of the SES-based CS-DAC.                           | . 63 |

| Table 5-2 Nominal current values for 12 sub-current sources in UCC               | . 76 |

| Table 5-3 Performance summary of the ESES-based CS-DAC with expected performance | . 80 |

### 1 Introduction

As CMOS technology continues to scale [1], digital circuits have leveraged the corresponding technology improvements to achieve better area, speed and power. In contrast, analog circuits have scaled sub-optimally with process technology. One important limiter is transistor random mismatch in CMOS technology that degrades the analog circuit performance, specifically accuracy and yield [2].

To combat the impact of transistor random mismatch on analog circuit performance, a straightforward method is to increase transistor sizes to improve matching properties. However, this is not favored since this method increases analog circuit area and also lowers circuit bandwidth.

A novel form of sizing based on redundancy at the subcomponent level, statistical element selection (SES), was proposed in [3] to address this challenge. The SES method provides combinatorial design choices to be digitally selected from among a large population, thus achieving excellent matching properties after selection. It has been shown that this combinatorial redundancy can be applied to analog designs for high resolution calibration, such as for tuning input offset of a differential pair [3]. However, the calibration tuning range of the SES method is purely determined by transistor random mismatch and this limitation of the tuning range makes SES methodology unsuitable for many calibration applications as a general calibration method.

To address this limitation and make the calibration range a design parameter, an extended statistical element selection (ESES) method is proposed here that is based on non-uniform sizing of the elements under selection. We have applied the ESES-based high resolution calibration method to two categories of calibration applications for analog and RF circuits, current

calibration and phase delay calibration. Our comparison of traditional calibrations methods for these applications indicates that our high resolution digital calibration method has lower calibration circuit overhead, improved calibration resolution and flexible circuit implementation.

As a demonstration for the proposed high resolution digital calibration method, we have designed a wideband harmonic rejection receiver using the ESES methodology. The ESES-based calibration is applied to correct both gain errors and phase errors. By having high calibration resolution, best-in-class 2<sup>nd</sup> to 6<sup>th</sup> order harmonic rejection ratios are achieved. Moreover, by calibrating gain errors and phase errors independently, both 3<sup>rd</sup> order and 5<sup>th</sup> order harmonic rejection ratios can be optimized simultaneously.

As another example, for the proposed high resolution digital calibration method we designed a current-steering D/A data converter (CS-DAC). We applied ESES-based current and phase delay calibration method to the CS-DAC design to correct amplitude error as well as timing errors of the thermometer coded MSBs' current cells in CS-DAC. After calibration, we can achieve much improved linearity performance.

This document is arranged as follows:

- Chapter 2 discusses the challenges for analog circuit design with the presence of transistor random mismatch. It surveys existing design methods to address the matching problems, including transistor sizing, SES method and traditional calibration methods.

- Chapter 3 describes our proposed high resolution digital calibration method, known as ESES, and compares it to the original SES method. Two types of calibration application based on ESES method are also described in this chapter.

- Chapter 4 presents a demonstration for the proposed ESES method by a design of harmonic rejection receiver. ESES based calibration method is applied to the receiver

design to achieve best-in-class harmonic rejection ratio. The implementation and testing of the design is detailed in this chapter.

- Chapter 5 presents a second example for the proposed ESES method by a design of CS-DAC. The amplitude and timing errors of the data converter are calibrated following ESES-based methods to achieve greatly improved linearity performance of the CS-DAC.

- Chapter 6 concludes with a discussion of key results as well as future research direction.

## 2 Background

#### 2.1 Random Mismatch in CMOS Technology

Transistor random mismatch poses a significant challenge for analog circuit design. As pointed out in [2], the matching properties of CMOS transistors, especially the threshold voltage mismatch, determine the yield and performance of many data converters. For the application of parallel analog signal processing, random mismatch can determine the equality of parallel signal paths, which has a great impact on the system performance.

With CMOS scaling, the matching properties of transistors become worse. As shown in [4], from technology node of 180 nm to 45 nm, the transistor feature size has scaled down by 4X, while the threshold voltage matching coefficient has only improved roughly by 2X. According to Pelgrom's transistor mismatch model [5], this would lead to an increase in threshold voltage mismatch if analog transistor sizes scale proportionally with process technology.

For sub-20nm CMOS, the FinFET has been the device of choice for volume production. The threshold voltage matching coefficient of the FinFET is shown to be low in [4] since the channel doping (a major source of variability in threshold voltage random mismatch) can be absent in fully depleted devices. However, line-edge roughness of the fins degrades the threshold voltage matching dramatically for deeply scaled nanoscale processes [6]. Moreover, the assumption of absence of channel doping may not hold true if channel doping is ultimately used for generating multiple threshold voltage flavors instead of having different gate work-functions, since the latter has significantly higher process complexity and cost [7]. Hence, analog circuit design will continue to suffer from transistor matching properties with FinFETs.

#### 2.2 Transistor sizing for Matching

Pelgrom's transistor mismatch model [5] shows that the standard deviations of the current factor and threshold voltage random variation are proportional to 1/ WL. So in order to improve matching, one straightforward method is to increase the transistor sizes W and/or L. However, this trade-off between area and matching has very low efficiency as the matching property improvement factor is only a square root of the area increasing factor. And increased transistor gate area is not favored as it results in increased gate capacitance and parasitic capacitance that decrease circuit speed and performance.

One example of relying on the intrinsic accuracy through Pelgrom type transistor sizing is for a high resolution current steering DAC (CS-DAC) design. In [8], a 14-bit CS-DAC was designed with each current cell sized sufficiently big enough to ensure certain matching property for achieving 14-bit static linearity. Area of the current cell array totaled more than 5 mm² in 0.5 µm CMOS technology, while dynamic performance of the CS-DAC greatly suffered from the resulting parasitic capacitance. Since the transistor matching property hasn't improved at the same pace as the process technology scaling, the CS-DAC design using Pelgrom type transistor sizing would produce proportionally larger analog circuit area, which mainly consists of overly sized current cells for matching purpose as technology process scales.

#### 2.3 Statistical Element Selection (SES) Design Methodology

Matching properties can be improved by redundancy. A traditional method to create redundancy is to have a large population of cells to choose from. Instead of only having one cell, redundancy is based on having N cells and choosing the best one from that population. Assuming these N cells follow the same independent distribution and the success rate of each cell passing certain specifications is  $P_{\text{success}}$ , then the total success rate of having N cells available for selection is 1-(1- $P_{\text{success}}$ )<sup>N</sup>, which is significant improvement over  $P_{\text{success}}$ . This method was incorporated in the flash ADC design in [9] to improve ADC linearity. Although traditional redundancy can improve the yield of the analog circuit design, the cost is very high (scales by N).

With statistical element selection (SES) that was proposed in [3], the approach is based on digitally selecting K elements from a set of N elements and sacrificing N-K elements, resulting in a combinatorial redundancy. The number of available combinations increases exponentially as N and K increase, enabling an exponential number of design choices that can be digitally selected. By having this combinatorial redundancy, the failure rate to pass certain specifications can be improved by orders of magnitude. Keskin et. al. demonstrated multiple orders of magnitude lowering of standard deviation of the comparator input offset voltage after optimal selection [10]. Therefore, the total area requirement for meeting certain matching properties is lowered dramatically, thereby consuming much smaller area, even when considering the sacrificial area that enables combinatorial redundancy. This design methodology can solve the transistor matching problem at a relatively low circuit overhead (usually a digital controller). And since there exists an exponential number of design choices aggregated around the nominal design value, this methodology also enables high resolution calibration within a small range.

#### 2.4 Calibration Methods for Current Sources and Phase Delays

#### **2.4.1** Current Sources Calibration Methods

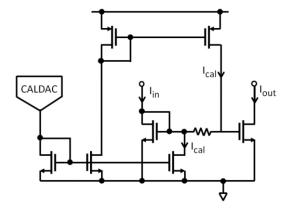

To address the transistor random mismatch problem for current sources, many calibration methods have been proposed. Current adjustment can be done by varying the bias voltage of the current source [11] [12]. By adding a serial resistor to the gate of the current source and supplying a small tunable current flowing through that resistor, the effective biasing gate voltage of the current source can be tunable. The current calibration circuit is shown in Figure 2.1. The major overhead of this method is the calibration DAC (CALDAC) and associated current mirror structure that can require significant area, as shown in [12].

Figure 2.1 Current calibration circuit based on varying gate voltage [12].

More directly, current adjustment can be done by adding small tunable current source in parallel to the current source under calibration. There are mainly two methods to create the small tunable current source. The first method is to tune the gate voltage of the added current source and use a capacitor to store the calibrated gate voltage value for use during normal operation [13] [14]. A conceptual diagram of this method is shown in Figure 2.2 (a). This method can share the CALDAC among all current sources under calibration. However, it also requires frequent refreshing of the capacitor to handle charge leakage. Moreover, the resulting calibration schemes

for this method presented in [13] [14] involve high analog circuit overhead that also suffers with process scaling. Another method is to attach the CALDAC current output directly in parallel to the current source under calibration [15] [16]. A conceptual circuit diagram of this method is shown in Figure 2.2 (b), which is more digital calibration orientated, but each current source needs one CALDAC. For high calibration accuracy, a very small least significant bit (LSB) current cell of CALDAC is needed for a small calibration step, which usually leads to LSB current cell design with much larger channel length than that of the current source under calibration. As a result, the area overhead for the CALDACs is observed to be high in [15] [16].

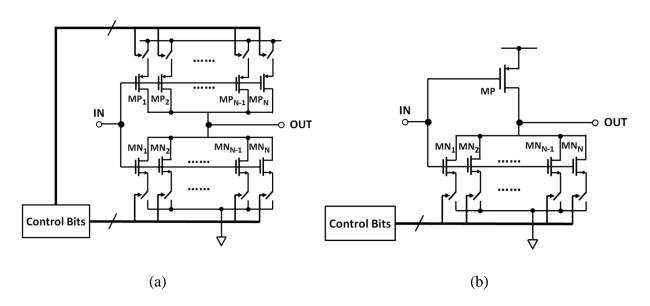

Figure 2.2 Conceptual circuit diagram of current calibration based on attaching extra current source (a) method one (b) method two.

#### 2.4.2 Phase Delay Calibration Methods

Phase delay matching also suffers from transistor random mismatch. Most of the phase delay calibration methods utilize one of the two existing tuning mechanisms for delay element: current-starved inverter [17] and shunt-capacitor inverter [18]. These techniques were proposed originally for digital delay-locked loops or digital phase-locked loops design with large tuning range. But they can also be modified to have finer tuning resolution to be applied to analog/RF designs where digital signals when high timing requirements are needed; e.g. timing skew requirement of time-interleaved ADC and phase offset requirement of multi-phase local

oscillator (LO).

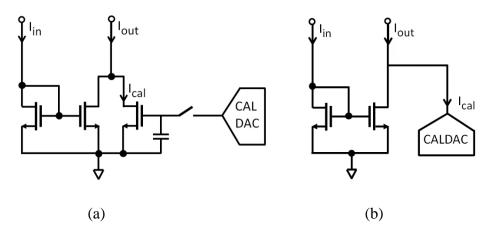

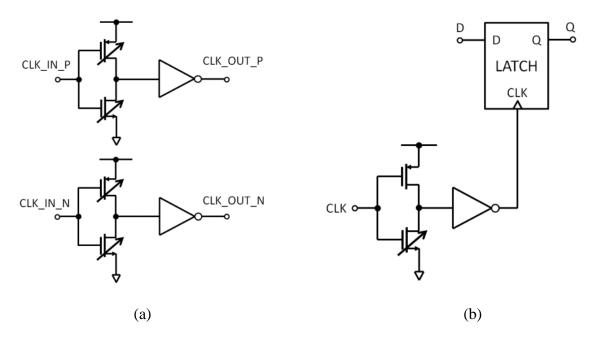

The current-starved inverter with analog control voltage [17] is shown in Figure 2.3 (a). The maximum current available to the inverter is controlled by the control voltage  $V_{ctrl}$ . By tuning this voltage, the delay become tunable and thus can be calibrated. A digital adaptation [19] is shown in Figure 2.3 (b), with current-starving transistors discretized and hence controlled digitally.

Figure 2.3 Current-starved inverter: (a) analog implementation; (b) digital implementation.

A shunt-capacitor inverter with analog control voltage [18] is shown in Figure 2.4 (a). An MOS capacitor is loading the inverter in series with one transistor. This transistor has tunable "on" resistance by varying control voltage  $V_{ctrl}$ , thus affecting the effective loading of the inverter and making the delay tunable. A digital adaptation shown in Figure 2.4 (b) was proposed in [20]. The idea is to break the big MOS capacitor into small capacitors in parallel, and tune the loading capacitance by digital control of the MOS capacitor's gate voltage.

Figure 2.4 Shunt-capacitor inverter: (a) analog implementation; (b) digital implementation.

The analog versions of these two calibration mechanisms involve high analog circuit overhead for generating the control voltage. Although the digital adaptations have much less circuit overhead, the calibration resolution is limited by the smallest current starving transistor or the smallest loading capacitor.

Another limitation of these calibration methods is that the output rising edge and falling edge cannot be tuned separately. This further limits their utility for applications where both edges are critical and need to be calibrated independently.

#### 2.5 Summary

In this chapter, we reviewed the matching challenges for the analog/RF circuit design in advanced CMOS technology node and a traditional upsizing technique that can improve transistor matching properties. A more efficient way to improve matching is through combinatorial redundancy and the associated design methodology is called statistical element selection. This method can dramatically improve the yield of the analog circuit design. Traditional calibration methods for current sources and phase delay were also reviewed in this chapter.

## 3 High Resolution Calibration Approach

The original SES methodology enables high resolution calibration within a small range determined by its own random variations. However, the very limited and uncontrollable calibration range makes it unsuitable for many applications. We propose an extended statistical element selection approach that provides for a wider calibration range that can be controlled during the design process. With these features, this new approach can be used as a general calibration method for high resolution purpose. Two types of calibration based on the new design methods are further proposed, which are current calibration and phase delay calibration.

#### 3.1 Extended Statistical Element Selection (ESES)

#### 3.1.1 Limitations of SES

For the original SES methodology the distribution of the combined K-element is created by the random variation of the equally-sized N elements [3], and a large number of combinations aggregate around the center of the design choices distribution. The clustering effect of SES creates an area of ultra-high density of combinations as available design choices for selection, and therefore, high calibration resolution can be realized around the nominal design value.

However, once the calibration target window deviates from the nominal design value, the calibration success rate drops rapidly. This is because distribution density of the available design choices decreases dramatically as the target window deviates from the center; therefore much less design choices are available for selection in that area, resulting in lowered probability of finding a design choice falling in the target window.

Moreover, the entire calibration range created by the SES method purely depends on the

random variation of the elements. The only way to change the calibration range is to purposely change the sizes of the equally-sized N elements, thereby changing their random variations. But this might not be favored as this would also change the circuit performance. In short, the calibration range of the SES method cannot be set independently.

These limitations of the original SES method do not create a big problem if the equally-sized N elements are the only variation source or the strongly dominant variation source in the design. The calibrated result of the combined K-element has to cancel out the impact from other variations sources in the design. If all other variation sources are negligible, the calibration target of the combined K-element can be bounded in a very small region around the nominal design value. Also there is no need for a larger calibration range in this case to cover any outlying calibration targets. As one example, a comparator design with SES-based input offset voltage calibration was shown in [3]. The input differential pair is the dominant variation source for the input offset voltage. Therefore, applying the SES method on the input differential pair can successfully calibrate the input offset voltage to be minimal.

Once there are other non-negligible variation sources, other comparable variation sources or even other dominant variation sources in the design, the calibration target of the combined K-element is determined by the random variation of the other sources. The location of the calibration target can be far away from the center of the design choices distribution or simply out of the calibration range created by the random variations of the equally-sized N elements. In these cases, SES method would be less effective or even not applicable.

In summary, the original SES methods has limited tuning range to counter other variation sources in the design. Without involving another level of coarse calibration preceding the SES based calibration, it has limited application as a general calibration method.

#### 3.1.2 ESES Method Overview

To increase the tuning range and to accommodate other dominant variation sources, we propose a design method called extended statistical element selection (ESES). The ESES design method has non-uniformly-sized N elements. For example, the N elements can be sized as an arithmetic sequence. Meanwhile, still K elements are selected out of the N elements, providing the same combinatorial redundancy as the original SES method. For this ESES method, the overall size of the combined K-element already spans a range for the nominal case, and this range can be controlled by the nominal sizes of the elements as a design parameter. In the case of using arithmetic sequence for the sizes, the distribution range in the nominal case can be controlled by the common difference of the arithmetic sequence while keeping the center value unchanged. With random variation considered in, the distribution of overall size of combined K-element creates a wider calibration tuning range. This proposed ESES method will effectively trade high distribution density around the center of the design choices distribution for a wider tuning range.

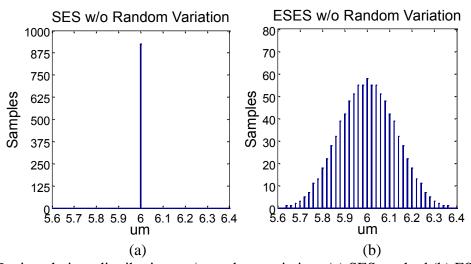

As an example, we apply combinatorial redundancy to transistor width by breaking a large transistor into multiple segments and selecting a subset of the segments. The distributions of all available SES/ESES design choices are shown in Figure 3.2. In this example, both SES and ESES methods have parameters of N=12 and K=6. This generates 924 available design choices with each one having 6 segments selected. The nominal transistor width for each segment is set as 1  $\mu$ m for SES method; and for ESES method, nominal widths are set as an arithmetic sequence of 12 numbers centered at 1  $\mu$ m and with a gap of 0.02  $\mu$ m for two adjacent segments (i.e., an arithmetic sequence of 0.89  $\mu$ m, 0.91  $\mu$ m, ..., 1.09  $\mu$ m, 1.11  $\mu$ m with a common difference of 0.02 $\mu$ m). Although there are slight nominal sizing differences, the standard deviation of all segments are set as 0.01  $\mu$ m. The histogram bin width in Figure 3.2 is

set as 0.004 µm. As shown in Figure 3.2 (a), without random variation considered in, all design choices of SES are the same therefore forming a single bin in the distribution. Figure 3.2 (b) shows that with ESES method, even without random variation, the 924 design choices create a wide distribution range. With random variation considered, Figure 3.2 (a) shows that SES method creates a relatively small calibration range, which is purely created by the segments' own random variation. However in Figure 3.2 (b), the ESES method creates a much wider distribution that roughly follows the shape as in Figure 3.2 (b), of which the shape is pre-determined by nominal transistor sizing.

Figure 3.1 Design choices distributions w/o random variation: (a) SES method (b) ESES method.

Figure 3.2 Design choices distributions w/ random variation: (a) SES method (b) ESES method.

#### 3.1.3 ESES Calibration Resolution and Calibration Range Study

In this section we study the calibration resolution and calibration range of the ESES design method with the comparison to the SES design method. In this study, both SES and ESES methods have parameters of N = 12 and K = 6. As shown in [3], different N, K settings have different calibration yield performance, calibration time (due to different sizes of searching space) and utilization ratios. A setting of N = 12 and K = 6 is picked here as an example to demonstrate the advantages of the ESES method over the SES method, while the following experiments can also be applied to different N, K settings while arriving similar conclusions drawn in this section.

For the SES method, all elements have a nominal size of 1 µm and the standard deviation is set as 0.01 µm. Hence, the size of a combined K-element has a nominal value of 6 µm and a standard deviation of  $6 * 0.01 \mu m = 0.0245 \mu m$ . We denote the standard deviation of the subset that has K elements as k and this value is used as a unit for normalizing calibration resolution and calibration range. For the ESES method, the nominal sizes of the 12 elements are set as an arithmetic sequence. The average value of the arithmetic sequence is denoted as a<sub>ESES</sub>, which is set as 1 µm if not otherwise stated. The common difference of the arithmetic sequence is denoted as d<sub>ESES</sub>. The standard deviations of each element in the ESES method are calculated based on the assumption that the standard deviation of each element is proportional to the square root of its nominal size. The center value of the standard deviations of the 12 elements is also set as 0.01 um for fair SES/ESES comparison purpose. For each experiment, a calibration target window size, denoted as T<sub>window</sub>, is set in the unit of k. This T<sub>window</sub> value shows the calibration resolution with respect to the standard deviation of the K-element. Once the overall size of the subset (the K elements that are selected) falls into that target window, the calibration process is marked as successful. If we assume the combination falling into the target window follows a uniform

distribution, then after calibration the standard deviation of the selected subset decreases to  $T_{window}$ / 12. The location of the center of the target window is described by its offset from the nominal design value (in this example, this value is 6  $\mu$ m). This offset of the center of the target window is denoted as  $T_{offset}$ . This value is also in the unit of  $_k$ , and it shows how far away the calibration target can be from the nominal design value.

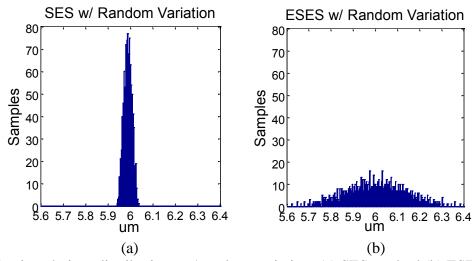

We first study the trade-off between calibration success rate and calibration target window size when the calibration target is right at the nominal design value (T<sub>offset</sub> = 0). For the ESES method, a set of different values for common difference of the arithmetic sequence are analyzed, which are d<sub>ESES</sub> =  $_k/4$ ,  $_k/2$ ,  $_k$  and 2  $_k$ . The target window size T<sub>window</sub> varies from  $_k/100$  to  $_k/5$  in this experiment. For each different SES/ESES setting and target window size, we run the Monte Carlo simulation with  $10^5$  samples. Figure 3.3 shows the relationship between calibration failure rate and calibration target window size. In order to have a closer look at the region where success rate is very close to 100%, failure rate in log scale are shown in this figure.

Figure 3.3 SES/ESES calibration failure rate vs. calibration target window when  $T_{offset} = 0$ .

From Figure 3.3, we can see that the SES method only shows advantage over the ESES method in terms of lower calibration failure rate when the calibration target window size Twindow is set as minimum. As Twindow increases the failure rate of the ESES method improves much faster than that of the SES method improves. Especially at the region where calibration failure rate is lower than 10% as shown in Figure 3.3, the ESES method is dominating the SES method for providing higher calibration yield. The inefficiency of the SES method when the calibration target is right at the nominal design value can be explained as follows: although SES provides more design choices than ESES does at the center of the design choice distributions as shown in Figure 3.2 (a) and Figure 3.2 (b), which supposedly translate to higher calibration yield for the SES method at that region, the center of the design choices distribution is not the calibration target for  $T_{offset} = 0$ . The calibration target is always a constant. And in the case of  $T_{offset} = 0$ , the calibration target is the nominal design value, which is exactly 6 µm in this example. Meanwhile the center of the design choices distribution is a random variable. It is determined by the sizes of the N elements that are available in each sample. Therefore, statistically, the center of the design choices distribution of the SES method can be far away from the nominal design value. And because SES has a very sharp distribution, as shown in Figure 3.2 (a), the misalignment between the center of the design-choices distribution and the nominal design value can result in a very small number of design choices at the nominal design value. Meanwhile for the ESES method, as the design choices have a much wider distribution, the misalignment between the center of the design choices and the nominal design value has less impact on the design choices density at the nominal design value. Therefore, although SES has more design choices around the center of the design choices distribution, it does not translate to a higher calibration yield as compared to ESES when the calibration target is the nominal design value.

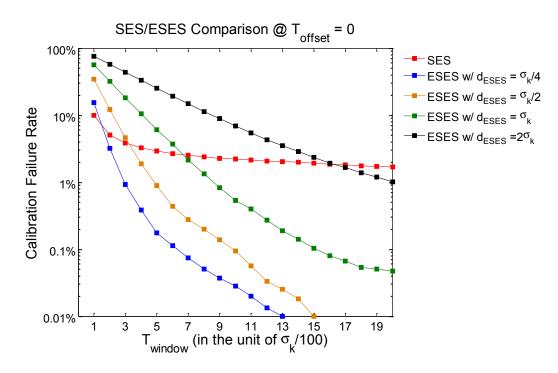

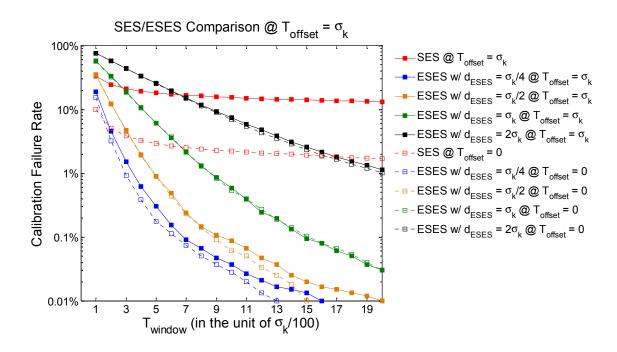

As the calibration target location deviates from the nominal design value as  $T_{offset}$  increases, the ESES design method is showing increasing advantages over the SES method. Figure 3.4 shows the calibration failure rate vs.  $T_{window}$  for  $T_{offset} = \ _k$  in solid lines, while dotted lines show the results for  $T_{offset} = 0$  for comparison. The failure rate for  $T_{offset} = \ _k$  increases dramatically for the SES method for almost one order of magnitude as compared to the case of  $T_{offset} = 0$ . Meanwhile for the ESES method, the calibration failure rate only increases marginally as  $T_{offset}$  increases to  $\ _k$ .

Figure 3.4 SES/ESES calibration failure rate vs. calibration target window when  $T_{offset} = k$ .

Figure 3.5 SES/ESES calibration failure rate vs. calibration target window when  $T_{offset} = 3$  k.

As  $T_{offset}$  keeps increasing, we very soon reach a point that the SES method is no longer usable for calibration while the ESES method is still effective. Figure 3.5 shows the calibration failure rate vs.  $T_{window}$  for  $T_{offset} = 3$   $_k$  in solid lines, while dotted lines show the results for  $T_{offset} = 0$  for comparison. For the SES method, the calibration failure rate is almost 100% when  $T_{offset} = 3$   $_k$ . For the ESES method, the calibration failure rate for the case of  $d_{ESES} = \frac{1}{k}$ 4 also increases significantly, which means the calibration range of this specific ESES setting is not sufficient for  $T_{offset} = 3$   $_k$ . But as  $d_{ESES}$  increases, the ESES method can still provide very low calibration failure rate. For example, when  $d_{ESES} = \frac{1}{k}$ 2 and  $T_{window} = 7$   $_k$ 7100, the calibration failure rate is down below 1%.

The aforementioned experiments are all performed at fixed  $T_{offset}$  values. In a more realistic calibration environment, the deviation of the calibration target from the nominal design value is determined by the random variations of other variation sources in the design. Therefore, in the

next experiment we assume  $T_{offset}$  is a random number that follows a normal distribution N(0,  $_{\rm T}$ ), where  $_{\rm T}$  shows the total variation coming from the other variation sources in the design. Before calibration, overall standard deviation in the design, denoted as  $_{\rm All}$ , can be calculated as  $_{\rm All}$  = (  $_{\rm k}^2$ +  $_{\rm T}^2$ ). As aforementioned, after successfully performing calibration, the standard deviation can be reduced to  $T_{\rm window}$ / 12 as the calibrated values are all bounded in a small calibration window. To show the benefit of the calibration, we further define the ratio of  $_{\rm All}$  and  $T_{\rm window}$ / 12, denoted as  $R_{\rm cal}$ , as the standard deviation reduction factor of the calibration method. For the following experiments,  $_{\rm T}$  is set as  $_{\rm k}$ /4,  $_{\rm k}$  and 2  $_{\rm k}$ . These three values correspond to three scenarios: other variation sources in the design are negligible, comparable or dominant as compared to the variations of the N-element undergoing SES/ESES based calibration process. Figure 3.6 to Figure 3.8 show the calibration failure rate vs. calibration target window size for these three scenarios respectively.

Figure 3.6 SES/ESES calibration failure rate vs. calibration target window when  $T_{offset} \sim N(0, k/4)$ .

Figure 3.7 SES/ESES calibration failure rate vs. calibration target window when  $T_{offset} \sim N(0, k)$ .

Figure 3.8 SES/ESES calibration failure rate vs. calibration target window when  $T_{offset} \sim N(0, 2_k)$ .

In Figure 3.6, where the other variation sources in the design are negligible, the calibration failure rate of the SES method is much higher than 1%. However for the ESES method, calibration failure rate can be much lower than 1% depending on the value of calibration target window. For example, for  $T_{window} = 3 \text{ k/100}$ , which corresponds to a standard deviation reduction factor  $R_{cal}$  of 115, the calibration failure rate is less than 1% with  $d_{ESES} = \text{ k/4}$  for ESES method.

In Figure 3.7 and Figure 3.8, where  $_{\rm T}$  increases to  $_{\rm k}$  and 2  $_{\rm k}$  such that other variation sources become comparable or dominant to the N-element, the calibration failure rate of the SES method becomes unacceptable, as it is much higher than 10%. On the other hand, the ESES method still exhibits very low calibration failure rate for certain calibration windows. For example, if we still target at a calibration failure rate less than 1%, for  $_{\rm T}$  =  $_{\rm k}$  (Figure 3.7), we can obtain a  $_{\rm Cal}$  of 98 when  $_{\rm deses}$  =  $_{\rm k}$ /4 and  $_{\rm Twindow}$  = 5  $_{\rm k}$ /100; for  $_{\rm T}$  = 2  $_{\rm k}$  (Figure 3.8), we can obtain a  $_{\rm Cal}$  of 111 when  $_{\rm deses}$  =  $_{\rm k}$ /2 and  $_{\rm Twindow}$  = 7  $_{\rm k}$ /100.

The above experiments show that the ESES method is effective to perform calibration with more than 99% calibration success rate while achieving a standard deviation reduction factor of around 100 in all three scenarios. This also means that the matching property after calibration is improved by approximately 40 dB.

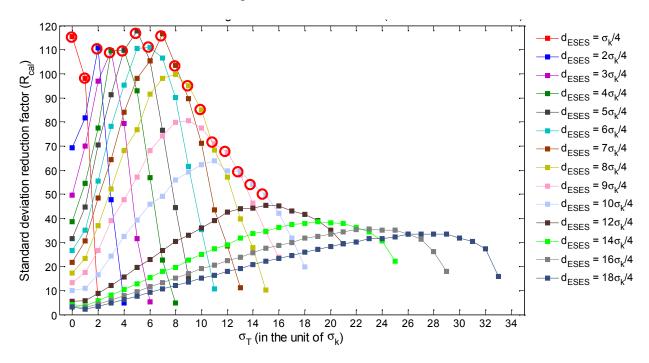

While  $R_{cal}$  shows the matching improvement the ESES method can provide,  $_{T}$  (in the unit of  $_{k}$ ) shows the amount of variations from other variation sources that the ESES method can handle. A higher  $_{T}$  value means the ESES method needs to provide a larger calibration range to cover the overall variations. In the following experiment, we further study how much matching improvement we can achieve while we keep increasing  $_{T}$ . Assuming our calibration yield target is greater than 99%, Figure 3.9 shows the relationship between standard deviation reduction factor  $R_{cal}$  and  $_{T}$  (in the unit of  $_{k}$ ). As we can see from the figure, different  $d_{ESES}$  settings are

needed to achieve optimal  $R_{cal}$  at different  $_T$  values. For example, the ESES method can achieve an  $R_{cal}$  value around 100 when  $_T$  is no greater than 9  $_k$ . As  $_T$  keeps increasing, the achievable  $R_{cal}$  value decreases. In order to obtain an  $R_{cal}$  value greater than 50,  $_T$  can be as large as 15  $_k$ . In both aforementioned  $R_{cal}$  targets, the allowable  $_T$  value can be almost one order of magnitude larger than  $_k$ . These numbers show that even the variations from other sources are much larger than those of the N-element, we can achieve very large matching property improvement by using the ESES method which leads to high-resolution calibration results.

Figure 3.9 ESES calibration standard deviation reduction factor R<sub>cal</sub> vs. <sub>T</sub> with more than 99% calibration success rate.

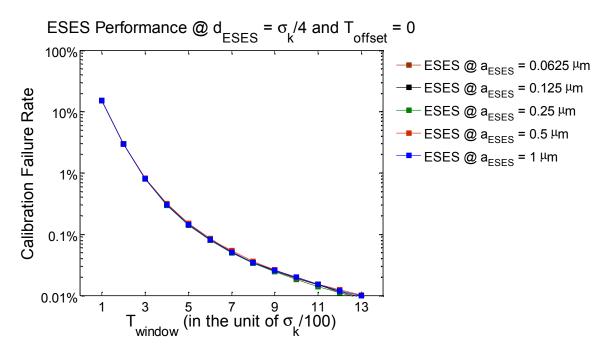

For the ESES method, which uses arithmetic sequence for element sizing, all of the previous simulation results are obtained by setting the average value of the sequence (denoted as  $a_{ESES}$ ) to be 1  $\mu$ m. We also assumed that the standard deviation of each element is proportional to the square root of its nominal size, and then set the center value of the standard deviation for the distribution of the 12 elements to be 0.01  $\mu$ m. This results in a relative standard deviation for

each element to be about 1% before calibration, which is considered as a very good starting point for matching. If we have a worse starting point for the relative standard deviation, it can be shown that the simulation results obtained previously still withstand. For example, we now set the a<sub>ESES</sub> value to be 1 $\mu$ m, 0.5  $\mu$ m, 0.25  $\mu$ m, 0.125  $\mu$ m or 0.0625  $\mu$ m, while keeping the center value of the standard deviations of the 12 elements fixed at 0.01  $\mu$ m. As a result, the relative standard deviation of each element is approximately 1%, 2%, 4%, 8% and 16% respectively before calibration. We also set d<sub>ESES</sub> =  $_{k}$ /4 for all a<sub>ESES</sub> cases. Now, for the extreme case when a<sub>ESES</sub> = 0.0625  $\mu$ m, the nominal sizes for the 12 elements are of an arithmetic sequence starting from 0.0288  $\mu$ m to 0.0962  $\mu$ m, with a common difference of 0.0061  $\mu$ m. Whereas for a<sub>ESES</sub> = 1  $\mu$ m, the nominal sizes range from 0.9663  $\mu$ m to 1.0337  $\mu$ m for the 12 elements, while having a same common difference of 0.0061  $\mu$ m for the arithmetic sequence. The simulation results for the calibration failure rates when T<sub>offset</sub> = 0 are shown in Figure 3.10 for different a<sub>ESES</sub> settings.

Figure 3.10 ESES calibration failure rate for various  $a_{ESES}$  settings when  $T_{offset} = 0$ ,  $d_{ESES} = k/4$

As observed from Figure 3.10, the simulation results for different  $a_{ESES}$  values almost overlap with each other. Similar behaviors can be observed for different  $T_{offset}$  settings and different  $d_{ESES}$  settings. This suggests that the results obtained in this section do not lose generality because of the specific relative standard deviation settings (around 1% for each ESES-based element) that we have used in the aforementioned example.

To summarize the results of the experiments in this section, by using the proposed ESES method we can utilize combinatorial redundancy in a non-dominant variation source to calibrate the dominant variations in the design and still achieve large improvement for the matching property. This proposed calibration method extends the usage of combinatorial redundancy for general high-resolution calibration applications. As the calibration location no longer has to be the dominant variation source, it provides the flexibility of choosing a suitable location in the design for applying combinatorial redundancy. Two types of applications, current calibration and phase delay calibration, are considered in the following sections.

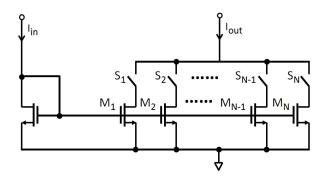

#### 3.2 ESES-based High Resolution Current Calibration

The combinatorial redundancy based ESES method can be applied to current calibration to achieve high calibration resolution with more than one order of magnitude matching property improvement. Consider the conceptual circuit shown in Figure 3.11. The current source under calibration is split into N non-uniformly sized sub-current sources, with each one controlled by a switch and only K of the N sub-current sources are activated. During calibration, different K subsets can be tested in order to find the optimal selection from the built-in combinatorial redundancy. The number of available combinations increases exponentially as N and K increase, providing a large number of calibration choices and enabling high calibration resolution. The applied ESES method provides higher calibration range as compared to SES method to accommodate extra variation sources if any. Even in the case of there is no extra variation source of the current source in the design, ESES can provide higher calibration success rate as shown in Figure 3.3.

Figure 3.11 Conceptual circuit of ESES-based current calibration.

In contrast to traditional current calibration, the ESES-based high resolution current calibration method does not involve the overhead of a CALDAC, as seen in other calibration methods. The major overhead of this method is the sacrificed circuit area of N-K unselected subcurrent sources. However, as pointed out in [3], the combinatorial redundancy dramatically

relaxes the area requirement for achieving certain CMOS matching properties. As a result, even considering the sacrificial area, the total area for current source can be reduced significantly (as compared with traditional sizing) when meeting the high matching requirement.

There are various applications for the ESES-based high resolution current calibration method. One direct application for current source calibration is segmented CS-DACs, where the current matching for the thermometer coded several bits MSBs is critical for achieving good D/A linearity. The high resolution current calibration method can be applied to the MSBs unary current sources to optimize matching properties. This application is shown in the design of a ESES-based CS-DAC in section 5.3.1.

Another application is for differential amplifier transconductance calibration. A conceptual circuit is shown in Figure 3.12. The tail current source of the differential amplifier is split into several sub-current sources to create combinatorial redundancy. As the transconductance of the differential pair is set by the DC biasing current, by tuning the biasing current, the transconductance is effectively calibrated. This application is demonstrated in the design of a transconductance amplifier that is described in section 4.3.2.

Figure 3.12 Conceptual circuit of ESES-based differential amplifier transconductance calibration.

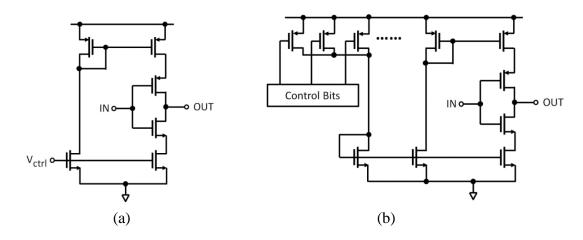

## 3.3 ESES-based High Resolution Phase Delay Calibration

The combinatorial redundancy can further be applied to phase delay calibration for high calibration resolution and the conceptual circuit is shown in Figure 3.13 (a). The idea is to break the NMOS and PMOS transistors into N elements, and select a subset of them by adding big switches at their drain nodes (to minimize "on" resistance of the switch). The ESES design methodology with wider tuning range is suitable for phase delay calibration since a chain of logic gates is usually involved in the design and the delay variation generally not only comes from a single stage. By using the ESES methodology, calibration performed in one inverter stage can potentially cover the delay variations coming from the entire logic chain.

Different from existing phase delay calibration methods, the circuit shown in Figure 3.13 (a) has the capability of tuning the rising edge and falling edge of the inverter output independently. If only one edge is needed for calibration, e.g. falling edge, the circuit can be simplified, as shown in Figure 3.13 (b).

Figure 3.13 Conceptual circuit of ESES-based phase delay calibration: (a) tunable rising and falling edge; (a) tunable falling edge only.

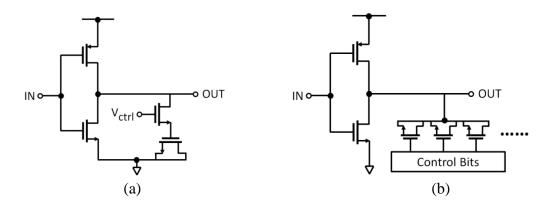

This high resolution phase delay calibration can be applied to various circuit designs. The delay of asynchronous signals can be calibrated directly using this calibration technique. One application for analog/RF design is the calibration of a pair of differential clocks. As shown in Figure 3.14 (a), a pair of differential clocks CLK\_IN\_P and CLK\_IN\_N pass through a pair of tunable inverters (Figure 3.13 (a)) and one more pair of inverters for buffering. By calibrating both the rising edges and falling edges, the even-order harmonics for the differential output (CLK\_OUT\_P – CLK\_OUT\_N) can be minimized. This can improve even-order distortions for analog/RF design driven by the differential clock pair. One implementation of this application is shown in section 4.3.5.

Figure 3.14 Conceptual circuits for high resolution phase delay calibration applications: (a) differential signals calibration; (b) delay calibration of synchronous signals.

Many digital signals used in analog/RF design have to be synchronous, e.g. switching signals for D/A converter and multi-phase LO signals generated by a frequency divider. For those signals, the delay calibration can be done indirectly on the clocking signals. Figure 3.14 (b) shows the application of delay calibration for synchronized signal Q. Assume that the latch is

transparent when clock is high and there is no switching activity of D when clock is high. The clock signal is passed through a tunable inverter (Figure 3.13 (b)) to calibrate the rising edge for the latch's clock input, hence calibrating the transitioning timing of output signal Q. The benefit of calibrating over clocking signals instead of output Q signal directly is that the former one applies to all signals generated by this latch. This is especially useful for analog/RF design where differential latches with differential outputs are widely used. One implementation of delay calibration for synchronous signals is presented in section 4.3.5 for the design of a multi-phase LO generator circuit. A second implementation is shown in section 5.3.2 for the design of a differential latch with delay and duty-cycle calibration.

## 3.4 Summary

In this chapter, a new design method call extended statistical element selection (ESES) was introduced. The ESES method can provide wider calibration range as well as higher calibration yield as compared to the original SES method. The new method also enables the flexibility of the calibration location in a design. With these advantages, the ESES method can be applied to a broader range of applications as compared to SES while still providing high calibration resolution. Two types of ESES-based calibration were also introduced in this chapter. One is current source calibration, and the other is phase delay calibration. Applications for both types are further discussed. In the next two following chapters, we are going to present two circuit designs that are utilizing ESES-based calibration methods.

# 4 Harmonic Rejection Receiver Design

The harmonic rejection scheme presented in [21] can be applied to a wideband receiver design for rejecting interferences at local oscillator's harmonic frequencies. However, the achieved harmonic-rejection ratio highly depends on the gain matching and phase matching. As a demonstration of the proposed ESES-based high resolution calibration method, we present a design of a harmonic-rejection receiver that utilizes ESES for gain and phase calibration that achieves best-in-class harmonic-rejection ratios.

## 4.1 Harmonic Rejection Receiver Overview

#### 4.1.1 Harmonic Rejection Scheme and Impacts of Gain and Phase Errors

Due to the proliferation of wireless devices and standards, software defined radio (SDR) has become an increasingly interesting research area for radio architectures, not only to replace multiple narrow-band radios with reduced size and cost, but also because SDR is an important enabler for future cognitive radios with dynamic, intelligent, and thus efficient spectrum usage.

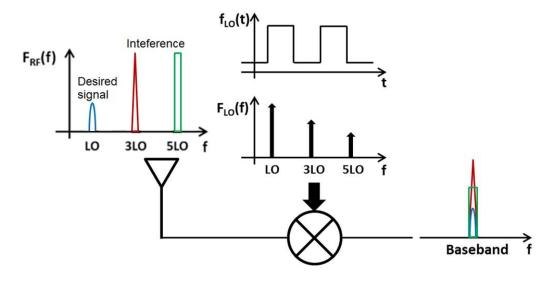

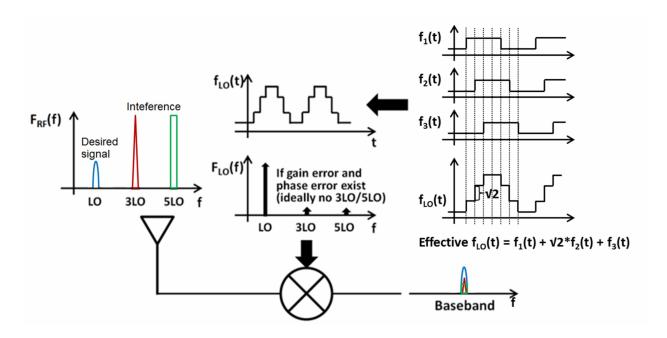

On the receiver side, SDR needs to support the reception of signals in multiple frequency bands with different radio standards. Thus a wideband receiver seems to be an obvious solution for a SDR receiver [22]. However, wideband receivers not only receive the desired signal, but also interfering signals, which can ultimately degrade receiver performance. In particular, interfering signals at harmonics of the local oscillator (LO) are especially problematic. Figure 4.1 illustrates the reception of interference at LO harmonic frequencies. Harmonics of the LO downconvert the interference to the same frequency as the desired signal thereby reducing the signal-to-noise ratio. The interfering signals need to be rejected down to thermal noise levels to

minimize the desensitization of the receiver. This rejection is typically performed with a band-select filter but this solution is not ideal for SDRs. In [22] it was shown that a -40 dBm to 0 dBm interferer at the harmonics of the LO requires a rejection ratio of 60 dB to 100 dB.

Figure 4.1 Reception of interference at LO harmonic frequencies for wideband receiver.

A harmonic-rejection mixer scheme, which was first proposed in [21] for a transmitter design, has been widely adopted in modern wideband RF receiver designs [23] [24] [25] [26] [27] [28] [29] [30] to alleviate the wideband interference problem. The basic idea is to construct an equivalent LO signal that is free of 3<sup>rd</sup> and 5<sup>th</sup> order harmonics, such that the 3<sup>rd</sup> and 5<sup>th</sup> order harmonic interferer would not be down-converted by the mixer, therefore being completely rejected. To achieve this, three LO signals need to be generated with a 45° phase shift from one to another and summed up by a weighting ratio of 1: 2:1. However, the harmonic rejection effect degrades as the phase shift deviates from 45° and gain ratio deviates from 2. Practically, with gain errors and phase errors considered in that are due to CMOS technology process variation as well as difficulties of generating the irrational number of 2, the achievable harmonic rejection ratio (HRR) is limited to 30-40 dB [23]. Figure 4.2 illustrates that a harmonic

rejection wideband receiver still has limited harmonic rejection effects if gain errors and phase errors exist.

Other than 3<sup>rd</sup> and 5<sup>th</sup> order harmonic interference, wideband receivers also need to reject even-order harmonic interference, specifically 2<sup>nd</sup>, 4<sup>th</sup> and 6<sup>th</sup> order harmonics, which are still not far enough away from the desired signal band to allow for simple filtering. Fortunately, the differential nature of the mixer operation makes the wideband receiver ideally immune from even-order harmonic interference. If the mixer has perfect differential phase, meaning exactly180° of phase shift between the differential signals, the even-order harmonic rejection ratio is infinite. However, in reality the phase deviates from 180° resulting in degraded even-order HR performance. In [22], the second order HRR (HRR<sub>2</sub>) was reported as 62 dB at 0.8 GHz LO frequency. At higher frequency bands, the effect of phase mismatch would be more critical, thereby resulting in even worse HRR performance.

Figure 4.2 Reception of interference at LO harmonic frequencies for harmonic rejection wideband receiver with gain errors and phase errors.

#### 4.1.2 Previous Work on Achieving High HRR

Generating the irrational number of 2 accurately has been a very difficult task to do on chip for achieving high 3<sup>rd</sup> and 5<sup>th</sup> order HRR (HRR<sub>3</sub>, HRR<sub>5</sub>). It is usually done through approximating 2 by 3/2, 7/5, 17/12, or 41/29, with increasing HRR performance in this order. The maximum achievable HRR<sub>3,5</sub> with a 41/29 approximation is more than 77 dB. However, considering random variations in CMOS processes, this theoretical number is difficult to achieve. To solve the gain mismatch problem of the HR mixer, a two-stage HR scheme was proposed in [24], and has been widely adopted recently [25] [26] [31]. The fundamental idea is to perform HR operations twice in baseband, such that the combined HRR is the summation of the HRR of the two stages. The authors also proved in [22] that the overall gain error is the multiplication of the gain errors of the two stages. Therefore, a very small overall gain error can be achieved. The authors successfully approximate 41/29 with negligible gain errors in [24], which can potentially reach an HRR of more than 77 dB. While this approach accounts for gain mismatch, it cannot improve the errors coming from LO phase mismatch. As the first stage and second stage suffer from the same LO phase error, the correlated phase errors in two stages do not benefit from this two-stage operation. Therefore, LO phase mismatch limits the achievable HRR of the two-stage HR to approximately 60 dB without extra RF filtering [24] [25] [26] [31]. Furthermore, this phase mismatch increases with RF frequency, thus further limiting the usage of the two-stage HR scheme in higher frequency bands. It is also worth mentioning that this method requires extra baseband circuitry to perform the second-stage HR operation.

In addition to relying on the intrinsic matching of CMOS process, calibration methods [27] [28] have also been proposed to increase the HRR. These methods rely on a common technique for which gain mismatch cancels phase mismatch. However, different phase and gain setting are needed to optimize HRR<sub>3</sub> and HRR<sub>5</sub>, respectively, resulting in the optimization of either HRR<sub>3</sub> or

HRR<sub>5</sub>, not both. In [27] and [28] the authors calibrate the gain mismatch of the HR mixers and achieve HRR<sub>3</sub> of approximately 70 dB. However, a degradation of HRR<sub>5</sub> after HRR<sub>3</sub> calibration is reported in [27]. In [29], both gain and phase are tunable and the achieved HRR<sub>3</sub> is limited to 65 dB. Although these techniques cannot optimize HRR<sub>3</sub> and HRR<sub>5</sub> concurrently, they are still useful when the system is able to detect a single harmonic jammer and re-configure the calibration.

Other than these aforementioned traditional circuit calibration techniques, a unique HR scheme with adaptive interference cancellation was proposed in [30]. This scheme dynamically estimates and then subtracts harmonic interference at the baseband in digital domain. To do so requires a total of four baseband ADCs, which is the major circuit overhead for this scheme. Although the reported HRR can be more than 80 dB, as the technique can only estimate one interference signal, it ends up either rejecting 3<sup>rd</sup> order harmonic or 5<sup>th</sup> order harmonic interference.

In summary, the previous techniques have all failed to achieve simultaneous HRR<sub>3</sub> and HRR<sub>5</sub> above 70 dB. In addition, as mentioned in section in 4.1.1, even-order harmonic rejection, specifically 2<sup>nd</sup> order, 4<sup>th</sup> order and 6<sup>th</sup> order HRR (HRR<sub>2</sub>, HRR<sub>4</sub>, and HRR<sub>6</sub>) are also important for receiver performance and need to be taken care of to achieve high HRR values. Not many previous works have addressed this problem. In [29] a duty-cycle calibration is performed to calibrate HRR<sub>2</sub> and the resulting even-order rejection is reported to be greater than 65 dB.

## 4.2 ESES-based Harmonic Rejection Receiver Design

To overcome the aforementioned shortcomings of the previous solutions, we are aming to design an HR receiver that can achieve high HRR values for 2<sup>nd</sup> to 6<sup>th</sup> order harmonic interference simultaneously and high HRR values for high frequency bands. As an example of the ESES-based calibration method we applied it for the HR receiver calibration. To achieve better HRR, a digital calibration scheme is used to tune both gain mismatch and phase mismatch for HRR3,5. Gain mismatch and phase mismatch can be decoupled and calibrated independently following ESES method. Phase mismatch for HRR2,4,6 can also be calibrated by ESES method. With the calibration accuracy provided by ESES approach, better HRR2-6 can be expected at not only low frequency band but also high frequency band.

Our proposed HR receiver architecture is shown in Figure 4.3. For simplicity, all paths are drawn as single-ended but in the actual implementation only the RF input is single-ended while the rest of the receiver is fully differential. The receiver frontend starts with an LNA, which performs single-ended to differential conversion while achieving low noise figure using noise-cancellation technique [32]. The LNA is followed by a transconductance (G<sub>m</sub>) stage, which is a fully differential design for better second order in-band linearity [33]. The Gm stage is followed by a standard passive mixer and baseband transimpedance amplifier (TIA) hereafter. The TIA is realized as an operational transconductance amplifier (OTA) configured in closed loop. For HR operation, four branches are created after the LNA and they are followed by a harmonic recombination stage for each respective I and Q path. A switch preceding each TIA is used to turn each branch on or off, which is needed in the ESES calibration process.

Gain mismatch calibration in the HR receiver is achieved by tuning the gain of the Gm stage with the ESES method, as described in the upcoming section 4.3.2. The harmonic recombination

stage for both I and Q paths is designed as weighted resistors and a summing TIA stage. The weighting ratio for the  $0^{\circ}$ ,  $45^{\circ}$  and  $90^{\circ}$  branches is 12:17:12. The inherent limitation of this weighting ratio is also accounted for by using the ESES method.

The phases of the multi-phase LO generator are designed to be tunable by utilizing the ESES method for calibrating various phase mismatches in the HR receiver. This is covered in the upcoming section 4.3.5.

Figure 4.3 HR receiver architecture with ESES-based calibration.

## 4.3 Chip Implementation

#### 4.3.1 LNA Design

Figure 4.4 LNA circuit design.

The LNA circuit design is shown in Figure 4.4. A similar topology was proposed in [32] for achieving simultaneous output balancing, noise-cancellation and distortion-cancellation. The common gate transistor M1 was designed such that the real part of the LNA input impedance, which is roughly  $1/g_{m1}$ , is matched to the 50 source impedance. The noise or distortion induced by the input matching transistor M1 has out-of-phase responses at the RF input node and positive output node. A common source transistor M2 was then added such that the noise or distortion at the RF input node further creates an out-of-phase response at the negative output node. Therefore, the noise or distortion coming from M1 has in-phase responses at the positive and negative LNA output which results in cancellation for differential operation. The condition for M1 noise and/or distortion cancellation as in [32] is  $g_{m2}/g_{m1} = R_1/R_2$  whereas  $1/g_{m1} = 50$ . On the signal side, the common gate stage has a positive gain while the common source stage has negative gain. The differential output voltage gain is the summation of the gains of both

branches, which are both  $R_1/50$  when simultaneously achieving both power matching and noise cancellation. In addition to the noise cancellation, this LNA operates as a balun for converting the single-ended RF input to a differential RF output for succeeding stages.

In this design, R<sub>1</sub> was set to 240 , which results in a gain of 19.6 dB for the LNA in simulation. The transconductance of M1 was designed as 20 mA/V to meet the receiver power matching requirement. For M2, the transconductance was designed to be 80 mA/V as a trade-off between power consumption and noise figure (NF). Power consumption and NF were simulated as 12 mW and 1.9 dB at 1 GHz respectively. The power supply rejection ratio ranges from 55 dB at 0.15 GHz to 38 dB at 1 GHz due to the unbalanced bandwidth at the two sides of the LNA outputs. The IIP<sub>3</sub> and IIP<sub>2</sub> performance of the LNA were simulated as 3 dBm and 20 dBm, respectively. The IIP<sub>2</sub> performance is limited by the LNA design topology due to its nature of converting single-ended input to differential outputs. A fully differential LNA can exhibit much better IIP<sub>2</sub> performance such as the one designed in [24]. However, the fully differential LNA design has the premise that there exists a wideband low-loss balun or differential antenna as a preceding stage. The cost associated with the preceding stage limits the usage of the fully differential LNA.

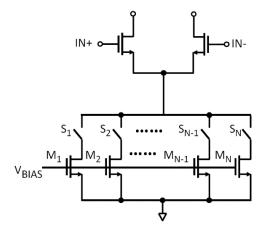

## 4.3.2 G<sub>m</sub> Stage with ESES-based Tunable Gain

The circuit topology of the G<sub>m</sub> stage is shown in Figure 4.5, which is similar to the topology in [33]. A fully differential architecture was chosen for better second-order non-linearity performance, which is crucial for direct conversion receiver architecture. A common mode feedback (CMFB) circuit was designed to define the output common mode voltage for the Gm stage. As the Gm stage is DC coupled to the subsequent passive mixer and baseband TIA, this common mode output voltage is hence also the common mode input voltage for the TIA stage.

The amplifier inside the CMFB circuit is a single-stage differential common-source amplifier. This extra amplifier together with the  $G_m$  stage forms a two-stage amplifier for the CMFB loop. To stabilize this feedback loop, a Miller compensation capacitor  $C_C$  was added.

Figure 4.5 G<sub>m</sub> stage with tunable gain.

Tunable gain was realized by tuning the size of the PMOS current source tail transistor following the ESES based high-resolution current calibration method (section 3.2). ESES with parameters of N=12 and K=6 were applied to sub-transistors  $M_{T1-12}$ , of which widths were sized with an arithmetic sequence. Switches were placed at the drains of the  $M_{T1-12}$  to control the selection of the combination. Each combination has six switches on and six switches off. The total current sets the gain of the  $G_m$  stage. The gain tuning range coming from  $M_{T1-12}$  must not only cover their own variation, but also cover gain mismatch originating from the PMOS and NMOS input differential pairs, TIAs, and the non-ideal weighting ratio of the resistors in the summing stage. SPICE-level Monte Carlo (MC) simulations show that only 8% of the total gain variation is caused by the PMOS tail current source. The majority of the gain variation is coming from the differential PMOS and NMOS input transistors, as they have the minimal channel

length, for bandwidth considerations. With the ESES design method, a sufficiently large tuning range can be created with the PMOS tail current transistor through combinatorial redundancy even though its own randomness is far from dominant. To leave some margin, the gain tuning range was created to cover a six-sigma gain variation seen from the MC circuit simulation. By doing so, applying ESES to a single non-dominant variation source can calibrate gain mismatch from multiple sources. The G<sub>m</sub> stage has simulated performance of 8.8 mA/V transconductance gain and 12 dBm IIP<sub>3</sub>. The CMFB loop has a unity gain bandwidth of 120 MHz and a phase margin of 80°. The power consumption was measured as 3.7 mW with a 1.2 V power supply.

#### 4.3.3 Passive Mixer Design

Figure 4.6 Passive mixer circuit design.