## Reducing DRAM Latency at Low Cost by Exploiting Heterogeneity

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

1 3

#### Donghyuk Lee

M.S., Electrical and Computer Engineering, Carnegie Mellon University B.S., Electrical Engineering, Seoul National University

> Carnegie Mellon University Pittsburgh, PA

> > May 2016

#### Acknowledgement

The last five years at Carnegie Mellon University have been most exciting time of my life, thanks to all of the fantastic people that I have met and worked together with. First and foremost, I am grateful to my advisor, Prof. Onur Mutlu. He provided a great opportunity for me to join his research group as a Ph.D. student and provided great guidance to do not only all the works in this dissertation but also many other works. He taught me to think differently and thoroughly to determine real-world problems and to find better ways to solve these problems, leading to making an impact on the real world. Prof. Mutlu always supported me and encouraged me to improve all my works and my abilities. I am also very thankful to Prof. Mutlu for providing me with a great research environment. Under his support, providing all of the required resources, I could focus on my research and collaborate greatly with many fantastic people.

I would like to thank my thesis committee members, Prof. Todd Mowry, Prof. Kayvon Fatahalian, Prof. Shih-Lien Lu, and Prof. Mattan Erez for their time, efforts, and comments in bringing this dissertation to completion. Special thanks to Prof. Erez for his precise feedback on the entire dissertation. Thanks to Prof. Mowry for his guidance on my research, which started from my qualifying examination. Thanks to Prof. Lu for his interest in my research and valuable feedback. Thanks to Prof. Kayvon Fatahalian for his valuable comments on my research. I would also like to thank Prof. Rajeev Balasubramonian, Dr. Michael Kozuch and Konrad Lai for their interests and great feedback on my research.

The SAFARI group has been like my home and family. Without support from SAFARI members, this dissertation could not have been completed. Yoongu Kim has always been my good friend and mentor. I am really thankful to all his support over every step of my graduate school career. I mostly followed his mentoring, which made it possible to finish this dissertation. Thanks to Vivek Seshadri for his incisive insight and plentiful helps, which improved all works in this dissertation. His optimistic attitude on research and life impressed me. Thanks to Lavanya Subramanian for all her great support, and for many valuable discussions on research and life. Whenever I faced problems, she was always there and provided priceless suggestions. Thanks to Samira Khan for her kindness to listen to all of my problems and provide valuable suggestions. With her dedicated support, I was able to keep working and finish this dissertation. Thanks to Gennady Pekhimenko for his valuable comments on my ideas and suggestions on research directions. His enthusiasm on research and endless efforts to achieve each of his goals impressed me, which made me to put more efforts into my research. Thanks to Hongyi Xin for being a great office mate over four and half years. He taught me the basics of programming and provided valuable guidance on being a programmer. He made my graduate life more exciting and fruitful. Thanks to Saugata Ghose for his critiques. He provided great feedback and helped to improve my work. Thanks to Rachata Ausavarungnirun for his kindness to discuss anything on research and life. He always supported and encouraged me to be a better researcher. Thanks to Chris Fallin for his critical feedback on my research. He provided great help when I prepared for my qualifying examination and conference presentations. His endless efforts and enthusiasm on research impressed me. Thanks to Kevin Chang for his friendly nature and great help in building the DRAM infrastructure. Thanks to Justin Meza, Hanbin Yoon, Ben Jayiyen, Jamie Liu, Nandita Vijayakumar, Yang Li, Kevin Hsieh, Amirali Boroumand, Jeremie Kim, Damla Senol, and Minesh Patel for many discussions and feedback on my research.

Beside the members of the SAFARI group, many people have supported me as I have finished all these works. Thanks to Prof. Jongmoo Choi for his valuable feedback on my research from a system-level perspective. Thanks to Prof. Can Alkan, Farhad Hormozdiari, and Faraz Hach for all their guidance on my DNA sequencing research [141, 287]. Thanks to Ahmad Khairi, Cheng-Yuan Wen, Jaewon Choi, Sandipan Kundu, Shadi Saberi, and Prof. Jeyanandh Paramesh for their help on my first-year research. Thanks to Elaine Lawrence, Samantha Goldstein, Karen Lindenfelser, Nathan Snizaski, Marilyn Patete, Olivia Vadnis, and Jennifer Gabig for their administrative support. Thanks to John and Claire Bertucci for providing me with their fellowship. Thanks to Prof. Andrzej Strojwas and Prof. Brandon Lucia for providing TA opportunities. Thanks to Jinkyu Kim, Soonho Kong, Yongjun Kim, Abhishek Sharma, and Hyoseung Kim for their friendship, which has helped me complete this dissertation.

My family has always provided me with endless support. Thanks to my parents, Seungjoon lee and Hanki Yang, for their encouragement, support, and love. Thanks to my parents-in-law, Byunghwan Choi and Soonja Lee, for their understanding and great support. My brothers and their families, Dongshin Lee, Grace Kim, Hyunseok Choi, Jungyoon Heo, and Yewon Choi, also deserve many thanks for all of their support.

Finally, I would like to thank to my wife, Woonjung Choi, for her devotion supports. She has always been by my side and provided endless love and support during my Ph.D. She always provided a comfortable environment for me to focus on my research, understood me, and encouraged me to make progress on my work. I could not have been completed any of the work in this dissertation without her support.

The research I did during my PhD study was supported in part by myself and in part by National Science Foundation grants (CAREER Award 0953246, and grants numbered 1065112, 1147397, 1212962, 1320531), NIH grant (HG006004) to Professors Onur Mutlu and Can Alkan, Semiconductor Research Corporation, Intel Science and Technology Center for Cloud Computing, Intel URO Memory Hierarchy Program, the John and Claire Bertucci Graduate Fellowship, and gift funding and support provided to Professor Onur Mutlu's group by AMD, Facebook, Google, HP, IBM, Intel, Microsoft, Nvidia, Oracle, Qualcomm, Rambus, Samsung, and VMware.

Donghyuk Lee May 2016, Pittsburgh, PA

#### Abstract

In modern systems, DRAM-based main memory is significantly slower than the processor. Consequently, processors spend a long time waiting to access data from main memory, making the long main memory access latency one of the most critical bottlenecks to achieving high system performance. Unfortunately, the latency of DRAM has remained almost constant in the past decade. This is mainly because DRAM has been optimized for cost-per-bit, rather than access latency. As a result, DRAM latency is not reducing with technology scaling, and continues to be an important performance bottleneck in modern and future systems.

This dissertation seeks to achieve low latency DRAM-based memory systems at low cost in three major directions. The key idea of these three major directions is to enable and exploit latency heterogeneity in DRAM architecture. First, based on the observation that long bitlines in DRAM are one of the dominant sources of DRAM latency, we propose a new DRAM architecture, Tiered-Latency DRAM (TL-DRAM), which divides the long bitline into two shorter segments using an isolation transistor, allowing one segment to be accessed with reduced latency. Second, we propose a fine-grained DRAM latency reduction mechanism, Adaptive-Latency DRAM, which optimizes DRAM latency for the common operating conditions for individual DRAM module. We observe that DRAM manufacturers incorporate a very large timing margin as a provision against the worst-case operating conditions, which is accessing the slowest cell across all DRAM products with the worst latency at the highest temperature, even though such a slowest cell and such an operating condition are rare. Our mechanism dynamically optimizes DRAM latency to the current operating condition of the accessed DRAM module, thereby reliably improving system performance. Third, we observe that cells closer to the peripheral logic can be much faster than cells farther from the peripheral logic (a phenomenon we call architectural variation). Based on this observation, we propose a new technique, Architectural-Variation-Aware DRAM (AVA-DRAM), which reduces DRAM latency at low cost, by profiling and identifying only the inherently slower regions in DRAM to dynamically determine the lowest latency DRAM can operate at without causing failures.

This dissertation provides a detailed analysis of DRAM latency by using both circuit-level simulation with a detailed DRAM model and FPGA-based profiling of real DRAM modules. Our latency analysis shows that our low latency DRAM mechanisms enable significant latency reductions, leading to large improvement in both system performance and energy efficiency across a variety of workloads in our evaluated systems, while ensuring reliable DRAM operation.

# Contents

| 1 | Introduction       |                                                                      |  |  |

|---|--------------------|----------------------------------------------------------------------|--|--|

|   | 1.1                | Problem                                                              |  |  |

|   | 1.2                | Our Approach                                                         |  |  |

|   |                    | 1.2.1 Lowering DRAM Latency by Rearchitecting DRAM Bitline Architec- |  |  |

|   |                    | ture (Tiered-Latency DRAM)                                           |  |  |

|   |                    | 1.2.2 Optimizing DRAM Latency to the Common Operating Conditions     |  |  |

|   |                    | (Adaptive-Latency DRAM)                                              |  |  |

|   |                    | 1.2.3 Lowering DRAM Latency by Exploiting the Awareness of Internal  |  |  |

|   | 1.0                | DRAM Architecture (Architectural-Variation-Aware DRAM)               |  |  |

|   | 1.3                | Thesis Statement                                                     |  |  |

|   | 1.4                | Contributions                                                        |  |  |

|   | 1.5                | Dissertation Outline                                                 |  |  |

| 2 | Bac                | kground                                                              |  |  |

|   | 2.1                | DRAM Organization                                                    |  |  |

|   | 2.2                | DRAM Cell Organization                                               |  |  |

|   | 2.3                | DRAM Access                                                          |  |  |

|   | 2.4                | DRAM Cell Operation: A Detailed Look                                 |  |  |

| 3 | Related Prior Work |                                                                      |  |  |

|   | 3.1                | Low Latency DRAM Architecture                                        |  |  |

|   | 3.2                | Reducing DRAM Latency by Enabling Heterogeneous Memory Control       |  |  |

|   | 3.3                | Enabling More Parallelism in DRAM to Hide DRAM Latency               |  |  |

|   | 3.4                | Memory Scheduling for Mitigating High DRAM Latency                   |  |  |

|   | 3.5                | Memory Scheduling for Mitigating High DRAM Latency                   |  |  |

|   | 3.6                | Enabling Heterogeneity in the System to Optimize System Design       |  |  |

|   | 3.7                | Other Related Prior Works for Mitigating High DRAM Latency           |  |  |

|   |                    |                                                                      |  |  |

| 4 |                    | red-Latency DRAM:                                                    |  |  |

|   |                    | Vering Latency by Modifying the Bitline Architecture                 |  |  |

|   | 4.1                | Motivation: Short vs. Long Bitlines                                  |  |  |

|   |                    | 4.1.1 Latency Impact of Cells-per-Bitline                            |  |  |

|   |                    | 4.1.2 Die-Size Impact of Cells-per-Bitline                           |  |  |

|   | 4.0                | 4.1.3 Trade-Off: Latency vs. Die-Size                                |  |  |

|   | 4.2                | Tiered-Latency DRAM (TL-DRAM)                                        |  |  |

|   |                    | 4.2.1 Latency Analysis (Overview)                                    |  |  |

|   |                    | 7                                                                    |  |  |

|   |                    | v                                                                    |  |  |

|   |                    | 4.2.4 Enabling Inter-Segment Data Transfer                           |  |  |

|                          | 4.3     | Leveraging the TL-DRAM Substrate                                          | 42              |  |  |  |

|--------------------------|---------|---------------------------------------------------------------------------|-----------------|--|--|--|

|                          |         | 4.3.1 Near Segment as an OS-Transparent Hardware-Managed Cache            | 42              |  |  |  |

|                          |         | 4.3.2 Exposing Near Segment Capacity to the OS                            | 44              |  |  |  |

|                          | 4.4     | Implementation Details & Further Analysis                                 | 46              |  |  |  |

|                          |         | · · · · · · · · · · · · · · · · · · ·                                     | 46              |  |  |  |

|                          |         |                                                                           | 46              |  |  |  |

|                          |         | 9                                                                         | 47              |  |  |  |

|                          |         |                                                                           | 48              |  |  |  |

|                          | 4.5     |                                                                           | 48              |  |  |  |

| 30                       |         | 3.                                                                        | 50              |  |  |  |

|                          | 2.0     |                                                                           | 50              |  |  |  |

|                          |         | <u>g</u>                                                                  | 51              |  |  |  |

|                          |         |                                                                           | 53              |  |  |  |

|                          |         | · · · · · · · · · · · · · · · · · · ·                                     | 54              |  |  |  |

|                          |         | v                                                                         | 54              |  |  |  |

|                          |         |                                                                           | 55              |  |  |  |

|                          |         |                                                                           | 57              |  |  |  |

|                          |         |                                                                           | 57              |  |  |  |

|                          | 4.7     | 0 11 0                                                                    |                 |  |  |  |

|                          | Summary | 58                                                                        |                 |  |  |  |

| 5 Adaptive-Latency DRAM: |         |                                                                           |                 |  |  |  |

|                          |         | ptimizing DRAM Latency to the Common Operating Conditions 59              |                 |  |  |  |

|                          | 5.1     | ·                                                                         |                 |  |  |  |

|                          |         |                                                                           | 63              |  |  |  |

|                          | ٠       |                                                                           | 64              |  |  |  |

|                          |         |                                                                           | 65              |  |  |  |

|                          |         |                                                                           | 66              |  |  |  |

|                          | 5.3     |                                                                           | 67              |  |  |  |

|                          | 0.0     | 1 0                                                                       | 67              |  |  |  |

|                          |         | ¥ 9                                                                       | 68              |  |  |  |

|                          | 5.4     |                                                                           | 69              |  |  |  |

|                          | 0.1     |                                                                           | 69              |  |  |  |

|                          |         |                                                                           | 70              |  |  |  |

|                          | 5.5     |                                                                           | 72              |  |  |  |

|                          | 5.5     |                                                                           | $\frac{72}{72}$ |  |  |  |

|                          |         |                                                                           | 74              |  |  |  |

|                          |         |                                                                           | 75              |  |  |  |

|                          |         | 5.5.4 Potential Timing Parameter Reductions While Maintaining the Safety- | 75              |  |  |  |

|                          |         | · ·                                                                       | 76              |  |  |  |

|                          |         |                                                                           | 76              |  |  |  |

|                          |         | 9                                                                         | 78              |  |  |  |

|                          | - 0     |                                                                           | 82              |  |  |  |

|                          | 5.6     | ·                                                                         | 82              |  |  |  |

|                          |         |                                                                           | 83              |  |  |  |

|                          |         | *                                                                         | 83              |  |  |  |

|                          |         | · · · · · · · · · · · · · · · · · · ·                                     | 84              |  |  |  |

|                          |         | 5.6.4 Sensitivity Analysis                                                | 85              |  |  |  |

|   | 5.7 | Summary                                                                           | 8                 |  |

|---|-----|-----------------------------------------------------------------------------------|-------------------|--|

| 6 |     | A-DRAM:                                                                           | 89                |  |

|   | 6.1 | vering DRAM Latency by Exploiting Architecture Variation  Architectural Variation | 9:                |  |

|   | 0.1 | 6.1.1 Impact of DRAM Organization                                                 | 9;                |  |

|   |     | 6.1.2 Impact of the Row/Column Interface                                          | 90                |  |

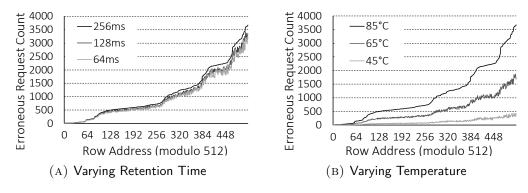

|   |     | 6.1.3 Impact of Operating Conditions                                              | 98                |  |

|   | 6.2 | DRAM Testing Methodology                                                          | 98                |  |

|   | 6.2 |                                                                                   | 100               |  |

|   | 0.5 | DRAM Test Results and Analysis                                                    | 100               |  |

|   |     | 6.3.2 Architectural Variation in Wordlines                                        | 100               |  |

|   |     | 6.3.3 Effect of the Row Interface                                                 | 102               |  |

|   |     | 6.3.4 Effect of the Column Interface                                              |                   |  |

|   |     |                                                                                   | $\frac{107}{108}$ |  |

|   |     | 1 0                                                                               |                   |  |

|   | C 1 | 6.3.6 Summary Results of 96 DRAM modules                                          | 109               |  |

|   | 6.4 | Mechanisms to Reduce Latency                                                      | 11(               |  |

|   |     | 6.4.1 Architectural Variation Aware Online Latency Profiling                      | 11(               |  |

|   |     | 6.4.2 Architectural Variation Aware Shuffling                                     | 114               |  |

|   |     | 6.4.3 AVA Profiling/Shuffling vs. Having Stronger ECC                             | 117               |  |

|   | CF  | 6.4.4 DRAM Latency & Performance Analysis                                         | 117               |  |

|   | 6.5 | Summary                                                                           | 121               |  |

| 7 | Sys | System Design Guidelines                                                          |                   |  |

|   |     | Heterogeneous Memory Systems                                                      | 122               |  |

|   | 7.1 | · ·                                                                               | 122               |  |

|   |     | 7.1.1 Information for Tiered-Latency DRAM                                         | 123               |  |

|   |     | 7.1.2 Information for Adaptive-Latency DRAM                                       | 124               |  |

|   |     | 7.1.3 Information for AVA-DRAM                                                    | 125               |  |

|   | 7.2 | Interface to Heterogeneous-Latency DRAM                                           | 120               |  |

|   | 7.3 | Summary                                                                           | 12'               |  |

| 8 | Cor | nclusions and Future Research Directions                                          | 129               |  |

| _ | 8.1 | Future Research Directions                                                        | 132               |  |

|   | 0.1 | 8.1.1 Optimizing Timing Parameters in 3D-Stacked DRAM                             | 132               |  |

|   |     | 8.1.2 Optimizing Refresh Operations for the Common-Case                           | 132               |  |

|   |     | 8.1.3 System Design for Heterogeneous-Latency DRAM                                | 133               |  |

|   |     | 8.1.4 New Interfaces for Heterogeneous Main Memory                                | $13^{2}$          |  |

|   |     | 8.1.5 Reducing Latency of Emerging Memory Technologies                            | 135               |  |

|   | 8.2 | Final Summary                                                                     | 135               |  |

|   | 0.4 | I mai pamma y                                                                     | тО,               |  |

# List of Tables

| 2.1 | Timing Constraints (DDR3-1066) [232]             | 16  |

|-----|--------------------------------------------------|-----|

| 4.1 | Segmented Bitline: Effect on Latency             | 36  |

| 4.2 | Evaluated System Configuration                   | 49  |

| 5.1 | Repeatability and Consistency of Erroneous Cells | 82  |

| 5.2 | Evaluated System Configuration                   | 83  |

| 6.1 | DRAM Modules, Observed Architectural Variation   | 109 |

| 6.2 | Configuration of Simulated Systems               | 120 |

# List of Figures

| 1.1  | DRAM Capacity & Latency Over Time [27, 111, 207, 232]                         |

|------|-------------------------------------------------------------------------------|

| 2.1  | Hierarchical Organization of a DRAM System                                    |

| 2.2  | DRAM Elementary Components                                                    |

| 2.3  | Three Phases of DRAM Access                                                   |

| 2.4  | DRAM Operations, Commands and Parameters                                      |

| 4.1  | DRAM: Latency vs. Cost Optimized, Our Proposal                                |

| 4.2  | Bitline Length: Latency vs. Die-Size                                          |

| 4.3  | TL-DRAM: Near vs. Far Segments                                                |

| 4.4  | Circuit Model of Segmented Bitline                                            |

| 4.5  | Latency Analysis                                                              |

| 4.6  | Activation: Bitline Voltage                                                   |

| 4.7  | Precharging                                                                   |

| 4.8  | Tiered-Latency DRAM Integration in Open Bitline Scheme 41                     |

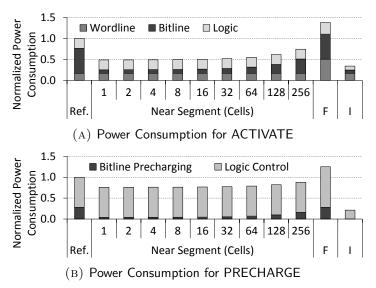

| 4.9  | Power Consumption vs. Bitline Length                                          |

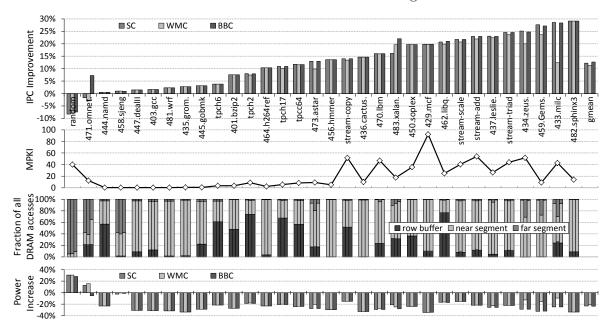

| 4.10 | Single-core: IPC improvement, LLC MPKI, Fraction of accesses serviced at      |

|      | row buffer/near segment/far segment, Power consumption                        |

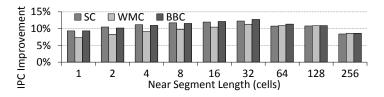

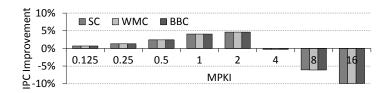

| 4.11 | Varying Near Segment Capacity (Inclusive Cache)                               |

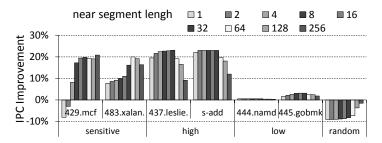

| 4.12 | Four Application Groups Based on Performance Characteristics                  |

| 4.13 | TL-DRAM Performance on Benchmark random                                       |

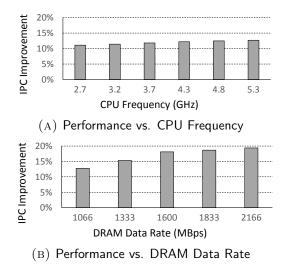

| 4.14 | Sensitivity to CPU Frequency and DRAM Data Rate                               |

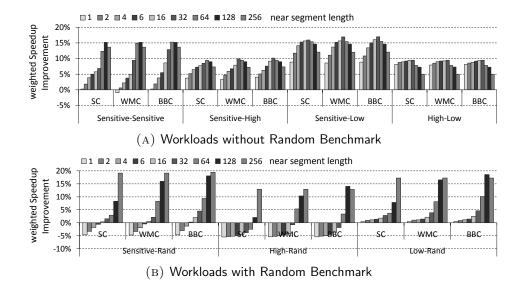

| 4.15 | System Performance: 2-Core, Inclusive Cache                                   |

|      | Inclusive Cache Analysis (BBC)                                                |

| 4.17 | Exclusive Cache Analysis (WMC)                                                |

|      | Profile-Based Page Mapping                                                    |

| 5.1  | Phases of DRAM Voltage Levels                                                 |

| 5.2  | Effect of Reduced Latency: Typical vs. Worst (Darker Background means Less    |

|      | Reliable)                                                                     |

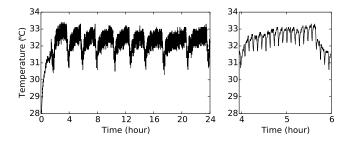

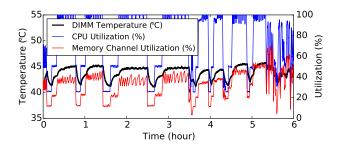

| 5.3  | DRAM Temperature in a Server Cluster                                          |

| 5.4  | DRAM Temperature in a Desktop System                                          |

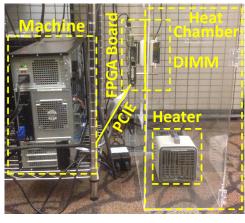

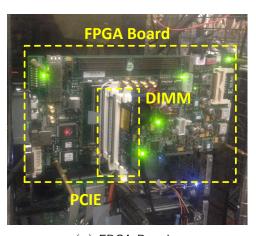

| 5.5  | FPGA-Based DRAM Test Infrastructure                                           |

| 5.6  | Effect of Varying Each Timing Parameter on Error Count                        |

| 5.7  | Error Counts When Varying Multiple Timing Parameters Simultaneously 74        |

| 5.8  | Error Counts When Varying Temperature, Refresh Interval, and $t_{RAS}/t_{WR}$ |

|      | $(t_{RCD}/t_{RP}: 12.5 \text{ ns})$                                           |

| 5.9  | Latency Reductions While Maintaining the Safety-Margin                        |

| 5.10 | Retention Time of Multiple DIMMs                                              |

| 5.11 | Latency Analysis of Multiple DRAM modules                                           | 81  |

|------|-------------------------------------------------------------------------------------|-----|

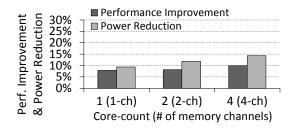

| 5.12 | Real-System Performance Improvement with AL-DRAM (Each Error Bar Shows              |     |

|      | the Standard Deviation across Multiple Runs)                                        | 84  |

| 5.13 | AL-DRAM Performance Improvement on a Real System with Different Rank                |     |

|      | and Channel Configurations                                                          | 86  |

| 6.1  | Architectural Variation in a DRAM Chip                                              | 90  |

| 6.2  | Architectural Variation due to Row Organization                                     | 94  |

| 6.3  | Architectural Variation in Column Organization                                      | 95  |

| 6.4  | Accessing Multiple Mats in a Data Burst                                             | 97  |

| 6.5  | FPGA-Based DRAM Test Infrastructure                                                 | 99  |

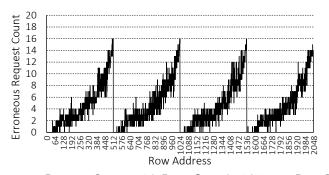

| 6.6  | Erroneous Request Count when Sweeping Row Addresses with Reduced $t_{RP}$           |     |

|      | Timing Parameter                                                                    | 102 |

| 6.7  | Periodicity in Error Request Count $(t_{RP} 7.5 \text{ns}) \dots \dots \dots \dots$ | 103 |

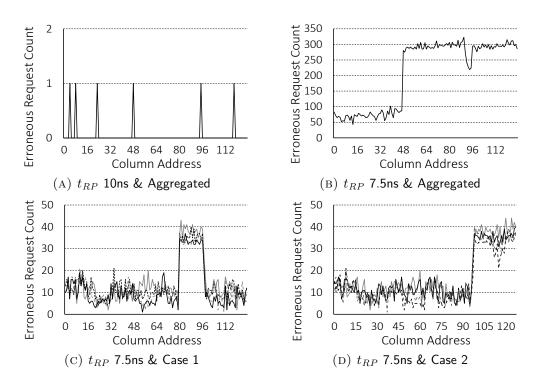

| 6.8  | Erroneous Request Count when Sweeping Column Addresses with Reduced                 |     |

|      | $t_{RP}$ Timing Parameter                                                           | 104 |

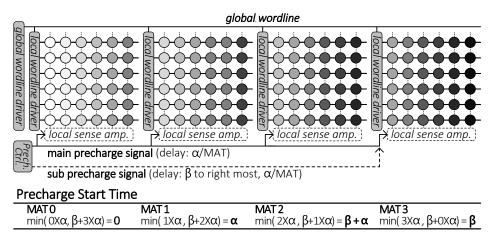

| 6.9  | Architectural Variation due to Precharge Control                                    | 105 |

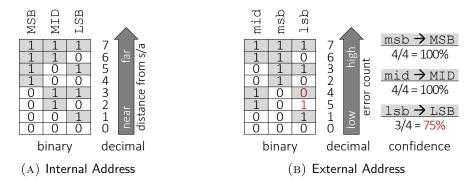

| 6.10 | DRAM-External Address vs. DRAM-Internal Address                                     | 106 |

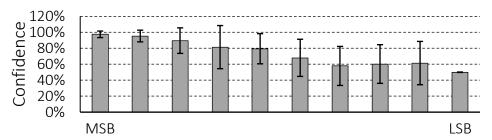

| 6.11 | Confidence in Estimated Row Mapping for Each Bit                                    | 107 |

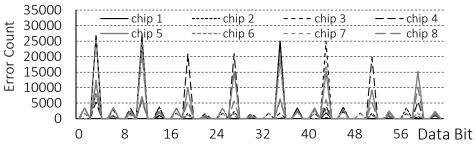

| 6.12 | Error Count in Bit Positions                                                        | 108 |

| 6.13 | Architectural Variation vs. Operating Conditions                                    | 109 |

| 6.14 | Latency Variation in a Mat (Darker: higher latency)                                 | 111 |

| 6.15 | Architectural Variation Aware Online Profiling                                      | 112 |

| 6.16 | Architectural Variation Aware Data Shuffling                                        | 115 |

| 6.17 | ECC with/without AVA Shuffling                                                      | 116 |

| 6.18 | Read and Write Latency Reduction                                                    | 118 |

|      |                                                                                     | 119 |

|      |                                                                                     | 120 |

|      |                                                                                     |     |

## Chapter 1

## Introduction

#### 1.1 Problem

Primarily due to its low cost-per-bit, DRAM has long been the choice substrate for architecting main memory systems. In fact, DRAM's cost-per-bit has been decreasing at a rapid rate as DRAM process technology scales to integrate ever more DRAM cells into the same die area. As a result, each successive generation of DRAM has enabled increasingly large-capacity main memory subsystems at low cost.

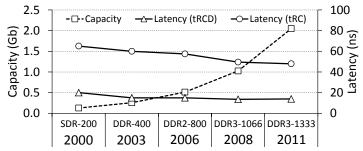

In stark contrast to the continued scaling of cost-per-bit, the *latency* DRAM has remained almost constant, During the same 11-year interval in which DRAM's cost-per-bit decreased by a factor of 16, DRAM latency (as measured by the  $t_{RCD}$  and  $t_{RC}$  timing constraints) decreased by only 30.5% and 26.3%, as shown in Figure 1.1. From the perspective of the processor, an access to DRAM takes hundreds of cycles – time during which a modern processor is likely stalled, waiting for DRAM [12, 76, 189, 191, 193, 194, 195]. Such wasted time, which is more than 50-60% of the execution time for many memory-intensive workloads [12, 189, 191, 194], leads to large performance degradations commonly referred to as the "memory wall" [283] or the "memory gap" [279].

However, the high latency of commodity DRAM chips is in fact a *deliberate* trade-off made by DRAM manufacturers. While process technology scaling has enabled DRAM designs with both lower cost-per-bit *and* lower latency [98], DRAM manufacturers have usually sacrificed the latency benefits of scaling in order to achieve even lower cost-per-bit. Hence, while low-latency DRAM chips exist [129, 173, 235], their higher cost-per-bit relegates them to

† We refer to the dominant DRAM chips during the period of time [27, 111].

FIGURE 1.1: DRAM Capacity & Latency Over Time [27, 111, 207, 232]

specialized applications such as high-end networking equipment that demand very low latency even at the expense of a very high cost [270].

Our main research objective is to enable a low latency DRAM-based memory system, in order to achieve high system performance, via simple and low cost DRAM architectures and memory control techniques.

#### 1.2 Our Approach

Towards achieving our goal of a low latency DRAM-based memory system, our major approach is to enable or exploit latency heterogeneity in DRAM. Due to the large number of cells in DRAM, there already exists such latency heterogeneity (latency variation) due to multiple aspects. For example, i) DRAM cells in different locations in the same chip or across different chips have different latencies, and ii) DRAM has different latencies at different operating conditions (e.g., temperature). However, to provide a simplified interface to access DRAM, DRAM has been designed to improve only the worst case latency. One simple example is that DRAM uses identical timing parameters for accessing all DRAM cells from any DRAM chip at all operating conditions, even though the latency can be very different based on the location of each cell, the characteristics of different chips, or the characteristics of each cell at different operating conditions. Therefore, DRAM has been focused on either minimizing these latency variations in its architecture or hiding them. Unfortunately, the latency variation in DRAM is expected to increase with further DRAM cell scaling due to

worsening process variation at smaller process technology nodes. Therefore, enabling low DRAM latency is expected to be more difficult in the future.

Our approach for lowering DRAM latency is enabling or exploiting such latency heterogeneity by i) rearchitecting DRAM at low cost, ii) enabling fine-grained DRAM control to optimize DRAM latency for the common operating conditions, and iii) exploiting the latency variation inherent in the internal DRAM architecture.

# 1.2.1 Lowering DRAM Latency by Rearchitecting DRAM Bitline Architecture (Tiered-Latency DRAM)

DRAM has been developed to make its capacitor-based cell smaller for higher capacity. The small size of this capacitor necessitates the use of an auxiliary structure, called a (local) sense amplifier, to detect the small amount of charge held by the cell and amplify it to a full digital logic value. But, a local sense amplifier is approximately one hundred times larger than a cell [223]. To amortize its large size, each local sense amplifier is connected to many DRAM cells through a wire called a bitline. Every bitline has an associated parasitic capacitance whose value is proportional to the length of the bitline. Unfortunately, such parasitic capacitance slows down DRAM operation for two reasons. First, it increases the latency of the local sense amplifiers. When the parasitic capacitance is large, a cell cannot quickly create a voltage perturbation on the bitline that could be easily detected by the local sense amplifier. Second, it increases the latency of charging and precharging the bitlines. Although the cell and the bitline must be restored to their quiescent voltages during and after an access to a cell, such a procedure takes much longer when the parasitic capacitance is large. Due to the above reasons and a detailed analysis of the latency break-down [145], we conclude that long bitlines are the dominant source of DRAM latency.

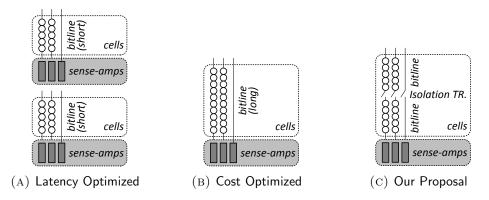

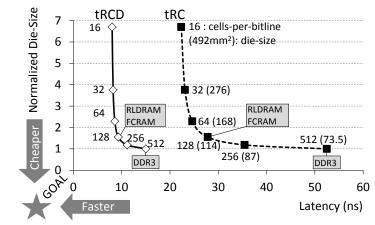

The bitline length is a key design parameter that exposes the important trade-off between latency and die-size (cost). Short bitlines (few cells per bitline) constitute a small electrical load (parasitic capacitance), which leads to low latency. However, they require more local sense amplifiers for a given DRAM capacity, which leads to a large die-size. In contrast, long bitlines have high latency and a small die-size. As a result, neither of these two approaches

can optimize for both latency and cost-per-bit. The goal in this work is to design a new DRAM architecture to approximate the best of both worlds (i.e., low latency and low cost), based on the key observation that long bitlines are the dominant cause of DRAM latency.

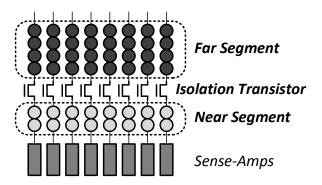

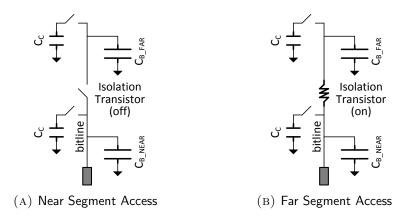

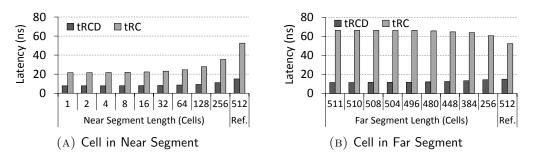

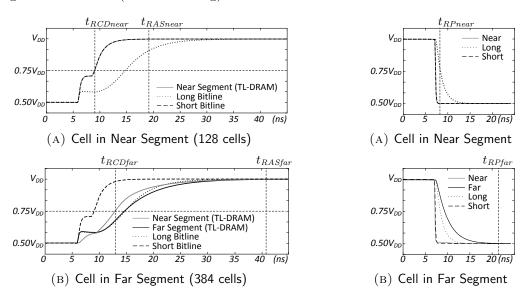

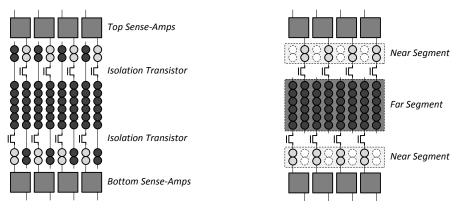

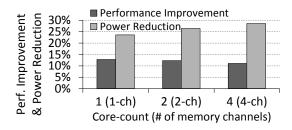

To achieve the latency advantage of short bitlines and the cost advantage of long bitlines, we propose the Tiered-Latency DRAM (TL-DRAM) architecture, which divides the long bitline into two shorter segments using an  $isolation\ transistor$ : the  $near\ segment$  (connected directly to the local sense amplifier) and the  $far\ segment$  (connected to the local sense amplifier only when the isolation transistor is turned on). As a result, the near segment has much lower latency than the far segment. To maximize the latency benefits from this heterogeneous bitline architecture, we propose two mechanisms -i) using the near segment as a hardware-managed cache to the far segment, and ii) exposing the near segment to the operating system, which places latency-critical data to the near segment. We propose two new policies to manage the near segment cache that specifically exploit the asymmetric latency characteristics of TL-DRAM. Our most sophisticated cache management algorithm, Benefit-Based Caching (BBC) improves system performance by an average of 12.8% and reduces energy consumption by an average of 23.6% over a wide variety of data-intensive workloads.

In summary, TL-DRAM enables latency heterogeneity in DRAM by changing the internal DRAM architecture with low area cost, and provides mechanisms to maximize the latency benefits by enabling intelligent data placement.

# 1.2.2 Optimizing DRAM Latency to the Common Operating Conditions (Adaptive-Latency DRAM)

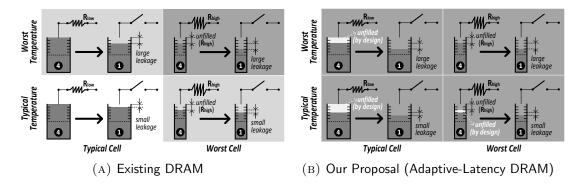

When a DRAM chip is accessed, it requires a certain amount of time before enough charge can move into the cell (or the bitline) for the data to be reliably stored (or retrieved). To guarantee this behavior, DRAM manufacturers impose a set of minimum latency restrictions on DRAM accesses, referred to as timing parameters [105]. Ideally, timing parameters should provide just enough time for a DRAM chip to operate correctly. In practice, however, DRAM manufacturers pessimistically incorporate a very large margin into their timing parameters to ensure correct operation under the worst case conditions due to two major concerns. First,

due to *process variation* [73, 147, 233], some outlier cells suffer from a larger delay than other cells, and require more time to be charged. Although every cell is designed to have a large capacitance (to hold more charge) and a small resistance (to facilitate the flow of charge), some deviant cells may not be implemented in such a manner. Second, due to *temperature dependence*, all cells suffer from a weaker charge-drive at high temperatures, and require more time to charge the bitline. Consequently, to accommodate the combined effect of process variation and temperature dependence (the worst case condition), existing timing parameters prescribed by the DRAM manufacturers are set to a very large value.

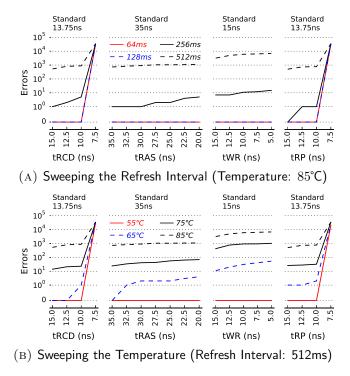

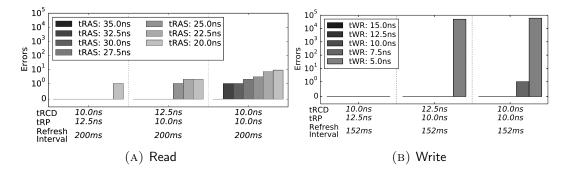

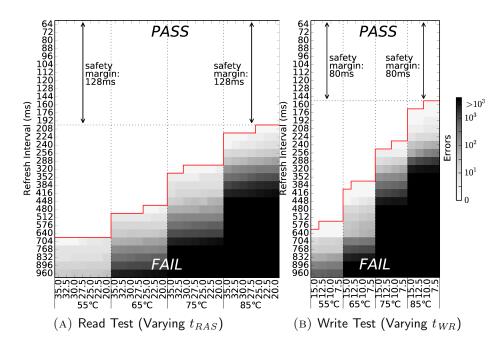

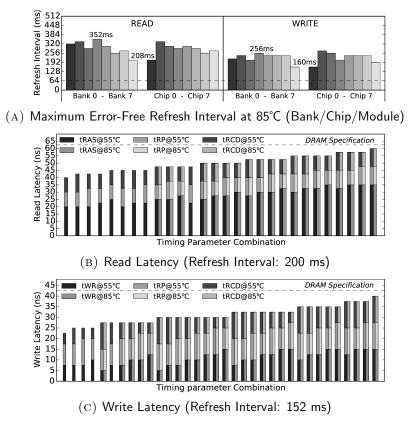

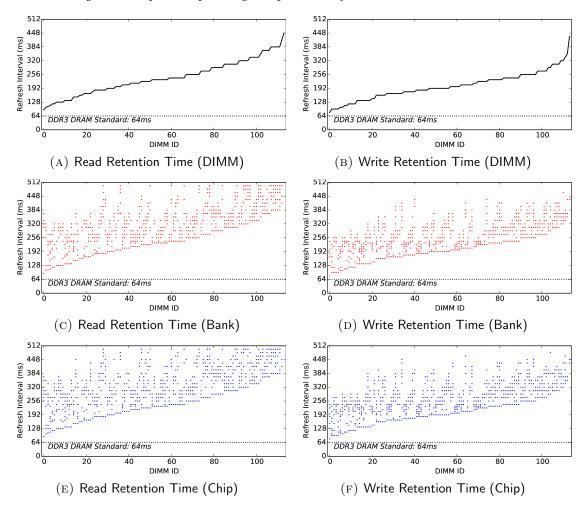

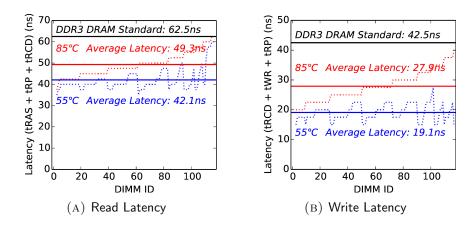

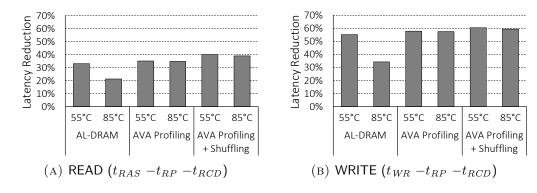

Our approach is to reduce the DRAM latency by reducing the additional *latency slack* in DRAM due to the pessimism on timing parameters. To study the potential for reducing timing parameters for each DRAM module, we characterize 115 DRAM modules from three manufacturers to expose the excessive margin that is built into their timing parameters. We make two observations. First, even at the highest temperature of 85°C, there is a high potential for reducing the latency of DRAM modules (21.1% on average for read and 34.4% for write operations). Second, we observe that at lower temperatures (e.g., 55°C) the potential for latency reduction is even greater (32.7% on average for read and 55.1% on average for write operations). As a result, we conclude that exploiting process variation and lower temperatures enable a significant potential to reduce DRAM latencies.

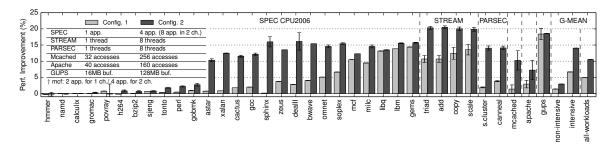

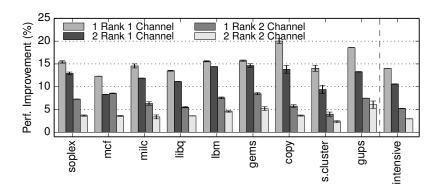

Based on our characterization, we propose Adaptive-Latency DRAM (AL-DRAM), a mechanism that dynamically optimizes the timing parameters for different modules at different temperatures. AL-DRAM exploits only the *additional charge slack* in the common-case compared to the worst-case, thereby maintaining the reliability of DRAM modules. We evaluate AL-DRAM on a real system [18, 19] and show show that AL-DRAM improves the performance of a wide variety of memory-intensive workloads by 14.0% (on average) without introducing any errors.

In summary, AL-DRAM enables lower DRAM latency while maintaining memory correctness and without requiring changes to the internal DRAM architecture or the DRAM interface (low cost).

# 1.2.3 Lowering DRAM Latency by Exploiting the Awareness of Internal DRAM Architecture (Architectural-Variation-Aware DRAM)

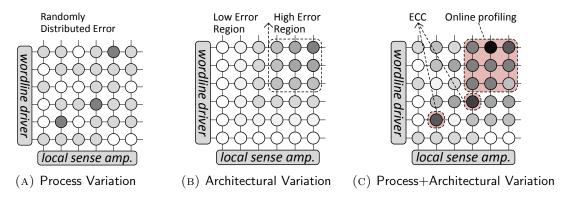

Modern DRAM consists of 2D cell arrays, each of which has its own accessing structure (e.g., wordline driver) and data sensing structure (e.g., local sense amplifier). We observe that there is variability across DRAM cells based on their locations in a DRAM cell array (mat). Some DRAM cells can be accessed faster than others due to their physical location. We refer to this variability in cells' access times, caused by the physical organization of DRAM, as architectural variation. Architectural variation arises from the difference in the distance between the cells and the peripheral logic that is used to access these cells. The wires connecting the cells to peripheral logic exhibit large resistance and large capacitance [143, 145]. Consequently, cells experience different RC delays based on their distance from the peripheral logic (e.g., accessing and sensing structures). Cells closer to the peripheral logic experience smaller delay and can be accessed faster than the cells located farther from the peripheral logic.

Architectural variation in latency is present in both vertical and horizontal directions in a mat: i) Each vertical column of cells in a mat is connected to a local sense amplifier and ii) each horizontal row of cells in a mat is connected to a wordline driver. Variations in the vertical and horizontal dimensions, together, divide the cell array into heterogeneous latency regions, where cells in some regions require larger latencies for reliable operation. This variation in latency has direct impact on the reliability of the cells. Reducing the latency uniformly across all regions in DRAM would improve performance, but can introduce failures in the inherently slower regions that have to be accessed longer for correct DRAM operation. We refer to these inherently slower regions of DRAM as architecturally vulnerable regions. We first experimentally demonstrate the existence of architectural variation in modern DRAM chips and identify the architecturally vulnerable regions. We then propose new mechanisms that leverage this variation to reduce DRAM latency while providing reliability at low cost.

Based on our experimental study that characterizes 96 DRAM modules by using our FPGA-based DRAM testing infrastructure, we show that i) modern DRAM chips exhibit

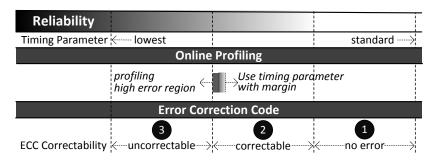

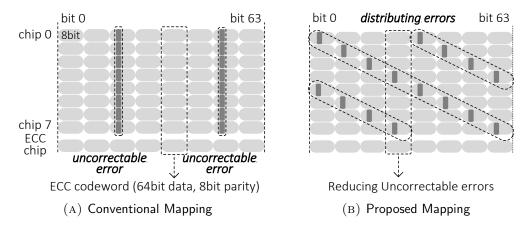

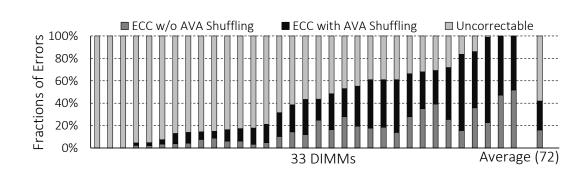

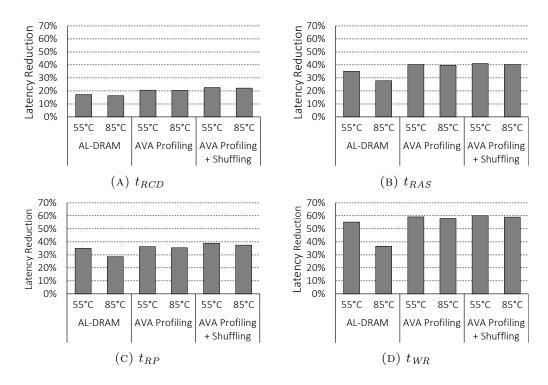

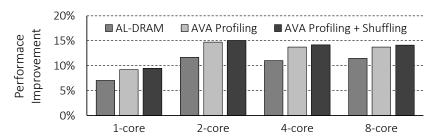

architectural latency variation in both row and column directions, and ii) architectural vulnerability gradually increases in the row direction within a mat and repeats the variability pattern in every mat. Then, we develop two new mechanisms that exploit the architecturally vulnerable regions to enable low DRAM latency with high reliability and at low cost (Architectural-Variation-Aware DRAM (AVA-DRAM)). The first mechanism, AVA Profiling, identifies the lowest possible latency that ensures reliable operation at low cost by periodically profiling only the architecturally vulnerable regions. To further reduce DRAM latency, the second mechanism, AVA Shuffling, distributes data from architecturally vulnerable regions to multiple ECC codewords to make it correctable by using ECC. AVA Profiling can dynamically reduce the latencies of read/write operations by 35.1%/57.8% at 55°C while ensuring reliable operation at low cost. AVA Shuffling on average corrects 26% of total errors which are not correctable by conventional ECC, leading to further latency reduction for 24 DRAM modules out of 96 DRAM modules. We show that the combination of our techniques, AVA-DRAM, leads to a raw DRAM latency reduction of 40.0%/60.5% (read/write) and an overall system performance improvement of 14.7%/13.7%/13.8% (2-/4-/8-core) over a variety of workloads in our evaluated systems, while ensuring reliable operation.

AVA-DRAM is the first work that exposes and experimentally demonstrates the existence of architectural variation. We then propose two mechanisms that leverage architectural variation towards achieving high performance, energy efficiency, and reliability through dynamic profiling (AVA Profiling) and data shuffling (AVA Shuffling).

#### 1.3 Thesis Statement

DRAM latency can be reduced by enabling and exploiting latency heterogeneity in DRAM architecture.

#### 1.4 Contributions

This dissertation makes the following major contributions.

- This dissertation makes the observation that long internal wires (bitlines) are the dominant source of DRAM latency, and exposes the important trade-off between DRAM latency and area. Based on this, this dissertation proposes a new DRAM architecture, Tiered-Latency DRAM, which divides long bitline into fast and slow segments, enabling latency heterogeneity in DRAM. This dissertation quantitatively evaluates the latency, area, and power characteristics of Tiered-Latency DRAM through circuit simulations based on a publicly available 55nm DRAM process technology [223]. We show that the near segment latency  $(t_{RC})$  for a 32-row near segment can be 49% lower than the modern DRAM standard latency.

- This dissertation describes two major ways of leveraging TL-DRAM: i) by using the near segment as a hardware-managed cache without exposing it to software, and ii) by exposing the near segment capacity to the OS and using hardware/software to map frequently accessed pages to the near segment. We propose two new policies to manage the near segment that specifically exploit the asymmetric latency characteristics of TL-DRAM. Our most sophisticated cache management algorithm, Benefit-Based Caching (BBC) improves system performance by an average of 12.8% and reduces energy consumption by an average of 23.6% over a wide variety of workloads.

- This dissertation provides a detailed analysis of why we can reduce DRAM timing parameters without sacrificing reliability in the common case. We show that the latency of a DRAM access depends on how quickly charge moves into or out of a cell. Compared to the worst-case cell operating at the worst-case temperature (85°C), a typical cell at a typical temperature allows much faster movement of charge, leading to shorter latency. This enables the opportunity to reduce timing parameters without introducing errors.

- This dissertation provides detailed DRAM profiling results (for 115 DRAM modules, comprised of 920 DRAM chips, from three manufacturers) by using an FPGA-based DRAM testing infrastructure, and exposes the large margin built into their timing parameters. In

particular, we identify four timing parameters that are the most critical during a DRAM access:  $t_{RCD}$ ,  $t_{RAS}$ ,  $t_{WR}$ , and  $t_{RP}$ . At 55°C, we demonstrate that the parameters can be reduced by an average of 17.3%, 37.7%, 54.8%, and 35.2% while still maintaining correctness.

- This dissertation proposes a practical mechanism, Adaptive-Latency DRAM (AL-DRAM), to take advantage of the extra margin built into DRAM latency. The key idea is to dynamically adjust the DRAM timing parameters for each module based on its latency characteristics and temperature so that the timing parameters are dynamically optimized for the current operating condition and the current DRAM module. We show that the hardware cost of AL-DRAM is very modest, with no changes to DRAM. We evaluate AL-DRAM on a real system [18, 19] running real workloads by dynamically reconfiguring the timing parameters. AL-DRAM improves system performance by an average of 14.0% and a maximum of 20.5% over a wide variety of memory-intensive workloads, without incurring any errors.

- This dissertation exposes and experimentally demonstrates the phenomenon of architectural latency variation in DRAM cell arrays, i.e., that the access latency of a cell depends on its location in the DRAM array. This phenomenon causes certain regions of DRAM to be inherently more vulnerable to latency reduction than others based on their relative distance from the peripheral logic.

- This dissertation identifies the regions in DRAM that are most vulnerable to latency reduction based on the internal hierarchical organization of DRAM bitlines and wordline drivers. We call such regions as architecturally vulnerable regions. We experimentally demonstrate the existence of architecturally vulnerable regions in DRAM by testing and characterizing 96 real DRAM modules (768 DRAM chips).

- This dissertation develops two new mechanisms, called AVA Profiling and AVA Shuffling, that exploit architectural variation to improve performance and reliability of DRAM at low cost. AVA Profiling dynamically finds the lowest latency at which a DRAM chip can operate reliably. AVA Profiling can dynamically reduce the latencies of read/write operations

by 35.1%/57.8% at 55°C while ensuring reliable operation at low cost. AVA Shuffling distributes data from architecturally vulnerable regions to multiple ECC codewords to make it correctable by using ECC. AVA Shuffling on average corrects 26% of total errors which are not correctable by conventional ECC. We show that the combination of our techniques, AVA-DRAM, leads to a raw DRAM latency reduction of 40.0%/60.5% (read/write) and an overall system performance improvement of 14.7%/13.7%/13.8% (2-/4-/8-core) over a wide variety of workloads in our evaluated systems, while ensuring reliable operation.

#### 1.5 Dissertation Outline

This dissertation is organized into seven chapters. Chapter 2 presents background on memory system organization and DRAM organization. Chapter 3 discusses related prior work on techniques for reducing and tolerating DRAM latency. Chapter 4 presents the design of Tiered-Latency DRAM and mechanisms to leverage the Tiered-Latency DRAM substrate for reducing overall DRAM latency. Chapter 5 first presents the latency slack in DRAM standard timing parameters that are dictated by the worst case conditions (accessing the smallest cell in DRAM products at the worst case operating temperature). It then proposes and evaluates Adaptive-Latency DRAM that optimizes DRAM timing parameters for the common case (accessing the common cells in each DRAM module at current operating temperature). Chapter 6 first presents the observation of architectural variation in a DRAM cell array (mat). It then proposes and evaluates AVA-DRAM that leverages architectural variation for reducing DRAM latency at low cost, by periodically profiling only the worst latency regions at low cost and distributing data in the worst latency regions to multiple ECC codewords. Chapter 7 introduces system design guidelines for future memory systems that have heterogeneous latency. Finally, Chapter 8 presents our conclusions and future research directions that are enabled by this dissertation.

### Chapter 2

## Background

To understand the dominant sources of DRAM latency, we first provide the necessary background on DRAM organization and operation.

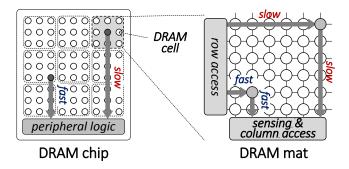

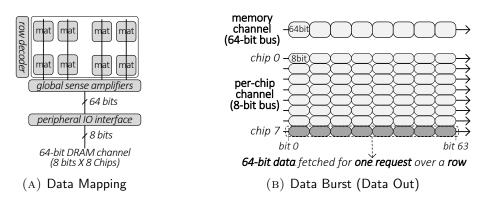

#### 2.1 DRAM Organization

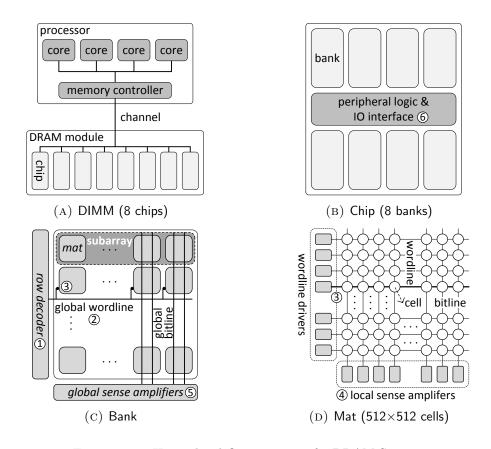

DRAM is organized in a hierarchical manner where each DRAM module consists of multiple chips, banks, mats, and subarrays. Figure 2.1 shows the hierarchical organization of a typical DRAM-based memory system, where the hierarchy consists of five levels (Figure 2.1a–2.1d). Module. At the highest level of the hierarchy (shown in Figure 2.1a), a memory controller in a processor is connected to a DRAM module over a memory channel. The memory channel has a 64-bit data bus that is divided into eight 8-bit buses connected to eight chips in the DRAM module. These eight chips operate in lock step while accessing the DRAM module. For example, when there is a read request from the memory controller, each DRAM chip transfers 8 bytes of data in 8 data bursts over the dedicated 8-bit data bus connected to it, transferring a total of 64 bytes (cache line size) across all chips.

**Chip.** A DRAM *chip* (shown in Figure 2.1b) consists of *i*) multiple banks and *ii*) peripheral logic that is used to transfer data to the memory channel through the IO interface.

**Bank.** Each bank (shown in Figure 2.1c), is subdivided into multiple mats. In a bank, there are two global components that are used to access the mats: i) a row decoder that selects a row of cells across a subarray that consists of multiple mats and ii) global sense amplifiers

FIGURE 2.1: Hierarchical Organization of a DRAM System

that transfer a fraction of data from the row through the global bitlines, based on the column address.

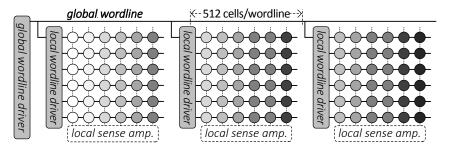

Mat. Figure 2.1d shows the organization of a mat that consists of three components: i) a 2-D cell array in which the cells in each row are connected horizontally by a shared wire called the wordline, and the cells in each column are connected vertically by a wire called the bitline, ii) a column of wordline drivers that drive each wordline to appropriate voltage levels in order to activate a row during an access and iii) a row of local sense amplifiers that sense and latch data from the activated row.

**Subarray.** A row of mats in a bank forms a subarray, where cells in a *subarray* are accessed simultaneously, managed by wordlines connected to a global wordline, as shown in Figure 2.1c.

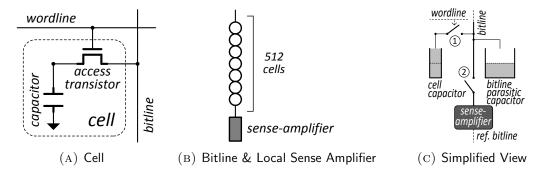

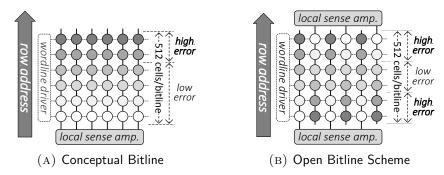

#### 2.2 DRAM Cell Organization

As explained in Section 2.1, a DRAM subarray is a group of mats in the horizontal direction and each mat is a 2-D array of elementary units called *cells*. As shown in Figure 2.2a, a cell consists of two components: *i)* a capacitor that represents binary data in the form of stored electrical charge and *ii)* an access transistor that is switched on/off to connect/disconnect the capacitor to a *bitline*. As shown in Figure 2.2b, there are approximately 512 cells in the vertical direction (a "column" of cells), all of which share the same bitline. For each bitline, there is a *local sense amplifier* whose main purpose is to read from a cell by reliably detecting the very small amount of electrical charge stored in the cell. When writing to a cell, on the other hand, the local sense amplifier acts as an electrical driver and programs the cell by filling or depleting its stored charge.

FIGURE 2.2: DRAM Elementary Components

Numerous bitlines (and their associated local sense amplifiers) are laid side-by-side in parallel to compose a subarray (Figures 2.1c and 2.1d). All cells in the horizontal direction (a "row" of cells) have their access transistors controlled by a wordline. When the wordline voltage is raised to  $V_{DD}$ , all cells of a row are connected to their respective bitlines and sensed in lockstep by the local sense amplifiers. This is why the set of all local sense amplifiers in a subarray is also called a row buffer. At any given time, at most one wordline in a subarray is ever raised (i.e., at most one cell per column is connected to the bitline) – otherwise, cells in the same column would corrupt each other's data.

Figure 2.2c depicts a simplified view of a cell as well as its bitline and local sense amplifier, in which electrical charge is represented in gray. Switch ① represents the access transistor controlled by the wordline, and switch ② represents the on/off state of the sense amplifier.

#### 2.3 DRAM Access

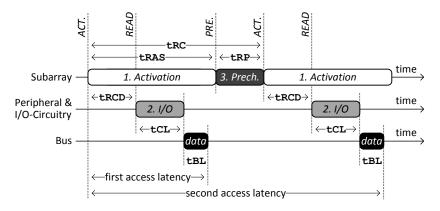

As the timelines in Figure 2.3 show, a DRAM chip access can be broken down into three distinct *phases*: *i*) activation, *ii*) IO, and *iii*) precharging. Activation and precharging occur entirely within the subarray, whereas IO occurs in the peripheral logic and IO circuitry. All these operations consist of two levels of accesses through: *i*) global structures across all subarrays within a bank (global sense amplifiers, global wordlines and global bitlines) and *ii*) local structures within a mat (local sense amplifiers, local wordlines, and local bitlines). A DRAM access goes through multiple steps in the global-local hierarchy:

FIGURE 2.3: Three Phases of DRAM Access

• Activation. During the activation phase, the row decoder in a bank receives a row address to activate (① in Figure 2.1c), then, it first activates the corresponding global wordline in the bank (② in Figure 2.1c). The global wordline, in turn, activates the corresponding wordline driver in each mat of the subarray. The wordline driver in each mat activates the corresponding local wordline connecting the row of cells to the bitlines (③ in Figures 2.1c and 2.1d). Soon thereafter, the data in the row of cells is copied (detected) to the local sense amplifiers of that subarray (④ in Figure 2.1d).

- IO. During the IO phase, the local sense amplifiers transfer the data to the global sense amplifiers, through the global bitlines (⑤ in Figure 2.1c). Data from the global sense amplifiers is then sent to the memory channel through the IO interface of the chip (⑥ in Figure 2.1b). From there, the data leaves the DRAM chip and is sent to the processor over the memory channel. As Figure 2.3 shows, the IO phase's latency is overlapped with the latency of the activation phase.

- **Precharging.** During the *precharging* phase, the raised wordline in the subarray is lowered, disconnecting the row of cells from the bitlines. Also, the subarray's local sense amplifiers and bitlines are initialized (i.e., cleared of their data) to prepare for the next access to a new row of cells.

Three DRAM Commands. The DRAM controller (typically residing on the processor die) issues *commands* to the DRAM chip to initiate the three phases listed above. As shown in Figure 2.3, there are three commands, one for each phase. In their respective order, they are: ACTIVATION (ACT), READ/WRITE, and PRECHARGE (PRE). Among the commands, ACTIVATION and PRECHARGE are subarray-related commands since they directly operate on the subarray, whereas READ and WRITE are IO-related commands.

Timing Constraints. After the DRAM controller issues a command to initiate a phase, it must wait for a sufficient amount of time before issuing the next command. Such restrictions imposed between the issuing of commands are called timing constraints. DRAM timing constraints are visualized in Figure 2.3 and summarized in Table 2.1. Two of the most important timing constraints are  $t_{RCD}$  (row-to-column delay) and  $t_{RC}$  (row-cycle time). Every time a new row of cells is accessed, the subarray incurs  $t_{RCD}$  (15ns; ACTIVATION  $\rightarrow$  READ/WRITE) to copy the row into the local sense amplifiers. On the other hand, when there are multiple accesses to different rows in the same subarray, an earlier access delays all later accesses by  $t_{RC}$  (52.5ns; ACTIVATION  $\rightarrow$  ACTIVATION). This is because the subarray needs time to complete the activation phase ( $t_{RAS}$ ) and the precharging phase ( $t_{RP}$ ) for the earlier access, whose sum is defined as  $t_{RC}$  (=  $t_{RAS}$  +  $t_{RP}$ ), as shown in Figure 2.3.

| Phase | Commands                                                                                                       | Name                           | Value              |

|-------|----------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|

| 1     | $\begin{array}{l} \mathtt{ACTIVATION} \to \mathtt{READ} \\ \mathtt{ACTIVATION} \to \mathtt{WRITE} \end{array}$ | $t_{RCD}$                      | 15ns               |

|       | ${\tt ACTIVATION} \to {\tt PRECHARGE}$                                                                         | $t_{RAS}$                      | $37.5 \mathrm{ns}$ |

| 2     | $\begin{array}{l} \mathtt{READ} \rightarrow data \\ \mathtt{WRITE} \rightarrow data \end{array}$               | $t_{CL} \ t_{CWL}$             | 15ns<br>11.25ns    |

|       | data burst                                                                                                     | $t_{BL}$                       | 7.5ns              |

| 3     | $\mathtt{PRECHARGE} \to \mathtt{ACTIVATION}$                                                                   | $t_{RP}$                       | 15ns               |

| 1 & 3 | ${\tt ACTIVATION} \to {\tt ACTIVATION}$                                                                        | $t_{RC} \\ (t_{RAS} + t_{RP})$ | 52.5ns             |

Table 2.1: Timing Constraints (DDR3-1066) [232]

Access Latency. Figure 2.3 illustrates how the DRAM access latency can be decomposed into individual DRAM timing constraints. Specifically, the figure shows the latencies of two read accesses (to different rows in the same subarray) that are served one after the other. From the perspective of the first access, DRAM is "unloaded" (i.e., no prior timing constraints are in effect), so the DRAM controller immediately issues an ACTIVATION on its behalf. After waiting for  $t_{RCD}$ , the controller issues a READ, at which point the data leaves the subarray and incurs additional latencies of  $t_{CL}$  (peripherals and IO circuitry) and  $t_{BL}$  (bus) before it reaches the processor. Therefore, the latency of the first access is 37.5ns ( $t_{RCD} + t_{CL} + t_{BL}$ ). On the other hand, the second access is delayed by the timing constraint that is in effect due to the first access ( $t_{RC}$ ) and experiences a large "loaded" latency of 90ns ( $t_{RC} + t_{RCD} + t_{CL} + t_{BL}$ ).

#### 2.4 DRAM Cell Operation: A Detailed Look

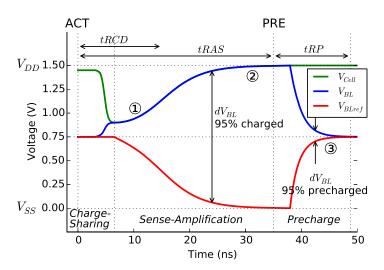

Subarray-related timing constraints ( $t_{RCD}$  and  $t_{RC}$ ) constitute a significant portion of the unloaded and loaded DRAM access latencies: 40% of 37.5ns and 75% of 90ns, respectively. Since  $t_{RCD}$  and  $t_{RC}$  exist only to safeguard the timely operation of the underlying subarray, in order to understand why their values are so large, we must first understand how the subarray operates during the activation and the precharging phases. (As previously explained, the IO phase does not occur within the subarray and its latency is overlapped with the activation

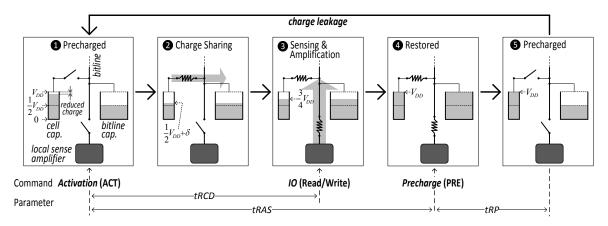

phase.) Specifically, we show how the bitline plays a crucial role in both activation and precharging, such that it heavily influences both  $t_{RCD}$  and  $t_{RC}$ . As shown in Figure 2.4, a cell transitions through five different states during each access.

Figure 2.4: DRAM Operations, Commands and Parameters

- Precharged (Initial) State. In the first state (State  $\bullet$ ), which is called the *precharged* state, before it is accessed, the cell is initially "fully" charged, while the bitline is only halfway charged (i.e., the bitline voltage is maintained at  $\frac{1}{2}V_{DD}$ ). In practice, the cell is usually not completely charged because of a phenomenon called *leakage*, wherein the cell capacitor loses charge over time.

- Activation (Charge Sharing). In order to access data from a cell, the DRAM controller issues a command called ACTIVATION. Upon receiving this command, DRAM increases the wordline voltage, thereby turning on access transistors connected to the wordline, leading to connecting their capacitors to the bitlines. Since the cell is at a higher voltage than the bitline, the charge in the cell capacitor (or the lack thereof) is slowly shared with the bitline parasitic capacitor, thereby perturbing the bitline voltage away from its quiescent value  $(\frac{1}{2}V_{DD})$  in the positive (or negative) direction until their voltages are equalized at  $\frac{1}{2}V_{DD} + \delta$  (or  $\frac{1}{2}V_{DD} \delta$ ). This is depicted in state ②, which is called charge sharing. During charge sharing, note that the cell's charge is modified (i.e., data is lost) because it is shared with the bitline. But this is only temporary since the cell's charge is restored as part of the next step, as described below.

- Activation (Sensing & Amplification). After allowing sufficient time for the charge sharing to occur, the sense amplifier is turned on. Immediately, the sense amplifier "senses" (i.e., observes) the polarity of the perturbation on the bitline voltage. Then the sense amplifier "amplifies" the perturbation by injecting (or withdrawing) charge into (or from) both the cell capacitor and the bitline parasitic capacitor. After a latency of  $t_{RCD}$ , midway through amplification, enough charge has been injected (or withdrawn) such that the bitline voltage reaches a threshold state of  $\frac{3}{4}V_{DD}$  (or  $\frac{1}{4}V_{DD}$ ). At this point, data is considered to have been "copied" from the cell to the sense amplifier (State 3). In other words, the bitline voltage is now close enough to  $V_{DD}$  (or  $\theta$ ) for the sense amplifier to detect a binary data value of '1' (or '0') and transfer the data to the IO circuitry, allowing READ and WRITE commands to be issued. After completing the sense-amplification, the voltage of the bitline and the cell are fully amplified to  $V_{DD}$  or  $\theta$  (State  $\bullet$ ). Only at this point is the charge in the cell fully restored to its original value. The latency to reach this restored state (State  $\bullet$ ) is  $t_{RAS}$  (which is one component of  $t_{RC}$ ). If there is a write operation, some additional time is required for the bitline and the cell to reach this state, which is expressed as a timing parameter called  $t_{WR}$ .

- Precharging. Before we can access data from a different cell connected to the same bitline, the sense amplifier must be taken back to the precharged state. This is done by issuing a PRECHARGE command. Upon receiving this command, DRAM first decreases the wordline voltage, thereby turning off access transistors and disconnecting the cell from the bitline. By doing so, the cell becomes decoupled from the bitline and is not affected by any future changes in the bitline voltage. Next, DRAM disables the sense amplifier and withdraws (or injects) charge from the bitline parasitic capacitor such that the bitline voltage reaches the quiescent value of  $\frac{1}{2}V_{DD}$  (State  $\odot$ ). Precharging is required to ensure that the next accessed cell can perturb the bitline voltage in either direction (towards  $V_{DD}$  or towards  $\theta$ ). This would not be possible if the bitline is left unprecharged at  $V_{DD}$  or  $\theta$ . The time taken for the precharge operation is expressed as a timing parameter called  $t_{RP}$  (which is the other component of  $t_{RC}$ ).

• Idle State (between Accesses). At state **⑤**, note that the cell is completely filled with charge. Subsequently, however, the cell slowly loses some of its charge until the next access (cycling back to state **⑥**). The length of time for which the cell can reliably hold its charge is called the cell's retention time. If the cell is not accessed for a long time, it may lose enough charge to invert its stored data, resulting in an error. To avoid data corruption, DRAM refreshes the charge in all of its cells at a regular interval, called the refresh interval. To avoid data corruption, modern DRAMs periodically access the cells to restore the lost amount of charge in all of its cells, called the refresh. This refresh operation happens at a regular interval, called the refresh interval. DRAM refresh operations waste energy and also degrade performance by delaying memory requests. This negative impacts are expected to increase in the future high capacity DRAMs. To mitigate the energy and performance impact of DRAM refresh, many works performed experimental studies to analyze DRAM refresh characteristics [119, 155, 217] and proposed hardware or software techniques [40, 156, 217].

Summary. Through our discussion, we have established a relationship between the timing constraints ( $t_{RCD}$ ,  $t_{RAS}$ ,  $t_{RP}$ , and  $t_{RC}$ ) and the internal DRAM architecture and cell operations. To summarize, these timing constraints are determined by how quickly the bitline voltage can be driven – for  $t_{RCD}$ , from  $\frac{1}{2}V_{DD}$  to  $\frac{3}{4}V_{DD}$  (threshold); for  $t_{RAS}$ , from  $\frac{1}{2}V_{DD}$  to  $V_{DD}$  (restored) and back again to  $\frac{1}{2}V_{DD}$ ; for  $t_{RP}$ , from  $V_{DD}$  to  $\frac{1}{2}V_{DD}$  precharging. In Chapter 4, we first show that the drivability of the bitline is determined by the bitline parasitic capacitance, whose value is a function of the bitline length, then proposes a new DRAM architecture that enables latency heterogeneity by changing the DRAM bitline architecture. In Chapter 5, we exploit the latency slack in the internal DRAM architecture to optimize the timing constraints for the common operation conditions. In Chapter 6, we exploit the latency variation inherited from the internal DRAM architecture to reduce DRAM latency.

## Chapter 3

### Related Prior Work

In this chapter, we describe prior proposals to reduce overall memory access latency in different areas, i) new DRAM architectures for lowering DRAM latency, ii) heterogeneous memory control techniques for reducing DRAM latency, iii) new DRAM architectures for enabling more parallelism, iv) memory scheduling to mitigate high DRAM latency, and v) other related prior works for mitigating high DRAM latency.

#### 3.1 Low Latency DRAM Architecture

Prior works aim to reduce DRAM latency in three major directions. The first approach is changing/optimizing DRAM architecture to reduce DRAM latency. The second approach is integrating low latency SRAM cells in DRAM, which can be used for caching recently accessed data. The third approach enables latency variation in DRAM. We present more detail of these three approaches. The key distinguishing factor of the proposals in this dissertation is the fact that they are low cost, while most prior works have high cost.

DRAMs Optimized for Low Access Latency. Some specialized DRAMs provide shorter latency than commodity DRAM by reducing the number of cells-per-bitline in their cell array. Micron's RL-DRAM [173] and Fujitsu's FCRAM [235] have much shorter bitlines than commodity DRAM, enabling lower latency than conventional DRAM. Embedded DRAM [42, 117, 166, 197] is recently introduced to use DRAM as the last level cache in the processor. To this end, embedded DRAM uses very short bitlines, enabling both competitive latency and much larger capacity compared to conventional SRAM-based on-chip

caches. Unfortunately, reducing cells-per-bitline requires more sense amplifiers to integrate the same amount of storage in a DRAM chip, leading to high area cost. We estimate the effective area of using shorter bitlines by using CACTI-D [268]. Our estimation shows that using 128 cells-per-bitline increases area by 30% compared to using 512 cells-per-bitline (commonly used in modern DRAM chip) because doing so requires four times the sense amplifiers of conventional DRAM. Therefore, this approach results in significantly higher cost-per-bit than conventional DRAM. Compared to these approaches, all our proposals reduce DRAM latency without significant area overhead and thus achieve both high system performance and low implementation cost.

Cached DRAM – Integrating SRAM Cache in DRAM. Cached DRAM [69, 83, 86, 90, 199, 234, 296] integrates an SRAM cache in a DRAM chip. Due to the locality in memory accesses, many requests could hit recently accessed data that is temporarily stored in the on-DRAM cache. Cached DRAM serves such requests from the low latency SRAM cells, reducing overall memory access latency. However, such cached DRAM approaches have two major limitations. First, an SRAM cache incurs significant area overhead. Based on DRAM area analysis using CACTI-D [268], an SRAM-cached DRAM requires 145.3% additional area (leading to requiring 245.3% area of the baseline conventional DRAM) to integrate SRAM cells (6% of total DRAM capacity) in a DRAM chip. Second, transferring data between the DRAM array and the SRAM cache requires the use of relatively narrow global I/O buses within the DRAM chip, leading to high latency to move the data from the DRAM array into the SRAM cache (and vice versa).

Compared to this approach, our proposals reduce DRAM latency without significant area overhead and thus achieve both high system performance and low implementation cost.

Enabling Latency Heterogeneity in DRAM. Son et al. [252] proposed a low latency DRAM architecture in two major directions. First, it integrates both short bitline subarrays, which have low access latency, and long bitline subarrays, which have high access latency, within a DRAM chip. Second, it leverages the latency difference from the physical locations of banks. For example, banks near an IO interface can be accessed with lower latency than banks far from an IO interface. Therefore, this approach enables latency heterogeneity in

DRAM by enabling different bitline lengths in different locations. For example, accessing a subarray, which is near the IO interface and which consists of short bitlines, has the lowest access latency. This static partitioning of different latency regions limits the effectiveness of the approach. One shortcoming of the design is the high latency required to move data between the slow and fast regions. This approach provides largest benefit if latency critical data is statically allocated to the low latency regions (the low latency subarrays). Static identification of latency critical or hot data could be difficult.

Lu et al. [159] improves the heterogeneous subarray architecture (having both long bitline subarrays and short bitline subarrays) by introducing low-latency migration capability between slow and fast subarrays. In the open-bitline scheme [96], even bitlines are connected to the upper sense amplifiers and odd bitlines are connected to the lower sense amplifiers. This work introduces new DRAM cells to connect these two bitlines (one connected to the upper sense amplifier and the other to the lower sense amplifier), enabling data migration between slow and fast subarrays (e.g., long bitline subarrays and short bitline subarrays). However, this approach requires specialized migration cells, leading to higher manufacturing cost.

Our first approach (TL-DRAM) reduces DRAM latency by introducing latency heterogeneity *within* a subarray, which is different from the works of Son et al. and Lu et al., which enable heterogeneity *across* subarrays. As such, TL-DRAM can achieve very fast migration between the slow and fast regions of the same subarray.

Our two other approaches (AL-DRAM and AVA-DRAM) reduce DRAM latency by exploiting the existing latency slack in DRAM, which none of these prior works has leveraged. Therefore, our proposals can be combined with these prior works in a synergistic manner to achieve even lower DRAM latency than all individual proposals.

# 3.2 Reducing DRAM Latency by Enabling Heterogeneous Memory Control

Prior works optimize DRAM latency for the operating conditions by exploiting process variation [37] or memory access patterns [85, 247]. The key distinguishing factor of our proposals is the fact that they provide mechanisms to maintain *reliability* while reducing DRAM latency.

Heterogeneous Memory Control Based on Process and Voltage Variation. Chandrasekar et al. [37] evaluate the potential of relaxing some DRAM timing parameters to reduce DRAM latency. This work observes latency variations across DIMMs as well as for a DIMM at different operating temperatures. However, there is no explanation as to why this phenomenon exists and no clear mechanism to exploit it in this prior work.

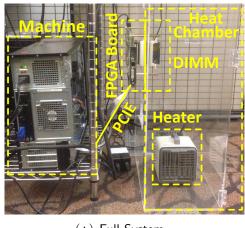

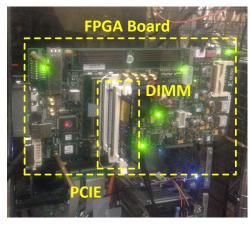

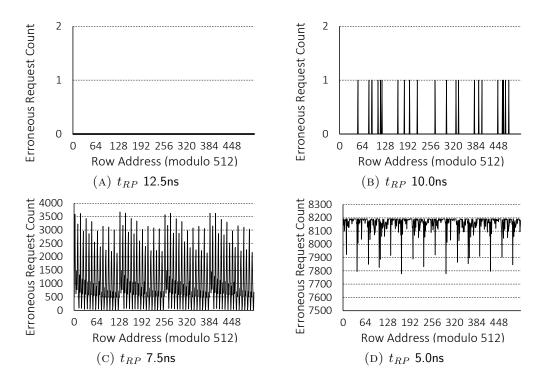

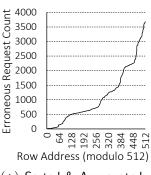

Heterogeneous Memory Control Based on Memory Access Patterns. Shin et al. [247] show that DRAM leakage affects two DRAM timing parameters  $(t_{RCD}/t_{RAS})$ . As a result, recently-refreshed rows have more charge, and can be accessed with lower latency than DRAM standard. Based on this observation, they propose a mechanism to access recently refreshed rows with reduced latency. However, this approach has two limitations. First, this work focuses only on the latency variation between refreshes, resulting in relatively small performance gains. Second, it is not clear how the proposed mechanism affects DRAM reliability.