# Accelerating Sparse Matrix Kernels with Co-Optimized Architecture

Submitted in partial fulfillment of the requirements for The degree of

DOCTOR OF PHILOSOPHY

IN

ELECTRICAL AND COMPUTER ENGINEERING

#### Fazle Sadi

B.Sc., EEE, BANGLADESH UNIVERSITY OF ENGINEERING AND TECHNOLOGY M.A.Sc., ECE, THE UNIVERSITY OF BRITISH COLUMBIA M.Sc., ECE, CARNEGIE MELLON UNIVERSITY

> Advisors: Professor Larry Pileggi Professor Franz Franchetti

CARNEGIE MELLON UNIVERSITY PITTSBURGH, PA, USA

December 2018

© Copyright by Fazle Sadi, 2018.

All rights reserved.

## Abstract

This dissertation presents an architecture to accelerate sparse matrix linear algebra, which is among the most important numerical methods for numerous science and engineering domains, such as graph analytics, in current big data driven era. Sparse matrix operations, especially for unstructured and large matrices with very few nonzeros, are devoid of guaranteed temporal and/or spatial locality making them inherently unsuitable for cache based general purpose commercial off-the-shelf (COTS) architectures. Lack of locality causes data dependent high latency memory accesses and eventually exhausts limited load buffer in COTS architectures. These render sparse kernels to run at a small fraction of peak machine speed and yield poor off-chip bandwidth saturation despite finely tuned software libraries/frameworks and optimized code. The poor utilization of compute and memory resources on COTS structures indicates significant room for improvement using existing technology. However, a computation paradigm that is not dependent on data locality is essential for sparse operations to achieve same level of performance that BLAS-like standards on COTS have delivered for dense matrix linear algebra.

An algorithm/hardware co-optimized architecture that provides a data locality independent platform for sparse matrix operations is developed in this work. The proposed architecture is founded on a fundamental principle of trading streaming bandwidth and compute to avoid high latency accesses. This principle stems from a counterintuitive insight that minimally required number of irregular memory accesses for sparse operations generally incur high traffic that is transferred at slow speed, whereas, more regular accesses can provide reduced traffic overall and faster transfer through better usage of block level data. This work finds that a scalable, high performance and parallelizable multi-way merge network, which is absent in current literature, is the core hardware primitive required in developing our proposed architecture. Through both algorithmic and circuit level techniques, this work develops a novel multi-way merge hardware primitive that meaningfully eliminates high latency accesses for sparse operations. This work also demonstrates methodologies to avoid strong dependency on fast random access on-chip memory for scaling, which is a major limiting factor of current custom hardware solutions in handling very large problems.

Using a common custom platform, this work shows implementations of Sparse Matrix dense Vector multiplication (SpMV), iterative SpMV and Sparse General Matrix-Matrix multiplication (SpGEMM), which are core kernels for a broad range of graph analytic applications. A number of architecture and circuit level optimization techniques for reducing off-chip traffic and improving computation throughput to saturate extreme off-chip steaming bandwidth, provided by state of the art 3D stacking technology, are developed. Our proposed custom hardware is demonstrated on ASIC (fabricated in 16nm FinFET) and FPGA platforms and evaluated against state of the art COTS and custom hardware solutions. Experimental results show more than an order of magnitude improvement over current custom hardware solutions and more than two orders of magnitude improvement over COTS architectures for both performance and energy efficiency. This work is intended to contribute through a software stack provided by GraphBLAS-like [1] standards where broadest possible audience can utilize this architecture using a well-defined and concise set of matrix-based graph operations.

### Acknowledgements

First and foremost, I would like to thank my supervisors Professor Larry Pileggi and Professor Franz Franchetti. I sincerely consider myself fortunate to have such well suited combination of supervision, without which this interdisciplinary research wouldn't have been possible. Larry and Franz provided me great flexibility and guidance to preserve and enjoy graduate school. At the same time they presented me ample opportunities to evolve as an independent researcher. To me both of them are great mentors.

I would also like to thank my committee members Professor James C. Hoe and Dr. Aydın Buluç for their important feedback on this thesis. I am specially thankful to James for guiding me as his own student when my project got involved with FPGAs. I have gained valuable perspectives from the insightful discussions I had with James about life within and outside academia. I am also grateful to Dr. Scott McMillan from Software Engineering Institute (SEI) for his mentorship during the last couple of years.

My first few years in graduate school would have difficult if not for my fellow group members Kaushik Vaidyanathan, Ekin Sumbul and Qiuling Zhu. Their work ethics and helpfulness allowed to me have a head start with my research. I would also like to thank Shaolong Liu, Jing Huang, Paul Brouwer, Jinglin (Kiki) Xu, Berkin Akin, Bishnu Prasad Das, Sam Pagliarini, Meric Isgenc and Joe Sweeney for their help, encouragement and friendship.

I am extremely grateful for the endless support that I received from the tightly knit group of friends at A level. I would like to individually thank Thom Popovici, Daniele Spampinato, Tze Meng low, Richard Veras, Guanglin Xu, Jiyuan Zhang and Anuva Kulkarni. I don't think I would have such memorable experience at CMU without them. I will always cherish their friendship.

I would like to express my gratitude to DARPA, IARPA and SEI for creating and nourishing a collaborative ecosystem necessary in undertaking such interdisciplinary research. The 16nm ASIC fabrication was funded by DARPA CRAFT program and the initial research was sponsored by DARPA PERFECT program. I would like to acknowledge IARPA TIC program for sponsoring Stratix<sup>®</sup> 10 FPGAs.

Most importantly I would like to thank my parents, brother, sister, relatives and in-laws for their never-ending love and support. I will always be indebted to my parents for the unthinkable sacrifices they made to grow me as an individual.

I am also grateful to our two pet birds, Tweety and Boo. Somehow they are always able to impart their joyfulness to us during difficult moments of life.

Finally, my journey of graduate school would have been impossible without my best friend and wife Faria. It is for her that I will always cherish the memories that graduate school has gifted us.

To my parents.

## Contents

|          | Abs  | $\operatorname{ract}$                              | iii |

|----------|------|----------------------------------------------------|-----|

|          | Ack  | nowledgements                                      | v   |

|          | List | of Tables                                          | cii |

|          | List | of Figures                                         | iv  |

| 1        | Intr | oduction                                           | 1   |

|          | 1.1  | Motivation                                         | 1   |

|          | 1.2  | Thesis Contributions                               | 3   |

|          |      | 1.2.1 Approach and Scope                           | 7   |

|          |      | 1.2.2 Effort vs Benefit                            | 9   |

|          |      | 1.2.3 Key Developments                             | 10  |

|          | 1.3  | Background                                         | 13  |

|          |      | 1.3.1 Sparse Matrix Kernel Acceleration Challenges | 14  |

|          |      | 1.3.2 Related Work in Literature                   | 15  |

|          | 1.4  | Dissertation Outline 1                             | 19  |

| <b>2</b> | Two  | 22-Step SpMV Algorithm                             | 22  |

|          | 2.1  | SpMV Operation on Large Matrices                   | 23  |

|          | 2.2  | Proposed Two-Step SpMV                             | 25  |

|   |      | 2.2.1   | Advantages of Two-Step SpMV                         | 28 |

|---|------|---------|-----------------------------------------------------|----|

|   | 2.3  | Evalua  | ation of Two-Step SpMV                              | 29 |

|   |      | 2.3.1   | Non-Streaming SpMV                                  | 29 |

|   |      | 2.3.2   | Streaming SpMV                                      | 31 |

|   | 2.4  | Challe  | enges                                               | 38 |

|   |      | 2.4.1   | Multi-way Merge for Two-Step SpMV                   | 38 |

|   |      | 2.4.2   | Multi-way Merge for other Sparse Matrix Operations  | 39 |

|   | 2.5  | Summ    | ary                                                 | 40 |

| 3 | Scal | lable N | Aulti-way Merge                                     | 41 |

|   | 3.1  | Scalab  | pility                                              | 42 |

|   | 3.2  | Proble  | em Scaling                                          | 44 |

|   |      | 3.2.1   | Register FIFO based Multi-way Merge                 | 44 |

|   |      | 3.2.2   | Block Memory based Multi-way Merge                  | 46 |

|   |      | 3.2.3   | Block Memory based Merge: Advantages and Challenges | 48 |

|   |      | 3.2.4   | Block Memory based Merge: Current Solutions         | 49 |

|   | 3.3  | Comp    | arison Look Ahead Merge (CLAM)                      | 53 |

|   |      | 3.3.1   | CLAM Implementation and Operational Details         | 56 |

|   | 3.4  | Techn   | ology Scaling                                       | 66 |

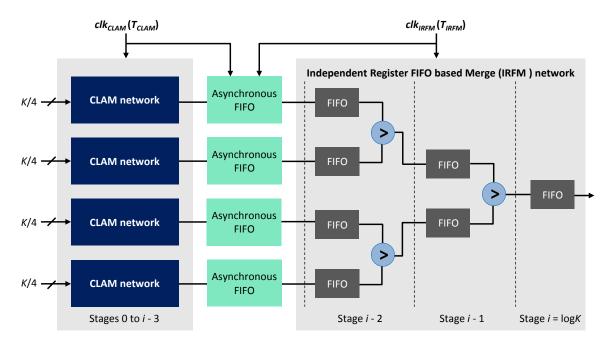

|   | 3.5  | Hybrid  | d CLAM (HCLAM)                                      | 68 |

|   | 3.6  | Parall  | el Multi-way Merge                                  | 70 |

|   |      | 3.6.1   | Parallelization by Input List Partitioning          | 71 |

|   |      | 3.6.2   | Parallelization by Radix Pre-sorter (PRaP)          | 72 |

|   | 3.7  | Summ    | ary                                                 | 77 |

| 4        | Imp  | olemen  | tation of Two-Step SpMV                                        | 79    |

|----------|------|---------|----------------------------------------------------------------|-------|

|          | 4.1  | Design  | n Goals and Challenges                                         | . 80  |

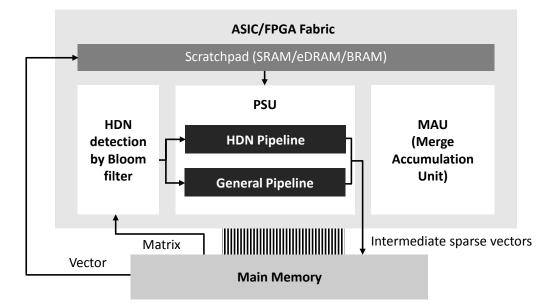

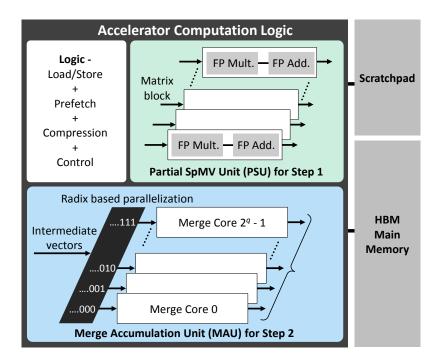

|          | 4.2  | Propo   | sed Architecture                                               | . 82  |

|          | 4.3  | Imple   | mentation of Step 1                                            | . 85  |

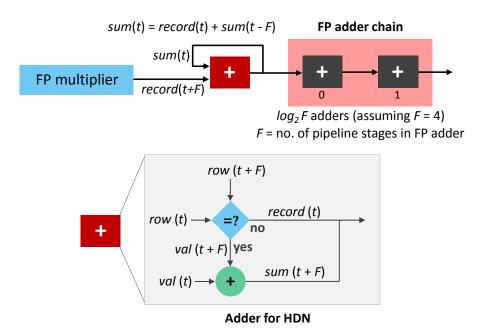

|          |      | 4.3.1   | Adder Chain                                                    | . 90  |

|          |      | 4.3.2   | Shift-Reduction Chain                                          | . 91  |

|          |      | 4.3.3   | Challenges with Power-law Graphs                               | . 92  |

|          | 4.4  | Imple   | mentation of Step 2                                            | . 97  |

|          | 4.5  | Meta-   | Data Compression                                               | . 100 |

|          | 4.6  | Summ    | nary                                                           | . 105 |

| <b>5</b> | Iter | ative ' | Two-Step SpMV and On-chip Memory Requirement                   | 107   |

|          | 5.1  | PageF   | ank                                                            | . 108 |

|          |      | 5.1.1   | SpMV Optimization by Iteration Overlap                         | . 109 |

|          |      | 5.1.2   | Advantages of Iteration Overlapped Two-Step SpMV $\ . \ . \ .$ | . 112 |

|          | 5.2  | On-ch   | ip Memory Requirement                                          | . 114 |

|          |      | 5.2.1   | Comparison with Current Solutions                              | . 115 |

|          |      | 5.2.2   | Energy Efficiency                                              | . 117 |

|          |      | 5.2.3   | Fast Storage vs Compute                                        | . 118 |

|          | 5.3  | Summ    | nary                                                           | . 120 |

| 6        | Eva  | luatio  | n of Performance & Energy Efficiency of SpMV                   | 121   |

|          | 6.1  | Imple   | mentation Platform & Design Points                             | . 122 |

|          |      | 6.1.1   | ASIC based Implementation                                      | . 123 |

|          |      | 6.1.2   | FPGA based Implementation                                      | . 125 |

|          | 6.2  | Comp    | arison against Custom Hardware and GPU                         | . 126 |

|    |        | 6.2.1   | Performance against Custom Hardware Solutions     | 128 |

|----|--------|---------|---------------------------------------------------|-----|

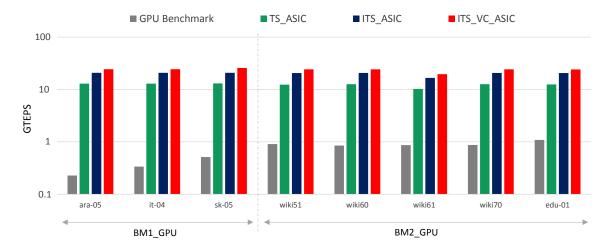

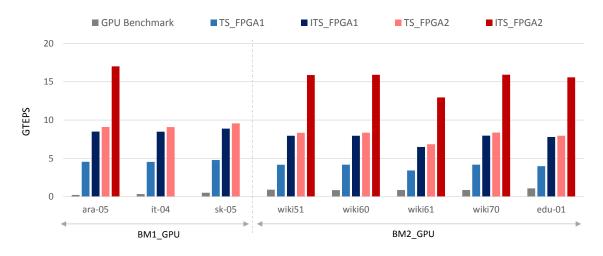

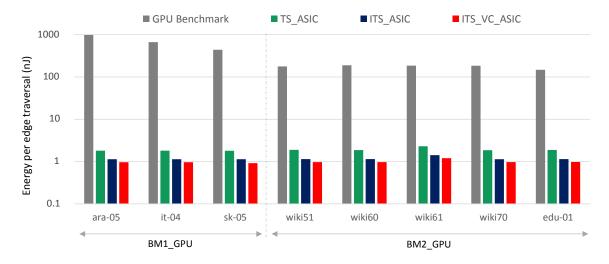

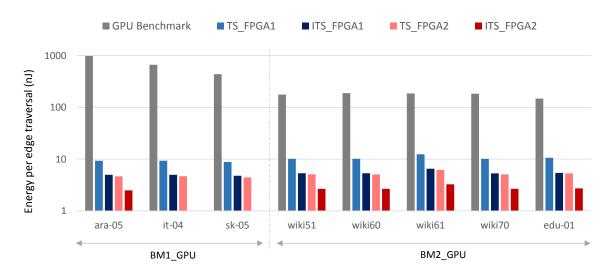

|    |        | 6.2.2   | Performance & Efficiency against GPU Solutions    | 129 |

|    | 6.3    | Comp    | arison against CPU and Co-Processor               | 133 |

| 7  | Acc    | elerati | ing Sparse Matrix-Sparse Matrix Operation         | 139 |

|    | 7.1    | Backg   | round and Challenges                              | 140 |

|    |        | 7.1.1   | Computation related Challenges                    | 141 |

|    |        | 7.1.2   | Partition and Off-chip Traffic related Challenges | 144 |

|    | 7.2    | Propo   | sed SpGEMM                                        | 148 |

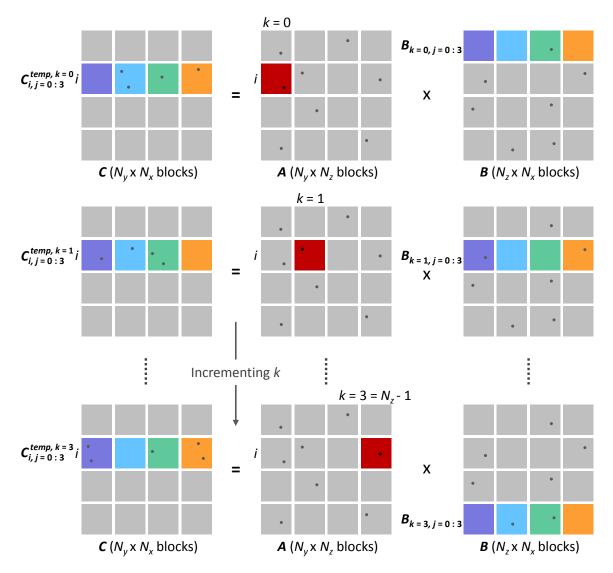

|    |        | 7.2.1   | SpGEMM Computation with SSPA                      | 149 |

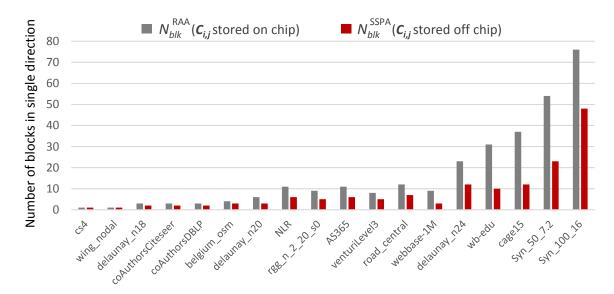

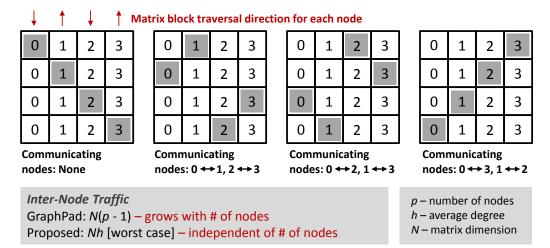

|    |        | 7.2.2   | Block Traversal using BPOP                        | 161 |

|    | 7.3    | Evalua  | ation and Results                                 | 164 |

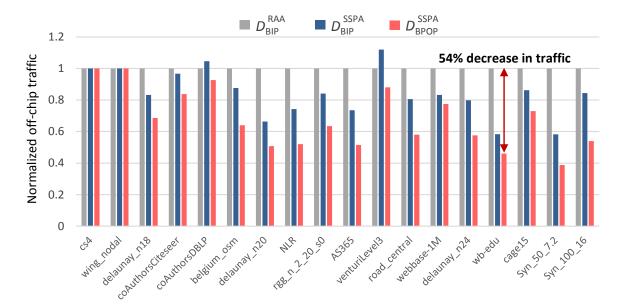

|    |        | 7.3.1   | Off-chip Traffic Reduction                        | 166 |

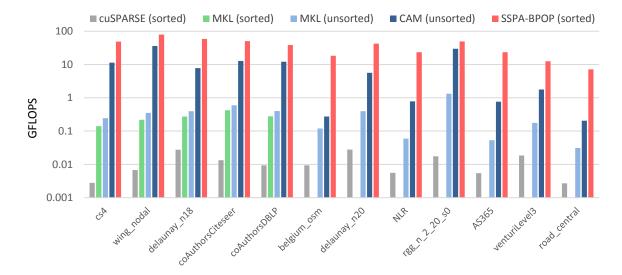

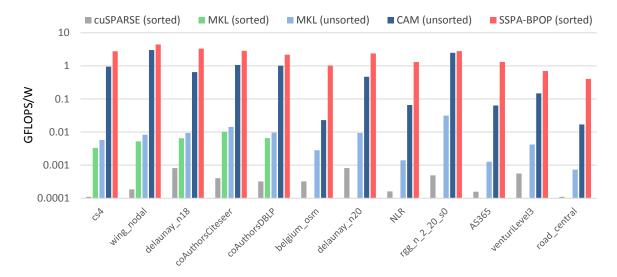

|    |        | 7.3.2   | Performance and Energy Efficiency                 | 167 |

| 8  | Fut    | ure Di  | rections and Conclusion                           | 170 |

|    | 8.1    | Future  | e Directions                                      | 170 |

|    | 8.2    | Conclu  | uding Remarks                                     | 173 |

| Bi | ibliog | graphy  |                                                   | 177 |

## List of Tables

| 2.1 | Off-chip traffic volume between DRAM and on-chip memory for Row-                                              |

|-----|---------------------------------------------------------------------------------------------------------------|

|     | major Block traversed Algorithms (RBA) (row-major block access) $~$ . $~$ 34 $~$                              |

| 2.2 | Off-chip traffic volume between DRAM and on-chip memory for Column-                                           |

|     | major Block traversed Algorithms (CBA) (column-major block access). 35                                        |

| 2.3 | Speedup of CBA over RBA on typical systems                                                                    |

| 5.1 | Fast on-chip memory requirement and largest graph dimension compar-<br>ison of current and proposed solutions |

| 6.1 | Maximum graph dimension and throughput for different design point                                             |

|     | and implementation variations of proposed SpMV accelerator 123 $$                                             |

| 6.2 | Graph data sets used for comparison with custom hardware                                                      |

|     | (ASIC/FPGA) benchmarks                                                                                        |

| 6.3 | Graph data sets used for comparison with custom hardware                                                      |

|     | (ASIC/FPGA) benchmarks                                                                                        |

| 6.4 | Graph data sets used for comparison with GPU benchmarks 128 $$                                                |

| 6.5 | Graph data sets used for comparison with CPU and many-core co-                                                |

|     | processor benchmarks                                                                                          |

| 7.1 Gra | iph data | i sets use | d for | SpGEMM | analysis. |  |  |  |  |  |  |  |  |  |  |  |  |  | 165 |

|---------|----------|------------|-------|--------|-----------|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

|---------|----------|------------|-------|--------|-----------|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

# List of Figures

| 1.1 | a) Traditional memory hierarchy used in general purpose architectures        |    |

|-----|------------------------------------------------------------------------------|----|

|     | that is not suitable for sparse operations, b) Low peak to actual perfor-    |    |

|     | mance ratio, and c) Redundant traffic and inefficient DRAM access of         |    |

|     | SpMV on traditional architecture                                             | 2  |

| 1.2 | Off-chip traffic of SpMV using latency bound and full streaming algorithms.  | 4  |

| 1.3 | Contribution of this dissertation in graph analytics acceleration ecosystem. | 6  |

| 1.4 | Example of performance and energy efficiency improvement of proposed         |    |

|     | ASIC architecture.                                                           | 8  |

| 1.5 | Custom ASIC for proposed accelerator.                                        | 8  |

| 2.1 | Sparse Matrix dense Vector multiplication (SpMV) operation                   | 23 |

| 2.2 | Two-Step SpMV algorithm.                                                     | 25 |

| 2.3 | Row major sparse formats                                                     | 26 |

| 2.4 | Redundant data transfer and random access in non-streaming SpMV. $$ .        | 30 |

| 2.5 | Off-chip traffic comparison between non-streaming and Two-Step SpMV.         | 31 |

| 2.6 | Matrix blocking and different ways of block traversal                        | 33 |

| 3.1 | Binary tree implementation of naive multi-way merge network                  | 43 |

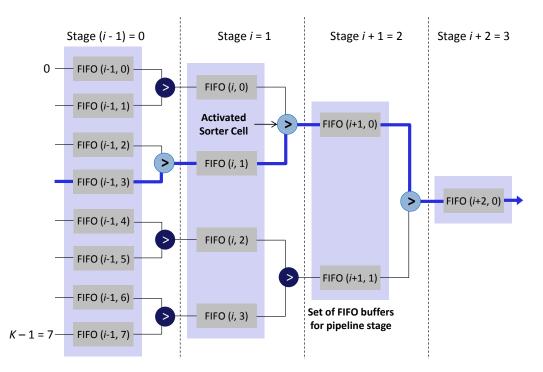

| 3.2  | Pipelined multi-way merge binary tree implemented using independent             |    |

|------|---------------------------------------------------------------------------------|----|

|      | register based FIFOs (IRFM). Highlighted blue line represents activated         |    |

|      | path in a given clock cycle                                                     | 45 |

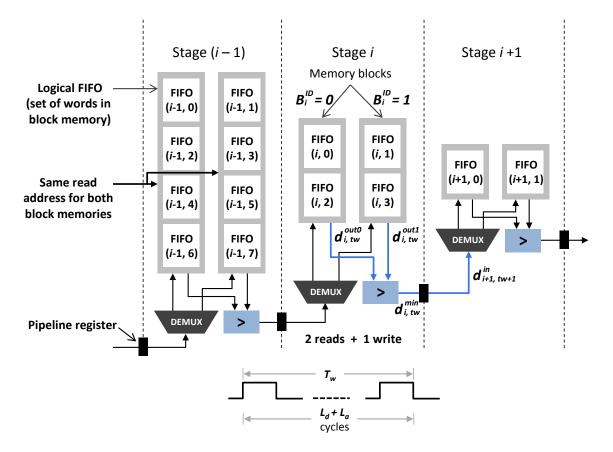

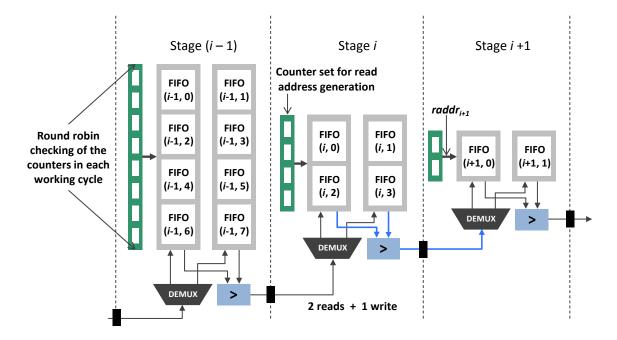

| 3.3  | Block memory based multi-way merge network (Scheme-1)                           | 48 |

| 3.4  | Block memory based multi-way merge network (Scheme-1a)                          | 50 |

| 3.5  | Block memory based multi-way merge network ( <i>Scheme-1b</i> )                 | 52 |

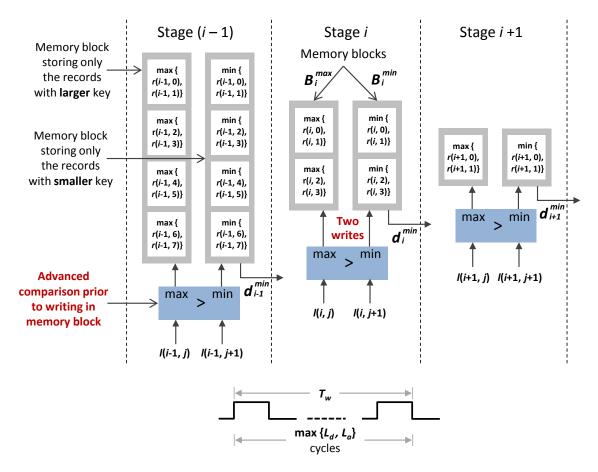

| 3.6  | Conceptual block diagram of advanced comparison based proposed                  |    |

|      | multi-way merge hardware CLAM.                                                  | 55 |

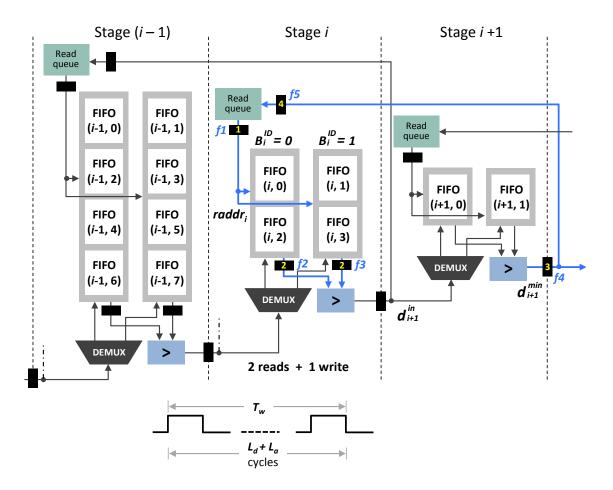

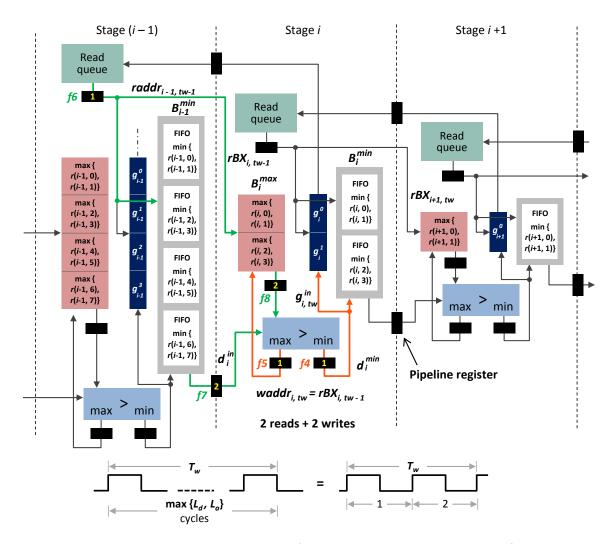

| 3.7  | CLAM hardware diagram (excluding pipeline registers) and initialization         |    |

|      | operation at work cycle $t_w - 1$ and $t_w$ . The blue and black paths show     |    |

|      | active paths during initialization work cycles $t_w-1$ and $t_w$ respectively.  | 57 |

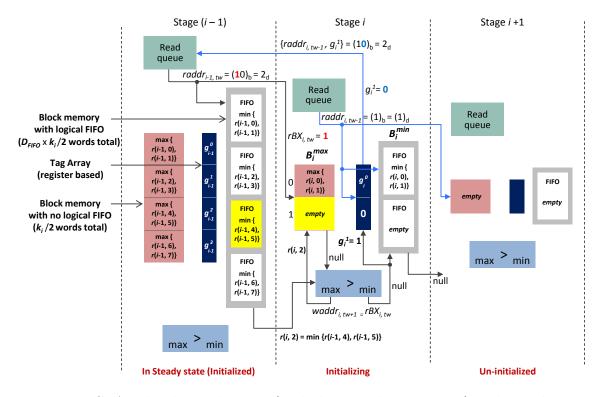

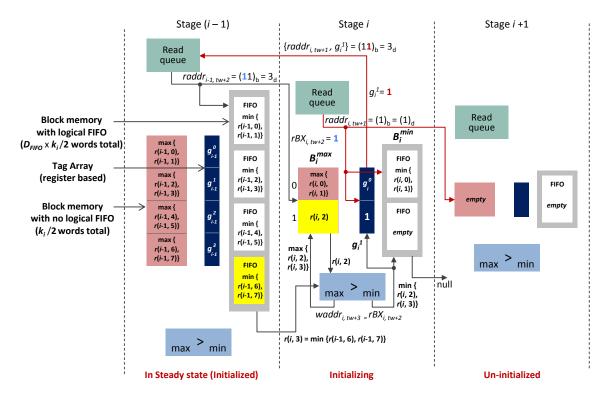

| 3.8  | CLAM hardware diagram (excluding pipeline registers) and initialization         |    |

|      | operation at work cycle $t_w + 1$ and $t_w + 2$ . The red and black paths       |    |

|      | show the active paths during initialization work cycles $t_w + 1$ and $t_w + 2$ |    |

|      | respectively                                                                    | 58 |

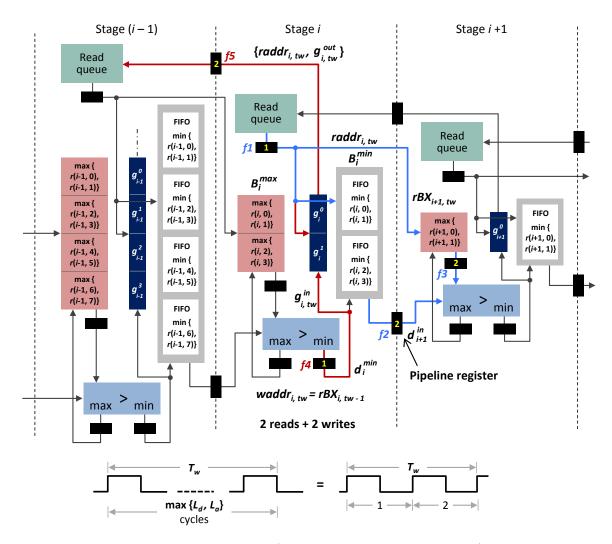

| 3.9  | CLAM hardware diagram (including all pipeline registers) and steady             |    |

|      | state read and address generation operations. The blue and red paths            |    |

|      | show the active paths for read and address generation respectively              |    |

|      | during $t_w$                                                                    | 62 |

| 3.10 | CLAM hardware diagram (including all pipeline registers) and steady             |    |

|      | state read and write operations. The green and orange paths show the            |    |

|      | active paths for read at $t_w - 1$ and write at $t_w$ respectively              | 63 |

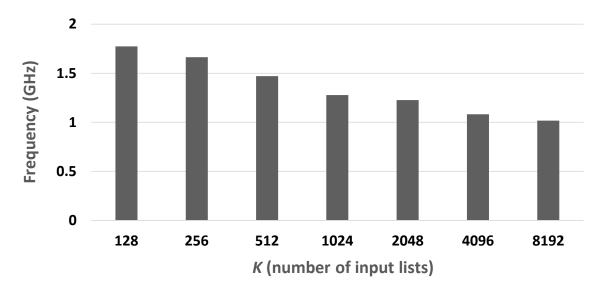

| 3.11 | Problem size scaling of CLAM vs achievable clock frequency in 16nm              |    |

|      | FinFET ASIC.                                                                    | 66 |

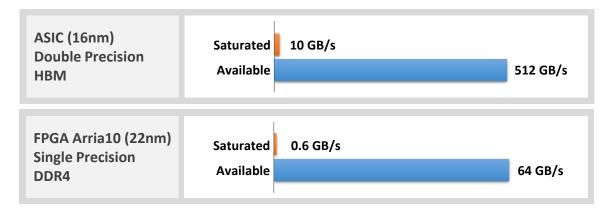

| 3.12 | Single CLAM multi-way merge network streaming bandwidth consump-                          |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | tion on ASIC (2048-way) and FGPA (64-way) platforms                                       | 67 |

| 3.13 | Hybrid Comparison Look Ahead Merge (HCLAM).                                               | 68 |

| 3.14 | Single HCLAM multi-way merge network streaming bandwidth con-                             |    |

|      | sumption on ASIC (2048-way) and FGPA (64-way) platforms                                   | 71 |

| 3.15 | multi-way merge parallelization by partitioning input lists for Two-Step                  |    |

|      | SpMV. This method becomes unscalable when the problem is larger                           |    |

|      | than on-chip memory                                                                       | 72 |

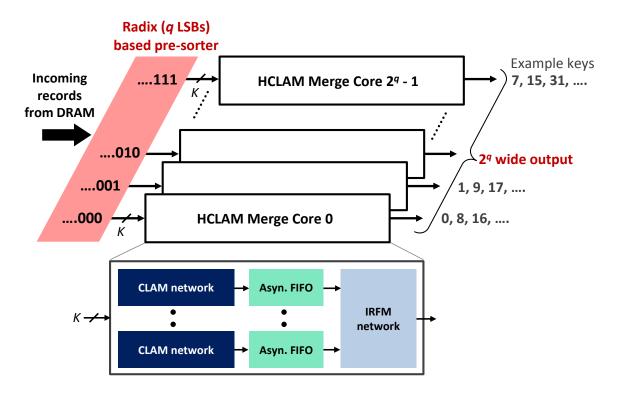

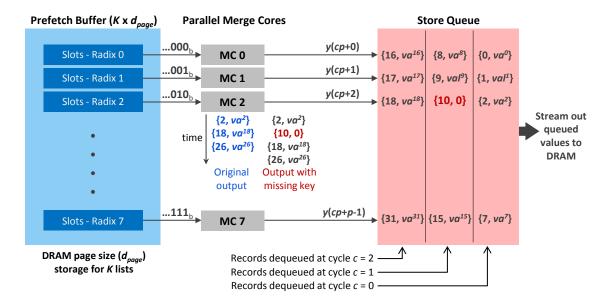

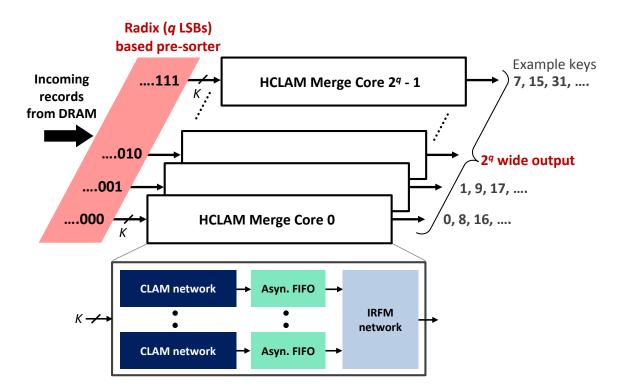

| 3.16 | HCLAM PRaP unit. Wide output multi-way merge implementation                               |    |

|      | using radix pre-sorter and multiple parallel HCLAM cores                                  | 74 |

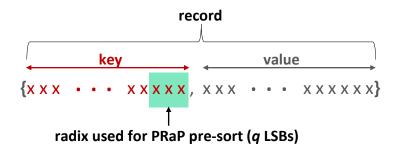

| 3.17 | Radix selection for pre-sort in PRaP                                                      | 74 |

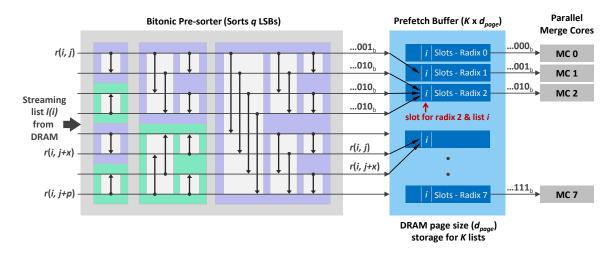

| 3.18 | Radix pre-sorter implementation using Bitonic sorter and prefetch buffer.                 |    |

|      | We assume that $r(i, j)$ and $r(i, j + x)$ has the same radix                             | 75 |

| 3.19 | Load balancing and synchronization by insertion of missing keys in                        |    |

|      | PRaP when output is dense                                                                 | 76 |

| 4.1  | Two-Step SpMV algorithm.                                                                  | 81 |

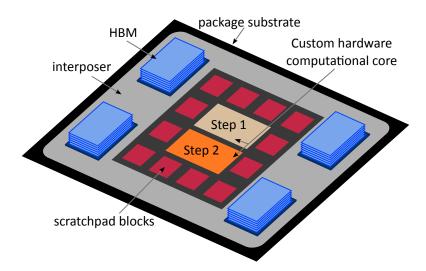

| 4.2  | Custom hardware based sparse matrix kernel acceleration system in-                        |    |

|      | cluding High Bandwidth Memory (HBM) and interposer                                        | 83 |

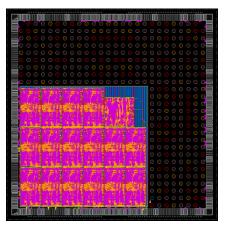

| 4.3  | 16nm FinFET Application Specific Integrated Circuit (ASIC) (currently                     |    |

|      | under fabrication) for sparse matrix kernel acceleration                                  | 84 |

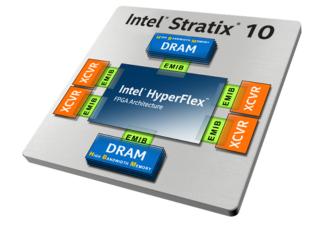

| 4.4  | Intel <sup>®</sup> Stratix <sup>®</sup> 10 FPGA platform [69]. $\ldots$ $\ldots$ $\ldots$ | 84 |

| 4.5  | Partial SpMV Unit (PSU) to conduct step 1 of Two-Step algorithm by                        |    |

|      | sharing entire scratchpad.                                                                | 86 |

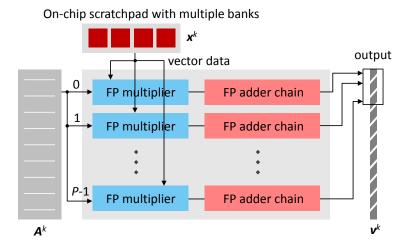

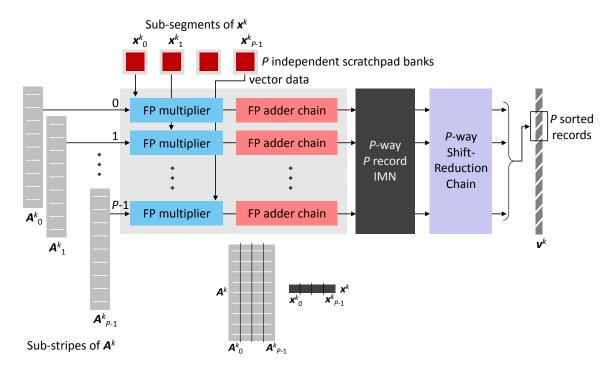

| 4.6  | Partial SpMV Unit (PSU) to conduct step 1 of Two-Step algorithm using     |

|------|---------------------------------------------------------------------------|

|      | Insertion based Merge Network (IMN) and independent scratchpad bank       |

|      | access                                                                    |

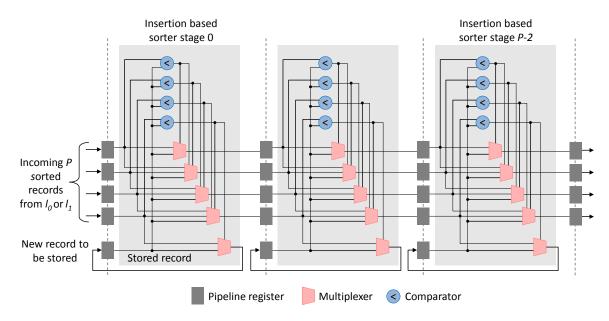

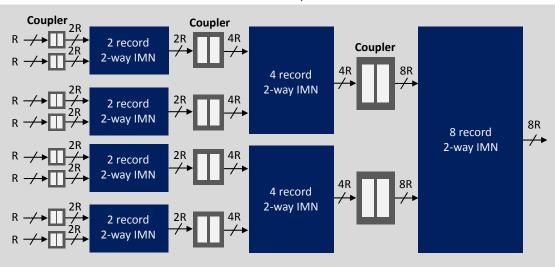

| 4.7  | Insertion based Merge Network (IMN) sorting stages                        |

| 4.8  | Construction of $P$ record $P$ -way IMN from smaller 2-way IMNs 89        |

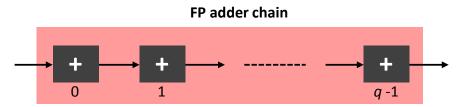

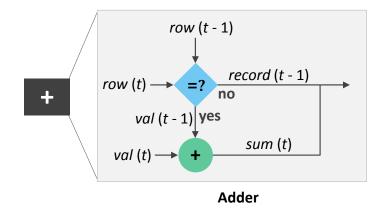

| 4.9  | Floating Point (FP) adder chain structure to avoid stalls due to internal |

|      | pipelines in the adder                                                    |

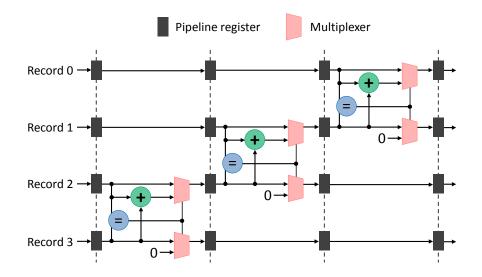

| 4.10 | Shift-reduction chain to handle collisions among sub-stripes. This        |

|      | diagram illustrates a 4-way shift-reduction chain                         |

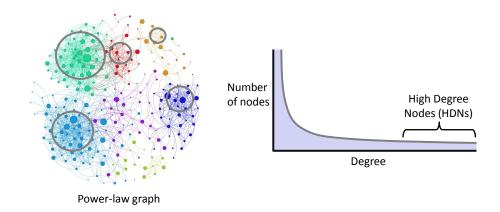

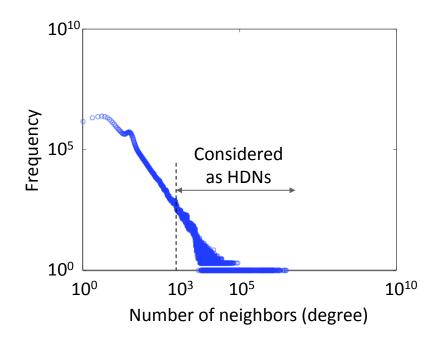

| 4.11 | Power-law graph and degree distribution                                   |

| 4.12 | Multiplier-adder set for the computation of High Degree Nodes (HDNs)      |

|      | in power-law graph                                                        |

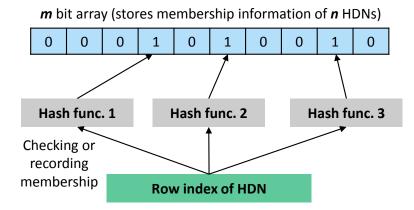

| 4.13 | Bloom Filter filter based method to process HDNs of power-law graphs      |

|      | efficiently for Two-Step SpMV implementation                              |

| 4.14 | Degree distribution of example graph 'Twitter_www' [55]                   |

| 4.15 | HCLAM PRaP unit                                                           |

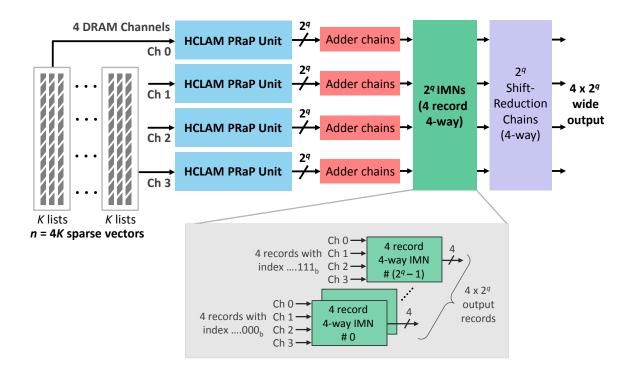

| 4.16 | Merge Accumulation Unit (MAU) implementing $2^{nd}$ step of Two-Step      |

|      | SpMV using 4 DRAM channels                                                |

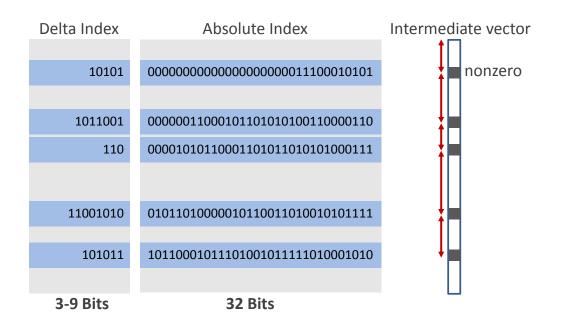

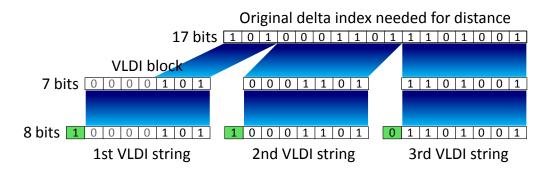

| 4.17 | Delta index vs absolute index as meta-data                                |

| 4.18 | Construction of Variable Length Delta Index (VLDI) strings from delta     |

|      | index                                                                     |

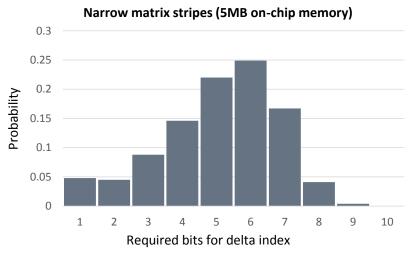

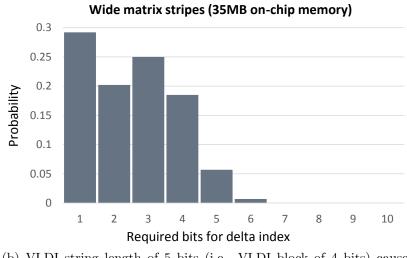

| 4.19 | Probability distribution of delta index widths for two different on-      |

|      | chip memory sizes and a randomly generated Erdos Rényi graph with         |

|      | dimension 80M×80M and average degree of 3                                 |

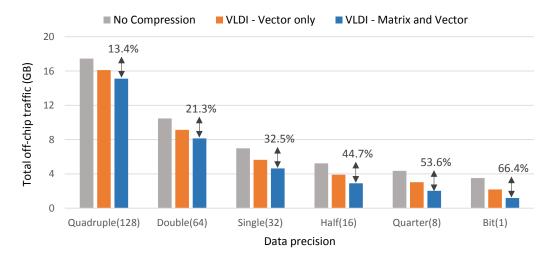

| 4.20 | off-chip traffic reduction using VLDI meta-data compression 105           |

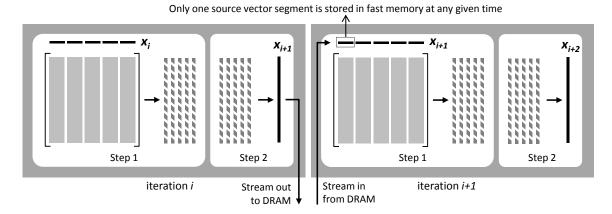

| 5.1 | Two-Step SpMV driven PageRank with independent iterations $(PR_TS)$ .109                                |

|-----|---------------------------------------------------------------------------------------------------------|

| 5.2 | Off-chip traffic optimized PageRank with iteration overlap $(PR\_ITS).~.~110$                           |

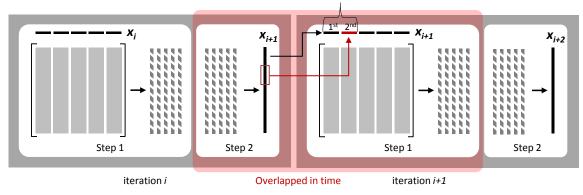

| 5.3 | Sustained computation throughput/streaming speed of $PR\_ITS$ vs                                        |

|     | $PR_{-}TS$ implemented in ASIC platform                                                                 |

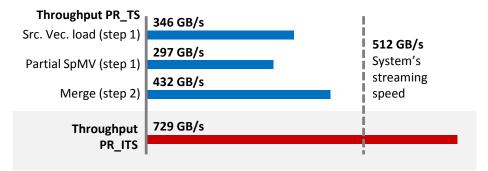

| 5.4 | Off-chip communication of PageRank using $TS$ vs $ITS$ (Iteration-                                      |

|     | overlapped $TS$ )                                                                                       |

| 5.5 | On-chip storage requirement for proposed Two-Step SpMV 115                                              |

| 5.6 | Energy consumption by different parts of the system for Two-Step                                        |

|     | SpMV acceleration                                                                                       |

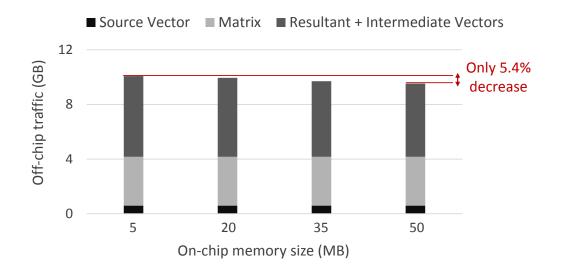

| 5.7 | Total off-chip traffic of Two-Step SpMV for different on-chip memory size.119                           |

| 5.8 | Trade-off between on-chip storage and computation in designing Two-                                     |

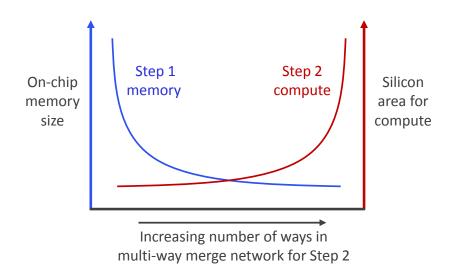

|     | Step SpMV accelerator                                                                                   |

| 6.1 | 16nm FinFET ASIC (currently under fabrication) for sparse matrix                                        |

|     | kernel acceleration                                                                                     |

| 6.2 | 16nm FinFET ASIC (currently under fabrication) for sparse matrix                                        |

|     | kernel acceleration                                                                                     |

| 6.3 | ${\rm Intel}^{\textcircled{R}}$ Stratix $\textcircled{R}$ 10 Field Programmable Gate Array (FPGA) plat- |

|     | form [69]                                                                                               |

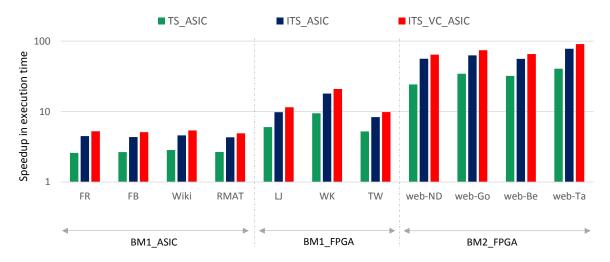

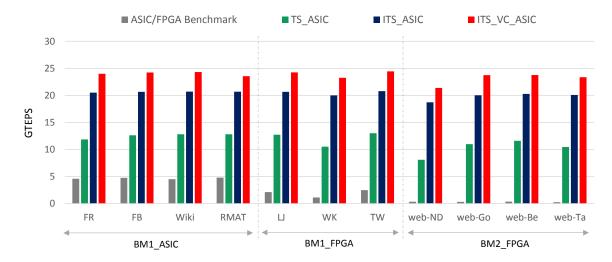

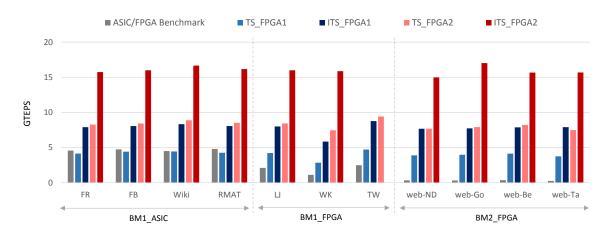

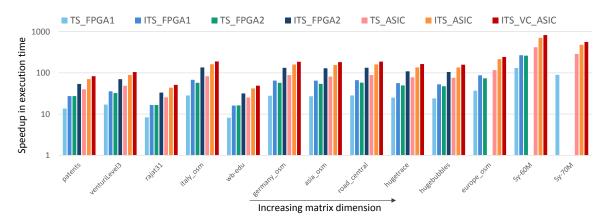

| 6.4 | Speedup of proposed ASIC over custom hardware benchmarks 129                                            |

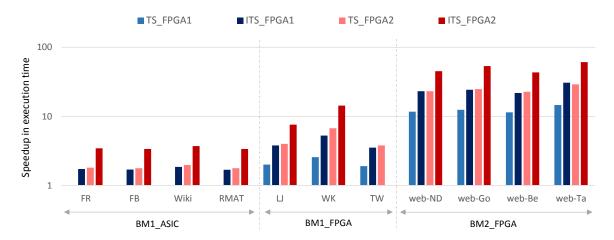

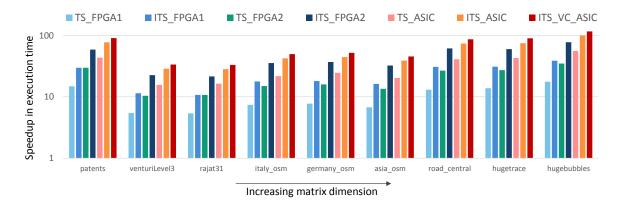

| 6.5 | Speedup of proposed FPGA implementations over custom hardware                                           |

|     | benchmarks                                                                                              |

| 6.6 | Comparison of Giga Traversed Edges Per Second (GTEPS) for proposed                                      |

|     | ASIC against custom hardware benchmarks                                                                 |

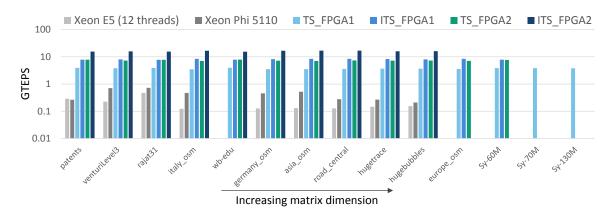

| 6.7  | Comparison of GTEPS for proposed FPGA implementations against        |

|------|----------------------------------------------------------------------|

|      | custom hardware benchmarks                                           |

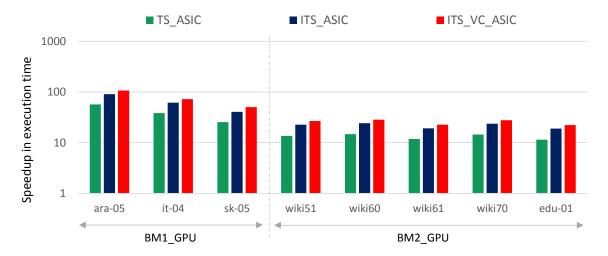

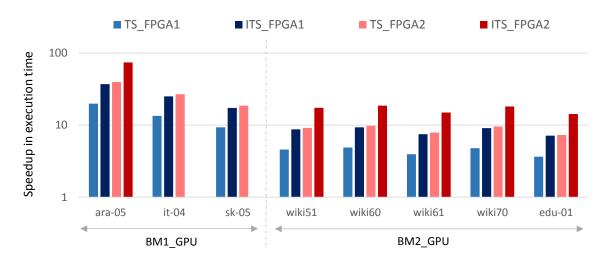

| 6.8  | Speedup of proposed ASIC over GPU benchmarks                         |

| 6.9  | Speedup of proposed FPGA implementations over GPU benchmarks 131     |

| 6.10 | Comparison of GTEPS for proposed ASIC against GPU benchmarks $132$   |

| 6.11 | Comparison of GTEPS for proposed FPGA implementations against        |

|      | GPU benchmarks for SpMV                                              |

| 6.12 | Comparison of energy per edge traversal of proposed ASIC against GPU |

|      | benchmarks                                                           |

| 6.13 | Comparison of energy per edge traversal of proposed FPGA implemen-   |

|      | tations against GPU benchmarks                                       |

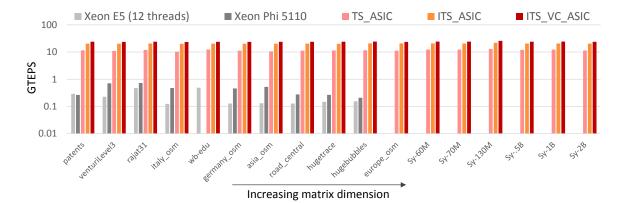

| 6.14 | Speedup of proposed ASIC and FPGA implementations over Intel Math    |

|      | Kernel Library (MKL) on dual socket Xeon E5-2620 (12 threads) CPU    |

|      | for SpMV. For MKL SpMV implementation 'mkl_scoogemv' routine is      |

|      | used                                                                 |

| 6.15 | Speedup of proposed ASIC and FPGA implementations over Intel MKL     |

|      | on Xeon Phi 5110 co-processor for SpMV. For MKL SpMV implemen-       |

|      | tation 'mkl_scoogemv' routine is used                                |

| 6.16 | Comparison of traversed edges per second in billions (GTEPS) for     |

|      | proposed ASIC against Intel MKL on dual socket Xeon E5-2620 (12 $$   |

|      | threads) CPU and Xeon Phi $5110$ co-processor for SpMV. For MKL      |

|      | SpMV implementation 'mkl_scoogemv' routine is used                   |

| 6.17 | Comparison of traversed edges per second in billions (GTEPS) for     |

|------|----------------------------------------------------------------------|

|      | proposed FPGA implementations against Intel MKL on dual socket       |

|      | Xeon E5-2620 (12 threads) CPU and Xeon Phi $5110$ co-processor for   |

|      | SpMV. For MKL SpMV implementation 'mkl_scoogemv' routine is used.137 |

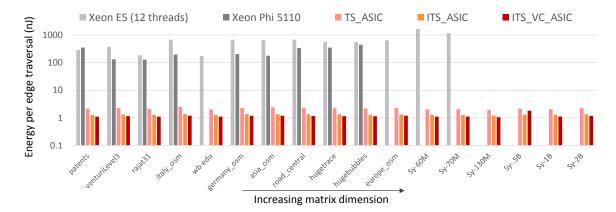

| 6.18 | Comparison of energy per edge traversal for proposed ASIC against    |

|      | Intel MKL on dual socket Xeon E5-2620 (12 threads) CPU and Xeon      |

|      | Phi 5110 co-processor for SpMV. For MKL SpMV implementation          |

|      | 'mkl_scoogemv' routine is used                                       |

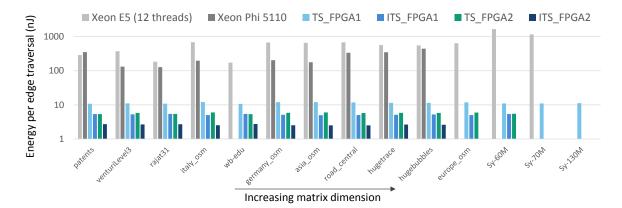

| 6.19 | Comparison of energy per edge traversal for proposed FPGA implemen-  |

|      | tations against Intel MKL on dual socket Xeon E5-2620 (12 threads)   |

|      | CPU and Xeon Phi 5110 co-processor for SpMV. For MKL SpMV            |

|      | implementation 'mkl_scoogemv' routine is used                        |

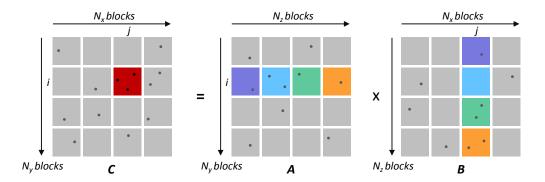

| 7.1  | SpGEMM computation using inner product (row-by-column) 142           |

| 7.2  | SpGEMM computation using Gustavson algorithm (row-by-row) 143        |

| 7.3  | 2D partitioned SpGEMM formulation and Block-level Inner Product      |

|      | (BIP) based computation                                              |

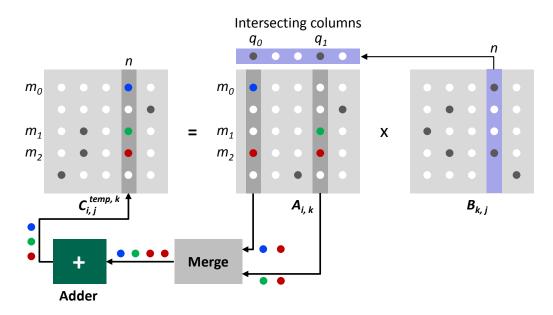

| 7.4  | Proposed SpGEMM computation method Streaming Sparse Accumula-        |

|      | tor (SSPA)                                                           |

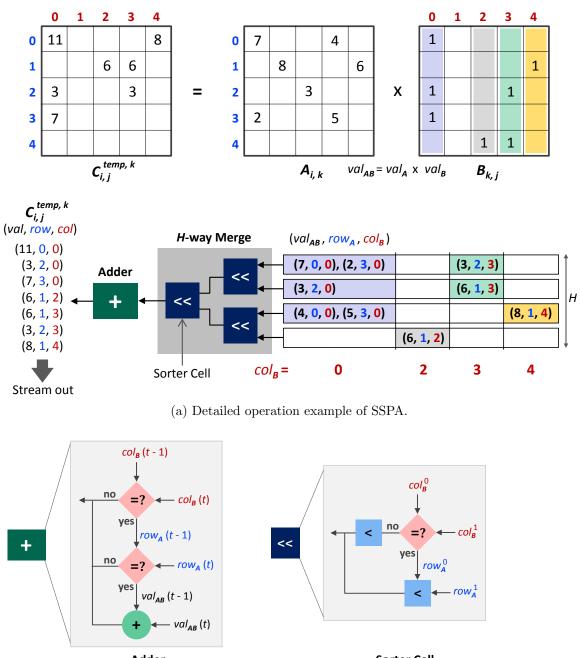

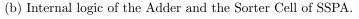

| 7.5  | SpGEMM operational details of SSPA for an example problem 152        |

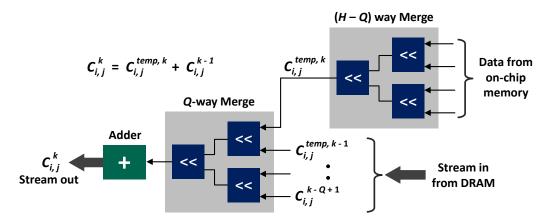

| 7.6  | Accumulation of $C_{i,j}$ across partitions                          |

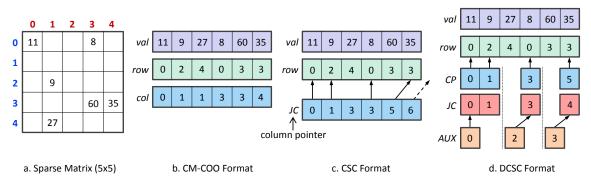

| 7.7  | CM-COO, CSC and DCSC sparse storage formats                          |

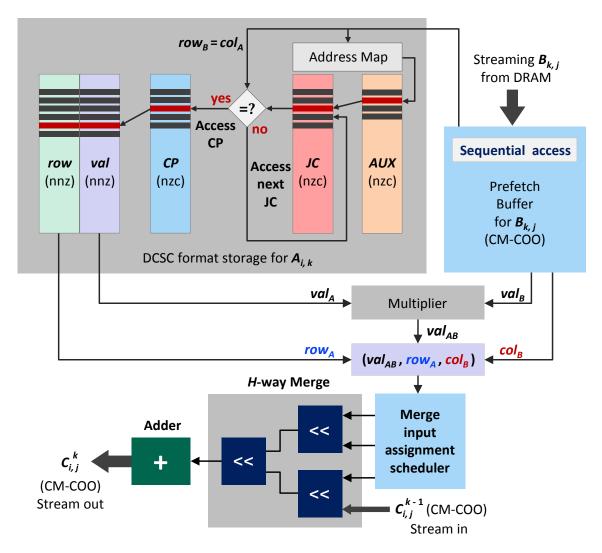

| 7.8  | SpGEMM computation elaboration using SSPA and DCSC format for        |

|      | <b>A</b> . We assume $Q = 2$ for this elaboration                    |

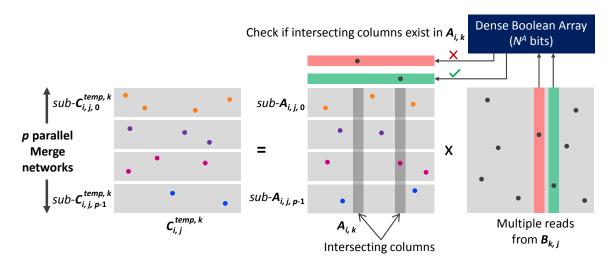

| 7.9  | Parallel SpGEMM computation using SSPA                               |

7.10 2D partitioned SpGEMM block traversal using Block-level Partial Outer Product (BPOP). We assumed  $Q = N_z$  for inter block accumulation. . . 163

| 7.11 | Off-chip traffic (normalized against $D_{\rm BIP}^{\rm RAA})$ comparison among various                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------|

|      | combinations of output block storage locations and block traversal                                                                |

|      | schemes. On-chip memory size is 8MB for all. For $D_{\mathrm{BIP}}^{\mathrm{RAA}}$ $C_{i,j}$ is stored                            |

|      | in on-chip memory. For $D_{\mathrm{BIP}}^{\mathrm{SSPA}}$ and $D_{\mathrm{BPOP}}^{\mathrm{SSPA}}$ $C_{i,j}$ is stored in off-chip |

|      | memory                                                                                                                            |

| 7.12 | Comparison of number blocks (in one direction) for 2D partitioned data                                                            |

|      | between RAA ( $C_{i,j}$ stored in on-chip memory) and SSPA ( $C_{i,j}$ stored in                                                  |

|      | off-chip memory)                                                                                                                  |

| 7.13 | Performance comparison of proposed SSPA based SpGEMM using                                                                        |

|      | BPOP against COTS and ASIC benchmarks                                                                                             |

|      |                                                                                                                                   |

- 8.1 Implementation of Two-Step algorithm in distributed memory scenario. 171

## Chapter 1

## Introduction

## 1.1 Motivation

Sparse matrix algebra has proven to be an essential tool in graph analytics of various domains, such as social networks, machine learning, bioinformatics, data mining, etc. Widespread necessity for improved performance of sparse operations has led to a proliferation of software frameworks/libraries, such as OSKI [2], GraphMat [3], SuperLU [4], GraphLab [5,6], Giraph [7], CombBLAS [8], Pregel [9], SociaLite [10], which reduces the "ninja performance gap" [11] between hand-optimized fine-tuned graph code and naively written code by researchers and developers from vastly different backgrounds. The expectation of user community is to have same level of benefits that Basic Linear Algebra Subprograms (BLAS) provided for the dense matrix algebra. However, while the high actual to peak performance ratio of dense operations on COTS platforms has been possible by BLAS like standards, it is largely due to the fact that the conceptual work horse for underlying traditional memory hierarchy of general purpose COTS platforms, i.e. temporal and spatial locality in data, is strongly

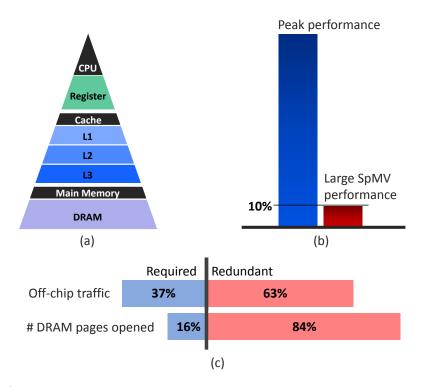

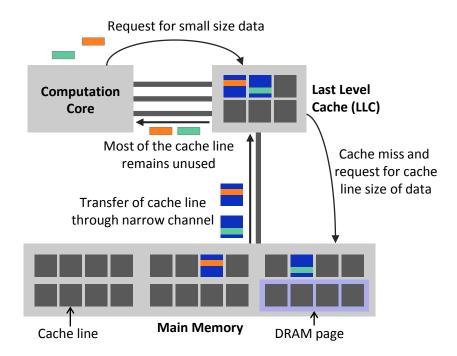

Figure 1.1: a) Traditional memory hierarchy used in general purpose architectures that is not suitable for sparse operations, b) Low peak to actual performance ratio, and c) Redundant traffic and inefficient DRAM access of SpMV on traditional architecture.

possessed by dense matrices. On the other hand, neither temporal nor spatial locality is guaranteed in sparse data. Even though locality to some extent is present in structured graphs, detection and exploitation of it often cause significant overhead, which also becomes increasingly difficult as graphs become larger and sparser. Hence, due to traditional memory hierarchy based COTS architectures not being inherently suitable for sparse operations, there is a large gap in performance between sparse matrix algebra and their dense counterpart.

**Key Problem.** The root cause of sparse matrix operation difficulties is data dependent random access to a huge address space. This translates to high latency load requests to DRAM. Moreover, general purpose architectures have limited depth of load buffer that becomes filled with parallel load requests due to high latency in serving pending loads. Therefore, high enough outstanding load requests cannot be generated to hide latency despite parallel operations. Additionally, these load requests may not always be independent. As a result, sparse kernels experience low actual to peak performance ratio and poor off-chip bandwidth usage. For example, conventional implementation of Sparse Matrix dense Vector multiplication (SpMV) yields less than 10% of the peak performance on cache based COTS architectures [12–16]. Additionally, absence of locality causes redundant off-chip traffic and inefficient DRAM access due to block level data transfer. Figure 1.1(c) shows that an example SpMV incurs 63% redundant off-chip traffic that never takes part in actual computation. Furthermore, it wastes 84% costly DRAM page openings due to this redundant traffic.

From the above metrics it is evident that current CMOS and memory technology are under-utilized for sparse operations. However, it requires an architecture where efficient synergy between compute and memory access is independent of data locality and fine grained parallelism is ensured. Such architecture is absent in current literature and warrants research effort given its potential to contribute in sparse matrix algebra.

### **1.2** Thesis Contributions

This thesis attempts to work out a computation paradigm to replace data dependent high latency random accesses for sparse operations with sequential/streaming accesses. Our work is founded on a central counterintuitive insight that is -

Minimum number of memory accesses result in higher amount of traffic and latency bound computation, whereas more memory accesses incur less overall traffic and computation can run at much faster streaming bandwidth speed.

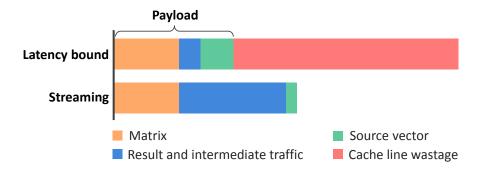

Figure 1.2: Off-chip traffic of SpMV using latency bound and full streaming algorithms.

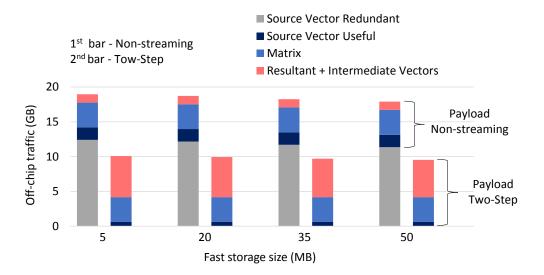

This insight is depicted in Figure 1.2 for an example SpMV operation, where the bars show total off-chip main memory traffic for latency bound and streaming algorithms. Orange, blue and green colored portions of the bars together represent payload, i.e. data that takes part in actual computation. The red portion represents the wasted data due to cache line level block transfers from DRAM. Latency bound SpMV requires least number of load requests, hence minimum payload. On the other hand, with streaming algorithm, where all random accesses are converted to sequential accesses, SpMV generates more load requests. However, full streaming algorithm performs better because of the following reasons.

- 1. Despite total payload is higher than what it is for latency bound algorithm, overall traffic is less in streaming SpMV due to elimination of excess portion of cache line transfers, which gets evicted before any use.

- 2. As modern DRAM offers significantly greater streaming bandwidth than high latency random access bandwidth, the overall reduced traffic is transferred at significantly higher speed and computation runs much faster than latency bound SpMV. This trend in DRAM is also likely to continue as memory technology

trend over past two decades has shown improvement in streaming bandwidth at a rate that is at least square of the improvement rate in latency [17].

Therefore, ideal solution for sparse operation acceleration is to eliminate latency bounded accesses and pay with streaming bandwidth and more compute. However, turning this solution into practical implementation is not trivial. While it is theoretically possible to implement full streaming algorithms on traditional COTS architectures, advantages of eliminating latency boundedness are generally offset by one of these two reasons - a) fine grained parallelism requirement introduces computational complexity and eventually renders the entire operation to become compute bound, and b) off-chip traffic overhead of COTS compatible streaming algorithm becomes prohibitively large diminishing benefits of sequential access over random access.

This works presents an algorithm/hardware co-optimized architecture that can practically eliminate all off-chip high latency random accesses while being able to harness the benefits. A major finding of this dissertation is that a scalable and high throughput multi-way merge hardware primitive is the key in building such architecture. By developing a novel set of methodologies for implementing such multi-way merge network, this work provides a common platform that is co-optimized for off-chip traffic aware streaming algorithms for fundamental sparse matrix operations. This work demonstrates implementations of these following core kernels.

1. SpMV. We primarily focus on Sparse Matrix dense Vector multiplication (SpMV) as it is a dominant and versatile component used in numerous operations, such as large-scale linear solvers, and possibly the most notorious bottleneck causing very low fractions of peak processor performance. SpMV is also a difficult kernel to accelerate due to huge dense address space of dense vectors and required random access.

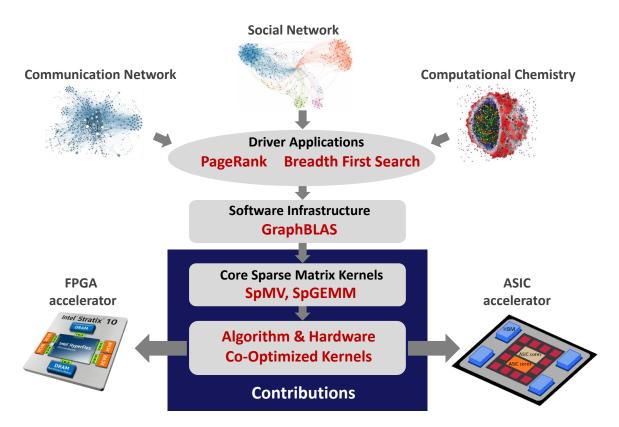

Figure 1.3: Contribution of this dissertation in graph analytics acceleration ecosystem.

This work demonstrates how our developed multi-way merge primitive can be leveraged to implement a SpMV algorithm possessing efficient data transfer characteristics, which is otherwise compute bound on COTS architectures and, hence, commonly discarded.

2. Iterative SpMV - PageRank. A large class of SpMV applications, such as PageRank, conjugate gradient, are conducted in iterative manner. This works demonstrates how iterative SpMV can be practically implemented yielding higher performance and efficiency than a single run using our proposed custom architecture. This work elaborates iterative SpMV implementation using PageRank as an example.

**3.** SpGEMM. Another class of graph analytics require sparse matrix multiplication with another sparse matrix or a set of sparse vectors, such as Betweenness

Centrality [19], All Pairs Shortest Path [20], Breath-First Search [21], which require Sparse General Matrix-Matrix multiplication (SpGEMM) as key operation. This work further demonstrates how off-chip traffic aware streaming SpGEMM can be implemented using a sparse accumulator requiring only sequential access, which is implemented using the multi-way merge hardware primitive developed in this work.

Our developed architecture is intended to contribute in the lower part of softwarehardware stack within the ecosystem provided by GraphBLAS-like standards, as shown in Figure 1.3, where wide array of applications can be mapped using few fundamental sparse kernels. This solution has shown orders of magnitude improvement in performance and efficiency over state of the art solutions, an example of which is shown in Figure 1.4. For practical demonstration, our proposed architecture has been implemented on ASIC, which is currently under fabrication in 16nm technology and shown in Figure 1.5, and FPGA custom platforms.

#### 1.2.1 Approach and Scope

In this dissertation we have taken a top-down approach, i.e architecture last, unlike most approaches in the literature that first assumes a given architecture characteristics and develop accelerator on top of it, which is a bottom-up approach. Our approach is to start with investigating the algorithmic properties that are required to yield high performance and efficiency. Later we have developed custom hardware to precisely address the requirements derived from the algorithm. Hence, this accelerator is termed as a 'co-optimized' solution. While developing these hardware primitives our priority is on scalability, technology trends and highest utilization of critical resources, such as off-chip bandwidth and on-chip storage.

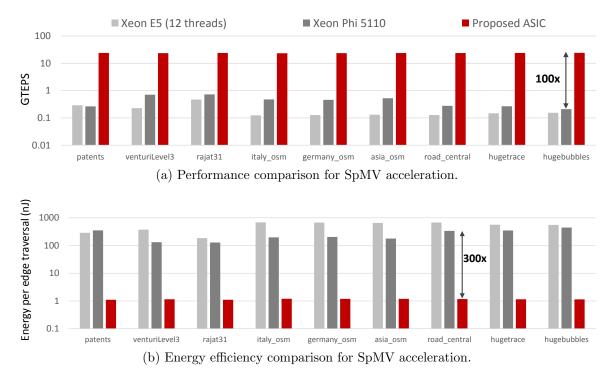

Figure 1.4: Example of performance and energy efficiency improvement of proposed ASIC architecture.

ASIC specifications Frequency: 1.4 GHz Occupied area: 7.5 mm<sup>2</sup> Leakage power: 0.10 W Dynamic power: 3.01 W Total power: 3.11 W

Figure 1.5: Custom ASIC for proposed accelerator.

We have focused on shared memory architecture in this work. It is because of the observation in memory technology trend that DRAM industry has been able to dramatically lower the cost [22] while storage capacity of single main memory sub-system has increased substantially. Main memory system with storage capability in the order of tera-bytes is common now a days, which can easily store working data set for very large (multiple billion node) graphs. Hence, shared memory architecture should be able to handle very large sparse matrix kernels if computational core can support data set of this scale.

In this work we have exclusively considered large graphs (~ billion nodes) for which working data set is too large to fit on the fast on-chip memory, such as last level cache (LLC), Block RAM (BRAM) and scratchpad. We have assumed no structure in the data pattern, i.e. data is devoid of both temporal and spatial locality. In this study our focus is on graphs with high sparsity, e.g. average degree < 10. Furthermore, we have actively avoided costly preconditioning of the input data and complicated sparse formats in an effort to eliminate related overheads.

#### **1.2.2** Effort vs Benefit

A practical concern in developing custom architecture is that often the impact is too narrow to justify the effort and cost. As there is no consensus on what the "building blocks" of graph processing should be [23], standard graph libraries provide hundreds of functions. It would be impractical to design custom hardware for all of them from the perspective of both usability and cost. However, a wide range of graph algorithms can be represented with sparse matrix algebra using just a handful of routines [24] and GraphBLAS [1] standard has been developed on this principle. GraphBLAS uses sparse matrix as the primary data structure and defines a concise set of sparse matrix routines that has been found to be useful for wide range of graph algorithms. These routines are defined on sparse matrices and, hence, work regardless of the complexity of the underlying graph. Standardization of data structure and narrow set of operations allow wide range of audience to leverage decades of developed knowledge in linear algebra. While GraphBLAS provides the programming environment for a broadest possible audience, this work facilitates the underlying implementation by a single hardware platform that accelerates the fundamental sparse matrix kernels.

Additionally, there are issues over CMOS technology trend that has made custom hardware even more relevant for data intensive operations such as large sparse matrix kernels. With slowing down of Moore's Law, i.e. doubling of transistors in every 18 months, the free ride of achieving higher performance with new generation of technology node is not true anymore. On the other hand, non-Dennard technology scaling [25] has imposed a severe constraint on power budget for the entire gamut of system design. This has led to the "Dark Silicon" phenomenon, that allows to utilize only a fraction of the transistors available on-chip. Specialized hardware can mitigate these problems and provide both performance and energy benefits.

Thus the effort in development of custom architecture for sparse matrix operation is worth the possible impact both in terms timeliness and broad range of audience.

### **1.2.3** Key Developments

The key developments of this work are as following.

1. We present a study on SpMV streaming algorithms and identify an algorithm that conducts in two separate phases and has the potential to achieve significant performance and efficiency improvement for large problems. We demonstrate that despite having superior data communication characteristics, this algorithm is abandoned in literature due to computational requirements, which is not well suited for general purpose processors. This work elaborates on how the proposed SpMV algorithm can be exploited by invoking various architecture and circuit level techniques enabled by custom hardware.

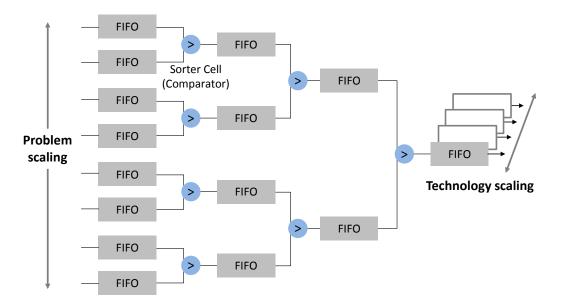

- 2. This work makes a finding that a scalable and high throughput multi-way merge network is a fundamental hardware primitive for both SpMV and SpGEMM operations. However, multi-way merge hardware scheme with these required properties is not available in current literature. We present a thorough investigation on the improvement of multi-way merge operation both at hardware implementation and algorithmic level. This work demonstrates novel circuit level techniques and parallelization scheme particularly suitable for sparse matrix operations that achieve scalability and high performance. As multi-way merge is a core operation in various other applications, our developed multi-way merge merge network scheme can have broader impact.

- 3. As off-chip communication directly affects performance and efficiency of sparse kernels, this work emphasizes on developing various techniques that reduce offchip data transfers for both SpMV and SpGEMM. We demonstrate effective meta-data compression scheme that significantly reduces main memory traffic. Furthermore, we present a new block traversal scheme for 2D partitioned data for SpGEMM that becomes increasingly more beneficial in terms of main memory traffic as matrix becomes larger and sparser.

- 4. This thesis demonstrates practical methodologies in properly utilizing extreme off-chip bandwidth for sparse operations that is offered by state of the art 3D stacked main memory technology. Keeping various computational constraints

and limited power budget in mind, this work makes a comprehensive effort in optimizing traffic and achieving high sustained throughput.

- 5. We show methods to enhance performance for a number of common cases in sparse kernel applications. One of these cases is SpMV operation for iterative applications, such as PageRank. We demonstrate a technique that reduces off-chip traffic and almost doubles the computation throughput of iterative SpMV. Another case is when the input graph contains nodes with disproportionately large number of neighbors that are commonly found in power-law graphs. This work shows that by detecting these nodes and processing them using specially designed pipeline provide additional benefits. This work makes active effort in ensuring that these optimization techniques do not cause considerable overhead in terms of either hardware resource or data structure.

- 6. In this work we thoroughly demonstrate a streaming sparse accumulator as the computation engine for efficient SpGEMM, which uses the same hardware primarily designed for SpMV. We show that streaming sparse accumulator eliminates the requirements of complex data structure and expensive hardwares that are otherwise required for sparse accumulation. Furthermore, we demonstrate that streaming sparse accumulator enables off-chip traffic reduction opportunities.

- 7. A key contribution of this work is to demonstrate scalable acceleration methodologies that can handle large problems. One of the major constraints of state of the art sparse kernel accelerators is strong dependence on the on-chip fast memory to scale. This work presents computation methodologies that are resource aware and can handle significantly larger matrices (~ billion nodes vs few million

nodes) with considerably less on-chip memory relative to custom accelerators in literature.

8. The proposed custom hardware solution in this work is suitable for implementation in both ASIC and FPGA platforms. We have fabricated a 16nm FinFET based ASIC chip as a practical demonstration of our proposed accelerator. We further ported the ASIC design to Intel<sup>®</sup> Stratix<sup>®</sup> 10 FPGA. Our proposed accelerator in both ASIC and FPGA platforms demonstrates multiple orders of magnitude improvement over general purpose architectures in terms of both performance and energy efficiency. Comparison results with recent custom accelerators also demonstrate significant improvement in these metrics and considerably higher scalability.

## 1.3 Background

Matrix algebra has been a part of graph analytics since its inception due to the duality between canonical representation of graphs as a set of edges and vertices and a matrix [1]. However, it is until recently that sparse matrix operations based on already existing mature knowledge-base of linear algebra are found highly productive by graph analytics community [24, 26]. This renewed interest in sparse matrix algebra, substantially triggered by the success of Google PageRank algorithm [27], is attributed to recent advancements in sparse matrix data structures and algorithms along with numerous high-impact applications.

We will discuss the general difficulties related to sparse matrix operations next. Later in this section, we will also discuss relevant research efforts in literature for accelerating these operations

#### **1.3.1** Sparse Matrix Kernel Acceleration Challenges

Fundamental challenges in achieving scalability, performance and efficiency for sparse matrix primitives in general are detailed below.

Low FLOP to memory access ratio. Fundamental sparse matrix kernels, such as SpMV and SpGEMM, are data intensive and have low flop to memory access ratio in general. This means for few computations it requires a relatively large quantity of data transfers. In modern architectures, data access is much more expensive than compute in terms of both energy and performance. For example, a double precision FP operation requires 0.5-50pJ, while reading the operands from cache memory at 20mm distance consumes 500pJ. Energy consumption is ever higher (6000pJ) if data is randomly accessed from off-chip main memory [28–31]. In terms of performance, modern microprocessors require around 200 cycles to randomly access main memory whereas FP multiplier takes only four cycles [32].

Inefficient Computation. Sparsity implies meta-data, huge address space and complicated load-store, which cause inefficiency in general purpose computing. As found by the authors of [33], among all the instructions of sparse matrix operation more than 94% are responsible for traversing the graph, e.g. finding relevant neighbors of a node, and loading arguments for computation. This also incurs a high energy overhead. While an arithmetic operation requires 0.5-50pJ, scheduling instructions in modern core consumes 2000pJ [29,34].

**Poor Bandwidth Usage.** Off-chip memory bandwidth is one of the most important resources of modern systems and sparse operations on general purpose processors generally render bandwidth utilization to be poor. For latency bound sparse operations data is transferred from off-chip memory in large blocks, most of which remain unused. On the other hand, off-chip bandwidth bound sparse kernels often cause repetitive transfers of same traffic as the working data set is too large for on-chip memory. This incurs redundant traffic and negatively affects both performance and energy efficiency.

**On-chip Memory Dependency for Scaling.** This is possibly the most important constraint in handling large graphs for both general purpose and custom architectures. Data structure of sparse matrix requires additional vectors as meta-data and random accesses to these are required for fast traversal. Hence, it is a common technique for custom accelerators to store large portion of meta-data, such as vertex and edge properties, in the fast on-chip random access memory. This severely limits scaling capability as larger problem requires larger on-chip memory. Modern SOCs and micro-processors already use around 90% of available silicon area for on-chip memory [35]. With Moore's law currently hitting physical limits, radical increase in on-chip memory capacity is not likely in foreseeable future. Hence, state of the art shared memory custom accelerators have reported to only handle graphs with few million nodes [16,33,36], whereas multi-billion node graphs are now commonplace.

#### **1.3.2** Related Work in Literature

Majority of the research efforts to improve sparse matrix operations has been dedicated in the software paradigm targeted for general purpose architectures. A commonality among many of these efforts is the focus in trying to extract and exploit temporal/spatial locality and execute by fine grained parallelism. Using sophisticated sparse formats to capture and to provide ease of access to neighboring data is one approach in exploiting locality. Another approach is to preprocess or precondition the matrix to induce locality using techniques such as register blocking and matrix reordering, which are expensive operations in general.

#### General Purpose Architecture

Authors of [37] have proposed to use blocked column-major and blocked row-major Compressed Sparse Row (CSR) formats, namely BCM-CSR and BRM-CSR. These formats improve SpMV performance of structured sparse matrices as long as the data set fits in LLC. However, the authors reported sharp decline in performance when the data set becomes larger than LLC. Authors of [13] used register, cache and TLB level blocking to accelerate SpMV for multi-core environments. Recently, GPUs got much attention of researchers where they have explored many sophisticated approaches, such as fine grained parallel decomposition [38], model based auto-tuning [39] and transformation of matrix representation and tiling to increase temporal locality [40]. In [40], authors have utilized column re-ordering according to column length to accelerate SpMV based PageRank application on GPU. Researchers of [39] have proposed to blocked ELLPACK format for GPUs. In Blocked ELLPACK nonzeros are stored in blocks and ELL format is used to index the blocks, which introduces high memory overhead. Authors of [41] also proposed several complicated data formats, such as hybrid ELL/COO and packet (PKT) format, for SpMV on GPU. One-warp-one-row (1W1R) method is used in [41] where it was reported to improve performance by reducing the divergence among rows. In an IBM technical report [42], the authors have shown how compile-time and run-time optimizations on GPU can

accelerate SpMV. In [43], SpMV has been implemented using one-thread-one-row (1T1R) method on GPU. However, this method suffers from the variable length of the rows, i.e. different number of nonzeros per row. The authors have explored scan-based method to overcome the inefficiency of this work. Cell processors have been used to accelerate SpGEMM and SpMV in [44] by SIMD style implementation on eight synergistic processing elements (SPEs). Even though SPEs have neither caches nor efficient word-granularity gather/scatter support, the authors reported that the task parallelism afforded by the SPEs, the eight independent load store units, and the ability to stream nonzeros via direct memory access units overcame the limitations. This work uses blocked compressed sparse row (BCSR) format and register blocking to exploit locality.

#### Custom Architecture - FPGA

Among custom hardware platforms, FPGAs are more popularly pursued due to more accessibility and cost effectiveness. For example, researchers of the works [45–48] have implemented custom SpMV acceleration hardware using FPGAs. The maximum reported performance improvement in [45] is 29x over CPU. While graph dimension of most FPGA implementations in literature are limited to fractions of a million nodes due to full vector storage requirement in on-chip Static Random Access Memory (SRAM), authors of [45] reported to handle 9M node graph by using multiple off-chip SRAM blocks. FPGA accelerator in [36] takes an edge centric graph processing approach for PageRank acceleration, which can be implemented using SpMV, where the authors reported maximum 2.3M node graph using 8.4MB SRAM. The work in [48] and [47] report maximum performance of 1.4giga floating point operations per second (GFLOPS) and 4GFLOPS accordingly. These performances are very much comparable to those for GPUs. GraphOps, a FPGA based modular hardware library for accelerating graph analytics presented in [49], focuses on optimizing graph layout for efficient layout in off-chip main memory and reported to operate on 16M node graph for SpMV and PageRank. However, the authors reported a poor throughput of 37 Million Edges Per Second (MEPS) and only 16% off-chip bandwidth utilization. In general, FPGAs are reported to have better efficiency than general purpose architecture, however, considerable performance improvement with FPGA for large scale SpMV is absent in the literature.

#### Custom Architecture - ASIC

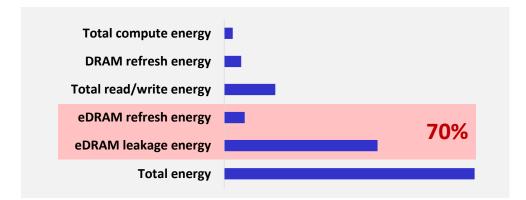

A handful of ASIC accelerators are available in literature for sparse kernel acceleration, such as [16,18,33,50]. Authors of [16] has implemented SpMV and Sparse Matrix Sparse Vector multiplication (SpMSpV) kernels on 14nm simulated ASIC for accelerating machine learning workloads, such as classification, regression, recommendation and clustering. This work reported highest graph of 1.6M nodes, 117x improvement in performance per watt against multi-threaded software implementation on CPU and 60GB/s aggregated throughput using 4 independent accelerator blocks. Authors of [18] accelerated SpMV operation for support vectors machine (SVM) using an 14nm simulated ASIC similar to [16]. This work reported 14.7x and 22.9x performance improvement against baseline SpMV software running on Intel<sup>®</sup> Atom and Xeon core respectively. Energy efficiency improvement against Atom and Xeon core is 9x and 20x respectively. The authors of [33] presented another ASIC simulated using sub-28nm technology node for graph analytics. This work reported to achieve 1.7x-6.5x speedup and 50x-100x energy efficiency in comparison with software graph analytics frame work on 16-core Haswell Xeon CPU for applications such as PageRank, breadth-first search (BFS), single source shortest path (SSSP) and collaborative filtering (CF). This work uses a large 32MB Embedded DRAM (eDRAM) scratchpad that is also very energy inefficient. The authors reported the eDRAM energy consumption to be 90% of what is consumed by the entire system. Despite using a large scratchpad, this work efficiently supports only 8M node graph. It is because this accelerator stores multiple tables related to all vertex and edge properties in the scratchpad for fast random access. The work in [50] presents a simulated 32nm ASIC along with 3D stacked architecture for SpGEMM acceleration. This work uses multiple Content Addressable Memory (CAM) blocks for random sparse accumulation during blocked SpGEMM computation. However, CAM is very expensive in terms of both silicon space and power. Furthermore, resultant output matrix of this work is not sorted.

## **1.4** Dissertation Outline

In this dissertation we will initially present the discussion of off-chip traffic aware algorithm and custom architecture development for SpMV kernel. In the later part of this thesis we will demonstrate how the developed architecture enables traffic aware algorithm implementation for SpGEMM, which can also be construed as sparse matrix multiplication with a set of sparse vectors, i.e. SpMSpV. The chapters of this dissertation are organized as following.

Chapter 2 will provide a study on streaming and non-streaming SpMV algorithms. We will elaborate our proposed off-chip traffic aware two phased algorithm, namely Two-Step SpMV, which can efficiently eliminate high latency accesses for SpMV. We will also present the comparative benefits and challenges related to Two-Step SpMV and demonstrate why a scalable multi-way merge hardware is essential for SpMV. Chapter 3 will thoroughly demonstrate the development of scalable multi-way merge hardware which is essential for sparse matrix operation acceleration. We will drive the discussion using SpMV kernel as it poses more difficulties in achieving performance. This chapter will elaborate circuit level details and techniques that have been devised to improve performance and scalability of multi-way merge tree. Furthermore, a parallelization method will be illustrated that does not require more on-chip memory to scale. We will explain how this parallelization method dictates the partitioning scheme of the matrix. This chapter also progressively discusses available multi-way merge implementation techniques in literature and why those are not suitable for sparse matrix kernel acceleration.

Chapter 4 will detail the implementation of Two-Step SpMV kernel on custom hardware. We will present accumulation techniques to avoid bubbles in pipelined adders in case of large number of consecutive collisions. Furthermore, this chapter will demonstrate our proposed meta-data compression scheme and special hardware to efficiently process high degree nodes in power-law graphs. We will also show efficient technique for this accelerator implementation where the main memory sub-system has multiple channels.

Chapter 5 will present an optimization technique by iteration overlap for iterative SpMV operation using an example of PageRank application. We will demonstrate how throughput is increased and traffic is reduced by iteration overlap optimization. The second half of this chapter will elaborate on-chip fast memory usage of our accelerator and the effects of memory management on custom hardware solutions' scalability and efficiency. This discussion will show how our proposed architecture is capable of handling significantly larger graphs than what is possible with present architectures despite using less or similar fast memory. Chapter 6 will present experimental results for SpMV kernel with our proposed accelerator implemented on both ASIC and FPGA platforms. We will show comparison against multiple general purpose architectures as benchmarks, which are CPU, coprocessor (Xeon Phi) and GPU. Furthermore, we will compare against other custom hardware solutions available in literature. We will use Intel<sup>®</sup> MKL for implementation on CPU and co-processor. For the rest of benchmarks, we will use the reported metrics from relevant publications. As performance metrics we will use speedup in execution time and GTEPS. As energy efficiency metric, we will use energy per edge traversal.

Chapter 7 will describe how the developed accelerator can be used for SpGEMM operation. We will demonstrate how an efficient streaming sparse accumulator can be implemented using the multi-way merge network primarily developed for Two-Step SpMV implementation. We will further discuss the advantage of streaming sparse accumulator over current SpGEMM acceleration techniques using both custom and general purpose hardware. Additionally, we will present a new block traversal scheme for 2D partitioned matrix that significantly reduces off-chip traffic for SpGEMM computation. Lastly, we will present experimental results and compare with general purpose and custom hardware benchmarks in terms of performance and energy efficiency.

Chapter 8 will discuss possible directions of future work and present concluding remarks.

# Chapter 2

# Two-Step SpMV Algorithm

## Contents

| 2.1 | $\mathbf{SpM}$ | IV Operation on Large Matrices 2                     | 3  |

|-----|----------------|------------------------------------------------------|----|

| 2.2 | Prop           | posed Two-Step SpMV                                  | :5 |

|     | 2.2.1          | Advantages of Two-Step SpMV                          | 28 |

| 2.3 | Eval           | uation of Two-Step SpMV 2                            | 9  |

|     | 2.3.1          | Non-Streaming SpMV                                   | 29 |

|     | 2.3.2          | Streaming SpMV                                       | 31 |

| 2.4 | Cha            | llenges                                              | 8  |

|     | 2.4.1          | Multi-way Merge for Two-Step SpMV                    | 38 |

|     | 2.4.2          | Multi-way Merge for other Sparse Matrix Operations 3 | 39 |

| 2.5 | Sum            | mary                                                 | 0  |

In this chapter, streaming algorithms for Sparse Matrix dense Vector multiplication (SpMV) operation on shared memory system are explored. We will elaborate our proposed streaming algorithm, namely Two-Step SpMV, that enables full main memory streaming by efficiently eliminating high latency accesses and reduces off-chip traffic for large problems. This algorithm also serves as an exemplary rationale behind the

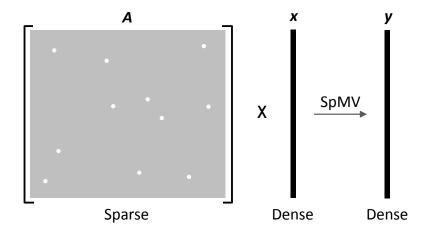

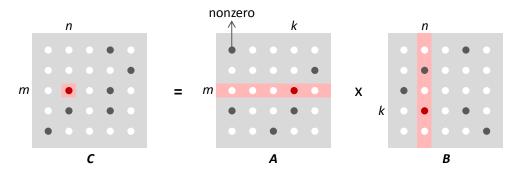

Figure 2.1: Sparse Matrix dense Vector multiplication (SpMV) operation.

development of scalable multi-way merge as a core hardware primitive for our proposed architecture in this work.

This chapter will also demonstrate comparative analysis of Two-Step algorithm against other bandwidth bound and latency bound algorithms. For evaluation and demonstration, we assume the Disk Access Machine (DAM) model [51] with two levels of memory hierarchy, on-chip storage (fast access) and off-chip main memory (slow access with block transfer). In this work we have focused on sparse matrices that are significantly larger than system's fast on-chip storage, e.g. last level cache (LLC), scratchpad, etc. Furthermore, we assume matrices with high sparsity where exploitation of temporal/spatial locality or any structure in the nonzero pattern is difficult.

# 2.1 SpMV Operation on Large Matrices

SpMV operation can be represented as y = Ax + y, where A is a sparse matrix and xand y are respectively the source and resultant vectors as shown in Figure 2.1. SpMV operation has low floating point operation (FLOP) to memory access ratio, i.e. for few computations we require a relatively large number of memory accesses. This is because for only two floating point operations, i.e. the multiplication and addition, three memory accesses to A, x and y are required. Given current technologies, our compute capability significantly exceeds memory access speed, which is termed as memory-wall [52,53]. Hence, resource requirement for SpMV operation is intrinsically imbalanced with respect to available system resources.

More importantly, SpMV requires random access to a large address space corresponding to either source vector  $\mathbf{x}$  or reslutsnat vector  $\mathbf{y}$ . When SpMV problem set become significantly bigger than fast memory, which is true for numerous real world problems, these random accesses are translated to high latency main-memory random accesses. As will be explained in detail later, random access to main memory makes SpMV latency bound for large problems that is substantially inefficient for both performance and energy. Matrix partitioning can help in overcoming this, however, at the cost of increased computational complexity and payload (data that actually takes part in computation).

Due to sequential main memory access, streaming SpMV algorithms are generally main memory bandwidth bound. Since off-chip main memory bandwidth is one of the most scarce resources of current architectures, performance and energy efficiency of SpMV operation critically depend on proper usage of it. Proper usage of off-chip memory bandwidth implies full streaming access and minimization of off-chip traffic. In this work, we propose a streaming SpMV algorithm that guarantees streaming main memory access and incurs relatively less off-chip traffic. This algorithm is named as Two-Step SpMV. We remain oblivious to computation related micro-architectural constraints in developing Two-Step SpMV and exclusively focus on data transfer characteristics.

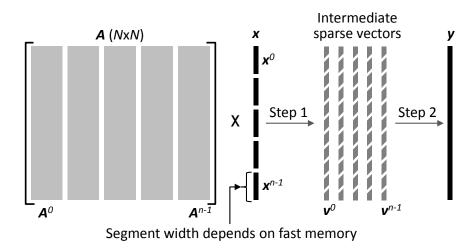

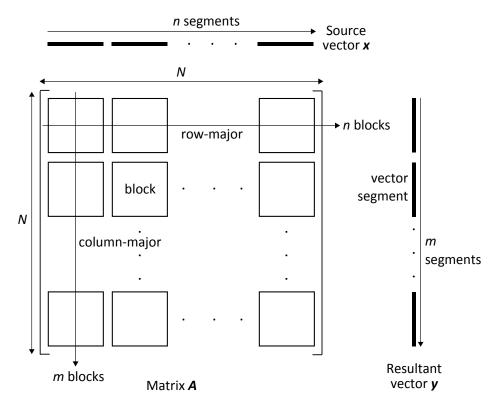

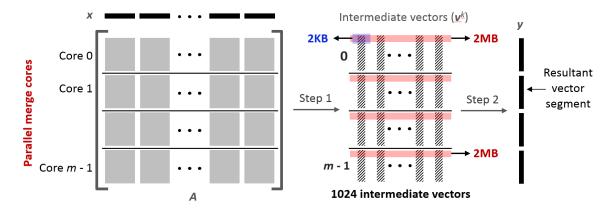

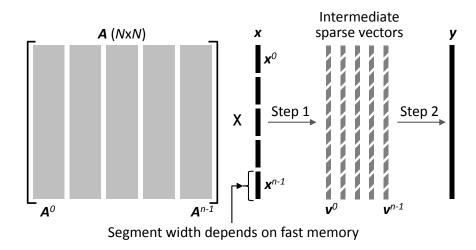

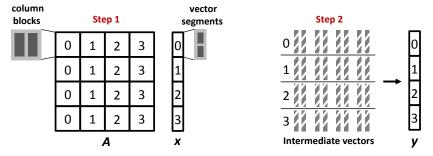

Figure 2.2: Two-Step SpMV algorithm.

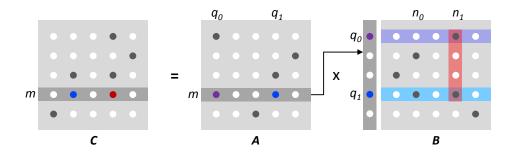

# 2.2 Proposed Two-Step SpMV

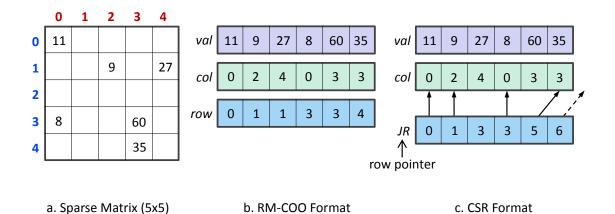

As the name suggests, Two-Step SpMV is conducted in two separate steps, which is depicted in Figure 4.1. This algorithm is fundamentally depended on matrix partitioning into 1D column-blocks and multi-way merge operation. For Two-Step SpMV, initially the source vector  $\mathbf{x}$  is first divided into multiple segments and matrix  $\mathbf{A}$  is partitioned into vertical stripes, i.e. column blocks, as shown in Figure 4.1. The stripes of  $\mathbf{A}$  is stored in a row major sparse format, e.g. Row Major Coordinate (RM-COO) or CSR as are depicted in Figure 2.3. Depending on the sparsity of matrix stripes one row-major format might be preferable to other. A detail discussion on preferable sparse formats is given in Chapter 4. Dimensional width of the stripes of  $\mathbf{A}$ is same as the source vector segment length, which is directly proportional to the fast storage that can be randomly accessed in constant time. This means, segment width of  $\mathbf{x}$  is determined such that fast memory storage is capable of holding the entirety of it.

Figure 2.3: Row major sparse formats.

A pseudocode of Two-Step SpMV algorithm is given in Pseudocode 1. We discuss the separate steps of Two-Step SpMV below. At the beginning of SpMV operation, we assume that matrix stripes and source vector segments are resided in main memory.

#### Step 1

In this step of Two-Step algorithm, partial SpMV is conducted between the stripes of matrix  $(\mathbf{A}^k)$  and the corresponding vector segments  $(\mathbf{x}^k)$ . At first, one vector segment is streamed out from main memory and stored in the fast storage. Afterwards, pertinent matrix stripe is streamed out from main memory to the computation core. Each nonzero in the matrix stripe is multiplied with the corresponding source vector element and accumulated with any existing partial results within the same matrix stripe of  $\mathbf{A}$ . As the matrix blocks are is stored in row major format, they are also sequentially traversed in increasing order of row indices of the nonzeros. Hence this partial SpMV operation on sparse matrix block produces a sparse vector that have nonzero elements sorted in ascending row indices of the matrix nonzeros, which are the

**Pseudocode 1:** Two-Step algorithm for large SpMV.

```

1 STEP 1

2 for k = 0 to n - 1 do

Stream in Matrix Column Block A^k

3

u ← 0

4

for All rows A_{i,:}^k with nnz > 0 do

\mathbf{5}

for Each non-zero A_{i,j}^k in A_{i,i}^k do

6

Random access to vector segment \boldsymbol{x}^k

7

u_i \leftarrow A_{i\,i}^k \cdot x_i^k + u_i

8

end

9

end

\mathbf{10}

Sparsify u to v^k

11

Stream out \boldsymbol{v}^k

12

13 end

14 STEP 2

for i = 0 to N - 1 do

15

for k = 0 to n - 1 do

16

Stream in \boldsymbol{v}^k

\mathbf{17}

y_i \leftarrow y_i + v_i^k [Multiway Merge]

18

end

19

20 end

21 Stream out y

```

meta-data (index) for the sparse vector nonzero elements. Thus, each sparse vector is effectively a sorted list and each nonzero in the sparse vector is a key-value pair where the key is the position index, i.e. the meta-data.

Since during the partial SpMV of  $A^k$  and  $x^k$  the intermediate sparse vector  $v^k$  is generated sequentially, it can be streamed out to main memory. In the first step, this process is conducted for all n matrix stripes. Therefore, after step 1 we end up with nintermediate sparse vectors residing in main memory. These intermediate vectors are stored in main memory as they are too large to fit in the fast on-chip storage.

#### Step 2

The second step of Two-Step SpMV is essentially a large multi-way merge operation among all the sorted lists, i.e. n intermediate sparse vectors. For this multi-way merge operation,  $\mathbf{v}^k$  for any value of k is accessed sequentially. Hence, in step 2 all the intermediate vectors are streamed out from main memory to the computational core and merged to form the final resultant dense vector  $\mathbf{y}$ . As  $\mathbf{y}$  is also generated in sequential manner, it can streamed to main memory.

## 2.2.1 Advantages of Two-Step SpMV

The main advantage of Two-Step SpMV is that it guarantees full main memory streaming access and incurs less off-chip traffic than other streaming and non-streaming algorithms for large problems. Therefore, Two-Step SpMV facilitate proper use of main memory bandwidth. We will elaborate on why this algorithm causes less traffic in later part of this chapter. Additionally, Two-Step enables various optimization opportunities such as meta-data compression for off-chip traffic reduction and throughput augmentation in iterative applications, which will be discussed in detail in Chapter 4 and Chapter 5. Furthermore, Two-Step SpMV does not require preconditioning (preprocessing) of the matrix and is not dependent on any exploitation of nonzero locality pattern. Hence, for large problems with high sparsity that are devoid of spatial and temporal locality or when preconditioning is expensive, Two-Step algorithm is especially advantageous.

In the following sections, we will evaluate Two-Step SpMV with other non-streaming and streaming SpMV algorithms and demonstrate the benefits of this algorithm in terms of off-chip data transfer characteristics.

# 2.3 Evaluation of Two-Step SpMV