# Novel Topologies for Highly-Scalable Non-Volatile NEMS Relays

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

**Electrical and Computer Engineering**

James T. Best

B.S. Engineering, Harvey Mudd College (2014)

Carnegie Mellon University Pittsburgh, PA

December, 2019

© James T. Best, 2019

All Rights Reserved

#### Acknowledgements

I would like to thank my advisor, Professor Gianluca Piazza, for his continual support throughout my Ph.D. He has helped me grow both academically and personally as he guided me through the various challenges that come during a Ph.D. I would also like to thank Jim Bain, Larry Pileggi, and Maarten De Boer for being on my defense committee. Their suggestions and guidance have been invaluable in developing and presenting my work.

I would like to thank the National Science Foundation DMREF project (award# DMREF-1334572) and the Kavcic-Moura Endowment Fund for supporting my research projects on the Pulse Activated Piezo Switch and the Phase Change NEMS Relay, respectively. I am thankful for the support of the Carnegie Mellon University Claire and John Bertucci Nanotechnology Laboratory staff members, Matt Moneck, Norm Gottron, Mason Risley, Mark Weiler, James Rosvanis, and Dante Boni for their knowledge, support, and help with fabrication.

I would like to thank the past and present members the Piazza lab as well as other nanofabrication colleagues. I would especially like to thank Ayaz who has been working with me on the Phase Change NEMS Relay project since starting his Ph.D.

I would like to thank my friends who have always provided entertainment and support throughout my Ph.D. program. I would especially like to thank my life-long friend, Eugene, who has offered support and competition since I was 7 years old. I would also like to thank my girlfriend, Catherine, whose love and support have been instrumental to completing my Ph.D.

I would like to thank Rick Dill, who encouraged me to do a Ph.D. at the Carnegie Mellon Electrical and Computer Engineering department. His guidance was a key factor in deciding to continue my education and work towards a Ph.D.

iii

Finally, I would like to thank my parents, John and Maggie, who have always encouraged me to continue my education and never stop pushing my boundaries. Additionally, their support for my passion of engineering, ranging from mentoring FIRST robotics to even installing machine tools in the garage, has been key to my success. I wouldn't have been able to finish my Ph.D. without their support.

#### Abstract

Complementary metal oxide semiconductors (CMOS) are nearing the limits for supply voltage and energy efficiency, motivating the search for alternative technologies. Emerging technologies like resistive memory (ReRAM), magnetoresistive memory (MRAM), phase change memory (PCRAM), and ferroelectric memory (FeRAM) offer scalable alternatives to CMOS, but are limited in either reliability, threshold voltage, or power consumption. Microelectromechanical system (MEMS) relays have gained interest as an energy efficient alternative to solid-state technologies due to the low leakage, abrupt switching, and high on/off ratios associated with mechanical contacts. A wide range of actuation methods are used in MEMS relays including electrostatic attraction, piezoelectric expansion, and thermal expansion. Common to these actuation methods is the use of a flexure to provide constraint or restoring force to overcome contact adhesion. These flexures prevent MEMS relays from scaling to dimensions comparable to CMOS devices.

This dissertation focuses on the development of the Phase Change NEMS Relay (PCNR), a novel non-volatile mechanical relay that eliminates the use of flexures and addresses the limited scalability of traditional MEMS relays. Phase change materials like GeTe can support crystalline and amorphous states at room temperature, which differ in material properties. Converting GeTe from the crystalline to amorphous state requires melting and quenching the GeTe. The PCNR is the first device to exploit the large 10 % volume change between the crystalline and amorphous states of GeTe in an actuator for mechanical displacement.

The PCNR is fabricated and tested with heater dimensions as small as 1  $\mu$ m wide by 3  $\mu$ m long and an air-gap of 20 nm. Actuator expansion is measured to be 26 nm, and switching is demonstrated with on and off times of 300 ns and 600 ns, respectively. On state resistance is measured to be 260  $\Omega$  and nonvolatility is demonstrated for over 24 hours. Off state leakage is measured as low as 10<sup>-14</sup> A. Scaling

v

analysis shows a path towards CMOS comparable device sizes (5 nm wide by 20 nm long heater) as well as lower than CMOS actuation voltage (0.52 V). Actuation energy is predicted to be as low as 1.8 pJ with a 1.8 ns actuation time.

### Table of Contents

| Acknowledgementsiii           |                       |              |                       |                                                    |    |  |  |  |  |

|-------------------------------|-----------------------|--------------|-----------------------|----------------------------------------------------|----|--|--|--|--|

| A                             | Abstractv             |              |                       |                                                    |    |  |  |  |  |

| Та                            | Table of Contents vii |              |                       |                                                    |    |  |  |  |  |

| Li                            | List of Tablesix      |              |                       |                                                    |    |  |  |  |  |

| Li                            | st of                 | Fig          | ures                  |                                                    | x  |  |  |  |  |

| 1                             | Ir                    | Introduction |                       |                                                    | 1  |  |  |  |  |

| 1.1 Emerging Technologies     |                       |              |                       | 2                                                  |    |  |  |  |  |

| 1.2 Background on MEMS Relays |                       |              | ground on MEMS Relays | 6                                                  |    |  |  |  |  |

|                               | 1                     | .2.1         |                       | Current State of MEMS Relays                       | 7  |  |  |  |  |

|                               | 1                     | 1.2.2        |                       | Scaling of Flexure Based MEMS Relays               | 12 |  |  |  |  |

|                               | 1                     | .2.3         |                       | Non-Flexure Based MEMS Relays                      | 18 |  |  |  |  |

|                               | 1.3                   |              | Pulse                 | e Activated Piezo Shuttle Relay (PAPS)             | 19 |  |  |  |  |

|                               | 1.4                   |              | Thes                  | sis Outline                                        | 23 |  |  |  |  |

| 2                             | Р                     | has          | e Cha                 | ange NEMS Relay (PCNR) Concept Design and Modeling | 24 |  |  |  |  |

|                               | 2.1                   |              | Abst                  | ract                                               | 24 |  |  |  |  |

|                               | 2.2                   |              | Opei                  | rating Concept                                     | 25 |  |  |  |  |

|                               | 2.3                   |              | Phas                  | e Change Materials                                 | 27 |  |  |  |  |

|                               | 2.4                   |              | Devi                  | ce Modeling                                        | 29 |  |  |  |  |

|                               | 2                     | 2.4.1        |                       | Electrical Modeling                                | 29 |  |  |  |  |

|                               | 2                     | 2.4.2        |                       | Thermal Modeling                                   | 32 |  |  |  |  |

|                               | 2                     | 2.4.3        |                       | Mechanical Modeling                                | 35 |  |  |  |  |

|                               | 2.5                   |              | Scali                 | ng Analysis                                        | 39 |  |  |  |  |

|                               | 2.6                   |              | Sum                   | mary                                               | 53 |  |  |  |  |

| 3                             | Ρ                     | CNF          | R Fab                 | prication                                          | 53 |  |  |  |  |

|                               | 3.1                   |              | Abst                  | ract                                               | 53 |  |  |  |  |

|                               | 3.2                   |              | Fabr                  | ication flow                                       | 54 |  |  |  |  |

|                               | 3.3                   |              | GeTe                  | e Processing                                       | 56 |  |  |  |  |

|                               | 3                     | .3.1         |                       | GeTe Composition                                   | 56 |  |  |  |  |

|                               | 3.3.2                 |              |                       | GeTe Seed Layer                                    | 58 |  |  |  |  |

|                               | 3                     | 3.3.3        |                       | Amorphous and Crystalline GeTe                     | 60 |  |  |  |  |

|                               | 3                     | 3.3.4        |                       | Etching GeTe                                       | 61 |  |  |  |  |

|             | 3.4               | Сар    | Layer                                               | 62  |  |  |  |

|-------------|-------------------|--------|-----------------------------------------------------|-----|--|--|--|

|             | 3.5               | Drai   | in and Source                                       | 64  |  |  |  |

|             | 3.6               | Rele   | ease                                                | 67  |  |  |  |

|             | 3.7               | Sum    | imary                                               | 68  |  |  |  |

| 4           | PCN               | R Act  | tuator Testing                                      | 69  |  |  |  |

|             | 4.1               | Abst   | tract                                               | 69  |  |  |  |

|             | 4.2               | Opti   | ical Characterization of Phase Change Actuation     | 69  |  |  |  |

|             | 4.3               | Pha    | se Change Material Reflow                           | 75  |  |  |  |

|             | 4.4               | Expa   | ansion Characterization via Atomic Force Microscopy | 76  |  |  |  |

|             | 4.5               | Sum    | nmary                                               | 82  |  |  |  |

| 5           | PCN               | R Re   | lay Testing                                         | 83  |  |  |  |

|             | 5.1               | Abst   | tract                                               | 83  |  |  |  |

|             | 5.2               | Swit   | tching Time                                         | 84  |  |  |  |

|             | 5.2.3             | 1      | Test Setup                                          | 84  |  |  |  |

|             | 5.2.2             | 2      | On Time                                             | 85  |  |  |  |

|             | 5.2.3             | 3      | Off Time                                            | 88  |  |  |  |

|             | 5.3               | Con    | tact Characterization                               | 90  |  |  |  |

|             | 5.3.3             | 1      | On State Contact Resistance                         | 91  |  |  |  |

|             | 5.3.2             | 2      | Off State Leakage                                   | 93  |  |  |  |

|             | 5.3.3             | 3      | Release Contamination                               | 95  |  |  |  |

|             | 5.4               | Mod    | deling Comparison                                   | 99  |  |  |  |

|             | 5.5               | Sum    | imary                                               | 101 |  |  |  |

| 6           | Con               | clusio | on / Future Work                                    | 102 |  |  |  |

|             | 6.1               | Con    | clusions                                            |     |  |  |  |

|             | 6.2               | Futu   | ure Work                                            |     |  |  |  |

|             | 6.2.3             | 1      | Improved Materials                                  |     |  |  |  |

|             | 6.2.2             | 2      | Scaling and Alternate "Fin" Geometry                |     |  |  |  |

| References1 |                   |        |                                                     |     |  |  |  |

| Appendix11  |                   |        |                                                     |     |  |  |  |

|             | Standa            | rd Pl  | hoto-Resist Recipes                                 | 117 |  |  |  |

|             | PCNR Process Flow |        |                                                     |     |  |  |  |

### List of Tables

| Table 1. Nominal Geometry used for scaling analysis of the PCNR     | 40 |

|---------------------------------------------------------------------|----|

| Table 2. Extracted actuation scaling trends for PCNR devices        | 51 |

| Table 3. Predicted PCNR performance at different levels of scaling. | 52 |

## List of Figures

| Figure 1. Current vs gate voltage for a MOSFET [5]. Sub-threshold slope and desired on-off ratio sets the   |

|-------------------------------------------------------------------------------------------------------------|

| threshold voltage of a transistor2                                                                          |

| Figure 2. Schematic of a ReRAM device. A single device can be used to store either a digital value (1/0)    |

| or an analog value (relative resistance)                                                                    |

| Figure 3. Schematic of an MTJ. Change in magnetic pole alignment of the two ferroelectric layers varies     |

| tunneling current through a thin insulator4                                                                 |

| Figure 4. Schematic of a PCRAM cell. A small section of phase change material is converted between          |

| amorphous and crystalline states to control device resistivity5                                             |

| Figure 5. Schematic of a FeFET. The polarization direction of a ferroelectric layer changes the threshold   |

| voltage of a FET6                                                                                           |

| Figure 6. Schematic of a simple electrostatic cantilever MEMS relay. Electrostatic force pulls the contact  |

| pair together, allowing current to flow7                                                                    |

| Figure 7. Schematic of the four terminal crab leg relay design. A bias can be applied to the body           |

| electrode, while actuation voltage is applied to the gate electrode. Drain and source contacts are          |

| separated from the electrodes                                                                               |

| Figure 8. Schematic of vertical electrostatic cantilever relay built in a back end of the line process. The |

| beam and contacts are made from multiple interconnect layers from a CMOS process                            |

| Figure 9. Schematic of a switch actuated by thermal expansion. A chevron structure is used to amplify       |

| the small displacements of the expanding beams10                                                            |

| Figure 10. Schematic of a piezoelectric cantilever. Expansion of the piezoelectric layer will bend the      |

| flexure to make connect the contacts                                                                        |

| Figure 11. Schematic of an electrostatic cantilever beam relay used for scaling analysis                    |

| Figure 12. Isotropic scaling of voltage and area based on scaling of the smallest demonstrated MEMS         |

| relay to date15                                                                                             |

| Figure 13. Comparison of actuation voltage and area between the scaled electrostatic cantilever MEMS        |

| relay and state of the art CMOS. CMOS data is pulled from [1] and [2]                                       |

| Figure 14. Isotropic scaling of beam restoring force and adhesion force based on scaling the smallest       |

| demonstrated MEMS relay to date                                                                             |

| Figure 15. Schematic of the Cavendish Kinetics "teeter-totter" non-volatile relay. A rigid beam pivots to   |

| connect and disconnect a pair of contacts                                                                   |

| Figure 16. Schematic of the electrostatic shuttle relay. The shuttle is held in place by Van der Waals      |

| adhesion and is moved by electrostatic attraction19                                                         |

| Figure 17. Schematic of the pulse activated piezo switch. A piezoelectric actuator is used to break         |

| surface adhesion and transfer a free floating shuttle between the actuator and the contacts                 |

| Figure 18. Fabrication of the PAPS relay. The relay is fabricated in 9 steps. SEM images show a fabricated  |

| and released PAPS relay from different angles. S and D represent the source and drain contacts21            |

| Figure 19. Testing summary for the PAPS relay highlighting (a) electrostatic only switching, (b) SEM        |

| images of shuttle motion, (c) schematics of shuttle motion, and (d) Piezoelectric actuation with            |

| electrostatic bias                                                                                          |

| Figure 20. Schematic representation of the phase change NEMS relay in (a) 2D cross section and (b) 3D       |

| isometric views. The actuator and contact pair are the two main components of the PCNR                      |

| Figure 21. Switching process for turning the phase change NEMS relay on and off27                           |

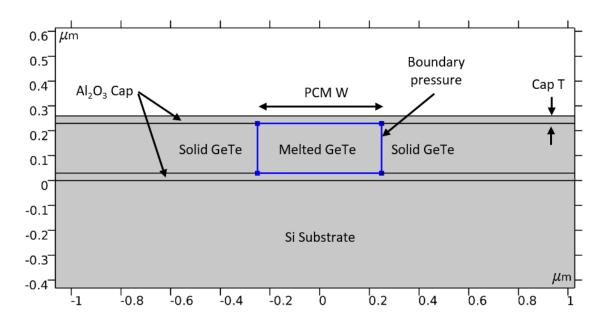

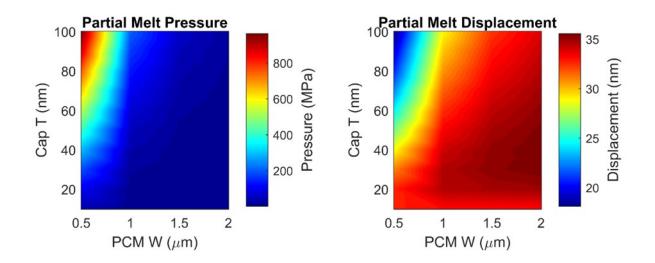

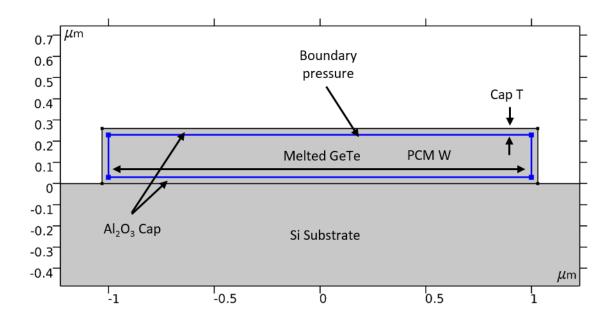

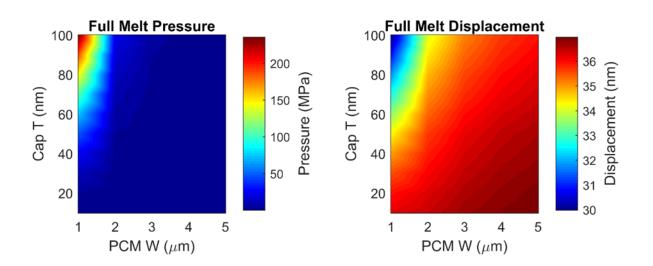

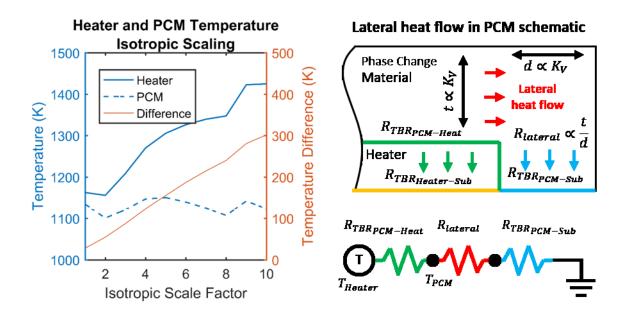

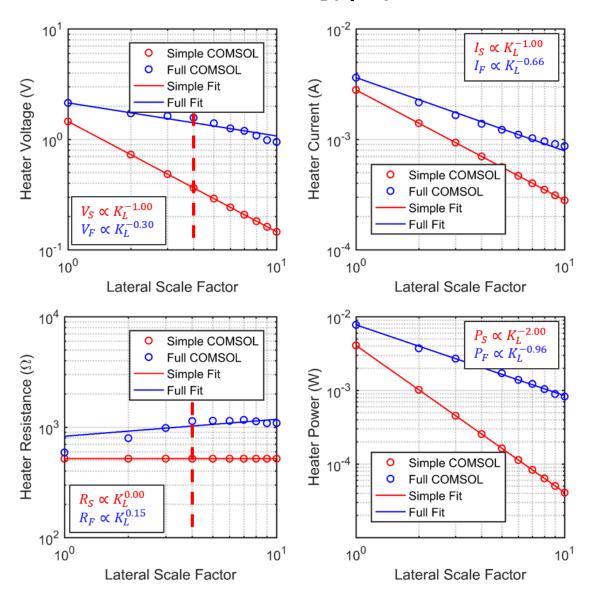

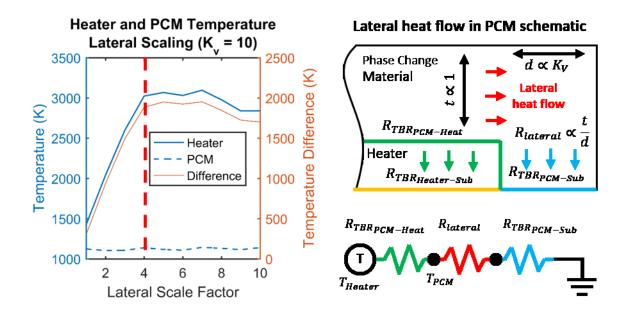

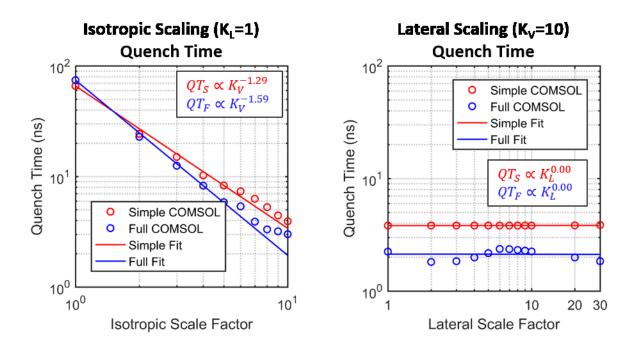

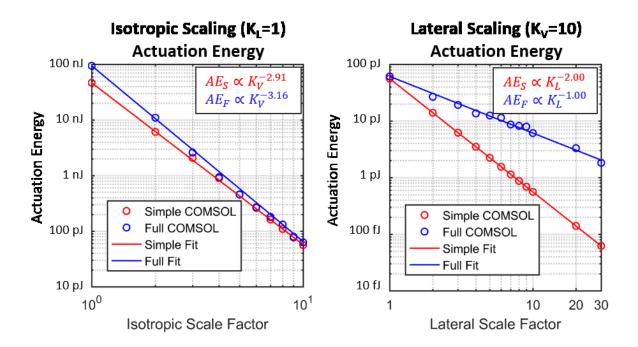

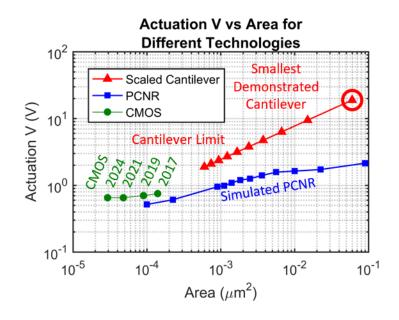

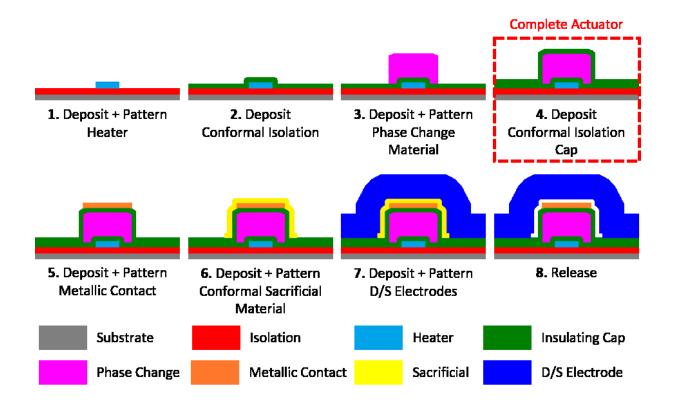

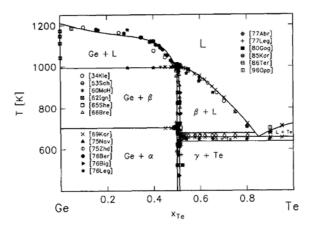

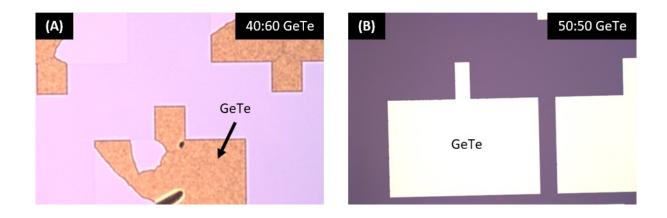

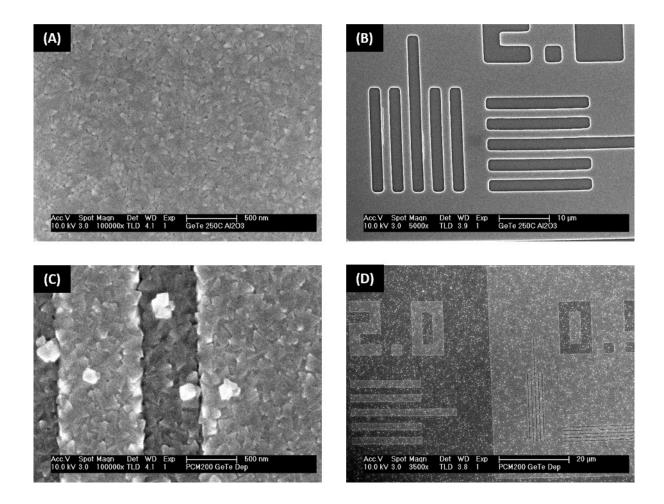

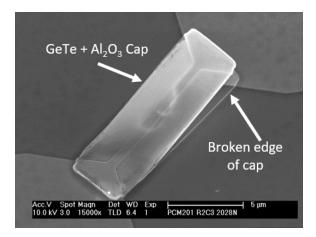

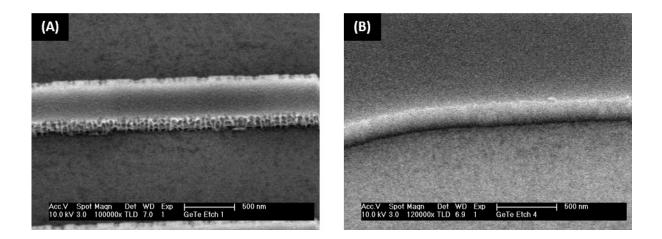

Figure 22. Comparison of work densities for common materials used in MEMS actuators. Adapted from Figure 24. Resistivity and temperature coefficient of resistivity measurements for heater tungsten. ..... 32 Figure 26. 3D and 2D cross-section views of the COMSOL model. Sections are colored by material.......34 Figure 27. Progression of melted PCM during heating and cooling of the PCNR actuator. Colored sections indicate melted PCM. Graphs show maximum temperatures of the actuator surface and internal PCM.35 Figure 28. Mechanical actuator 2D model. GeTe is encapsulated in  $Al_2O_3$  and is on top of an Si substrate. Figure 29. Mechanical actuator model setup for partially melted GeTe. A boundary load (blue) is applied Figure 30. Hydrostatic pressure and actuator displacement for varied melted phase change material widths and cap thicknesses. The melted PCM is constrained on the sides by solid PCM. PCM W refers to Figure 31. Mechanical actuator model setup for fully melted GeTe. A boundary load (blue) is applied to Figure 32. Hydrostatic pressure and actuator displacement for varied PCM widths and cap thicknesses. Figure 33. Isotropic scaling trend extraction for simple and full COMSOL models. Voltage, current, resistance, and power are all measured at the heater when heating the surface of the PCM to just above Figure 34. Heater and PCM temperature isotropic scaling. Colored arrows indicate heat flow through each thermal resistance. Deviation in heater and PCM temperature is explained by lateral heat flow (red Figure 35. Lateral scaling trend extraction for simple and full COMSOL models. Voltage, current, resistance, and power are all measured at the heater when heating the surface of the PCM to just above the melting point of the PCM. Vertical red dashed lines indicate the boundary between two trends. Fits Figure 36. Heater and PCM temperature lateral scaling. Colored arrows represent heat flow through the corresponding resistance. Deviation in heater and PCM temperature is explained by lateral heat flow (red arrows) in the 2D schematic of an actuator. The TBR between the PCM and substrate (blue) Figure 37. Quench time scaling trend extraction for simple and full COMSOL models. Quench time is Figure 38. Isotropic and lateral scaling of actuation energy. Actuation energy is defined as the electrical Figure 39. Comparison of actuation voltage and area between the highly scaled PCNR, the scaled electrostatic cantilever MEMS relay, and state of the art CMOS. CMOS data is pulled from [1] and [2]..52 Figure 40. Fabrication flow for the Phase Change NEMS Relay. Fabrication of just actuators is completed Figure 42. Optical microscope images comparing adhesion and roughness of GeTe with (a) Te rich 40:60 GeTe and (b) stoichiometric 50:50 GeTe......57

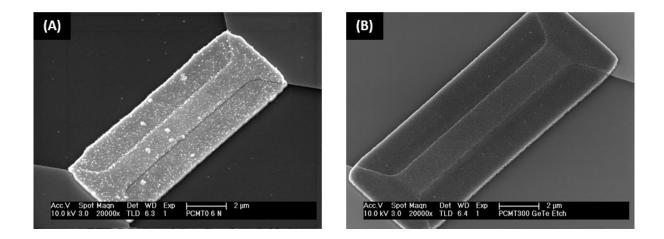

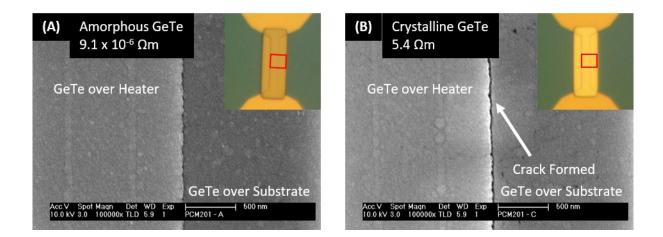

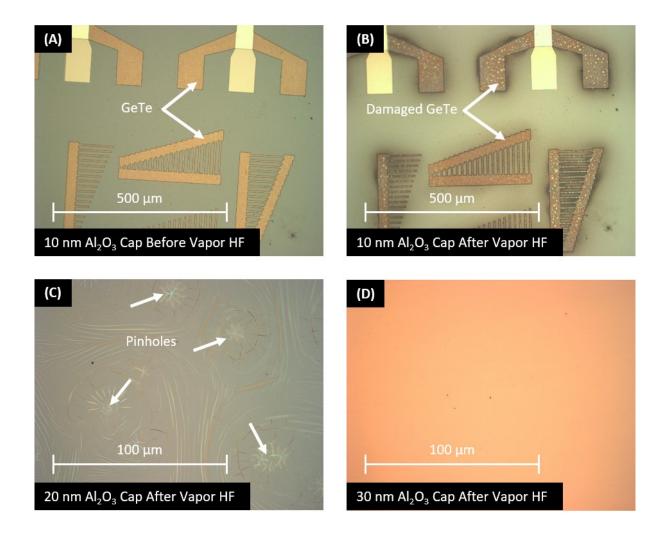

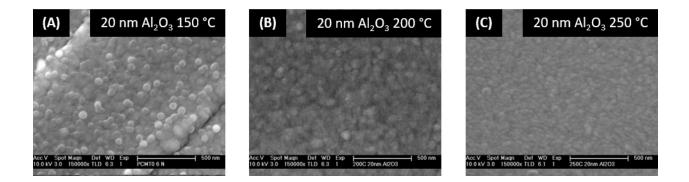

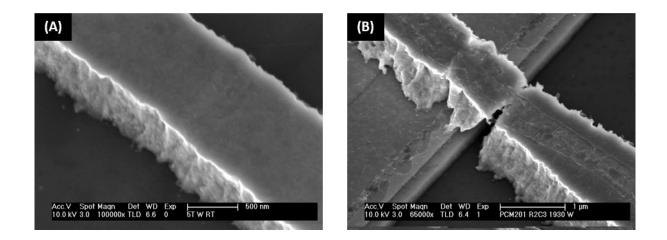

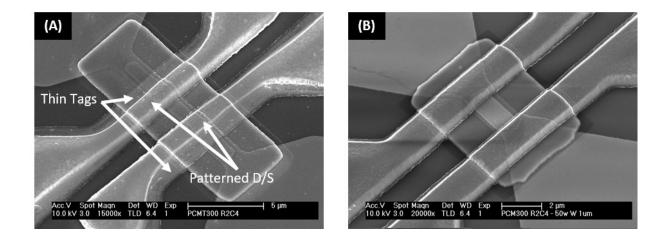

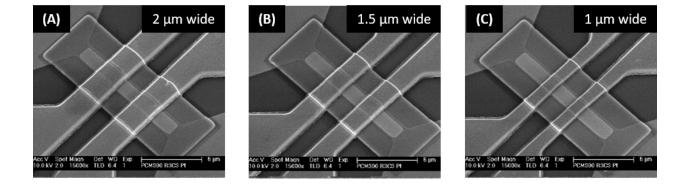

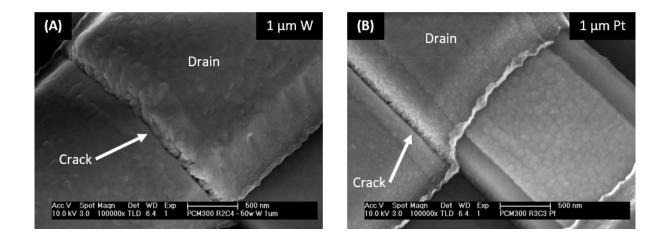

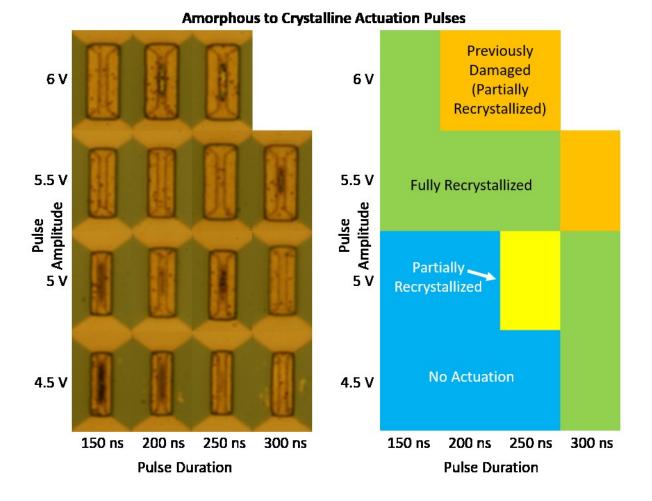

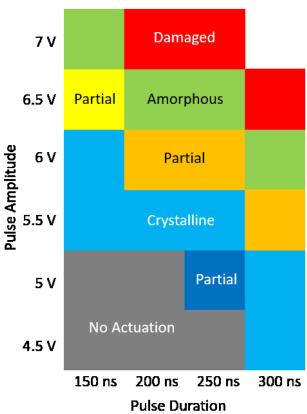

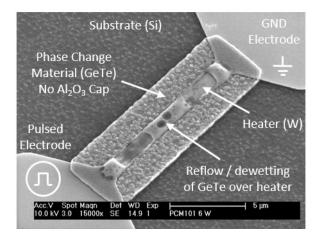

Figure 43. GeTe roughness comparison for crystalline GeTe deposited on (a,b) a test Si substrate with 10 nm Al<sub>2</sub>O<sub>3</sub> deposited by ALD at 250 °C and (c,d) device substrates with 10 nm Al<sub>2</sub>O<sub>3</sub> deposited by ALD Figure 44. GeTe roughness comparison between devices fabricated with (a) 10 nm Al<sub>2</sub>O<sub>3</sub> deposited by ALD at 150 °C and (b) 30 nm Al<sub>2</sub>O<sub>3</sub> deposited by ALD at 250 °C.....60 Figure 45. Conversion of patterned GeTe from (a) the amorphous state to (b) the crystalline state. The GeTe resistivity decreases by almost six orders of magnitude. Optical Microscope images show GeTe Figure 46. Actuator with delamination of the GeTe layer after actuation. GeTe was deposited as Figure 47. Sidewall comparison of GeTe patterned by RIE with (a) a mixture of Chlorine and Argon and Figure 48. Optical microscope images of (a) devices fabricated with a 10 nm Al<sub>2</sub>O<sub>3</sub> cap deposited by ALD at 150 °C before exposure to vapor HF, (b) devices with GeTe damaged by vapor HF, (c) a test layer of GeTe with a 20 nm Al<sub>2</sub>O<sub>3</sub> cap deposited by ALD at 250 °C with GeTe damage from vapor HF stemming from pinhole defects in the cap, and (d) a test layer of GeTe perfectly protected by a 30 nm Al<sub>2</sub>O<sub>3</sub> cap deposited by ALD at 250 °C......63 Figure 49. SEM images comparing roughness of a 20 nm film of Al<sub>2</sub>O<sub>3</sub> deposited by ALD at temperatures Figure 50. SEM images comparing wall roughness of patterned tungsten on (a) a test wafer with a step Figure 51. Comparison of drain and source liftoff with photoresist that has (a) too much undercut and Figure 52. SEM images comparing the drain and source with widths of (a) 2  $\mu$ m, (b) 1.5  $\mu$ m, and (c) 1  $\mu$ m. Figure 53. SEM images of step coverage of the drain and source fabricated from (a) 1 µm of tungsten Figure 54. Optical microscope images of a tungsten drain and source test structure on a 20 nm SiO<sub>2</sub> film Figure 55. Optical microscope images highlighting the transformation of GeTe from crystalline to Figure 56. Optical microscope images of actuators after varied actuation pulses are applied. The effect of each pulse is characterized to have one of four effects: no actuation, partial actuation, fully actuated, or damaged......72 Figure 57. Optical microscope images of actuators before and after varied recrystallization pulses are applied. Recrystallization can be observed by the disappearance of dark areas in the actuator......73 Figure 58. Optical microscope images of actuators after varied recrystallization pulses are applied. Pulse effects are categorized as: no actuation, partially recrystallized, fully recrystallized, and previously damaged (partially recrystallized)......74 Figure 59. Actuation pulse effect matrix. The desired areas of operation are amorphous and crystalline. Pulses labeled as amorphous are used to expand the actuator, and pulses labeled as crystalline are used Figure 60. SEM image of an actuated device exhibiting reflow. This device does not have an  $Al_2O_3$  cap, allowing GeTe to reflow and dewet from the heater.....76

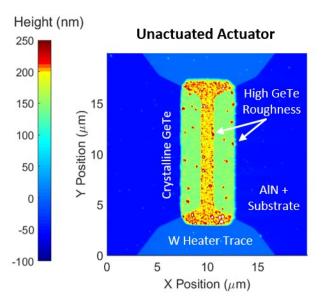

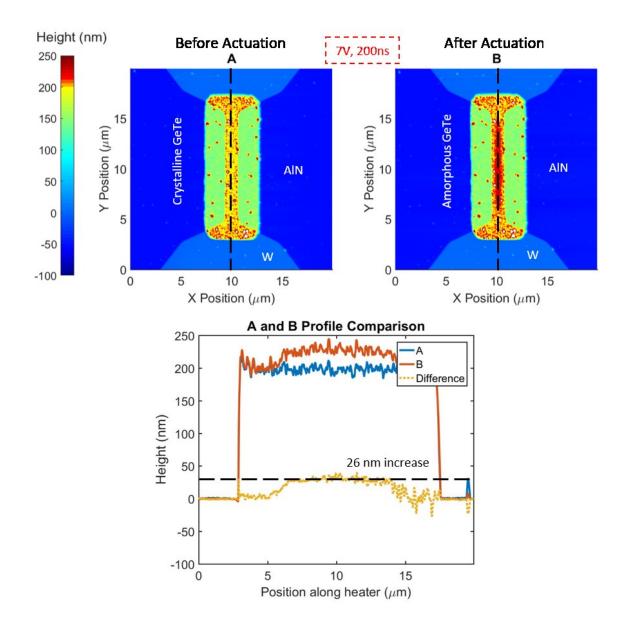

| Figure 61. AFM measurement of an unactuated (as fabricated) actuator. A nonlinear color scale is used           |

|-----------------------------------------------------------------------------------------------------------------|

| to highlight height variation of GeTe at the surface of the actuator. Height is referenced to the heater        |

| trace                                                                                                           |

| Figure 62. AFM measurements of a device before and after an actuation pulse. AFM profile A                      |

| corresponds to an as fabricated unactuated device. AFM profile B corresponds to the same device after           |

| actuation. Profile comparison shows the increase in actuator thickness after actuation (profile B –             |

| profile A)                                                                                                      |

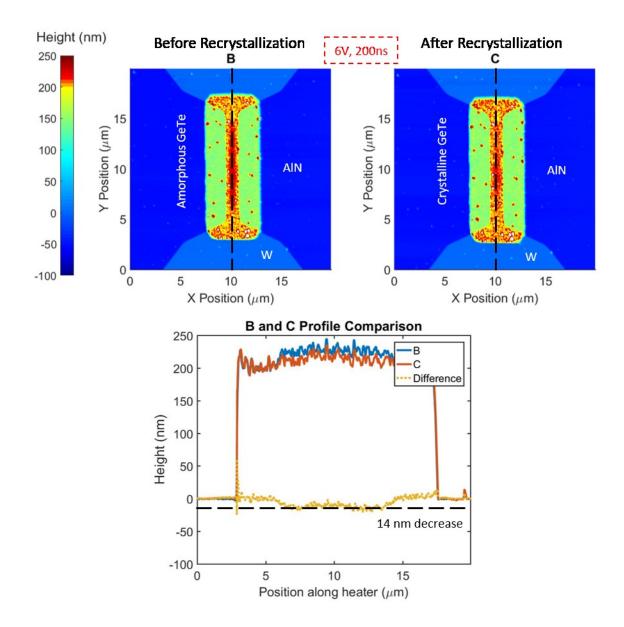

| Figure 63. AFM measurements of a device before and after a recrystallization pulse. AFM profile B               |

| corresponds to the previously actuated device. AFM profile C corresponds to the same device after the           |

| recrystallization pulse. Profile comparison shows the decrease in actuator thickness after                      |

| recrystallization (profile C – profile B)80                                                                     |

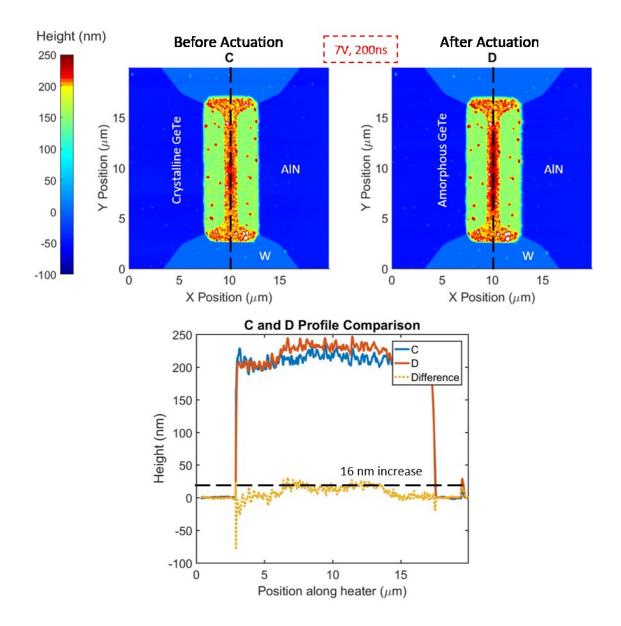

| Figure 64. AFM measurements of a device before and after a second actuation pulse. AFM profile C                |

| corresponds to the previously recrystallized device. AFM profile D corresponds to the same device after         |

| the actuation pulse. Profile comparison shows the increase in actuator thickness after recrystallization        |

| (profile D – profile C)                                                                                         |

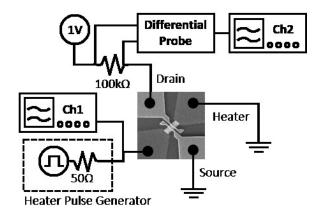

| Figure 65. Relay actuation test setup. A pulse generator with 50 $\Omega$ internal impedance is used to drive   |

| the PCNR heater. A 1 V potential with a 100 k $\Omega$ resistor is used to sense contact between the source and |

| drain85                                                                                                         |

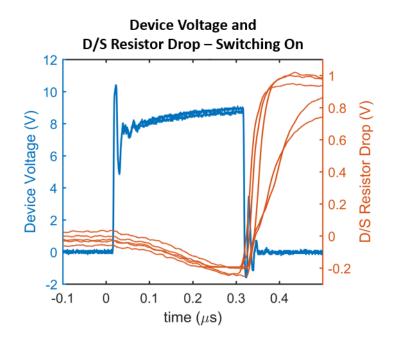

| Figure 66. Unprocessed oscilloscope traces of five consecutive actuations of a device being turned on.          |

| Device voltage includes voltage drop over the probes and traces. D/S resistor drop is proportional to           |

| current flow through the drain and source87                                                                     |

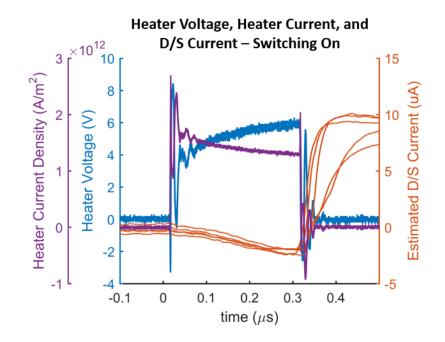

| Figure 67. Extracted heater voltage, heater current, and D/S current of five consecutive actuations of a        |

| device being turned on. Heater voltage is only the voltage drop over the heater. Heater current density         |

| is the current normalized to the 1.5 $\mu m$ by 50 nm heater cross-section                                      |

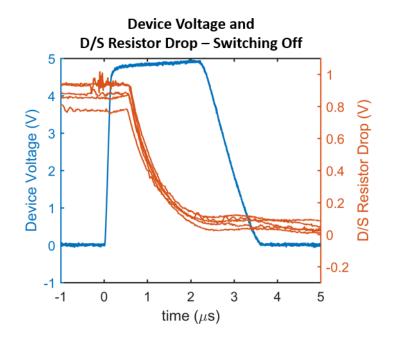

| Figure 68. Unprocessed oscilloscope traces of five consecutive actuations of a device being turned off.         |

| Device voltage includes voltage drop over the probes and traces. D/S resistor drop is proportional to           |

| current flow through the drain and source                                                                       |

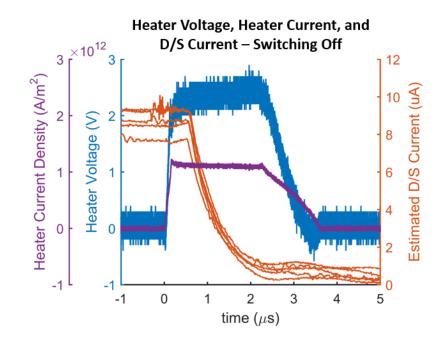

| Figure 69. Extracted heater voltage, heater current, and D/S current of five consecutive actuations of a        |

| device being turned off. Heater voltage is only the voltage drop over the heater. Heater current density        |

| is the current normalized to the 1.5 $\mu m$ by 50 nm heater                                                    |

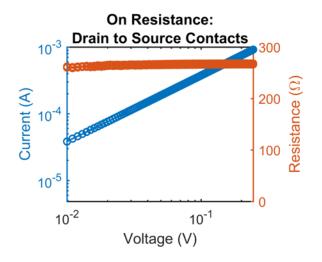

| Figure 70. I-V curve measurement of a PCNR device in the on state91                                             |

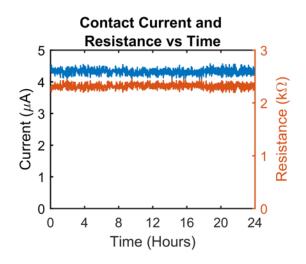

| Figure 71. Current and resistance measurements over 24 hours. The device being tested for non-                  |

| volatility is at room temperature92                                                                             |

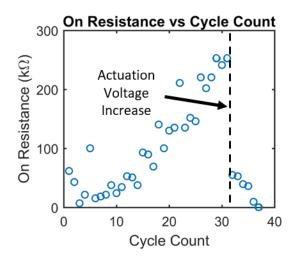

| Figure 72. On resistance versus cycle count for a device cycling to failure. A small increase in actuation      |

| voltage is used to reduce on resistance after 31 cycles. Failure occurs after 36 complete cycles                |

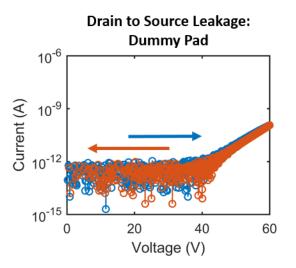

| Figure 73. I-V curve measurement of a PCNR device with dummy drain and source pads. Current is below            |

| the noise floor for this configuration until an applied bias of 40 V.                                           |

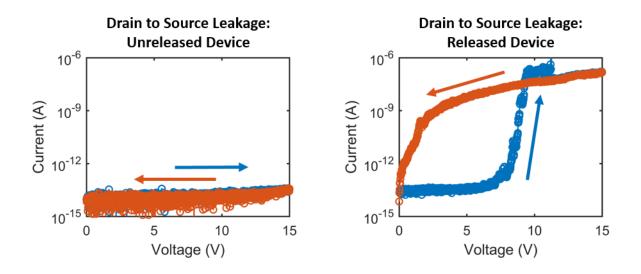

| Figure 74. I-V curve measurements of an unreleased and released PCNR device. Breakdown can be seen              |

| in the hysteresis of the released device95                                                                      |

| Figure 75. I-V curve measurements of the same released device at initial breakdown and after                    |

| breakdown. The after breakdown I-V curve is consistent for subsequent I-V curves                                |

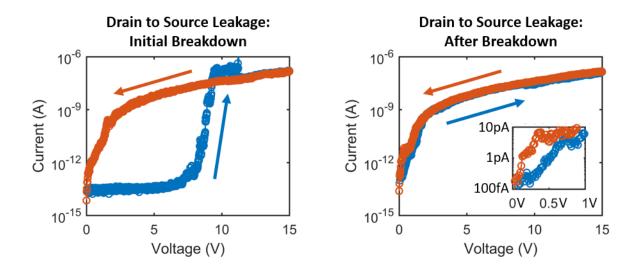

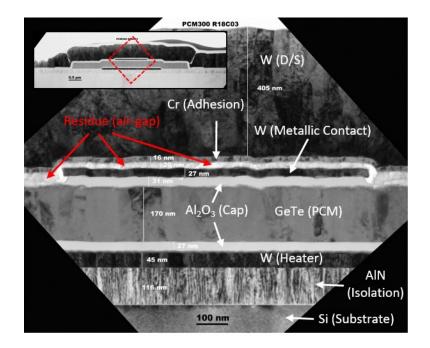

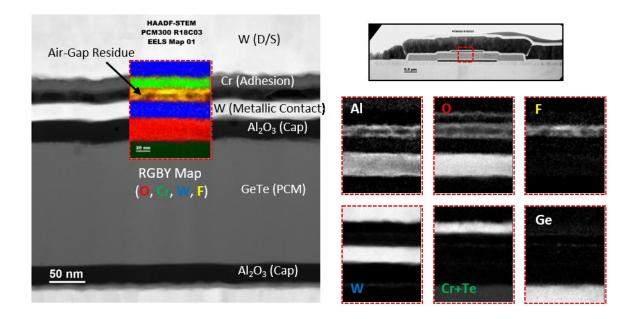

| Figure 76. Illustrated schematics of the (a) TEM cross-section sample cut location and (b) the PCNR             |

| cross-section and (c) TEM image. (TEM courtesy of IBM Almaden Research)                                         |

| Figure 77. TEM cross-section focused on the metallic contact and air gap of a released unactuated PCNR.            |

|--------------------------------------------------------------------------------------------------------------------|

| Residue can be seen in the air gap, likely preventing contact between the metallic contact and                     |

| drain / source contacts. (TEM courtesy of IBM Almaden Research)                                                    |

| Figure 78. Electron energy loss spectroscopy (EELS) elemental mapping of materials in and around the               |

| air-gap. Fluorinated alumina can be seen as a residual material inside the air-gap. (TEM courtesy of IBM           |

| Almaden Research)                                                                                                  |

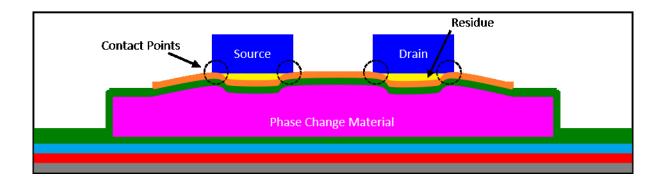

| Figure 79. Schematic of contact points assuming fluorinated alumina residue blocks contact at the                  |

| center of the drain and source                                                                                     |

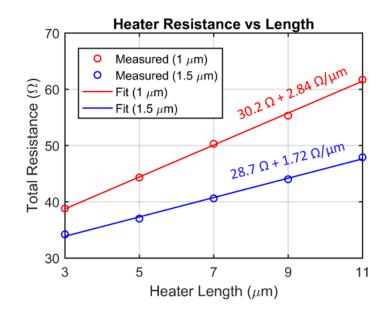

| Figure 80. Heater resistance measurements for 1 $\mu$ m and 1.5 $\mu$ m wide heaters. Measurements include         |

| probe and pad resistance of the device. Fit slopes extract true heater resistance, while offsets extract           |

| true pad and probe resistance                                                                                      |

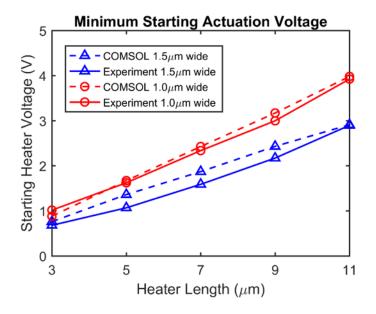

| Figure 81. Comparison of minimum starting actuation voltages between devices simulated in COMSOL                   |

| and measured fabricated devices. 1 $\mu m$ and 1.5 $\mu m$ wide heaters with lengths of 3 $\mu m$ – 11 $\mu m$ are |

| measured                                                                                                           |

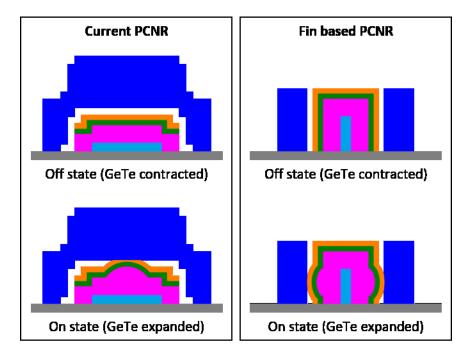

| Figure 82. Schematics of the current PCNR geometry and the proposed fin PCNR geometry. The current                 |

| PCNR expands vertically, while the fin PCNR expands laterally                                                      |

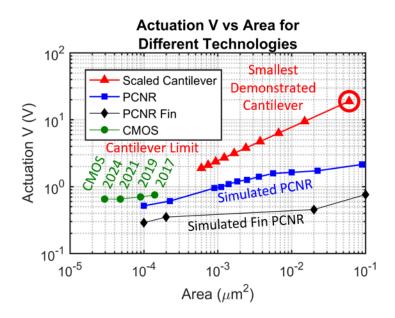

| Figure 83. Comparison of actuation voltage and area between the "fin" PCNR, the highly scaled current              |

| PCNR geometry, the scaled electrostatic cantilever MEMS relay, and state of the art CMOS. CMOS data                |

| is pulled from [1] and [2]105                                                                                      |

|                                                                                                                    |

#### 1 Introduction

Complementary metal oxide semiconductors (CMOS) have dominated all aspects of computing from logic to memory. Moore's law, which predicted aggressive scaling of transistors, lead to the complex, high speed, and efficient computers of today [1]. Scaling of transistors has become more difficult and is expected to saturate around 2028 [2]. Further scaling will need to be through 3D integration, which increases device density but does not address power efficiency. Concerns with energy efficiency and energy consumption have grown with the advent of the internet of things (IoT).

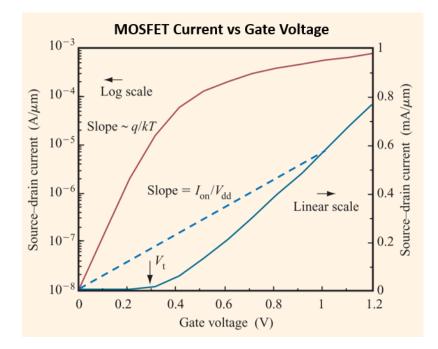

Leakage is becoming a dominant factor in energy consumption as CMOS is continued to be scaled down [3]. A tradeoff exists between actuation voltage and leakage [4]. The sub-threshold slope describes the current flow through a transistor as a function of voltage applied to the gate (Figure 1). In particular the sub-threshold slope defines the transistor response before the threshold voltage. A steep slope allows for greater on/off ratios for a given gate voltage. Switching voltage, and therefore switching energy for CMOS is limited by the sub-threshold slope [5]. An ideal energy efficient technology will have a steep sub threshold slope to maximize gain and minimize actuation voltage. Additionally, "more than Moore" devices have gained attention where additional functions may be built into a device. One particular feature is non-volatility where a device can hold a state without applied power. Non-volatility opens the use of a device in memory type applications. Lower voltage, lower power, and non-volatility are desired features of a CMOS alternative.

Figure 1. Current vs gate voltage for a MOSFET [5]. Sub-threshold slope and desired on-off ratio sets the threshold voltage of a transistor.

#### 1.1 Emerging Technologies

Many emerging CMOS alternatives are targeted towards non-volatile memory applications. Of these new technologies, the most common are: resistive memory (ReRAM), phase change memory (PCRAM), and magnetoresistive memory (MRAM) [6] [7]. These emerging memories work by changing the resistance of a material through various actuation methods. Additionally they are all characterized as two-terminal devices, where actuation and state sensing are performed through the same set of terminals. Another emerging technology is the ferroelectric field effect transistor (FeFET) which is a four-terminal device that can be in memory or logic circuits.

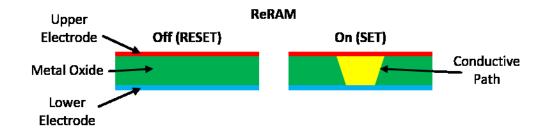

ReRAM (Figure 2) works by controlling the resistance of a metal-insulator-metal structure [8][9][10]. If sufficient voltage is applied to the metal electrodes that sandwich the insulator, a conductive path is formed, thus changing the insulator to a conductor. Forming the conductive path is referred to as

the "SET" action. Further application of voltage will destroy the conductive path, thus resetting the device to a high resistance state. Returning the device to a high resistance state is referred to as the "RESET" action. ReRAM devices are small and can be formed into dense memory arrays. In addition, resistance can be controlled leading to ReRAM use in fast and efficient neuromorphic computing applications [11][12]. The main disadvantage of ReRAM is reliability and consistency of switching.

*Figure 2. Schematic of a ReRAM device. A single device can be used to store either a digital value (1/0) or an analog value (relative resistance).*

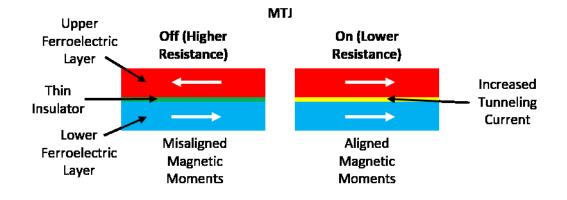

MRAM (Figure 3) devices are built using a magnetic tunnel junction (MTJ) [13][14][15]. The MTJ is a stack of two ferroelectric materials separated by a thin (< 2 nm) insulator. Switching the magnetic moments of the ferroelectric layers to be either aligned or misaligned will adjust the resistance through the MTJ as their alignment effects the tunneling through the thin insulating layer. Resistance is low for aligned moments, while resistance is high for misaligned moments. Switching is performed by the application of high magnetic fields. A few disadvantages of MRAM are limited scalability and high required currents associated with generating the fields. An alternate approach to MRAM is spin-transfer torque MRAM (STT-MRAM) [13]. In STT-MRAM current is flowed directly through the MTJ to switch alignment of the magnetic moments in the ferroelectric layers. The main disadvantages to STT-MRAM are fabrication difficulties associated with etching the MTJ pillars, endurance of the MTJ, and tradeoffs between error rates and switching energy.

*Figure 3. Schematic of an MTJ. Change in magnetic pole alignment of the two ferroelectric layers varies tunneling current through a thin insulator.*

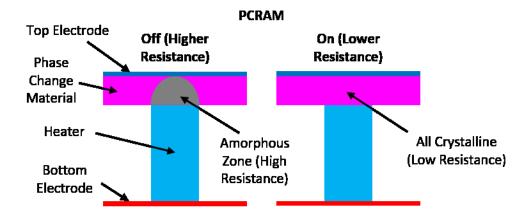

PCRAM (Figure 4) is built around the change in resistivity when switching between crystalline (conductive) and amorphous (resistive) states of chalcogenide glasses [16][17][18][19][20]. Switching states is a thermal process. A RESET operation will melt and quench a section of phase change material to set it in the amorphous state. A SET operation will heat the amorphous material to foster crystal growth, bringing the phase change material into the crystalline state. PCRAM has already seen success in commercial memory applications and will continue to be developed. The advantages of PCRAM are its high scalability, relatively high speed for a memory, and relatively high on-off ratio. The major disadvantages of PCRAM are the higher currents required to resistively heat and melt the phase change material, and limited ability to maintain non-volatility in elevated temperature environments.

Figure 4. Schematic of a PCRAM cell. A small section of phase change material is converted between amorphous and crystalline states to control device resistivity.

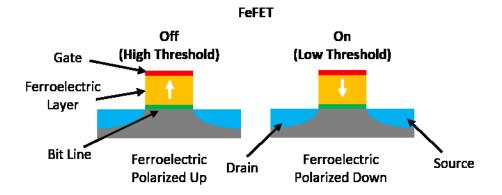

The FeFET (Figure 5) is a modified field effect transistor where the gate is augmented by the addition of a ferroelectric layer like HfO<sub>2</sub> [21][22]. The threshold voltage of the FET is shifted by the polarization direction of the ferroelectric layer. When the ferroelectric layer is polarized upward, the threshold voltage of the FET is high. When the ferroelectric layer is polarized downward, the threshold voltage of the FET is low. Gate voltage can be set between the threshold voltages associated with the different ferroelectric polarization directions. With the proper gate voltage, the FET will turn on and off depending on the ferroelectric polarization direction. Unlike the other emerging technologies, the FeFET is a four-terminal device, which makes possible to use it as logic element. FeFETs are fast and scalable, but require relatively high voltage (around 4 V) to switch states.

Figure 5. Schematic of a FeFET. The polarization direction of a ferroelectric layer changes the threshold voltage of a FET.

#### 1.2 Background on MEMS Relays

MEMS relays have come out as an alternative technology to CMOS to improve energy efficiency in computing and memory [23][24][25]. MEMS relays are built around contacts separated by an "air-gap" which is opened and closed by an actuator. When the contacts are open and separated by an air gap there is near zero leakage. When the contacts are closed, current can flow only limited by the contact resistance. These relays are characterized by a large on-off ratio. In addition, switching energy can be dramatically reduced as the transition from on to off states is determined by physical connection of the contacts [26]. MEMS relays differ from other emerging technologies in that they are not two terminal devices and can be used in logic. The high energy efficiency and resistance to harsh environments has led to MEMS relays being proposed as a replacement to CMOS for power efficient computing [27]. One particular target application for MEMS relays is integration with CMOS in field programmable gate arrays (FPGAs). FPGAs are reconfigurable logic, which can benefit from the zero leakage current associated with the air gap of MEMS relays and the potentially low on state resistance. A study by Altera, an FPGA manufacturer, showed integration of MEMS relays in an FPGA could reduce total area by 43.6 %, reduce leakage power by 37 %, and reduce critical path delay by up to 28 % [28].

#### 1.2.1 Current State of MEMS Relays

A wide range of MEMS relays have been proposed ranging in function, actuation, and fabrication. The common design aspect among MEMS relays is the use of a flexure. This flexure provides constraint for components and in most cases a restoring force. Common actuation methods include electrostatic attraction, thermal expansion, and the piezoelectric effect.

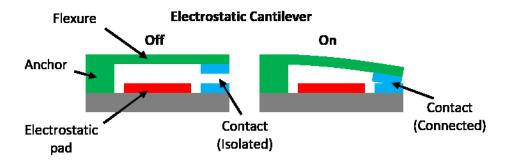

One of the most popular actuation methods for a relay uses electrostatic attraction to pull a pair of contacts together or apart. The simplest implementation of an electrostatic MEMS relay is a cantilever beam actuated by a single electrostatic pad (Figure 6) [29][30][31][32][33]. Beams are mostly commonly fabricated through common lithographic processes, but some are grown as nano-wires [34]. Electrostatic cantilevers have even been integrated to form a ring oscillator [35]. To date, the smallest by area demonstrated MEMS relays are simple electrostatic cantilever beams [36][37]. The cantilever beam devices typically rely on the flexure to provide adequate restoring force to break adhesion. Electrostatic actuation is typically characterized by high actuation voltages required to generate required forces over large gaps. The high actuation voltage limits the actuation energy reduction of this relay design compared to CMOS.

*Figure 6. Schematic of a simple electrostatic cantilever MEMS relay. Electrostatic force pulls the contact pair together, allowing current to flow.*

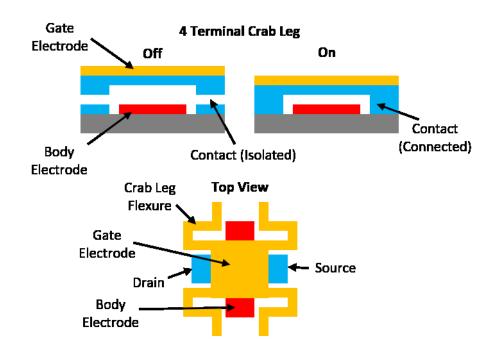

Another prominent example of an electrostatically actuation relay is the crab leg based four terminal electrostatic relay [38][39]. These relays (Figure 7) have been developed to minimize actuation voltage. A bias force is introduced by building a four terminal design. The bias force is generated by a constant voltage applied to the relay and allows for the relay to be kept close to the threshold for switching. The bias voltage does not switch, so no energy is consumed in the relay by the bias. The actuation voltage is dramatically reduced, lowering switching energy associated with charging and discharging both the actuator of the relay and the capacitance of the traces connecting to it. Other relays have also adopted the bias technique to reduce the switching energy consumption to near the theoretical limit [26]. The crab leg actuators have been used in logic circuits and a demonstration of a simple microprocessor [27]. The large actuator area of these relays limits scalability and requires significantly larger areas than other relays.

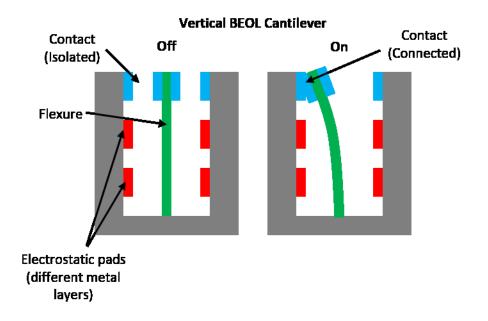

Figure 7. Schematic of the four terminal crab leg relay design. A bias can be applied to the body electrode, while actuation voltage is applied to the gate electrode. Drain and source contacts are separated from the electrodes. Another alternative electrostatic MEMS relay design is based on the back end of the line (BEOL) CMOS process where the relay is built within the interconnects. In this relay design (Figure 8) an electrostatic cantilever is built to stand vertically like a pillar and deform laterally [40]. The pillar configuration reduces the area required by the cantilever as it is now limited by the cross-section of the beam and the lithography for forming the air gap. Additionally, the relay is non-volatile and can be used as memory. The beam is held in a particular state by surface adhesion. Although this design shows promise for scalability and CMOS compatibility, tuning the residual stress in the layers and the defining high aspect ratio nanoscale airgaps will be a challenge for device yield.

Figure 8. Schematic of vertical electrostatic cantilever relay built in a back end of the line process. The beam and contacts are made from multiple interconnect layers from a CMOS process.

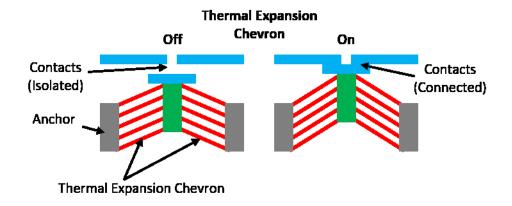

Thermal actuation is less commonly used in relays as it generally requires high power to maintain a state. One example of a thermal relay (Figure 9) uses a chevron type structure to close and open an air gap [41]. Thermal expansion as an actuation method generates high forces but small displacement. The chevron design amplifies the relatively small strains generated by thermal expansion into useable displacement. This thermal relay example is designed for characterizing relay contact materials. Since the relay is primarily used for laboratory measurements power consumption and speed are not important, only robustness and consistency.

*Figure 9. Schematic of a switch actuated by thermal expansion. A chevron structure is used to amplify the small displacements of the expanding beams.*

Piezoelectric actuation uses piezoelectric materials like aluminum nitride (AIN) to generate strains from an applied electric field. Piezoelectric relays are typically unimorph or bimorph cantilevers (Figure 10) where the piezoelectric is off center from the neutral axis of the beam. When the piezoelectric expands or contracts, it induces a bending moment in the beam and deflects the tip. Residual stresses and the fabrication of thin piezoelectric layers are challenges in the fabrication of piezoelectric cantilever relays. 10 nm thin piezoelectric layers have been synthesized for relays [42][43]. Piezoelectric cantilevers have demonstrated sub 1V actuation with ultra-thin piezoelectric layers and stress compensated beams [44]. Alternatively, buckling piezoelectric actuators have been demonstrated as an alternative geometry that allows for low voltage operation and high-scalability [45][46]. These demonstrated piezoelectric relays are all volatile devices, and use flexures which prevent scaling to sizes comparable to CMOS components.

*Figure 10. Schematic of a piezoelectric cantilever. Expansion of the piezoelectric layer will bend the flexure to make connect the contacts.*

Non-volatile relays have gained recent interest for their potential use in memory as well as logic for computing with an intermittent power source. A wide range of geometries have been explored for non-volatile relays, but the majority of designs rely on electrostatic actuation and surface adhesion [36][40][47][48][49][50]. Demonstrated non-volatile relays use surface adhesion of the contacts to hold a specific state when actuation power is not applied. Relay adhesion, which is typically seen as a challenge to scaling, is used as a feature to hold a state. Restoring forces from the beam are small, so actuation voltage must overcome adhesion rather than rigidity of the beams.

Key limits to the adoption of MEMS relays in memory and logic are reliability and scalability [23]. Failure of the contact is one of the most common failure modes in relays [51]. A range of failure mechanisms have been investigated ranging from mechanical failure of the contact material to tribopolymer buildup on the contact [52]. Careful selection of contact materials and processing methods have shown improvements in the cycles to failure [53]. While high cycle count is required for logic, some memory based applications can tolerate lower cycles to failure.

#### 1.2.2 Scaling of Flexure Based MEMS Relays

Although there have been attempts to aggressively scale flexure based relays, the smallest flexure based relay to date is only 200 nm by 300 nm based on the dimensions of the beam [36][37]. This excludes anchors and traces, so the full footprint is even larger. The general consensus is that these cantilever based relays cannot be scaled down to CMOS comparable dimensions with low actuation voltage and the scaling of flexure based relays is primarily limited by the air gap and contact adhesion [23].

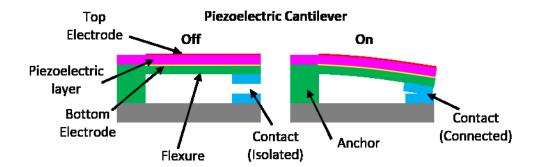

To fully understand the limits of flexure based relay scaling an electrostatic cantilever device is evaluated for scalability. An electrostatic cantilever relay is chosen because it is the smallest NEMS relay demonstrated to date. Figure 11 shows the schematic for the evaluated design. Key dimensions are the cross-section of the beam, the length of the beam, and the air gap. The air gap sets the required deflection of the cantilever beam.

Electrostatic Cantilever Model

*Figure 11. Schematic of an electrostatic cantilever beam relay used for scaling analysis.*

Beam stresses are the primary limiting factor in miniaturizing the flexure based relays. For a cantilever beam with an end load, deflection (d) can be related to beam geometry and force by:

$$d = \frac{FL^3}{3EI} \tag{1}$$

where F is the force at the tip of the cantilever beam, L is the length of the beam, E is the young's modulus of the beam material, and I is the second moment of area of the beam cross-section. For a rectangular cross-section, I can be modeled as:

$$I = \frac{wt^3}{12} \tag{2}$$

where w is the beam width and t is the beam thickness. Maximum stress on a bending beam is at the surface and is dependent on the applied bending moment. Maximum stress ( $\sigma_{max}$ ) can be calculated by:

$$\sigma_{max} = \frac{Mt}{2I} \tag{3}$$

where M is the bending moment in the beam. Bending moment varies along the length of a cantilever beam with an end load. The highest bending moment is at the anchor and can be calculated by:

$$M = FL \tag{4}$$

For a viable relay, maximum stress must be below the fatigue strength of the beam material. Rearranging maximum stress to be a function of beam displacement (air-gap) gives:

$$\sigma_{max} = \frac{3Edt}{2L^2} < \sigma_{fatigue} \tag{5}$$

When isotropically scaling a beam, where all dimensions scale by the same factor ( $K_v$ ), maximum stress will follow:

$$\sigma_{max} \propto \frac{dt}{L^2} \propto 1 \tag{6}$$

An aggressively scaled beam will be limited by the fatigue strength of the beam material. Assuming a minimum viable air-gap (fixed d), beam thickness and beam length must scale by:

$$t \propto L^2 \tag{7}$$

If a beam is optimized such that stress is close to the fatigue limit, it cannot be scaled after reaching the minimum air-gap. Beam thickness is limited by fabrication and sets the minimum beam length. For the purpose of this scaling analysis only electrostatic beams are considered. An alternate actuation method

uses a piezoelectric material in the beam to induce a bending moment with an applied voltage. While piezoelectric beams are generally considered a great actuation material for low power relays, they limit the scalability of the beam due to minimum layer thicknesses. The thinnest layer of piezoelectric AIN deposited for actuators to date is 10 nm, and film quality is shown to decrease with thickness [44][43] [42]. Electrostatically actuated relays only require the beam to be a metallic electrode and are therefore able to scale to thinner layers. Thinner beams allow for shorter beams, leading to smaller relays. Electrostatic actuation will cause a switch to turn on at the pull-in voltage. The pull in voltage ( $V_{pullin}$ ) for a cantilever can be calculated by:

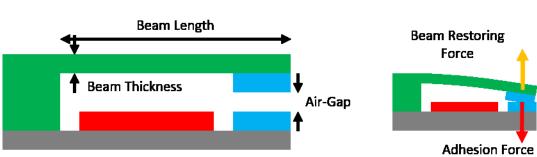

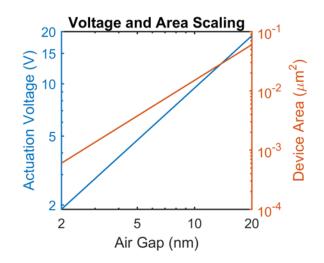

$$V_{pullin} = \sqrt{\frac{16t^3 d^3 E}{81\epsilon_o L^4}} \tag{8}$$

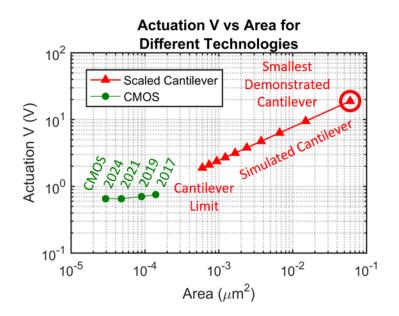

where  $\epsilon_o$  is the dielectric constant for vacuum [36]. The actuation voltage limit of electrostatic cantilevers can be estimated based on the current smallest demonstrated cantilevers to date. Actuation voltage (pullin voltage) and device area scaling are shown in Figure 12. The smallest beam is 20 nm wide and 30 nm long and actuates at nearly 2 V. Figure 13 compares these cantilever beams to CMOS and shows that even aggressive scaling results in devices that are significantly larger than CMOS and use high actuation voltages.

Figure 12. Isotropic scaling of voltage and area based on scaling of the smallest demonstrated MEMS relay

to date.

Figure 13. Comparison of actuation voltage and area between the scaled electrostatic cantilever MEMS relay and state of the art CMOS. CMOS data is pulled from [1] and [2].

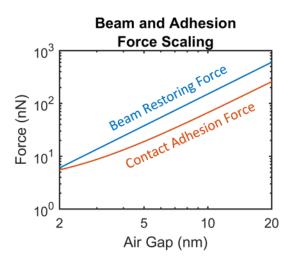

Adhesion force between contacts is present in all relay designs and can limit the scalability of a particular design. In a non-volatile relay design, where adhesion holds a contact in place, actuation forces

must be able to overcome adhesion. In a volatile relay design, where actuation voltage must be applied to maintain a state, the restoring force of the cantilever must be able to break the adhesion of the beam. The restoring force can be calculated by:

$$F = \frac{Edwt^3}{4L^3} > F_{adhesion} \tag{9}$$

where  $F_{adhesion}$  is the contact adhesion force. Contact adhesion is primarily Van der Waals forces between the contact surfaces assuming the contacts do not weld together from current flow during switching [54][55][56]. Van der Waals adhesion force ( $F_{VDW}$ ) can be modeled in two parts:

$$F_{adhesion} = F_{VDW} = F_{VDWsurface} + F_{VDWasperity}$$

(10)

where  $F_{VDW surface}$  is the parallel plate contribution from two close surfaces and  $F_{VDW asperity}$  is the contribution from direct contact of asperities in the contact. The parallel plate surface adhesion can be modeled as:

$$F_{VDW \, surface} = \frac{A_m A}{D_{rms}^3 6\pi} \tag{11}$$

where  $A_m$  is the Hamaker constant for the contact material pair, A is the overlapping area, and  $D_{rms}$  is the average roughness of the two contact surfaces. Roughness keeps the two surfaces separated, limiting adhesion between the parallel surfaces. In cases of high roughness, a few asperities will hold the surfaces apart. These asperities can have a large effect on adhesion at high surface roughness or small contact area, and can be modeled as:

$$F_{VDW\,asperity} = \frac{A_m R_A N_A}{6D_A^2} \tag{12}$$

where  $R_A$  is the radius of the asperity,  $N_A$  is the number of asperities, and  $D_A$  is the distance separating the contacting asperities. Three asperities will be in contact for a rigid plate with high roughness as it takes three points of contact to define a plane. In the case of a short cantilever one or two asperities may be in contact and provide the majority of adhesion. Figure 14 shows the restoring force and adhesion force scaling of the smallest demonstrated cantilevers to date. Adhesion force and restoring force scale together until a gap of 5 nm, where adhesion does not scale as aggressively. This is due to asperity adhesion becoming dominant over rough surface adhesion. Depending on surface roughness of the contacts adhesion may be higher or lower than modeled. Direct measurement of the adhesion forces in a fabricated relay is possible and should be performed for an accurate force estimate [57]. If adhesion forces are lower than estimated, an aggressively scaled relay will be limited by a minimum viable air-gap.

Figure 14. Isotropic scaling of beam restoring force and adhesion force based on scaling the smallest demonstrated MEMS relay to date.

In addition to physical limits of flexure based devices, fabrication becomes significantly more difficult. Stress gradients typically become harder to control with thin layers, and therefore can cause higher actuation voltages than predicted or require different aspect ratio beams to avoid generating too much stress in the flexures [58]. Overall electrostatic cantilevers are not able to meet the aggressive scaling required to compete with CMOS. An alternate design for NEMS relays is required to continue scaling for area and actuation voltage.

#### 1.2.3 Non-Flexure Based MEMS Relays

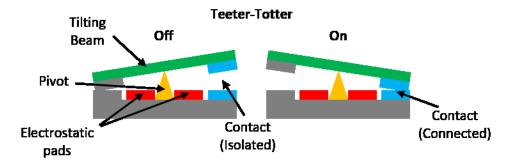

An alternate approach to scaling NEMS relays is to eliminate the use of a flexure. This can dramatically reduce the footprint of a device as the anchor is eliminated and materials are no longer limited by the stress generated by bending. Non-flexure based relays are also generally non-volatile in nature and can be used as memory. One example of an anchorless relay is developed by Cavendish Kinetics [59][60]. In this relay (Figure 15), a "teeter-totter" is built from a single rigid beam of metal and a pivot. The relay is actuated electrostatically by tilting the beam from one side to another. Van der Waals adhesion is used to hold the beam in place, making the relay non-volatile. Non-volatility is shown to be resilient to a wide temperature range (-150 °C to 300 °C) and high acceleration forces up to 20,000 g [59]. The Cavendish Kinetics relays are fabricated in a back end of the line CMOS process – making them cheap and easy to integrate with CMOS. One drawback is a relatively high contact resistance on the order of  $30 \text{ k}\Omega$ .

Figure 15. Schematic of the Cavendish Kinetics "teeter-totter" non-volatile relay. A rigid beam pivots to connect and disconnect a pair of contacts.

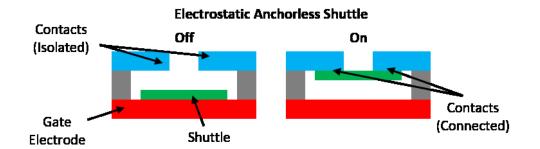

Another promising design to address the scalability of NEMS relays is the proposed Shuttle Nanoelectromechanical Nonvolatile Memory [61]. In this design (Figure 16) a free floating plate of metal, called the shuttle, is shifted within a cavity by electrostatic forces. The shuttle has two states, up and down, where the shuttle is connecting a set of contacts or sitting on the gate. Van der Waals adhesion holds the shuttle in place, making the device non-volatile. Electrostatic bias is generated by applying a potential between the gate electrode and the drain and source electrodes. One notable problem with this design is electrostatic instability of the shuttle. The free floating shuttle transfers charge as it travels from one state to the other. Upon contact with the new electrodes, charge is transferred, and the shuttle is now attracted to the opposite state. If adequate actuation voltage is applied to overcome adhesion forces, the shuttle will oscillate between the two states. This oscillation requires the relay to use pulsed actuation. The actuation pulse must be precisely timed to avoid the shuttle bouncing back to its original state [62]. Additionally tilting of the shuttle during actuation can cause shorting between the source or drain and the gate electrode [63]. The high scalability of the electrostatic shuttle relay [64] makes it a promising device towards making CMOS competitive NEMS relays. Although fabricated, the device does not have published results demonstrating switching.

Figure 16. Schematic of the electrostatic shuttle relay. The shuttle is held in place by Van der Waals adhesion and is moved by electrostatic attraction.

#### 1.3 Pulse Activated Piezo Shuttle Relay (PAPS)

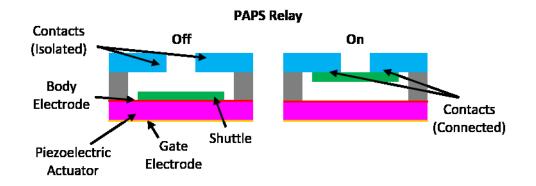

An advanced implementation of the electrostatic shuttle relay, called the pulse activated piezo switch (PAPS), was developed to address the challenges associated with the electrostatic only actuation [65][66]. The PAPS (Figure 17) differs by adding a piezoelectric actuator to the electrostatically actuated shuttle relay. The PAPS relay consist of three main components: the actuator, shuttle, and contacts for

the drain and source. The PAPS is a 4 terminal device, different from the 3 terminal electrostatic shuttle relay. The addition of the electrostatic actuator is controlled by the body and gate terminals. The actuator expands or contracts when voltage is applied to the gate. Rapid expansion of the actuator launches and releases the shuttle through an acoustic pulse. Additionally, a body bias can be applied through electrostatic forces, similar to the electrostatic shuttle relay. These electrostatic forces can reduce the required piezoelectric actuation pulse. Analysis for the PAPS showed device performance was only dependent on layer thickness, preventing the design from suffering from the same scalability limits as the flexure based designs.

Figure 17. Schematic of the pulse activated piezo switch. A piezoelectric actuator is used to break surface adhesion and transfer a free floating shuttle between the actuator and the contacts.

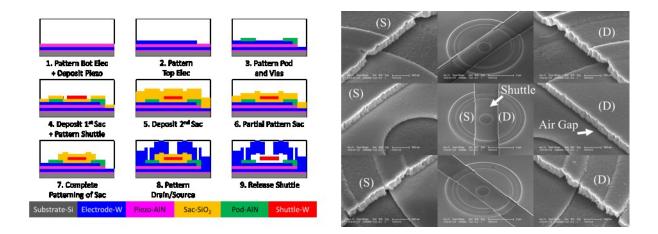

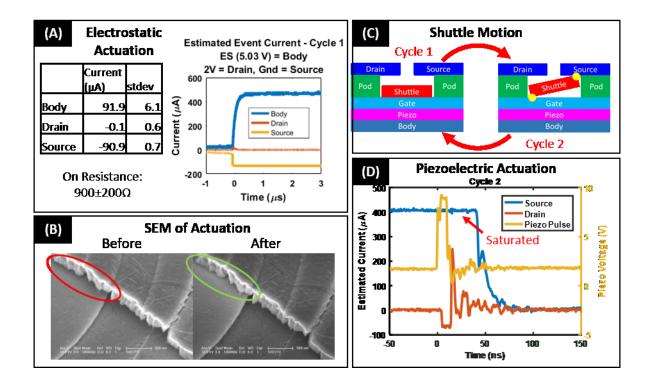

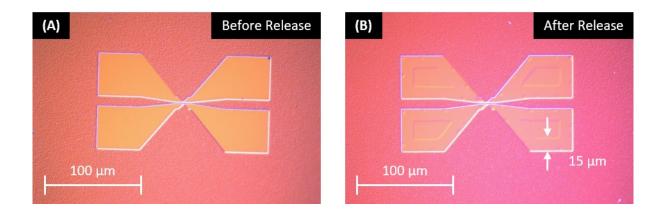

The PAPS device is fabricated in a nine step process (Figure 18) and tested under both electrostatic and piezoelectric actuation. Key fabrication difficulties are associated with creating and maintaining the narrow air gap. The fabricated shuttle is 100 nm of platinum surrounded by 75 nm of sacrificial material. The narrow gaps and long etch distances make release of the shuttles difficult. Additionally the thin shuttle requires significant tuning of stress gradient to avoid the shuttle warping and shorting the contacts after release. A summary of electrostatic and piezoelectric testing is shown in Figure 19. Electrostatic only actuation is demonstrated to switch a PAPS relay between two states, with motion confirmed by SEM. This switching is based on tilting of the shuttle, causing a short between the drain or source and the body electrodes. This instability is likely caused by varied adhesion along the actuator. The electrostatic actuation forces grow stronger as the shuttle approaches the other side, so if the shuttle begins to tilt, the tilting will be accelerated. The addition of the piezoelectric actuator can help alleviate this problem by supply additional energy to the shuttle where it touches the actuator, but piezoelectric testing still exhibits the tilting phenomenon.

Figure 18. Fabrication of the PAPS relay. The relay is fabricated in 9 steps. SEM images show a fabricated and released PAPS relay from different angles. S and D represent the source and drain contacts.

Figure 19. Testing summary for the PAPS relay highlighting (a) electrostatic only switching, (b) SEM images of shuttle motion, (c) schematics of shuttle motion, and (d) Piezoelectric actuation with electrostatic bias.

The PAPS device showed promise as a highly scalable NEMS relay but was unable to demonstrate reliable or predictable switching. An iteration of the PAPS device would require elimination of the tilting instability in the shuttle. One alternative to the shuttle design would be to directly open and close the air gap with vertical expansion of the actuator. The piezoelectric actuator of the PAPS, which expands in the vertical direction, is unable to generate the strain required to directly close the air gap. An alternative actuation material, capable of expanding and contracting enough to open and close the air gap directly, would be required for this iteration of the PAPS device.

## 1.4 Thesis Outline

This thesis will discuss the concept, design, fabrication, and testing of a novel iteration of the PAPS device, where the expansion of GeTe is used to directly actuate the air gap of a relay. This novel relay, the Phase Change NEMS Relay (PCNR) is a non-volatile device that addresses the limited scalability of traditional NEMS relays.

Chapter 2 will introduce the phase change NEMS relay concept. The operating principle of the relay will be described, including the theory on GeTe and other phase change materials. The modeling process will be described in detail, ranging from a 1D analytical model to varied COMSOL finite element models. Additionally, a scaling analysis will be presented to motivate an aggressively scaled PCNR. Scaling analysis will be used to predict the minimum dimensions and actuation metrics of a CMOS scale device for future iterations of the PCNR.

Chapter 3 will describe the fabrication process development for the PCNR. Key challenging fabrication steps will be described in depth. In particular, considerations for a useable GeTe film will be described, including ensuring proper composition, low roughness, and smooth sidewalls. Other features to be described include defect free deposition of an encapsulation layer and the formation of a narrow 20 nm air gap.

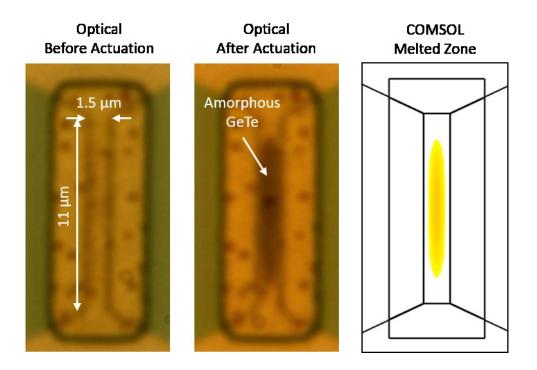

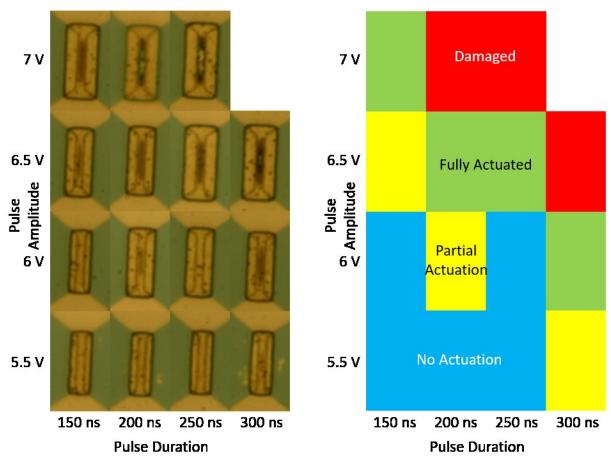

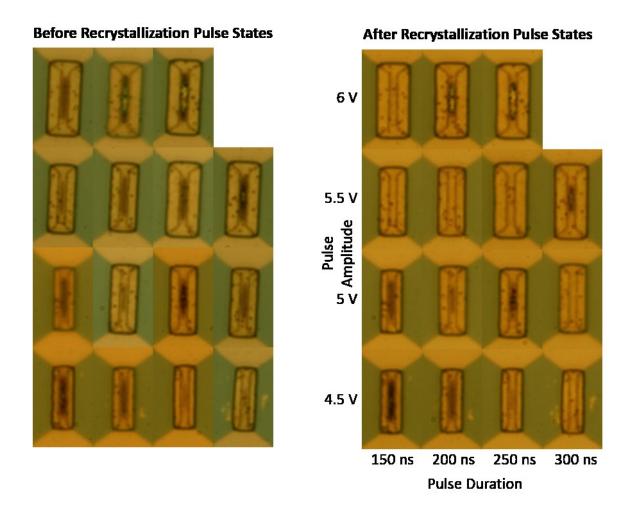

Chapter 4 will describe the testing of a phase change actuator. Optical measurements will be used to determine the presence of amorphous GeTe after actuation. Additionally, optical measurements will be used to rapidly test a range of actuators to determine the optimal actuation and recrystallization pulse. Finally, the actuator will be measured by AFM to determine the expansion and set the required air gap for full PCNR fabrication.

Chapter 5 will describe testing the fully fabricated PCNR. Testing will highlight key performance metrics of the PCNR including actuation voltage, actuation time, on resistance, non-volatility, reliability,

recrystallization voltage, recrystallization time, and leakage. Residual contamination in the air-gap will be characterized by TEM. Finally, the COMSOL model will be compared to the fabricated PCNR devices.

Chapter 6 will summarize the work of this thesis and state key contributions. Future work on the PCNR will be described including possible alternate materials for fabrication and an alternative geometry to improve the performance of an aggressively scaled PCNR.

# 2 Phase Change NEMS Relay (PCNR) Concept Design and Modeling

### 2.1 Abstract

The phase change NEMS relay (PCNR) is introduced as an alternative non-volatile relay that addresses the limited scalability of traditional mechanical relay designs while maintaining the high on-off ratio of mechanical contacts. The PCNR is built around the volumetric change observed in chalcogenide glass phase change materials when shifting between amorphous and crystalline states. These phase change materials support both amorphous and crystalline states at room temperature and are characterized by the rapid crystallization at elevated temperatures. Switching of the PCNR is performed by heating, melting, and quenching the phase change material into the expanded amorphous state. Expansion of the phase change material connects metallic contacts, leading to low on-state resistance. Turning the PCNR off is performed by heating, but not melting the phase change material to promote rapid crystallization into the contracted crystalline state. Contraction of the phase change material separates the metallic contacts, leading to a well isolated relay. GeTe is determined to be the best candidate phase change material for use in the PCNR due to its large volumetric expansion (10 %), higher temperature tolerance (amorphous for greater than 10 years at 125 °C), and rapid crystallization (less than 60 ns).

PCNR devices are modeled with both a 1D analytical model and a full COMSOL finite element analysis model. Electrical and thermal physics are combined to determine switching pulse requirements for a range of scaled geometries. Additionally, 2D COMSOL models of the phase change material expansion show the effects of cap thickness and melted PCM width. Scaling trends are fit to both the analytical and COMSOL models. Analytical models do not match the full COMSOL simulation, however lateral heat flow provides an explanation for analytical model deviation. Models predict an aggressively scaled relay with a 5 nm x 20 nm heater and a 2 nm air-gap is capable of switching at only 0.52 V with a quench time of 1.8 ns and a total switching energy of 1.8 pj.

## 2.2 Operating Concept

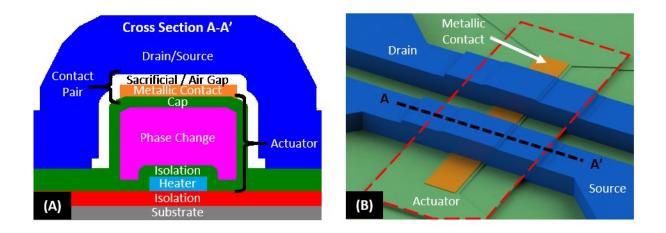

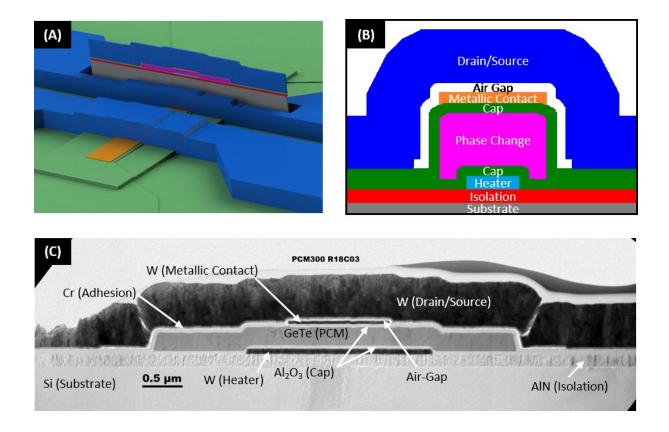

The phase change NEMS relay (PCNR) is built to address the limited scalability drawback of existing relay designs, while maintaining the high on-off ratio of mechanical contacts, with the added feature of non-volatility. The PCNR is based around the mechanical expansion of phase change material (PCM) when converting from a crystalline state to an amorphous state. The PCNR consists of two main components (Figure 20): a contact pair, and a GeTe based phase change actuator. The contact pair is formed by a metallic contact adhered to the top surface of the actuator and a suspended pair of drain/source contacts. The actuator is comprised of a resistive heater, and a layer of phase change material encapsulated in an insulating cap. The actuator expands and contracts depending on whether the GeTe is in the crystalline (smaller) or amorphous (larger) states.

Figure 20. Schematic representation of the phase change NEMS relay in (a) 2D cross section and (b) 3D isometric views. The actuator and contact pair are the two main components of the PCNR.

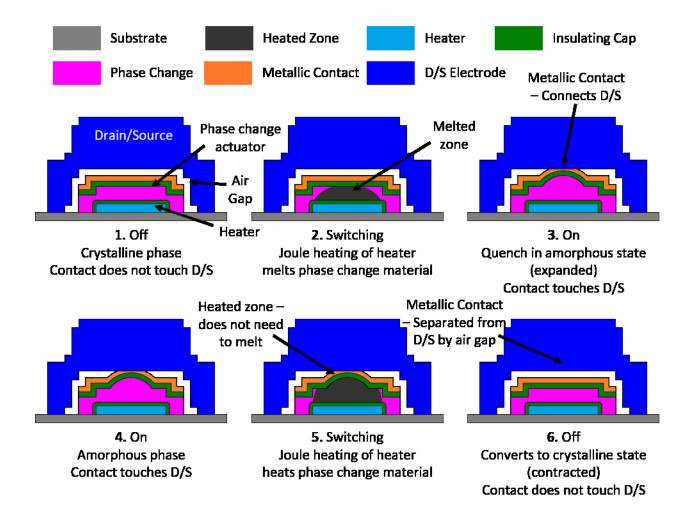

The PCNR operates following the process shown in Figure 21. The PCNR is initially fabricated in the off state where the drain and source electrodes are isolated from the metallic contact by an air gap. In the off state the phase change material is in the crystalline state. To switch to the on state, the heater is used to melt a portion of the phase change material, which is then quenched, converting the PCM to the larger amorphous state. The PCM is liquid for a short period before quenching. Quench time is important to ensure the PCM remains in the amorphous state. If cooled too slowly, the PCM will crystallize and the relay will not switch to the on state. The expansion of the actuator presses the metallic contact into the drain and source, connecting the drain and source, and thus turning the relay on.

A similar process is followed to switch the PCNR back to the off state, however the PCM is not melted. The heater is used to raise the PCM temperature without melting to promote rapid crystallization. The PCM remains solid throughout the process of switching the PCNR to the off state. The crystallization process contracts the actuator, separating the metallic contact from the drain and source, creating an air gap and turning the relay off.

Figure 21. Switching process for turning the phase change NEMS relay on and off.

# 2.3 Phase Change Materials

Phase change materials (PCM) are a broad category of materials encompassing any material that undergoes a change in atomic structure following an outside force [67]. Many of these phase changes encompass a large change in volume which can be harnessed in a mechanical actuator [67]. Shape memory alloys, a subset of PCMs, have been demonstrated as the active element in a number of cantilever based actuators [68][69]. These shape memory based actuators do not exhibit non-volatile states and must have power or heat applied to maintain an actuated state. Another subset of phase change materials is chalcogenide glass. Chalcogenide glasses are glasses containing elements from the oxygen family of elements: oxygen, sulfur, selenium, tellurium, and polonium. Common chalcogenide glass phase change such as GeTe and GST were originally developed for use in optical storage technologies [70][71], and later for resistivity based phase change memories [7]. These materials are characterized by room temperature stable amorphous and crystalline states, which can be used for non-volatile applications. When transitioning from one state to another, three material properties change: reflectivity, resistivity, and density. Optical storage takes advantage of the shift from reflective to opaque when switching from crystalline to amorphous states. PC-RAM takes advantage of the shift from conductive to resistive when switching from crystalline to amorphous. The change in volume has yet to be used in a non-volatile device as an actuator, although the change in stress has been used in FinFETs for stress enhancement [72][73]. When changing from crystalline to amorphous phase change materials expand by 5 - 10 % [74].

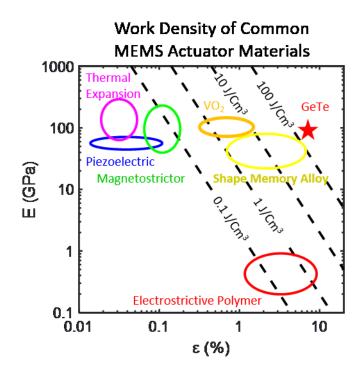

GeTe is a chalcogenide glass phase change material of particular interest for use in the PCNR. GeTe exhibits one of the largest changes in volume (10 %)[73] in any non-volatile PCM. Figure 22 compares intrinsic work density for GeTe and other materials commonly used in MEMS actuators. GeTe exhibits extremely high work density (200 J/cm<sup>3</sup>) with both higher strain and displacement than other comparable materials. GeTe has a higher crystallization temperature compared to GST (another common PCM) and is expected to maintain non-volatility for over 10 years at 125 °C [75][76]. Phase change materials like GeTe are also characterized by their fast crystallization time (less than 60 ns) [77]–[81]. The large volume change, elevated temperature non-volatility, and fast crystallization time make GeTe an ideal material for the actuator in the PCNR.

Figure 22. Comparison of work densities for common materials used in MEMS actuators. Adapted from [68].

## 2.4 Device Modeling

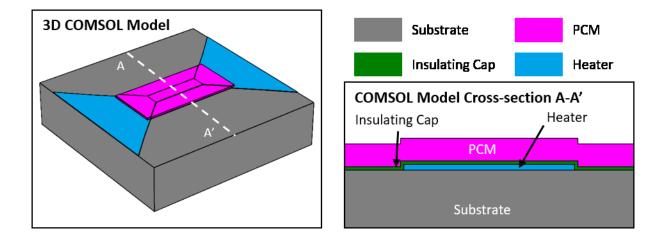

A 1D analytical model is used to quickly model operating voltages and scaling laws. Additionally, PCNR devices are modeled in COMSOL Multiphysics finite element analysis software to account for 3D effects and non-idealities in the geometry. Electrical and thermal effects are combined in one model to account for joule heating within the heater, while mechanical expansion and stress are separately modeled to optimize solving time.

# 2.4.1 Electrical Modeling

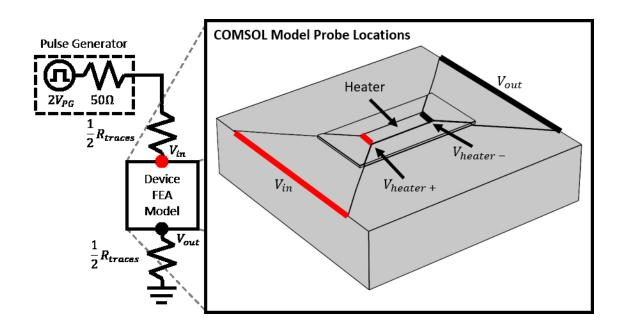

Electrical circuit modeling includes the pulse generator's 50  $\Omega$  internal impedance. Figure 23 shows the electrical circuit and probe locations for the simulated device. The probing pads are modeled in addition to the heater pads. Even though the pads and traces are substantially wider than the heater, the additional length leads to comparable resistances. Eventually, this additional resistance can be

eliminated in an advanced fabrication process. It is present in the currently fabricated devices and that is why it is included in the model. A thin isolation layer is conformally deposited over the heater layer to electrically separate the PCM from the heater. Capacitive coupling between the heater and PCM was found to be negligible, so only the heater is modeled for electric currents. Pulse generator voltage ( $V_{PG}$ ) is related to heater voltage ( $V_{heater}$ ) by:

$$V_{heater} = 2V_{PG} \left( \frac{R_{heater}}{50\Omega + R_{traces} + R_{Heater}} \right)$$

(13)

where  $R_{heater}$  is the heater resistance, and  $R_{traces}$  is the total resistance of the traces and probes connected to the heater.  $V_{PG}$  is the output voltage of the pulse generator assuming a 50  $\Omega$  load, so the high impedance output of the pulse generator is double the voltage. Thermal energy is generated by joule heating, and is modeled by:

$$P_{heater} = \frac{V_{heater}^2}{R_{heater}} \tag{14}$$

In the analytical model heat is assumed to be dissipated evenly over the heater as temperature and resistivity are assumed to be uniform over the heater.

*Figure 23. Heater actuation circuit model and probe locations in the COMSOL model.*

Change in resistance as a function of temperature must be included for an accurate estimate of energy dissipation in the heater. Heater resistance accounting for elevated temperatures is modeled as:

$$R_{heater} = R_{0heater} \left( 1 + \alpha_{heater} (T_{heater} - T_0) \right)$$

<sup>(15)</sup>

.....

where  $\alpha_{heater}$  is the temperature coefficient of resistivity (TCR) of the heater material,  $T_{heater}$  is the heater temperature, and  $T_0$  is the reference temperature for resistivity and TCR measurements.  $R_{0heater}$  is calculated by:

$$R_{0_{heater}} = \rho_{heater} \left( \frac{l_{heater}}{w_{heater} t_{heater}} \right) \tag{16}$$

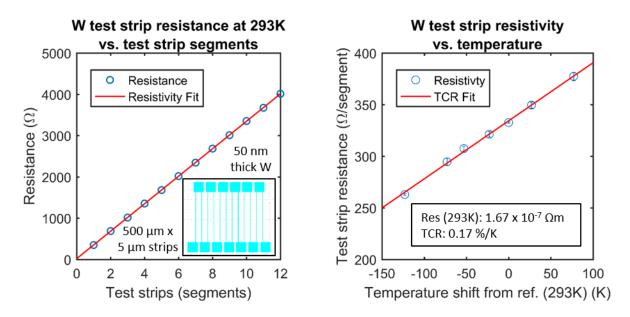

where  $\rho_{heater}$  is the resistivity of the heater material and  $l_{heater}$ ,  $w_{heater}$ , and  $t_{heater}$  are the length, width, and thickness respectively of the heater. Heater resistivity and TCR are measured for the tested fabricated device. Figure 24 shows resistivity measurements of the tungsten for a range of substrate temperatures. Resistance is measured as a function of trace length on a serpentine test structure and fit with a linear trend to account for probe contact resistance. Resistance was measured for temperatures ranging 170 K – 370 K in a Lakeshore Cryogenic probing station. TCR is estimated by fitting a linear trend to the resistance at each temperature. Resistivity and TCR referenced to 293 K are measured to be 1.67×10<sup>-7</sup>  $\Omega$ m and 0.17 %/K respectively. The TCR of tungsten has been shown to be constant up to the melting point [82], so measurements around the operating point were deemed unnecessary.

Figure 24. Resistivity and temperature coefficient of resistivity measurements for heater tungsten.

### 2.4.2 Thermal Modeling

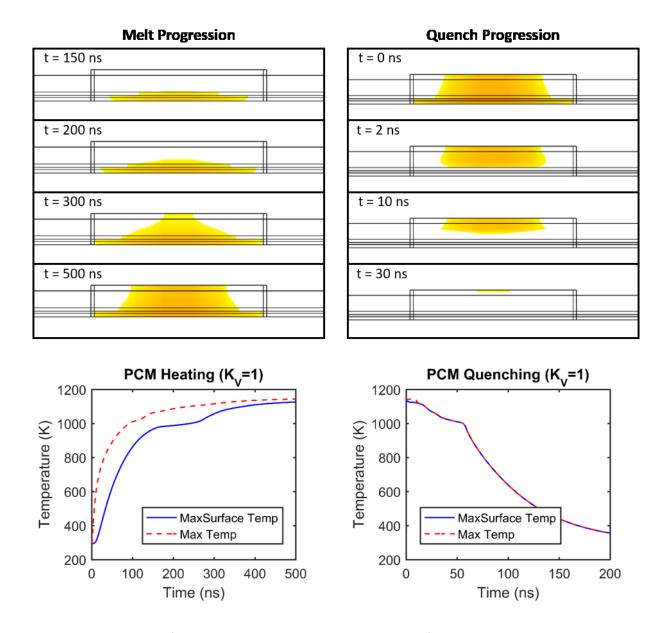

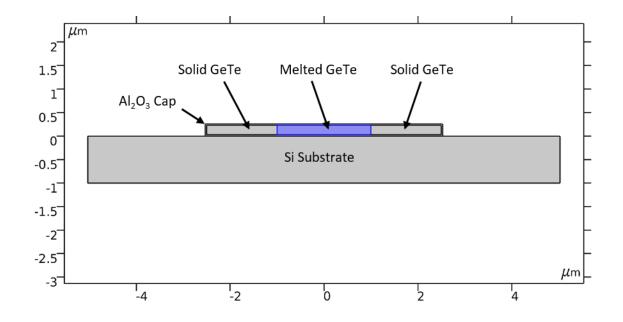

Thermal modeling is performed to characterize two key aspects of the actuator: temperature distribution and quench time within the PCM. Temperature distribution is important to control and limit the melted area of the PCM. Melted PCM must be rigidly encapsulated in the lateral dimensions to force the isotropic volume changes into only the vertical direction of the actuator. The melted PCM can be laterally encapsulated by solid PCM. Quench time is important to ensure the PCM does not crystalize before cooling to room temperature.

Thermal resistance is generated from two sources: intrinsic material thermal conductivity and thermal boundary resistance (TBR). For the 1D analytical model, resistance through a layer can be modeled as:

$$R_{th} = \frac{t_{layer}}{l_{layer} w_{layer} k_{th}} \tag{17}$$

where  $R_{th}$  is the thermal resistance of the layer,  $k_{th}$  is the thermal conductivity of the layer material, and  $l_{layer}$ ,  $w_{layer}$ , and  $t_{layer}$  are the length, width, and thickness of the layer respectively. Thermal boundary

resistance (TBR) also known as thermal interface resistance is modeled as a fixed thermal resistance per area at the interface between each layer. TBR can be quite substantial and even a dominant factor in thin materials with a large lattice mismatch [83]–[85]. Thermal resistance through a boundary between two layers ( $R_{TBR}$ ) can be modeled as:

$$R_{TBR} = \frac{TBR}{A_{laver}} \tag{18}$$

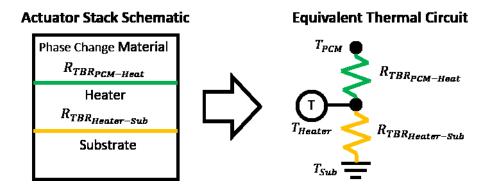

where  $A_{layer}$  is the lateral area of the layer and TBR is the thermal boundary resistance. Figure 25 shows the analytical thermal circuit model. The substrate is modeled as a fixed temperature heat sink, with TBRs separating the heater from the substrate and the PCM from the heater. Thermal resistance of the layers is neglected due to the high values of the TBRs.