## LEARNING ENHANCED DIAGNOSIS OF LOGIC CIRCUIT FAILURES

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

#### Soumya Mittal

B.Tech., Electronics and Communication Engineering, IIT Roorkee M.S., Electrical and Computer Engineering, Carnegie Mellon University

Carnegie Mellon University Pittsburgh, PA May, 2020

### Acknowledgements

I would like to thank my advisor, Professor Shawn Blanton, for his continuous support, constant motivation and endless patience over the years. I am extremely grateful for his continued invaluable insights in my research. He is the epitome of an exceptional mentor. His meticulosity, perspicacity, and strive for excellence and success have helped me to grow, both personally and professionally.

I would like to thank Professor Andrzej Strojwas, Professor Diana Marculescu, Dr. Enamul Amyeen, and Dr. Yan Pan for serving on my doctoral dissertation committee, and providing excellent feedback and constructive criticism on my work.

I am grateful to have learned a lot from my supervisors, John Carulli and Yan, during my internship at GlobalFoundries, and Enamul and Dr. Srikanth Venkat Raman, during my internship at Intel. I would also like to thank my former coworkers at GlobalFoundries and Intel for their help and support.

I would like to express my gratitude towards Prof. Xin Li for giving me an opportunity to work with him during my internship at Carnegie Mellon University (prior to PhD) and inspiring me to pursue research.

I would like to acknowledge my friends, and past and present ACTL (Advanced Chip Test Laboratory) colleagues for interesting discussions (research or otherwise) and furthering my academic development.

I would like to recognize the National Science Foundation (NSF), the Semiconductor

Research Corporation (SRC), and the Neil and Jo Bushnell Fellowship in Engineering for their financial support.

Most importantly, none of this would have been possible without the unwavering love, dedication, encouragement and sacrifice of my parents, Dr. Rajesh and Nandini Mittal, and my sister, Pavni Mittal; thank you for believing in me. I am also grateful for the love and support of my brother-in-law, Vibhu Gupta.

### Abstract

As semiconductor manufacturing progresses to smaller process nodes, it is becoming increasingly difficult to climb the yield learning curve rapidly. The rate of yield learning dictates the growth and success of the semiconductor industry, and must be accelerated to fulfill competitive time-to-market, time-to-money and time-to-volume requirements.

Software-based diagnosis plays a crucial role in yield learning. Diagnosis comprehends the test response of a failing circuit to determine the location, and sometimes, in addition, characterize the nature of a defect affecting the failing circuit. Besides identifying likely failure mechanisms and increasing the quality of chip testing, the feedback provided by diagnosis is used to select chips for physical failure analysis (PFA). PFA aims to visually examine a chip to characterize a defect, prevent similar defects in the future and, consequently, improve the design and manufacturing of a chip.

However, PFA is often destructive, time- and cost-intensive, and not always successful. Diagnosis, on the other hand, is non-invasive and time- and cost-effective; moreover, it assists PFA and guides yield learning. The advantages of diagnosis, coupled with the diminishing performance of PFA with advancing technology, make it an encouraging facilitator for rapid yield learning.

Therefore, the objective of diagnosis must be logic-level defect characterization to minimize (and ideally eliminate) the need for PFA, and accelerate yield learning. Logic characterization of a defect includes the derivation of its physical location and precise logic behavior.

In this dissertation, a comprehensive diagnosis methodology is developed to actualize the aforementioned objective.

The developed methodology comprises of three methods. LearnX/MD-LearnX is a physically-aware method that employs (a) the X-fault model to avert the elimination of a correct defect candidate and (b) machine learning to build a candidate-ranking model that learns the hidden correlations between the tester response and the defect candidates to pinpoint the correct candidate.

PADLOC, which stands for Physically-Aware Defect LOcalization and Characterization, improves the physical location of a back-end defect (i.e., a defect that affects one or more interconnects and resides outside a standard cell) returned by LearnX/MD-LearnX by partitioning the defective net into physical subnets and identifying the subnets that influence defect excitation. In addition, PADLOC deduces the precise impact of a defect on the circuit functionality by examining its surrounding circuitry.

NOIDA, which stands for <u>NO</u>ise-resistant <u>Intra-cell Diagnosis Approach</u>, pinpoints the location of a defect within a failing standard cell implicated by LearnX/MD-LearnX. In contrast to prior work that typically constructs/employs a fault dictionary, NOIDA ascertains the location as well as the behavior of a front-end defect (i.e., a defect that resides inside a standard cell) by monitoring the logical activity of its intra-cell neighborhood. Additionally, NOIDA is resistant to circuit-level noise that may originate from potentially inaccurate transistor-level simulation.

Results from numerous experiments reveal that our diagnosis methodology outperforms state-of-the-art commercial diagnosis. LearnX/MD-LearnX reports fewer defect candidates than commercial diagnosis for 69.4% silicon fail logs without losing accuracy. PADLOC implicates a smaller physical area for a defect for 47.2% silicon fail logs and attains at most 44X improvement. NOIDA reports an ideal diagnosis for 38.0% more front-end defects, when compared to leading-edge commercial diagnosis. In the presence of noise, NOIDA achieves

an ideal diagnosis 7.6X more often.

In summary, this dissertation endeavors to characterize a defect residing in a logic chip in terms of its precise physical location and logic behavior, which, consequently, most likely, enables rapid yield learning. The deployment of machine learning to pinpoint the correct candidate in LearnX/MD-LearnX, and the investigation of the neighborhood of a defect to determine its exact physical location and logic behavior in PADLOC and NOIDA are the novel components of this dissertation, and the reasons for its superiority over the state-of-the-art.

## Contents

| 1        | Intr | oducti | on         |                    |           |        |       |      |       |      |       |     |                      |     |     |    | 1  |

|----------|------|--------|------------|--------------------|-----------|--------|-------|------|-------|------|-------|-----|----------------------|-----|-----|----|----|

|          | 1.1  | Diagn  | osis Guide | ed Yield L         | earning   |        |       |      |       |      |       |     |                      |     |     | •  | 5  |

|          | 1.2  | Disser | tation Ove | erview .           |           |        |       |      |       |      |       |     |                      |     |     | •  | 13 |

|          | 1.3  | Disser | tation Org | ganization         |           |        |       |      |       |      |       |     |                      |     |     |    | 18 |

| <b>2</b> | Lea  | rnX: A | Determ     | $_{ m ninistic-S}$ | tatistica | al Sin | gle l | Defe | ect l | Diag | gnosi | s M | $\operatorname{eth}$ | ode | olc | gy | 20 |

|          | 2.1  | Prior  | Work       |                    |           |        |       |      |       |      |       |     |                      |     |     |    | 21 |

|          | 2.2  | Diagn  | osis Metho | odology .          |           |        |       |      |       |      |       |     |                      |     |     |    | 30 |

|          |      | 2.2.1  | Phase 1    |                    |           |        |       |      |       |      |       |     |                      |     |     |    | 33 |

|          |      | 2.2.2  | Supervise  | ed Machin          | ne Learni | ing .  |       |      |       |      |       |     |                      |     |     |    | 36 |

|          |      | 2.2.3  | Phase 2    |                    |           |        |       |      |       |      |       |     |                      |     |     | •  | 39 |

|          | 2.3  | Exper  | iments     |                    |           |        |       |      |       |      |       |     |                      |     |     | •  | 44 |

|          |      | 2.3.1  | Diagnost   | ic Metrics         | 3         |        |       |      |       |      |       |     |                      |     |     | •  | 44 |

|          |      | 2.3.2  | Simulation | on Experi          | ment      |        |       |      |       |      |       |     |                      |     |     |    | 45 |

|          |      |        | 2.3.2.1    | Phase 1            |           |        |       |      |       |      |       |     |                      |     |     |    | 48 |

|          |      |        | 2.3.2.2    | Phase 2            |           |        |       |      |       |      |       |     |                      |     |     |    | 53 |

|          |      |        | 2.3.2.3    | Results S          | Summary   | ·      |       |      |       |      |       |     |                      |     |     |    | 58 |

|          |      | 2.3.3  | Silicon E  | Experiment         | t         |        |       |      |       |      |       |     |                      |     |     |    | 60 |

|          |      |        | 2.3.3.1    | Setup .            |           |        |       |      |       |      |       |     |                      |     |     |    | 60 |

|          |      |        | 2 3 3 2    | Results            |           |        |       |      |       |      |       |     |                      |     |     |    | 61 |

| CONTENTED | •             |

|-----------|---------------|

| CONTENTS  | 1X            |

|           | <del></del> - |

|   | 2.4  | Conclu | usion                                                          | 65  |

|---|------|--------|----------------------------------------------------------------|-----|

| 3 | MD   | -Learn | X: A Deterministic-Statistical Multiple Defect Diagnosis Metho | d-  |

|   | olog | gу     |                                                                | 67  |

|   | 3.1  | Prior  | Work                                                           | 70  |

|   | 3.2  | Diagn  | osis Methodology                                               | 74  |

|   |      | 3.2.1  | Phase 1-3 steps                                                | 78  |

|   |      | 3.2.2  | Phase 1                                                        | 79  |

|   |      | 3.2.3  | Phase 2                                                        | 80  |

|   |      | 3.2.4  | Phase 3                                                        | 81  |

|   | 3.3  | Exper  | iments                                                         | 82  |

|   |      | 3.3.1  | Diagnostic Metrics                                             | 84  |

|   |      | 3.3.2  | Simulation Experiment                                          | 84  |

|   |      |        | 3.3.2.1 Results                                                | 85  |

|   |      |        | 3.3.2.2 Results Summary                                        | 94  |

|   |      | 3.3.3  | Silicon Experiment                                             | 97  |

|   |      |        | 3.3.3.1 Setup                                                  | 97  |

|   |      |        | 3.3.3.2 Results                                                | 97  |

|   | 3.4  | Conclu | usion                                                          | 99  |

|   |      |        |                                                                |     |

| 4 | PAI  | DLOC:  | Physically-Aware Defect Localization and Characterization      | 101 |

|   | 4.1  | Prior  | Work                                                           | 102 |

|   |      | 4.1.1  | Defect-based Approaches                                        | 103 |

|   |      | 4.1.2  | DIAGNOSIX                                                      | 108 |

|   | 4.2  | Diagn  | osis Methodology                                               | 112 |

|   |      | 4.2.1  | Neighborhood-based Net Segmentation and Segment Neighborhood   |     |

|   |      |        | Identification                                                 | 114 |

CONTENTS x

|   |                                               | 4.2.2                                                      | Segment-level Consistency Check              | 119                                                  |

|---|-----------------------------------------------|------------------------------------------------------------|----------------------------------------------|------------------------------------------------------|

|   | 4.3                                           | Exper                                                      | iments                                       | 120                                                  |

|   |                                               | 4.3.1                                                      | Diagnostic Metrics                           | 120                                                  |

|   |                                               | 4.3.2                                                      | Simulation Experiment                        | 122                                                  |

|   |                                               |                                                            | 4.3.2.1 Setup                                | 123                                                  |

|   |                                               |                                                            | 4.3.2.2 Comparison with LearnX               | 124                                                  |

|   |                                               |                                                            | 4.3.2.3 Comparison with Commercial Diagnosis | 138                                                  |

|   |                                               |                                                            | 4.3.2.4 Results Summary                      | 152                                                  |

|   |                                               | 4.3.3                                                      | Silicon Experiment                           | 155                                                  |

|   |                                               |                                                            | 4.3.3.1 Setup                                | 155                                                  |

|   |                                               |                                                            | 4.3.3.2 Results                              | 156                                                  |

|   | 4.4                                           | Conclu                                                     | usion                                        | 159                                                  |

|   |                                               |                                                            |                                              |                                                      |

| 5 | NO                                            | TDA · I                                                    | Noise-resistant Intra-cell Diagnosis         | 161                                                  |

| 5 |                                               |                                                            | 0                                            | 161                                                  |

| 5 | 5.1                                           | Motiv                                                      | ation                                        | 162                                                  |

| 5 | 5.1<br>5.2                                    | Motiva<br>Prior                                            | ation                                        | 162<br>167                                           |

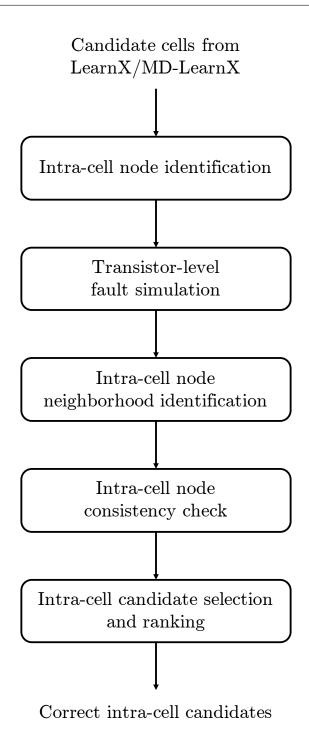

| 5 | 5.1                                           | Motiva<br>Prior                                            | ation                                        | 162<br>167<br>171                                    |

| 5 | 5.1<br>5.2                                    | Motiva<br>Prior                                            | ation                                        | 162<br>167<br>171                                    |

| 5 | 5.1<br>5.2                                    | Motive<br>Prior<br>Diagn                                   | ation                                        | 162<br>167<br>171                                    |

| 5 | 5.1<br>5.2                                    | Motive<br>Prior<br>Diagnet<br>5.3.1<br>5.3.2               | ation                                        | 162<br>167<br>171<br>172<br>174                      |

| 5 | 5.1<br>5.2                                    | Motive<br>Prior<br>Diagnet<br>5.3.1<br>5.3.2               | ation                                        | 162<br>167<br>171<br>172<br>174                      |

| 5 | 5.1<br>5.2                                    | Motive Prior Diagnet 5.3.1 5.3.2 5.3.3                     | ation                                        | 162<br>167<br>171<br>172<br>174<br>175               |

| 5 | 5.1<br>5.2                                    | Motive Prior Diagnet 5.3.1 5.3.2 5.3.3 5.3.4 5.3.5         | ation                                        | 162<br>167<br>171<br>172<br>174<br>175<br>176        |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Motive Prior Diagnet 5.3.1 5.3.2 5.3.3 5.3.4 5.3.5         | ation                                        | 162<br>167<br>171<br>172<br>174<br>175<br>176        |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Motive Prior Diagnates 5.3.1 5.3.2 5.3.3 5.3.4 5.3.5 Exper | ation                                        | 162<br>167<br>171<br>172<br>174<br>175<br>176<br>177 |

| CONTENTE | •   |

|----------|-----|

| CONTENTS | X   |

| COTTENTS | 11. |

|          |       | 5.4.4  | Results: Front-end ATPG                                     | 196 |

|----------|-------|--------|-------------------------------------------------------------|-----|

|          |       | 5.4.5  | Results: Circuit-level Noise                                | 203 |

|          | 5.5   | Conclu | usion                                                       | 210 |

| 6        | Cor   | clusio | ns                                                          | 213 |

|          | 6.1   | Disser | tation Contributions                                        | 215 |

|          |       | 6.1.1  | LearnX/MD-LearnX                                            | 215 |

|          |       | 6.1.2  | PADLOC                                                      | 217 |

|          |       | 6.1.3  | NOIDA                                                       | 218 |

|          | 6.2   | Future | e Work                                                      | 220 |

|          |       | 6.2.1  | Delay Defects                                               | 220 |

|          |       | 6.2.2  | Design Features in LearnX/MD-LearnX                         | 221 |

|          |       | 6.2.3  | Machine Learning for Ranking PADLOC and NOIDA Candidates $$ | 222 |

| ${f Bi}$ | bliog | graphy |                                                             | 223 |

# List of Figures

| 1.1  | A simplified flow depicting the role of manufacturing test and diagnosis in  |    |

|------|------------------------------------------------------------------------------|----|

|      | guiding yield analysis, learning and monitoring.                             | 6  |

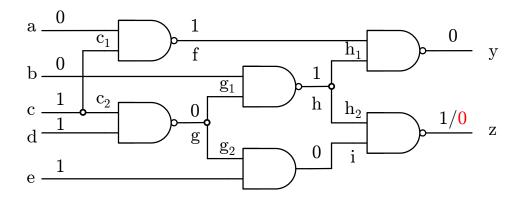

| 2.1  | Example to illustrate back-coning and path tracing                           | 23 |

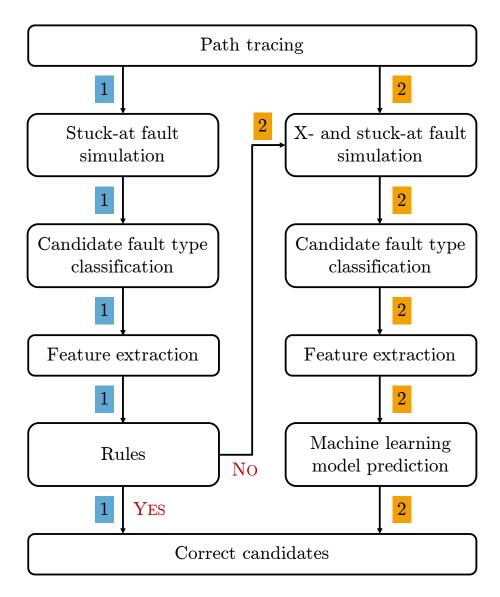

| 2.2  | An overview of the proposed diagnosis methodology, LearnX. The sequence      |    |

|      | of steps in each phase are marked with a different color                     | 32 |

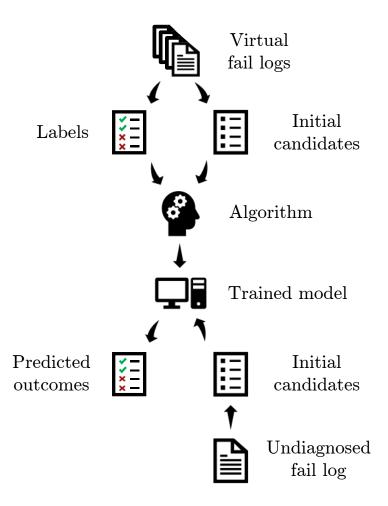

| 2.3  | An overview of how supervised machine learning is applied in LearnX          | 38 |

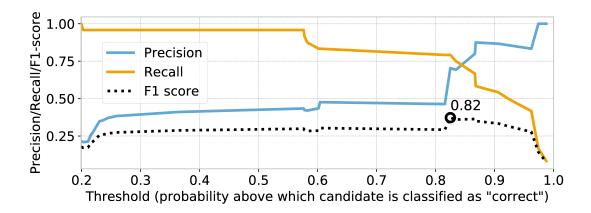

| 2.4  | Selecting the optimum decision threshold that maximizes the harmonic aver-   |    |

|      | age between precision and recall (known as the F1-score)                     | 40 |

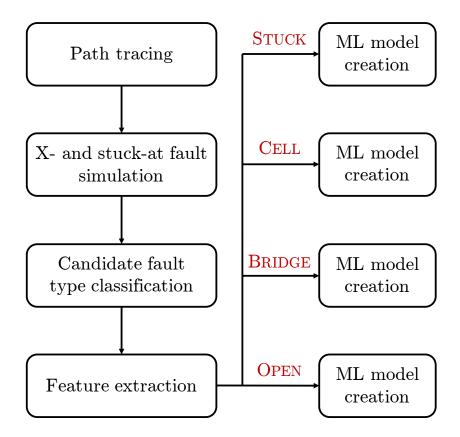

| 2.5  | Overview of the flow employed for creating a machine learning model for each |    |

|      | fault type                                                                   | 43 |

| 2.6  | Resolution distribution attained by LearnX (Phase 1) for the design "AES".   | 49 |

| 2.7  | Resolution distribution attained by LearnX (Phase 1) for the design "DES".   | 49 |

| 2.8  | Resolution distribution attained by LearnX (Phase 1) for the design "L2B".   | 50 |

| 2.9  | Resolution distribution attained by LearnX (Phase 1) for the design "B18"    | 50 |

| 2.10 | Resolution distribution attained by LearnX (Phase 2) for the design "AES".   | 54 |

| 2.11 | Resolution distribution attained by LearnX (Phase 2) for the design "DES".   | 54 |

| 2.12 | Resolution distribution attained by LearnX (Phase 2) for the design "L2B".   | 55 |

| 2.13 | Resolution distribution attained by LearnX (Phase 2) for the design "B18"    | 55 |

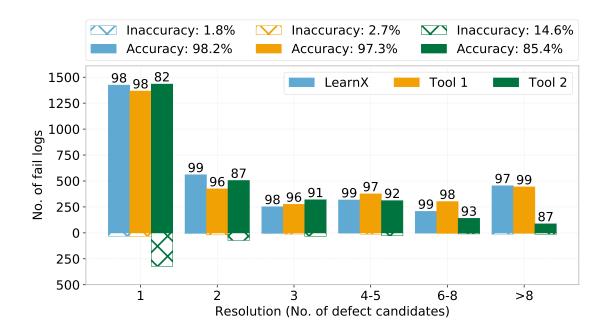

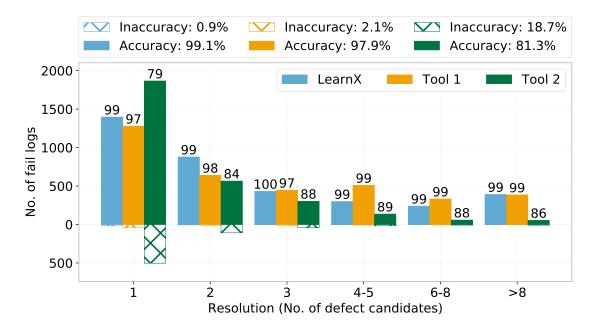

| 2.14 | Accuracy achieved by LearnX and commercial diagnosis                         | 59 |

| 2.15 | Home run achieved by LearnX and commercial diagnosis                         | 59 |

LIST OF FIGURES xiii

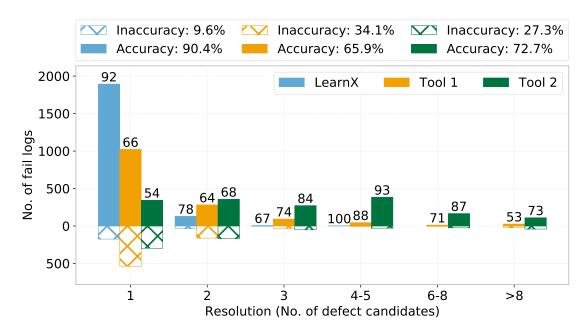

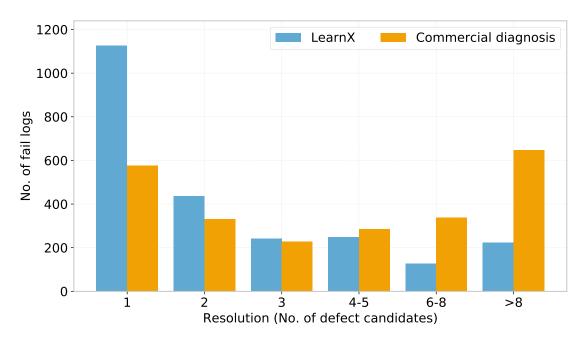

| 2.16 | Resolution distribution attained by LearnX for 2,400 silicon fail logs           | 62 |

|------|----------------------------------------------------------------------------------|----|

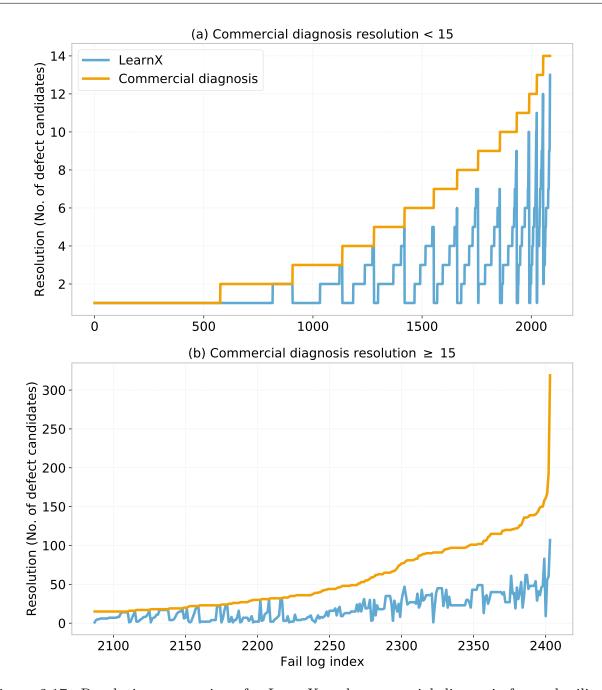

| 2.17 | Resolution comparison for LearnX and commercial diagnosis for each silicon       |    |

|      | fail log. The fail logs are divided in two groups based on commercial diagnosis  |    |

|      | resolution for an aesthetic reason: (a) fail logs with commercial diagnosis res- |    |

|      | olution of less than 15, and (b) fail logs with commercial diagnosis resolution  |    |

|      | of at least 15                                                                   | 63 |

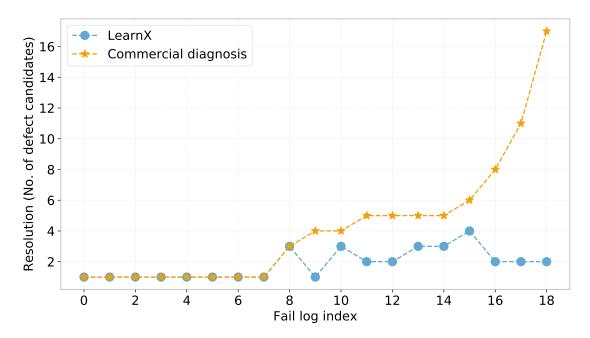

| 2.18 | Resolution comparison for LearnX and commercial diagnosis for each failing       |    |

|      | chip that is PFA'ed and suspected to have a single defect                        | 64 |

| 3.1  | Example to illustrate (a) error masking and (b) unmasking                        | 70 |

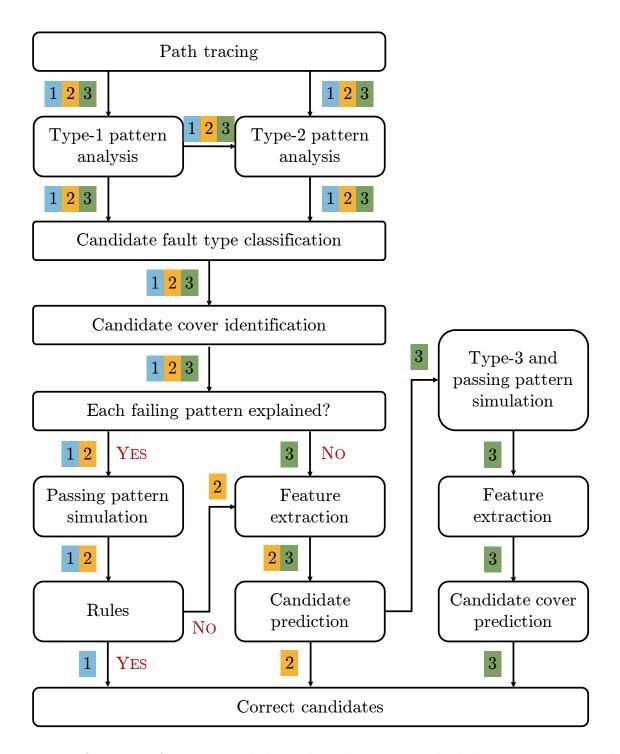

| 3.2  | Overview of the proposed three-phase diagnosis methodology, MD-LearnX.           |    |

|      | The sequence of steps in each phase are marked with a different color            | 76 |

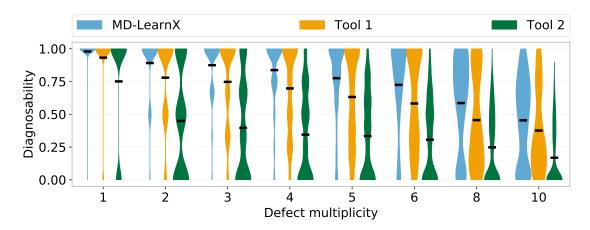

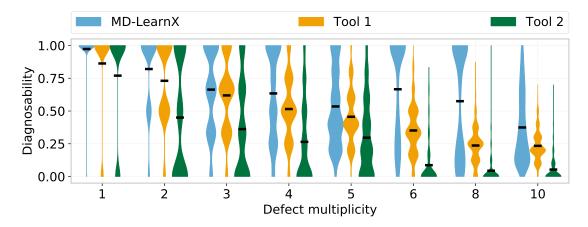

| 3.3  | Probability density distribution of diagnosability for the design "AES"          | 87 |

| 3.4  | Probability density distribution of diagnosability for the design "DES"          | 88 |

| 3.5  | Probability density distribution of diagnosability for the design "L2B"          | 88 |

| 3.6  | Probability density distribution of diagnosability for the design "B18"          | 88 |

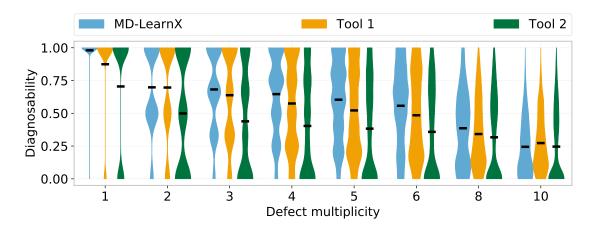

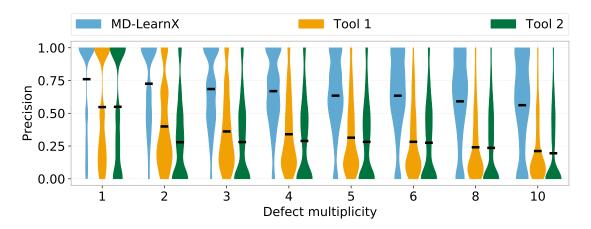

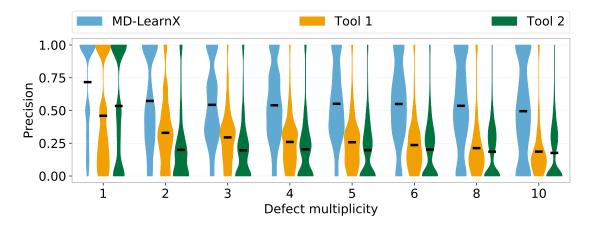

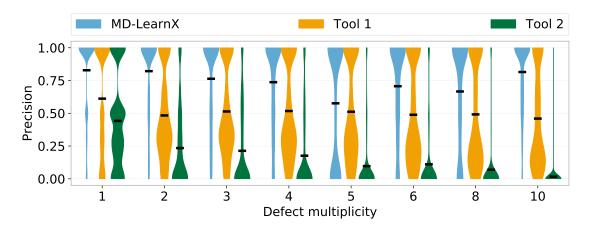

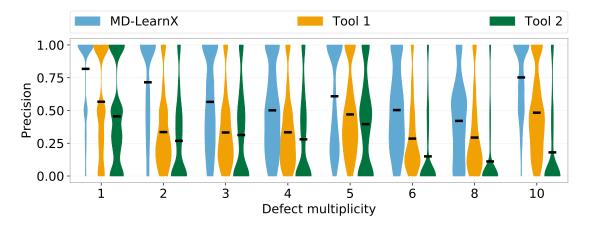

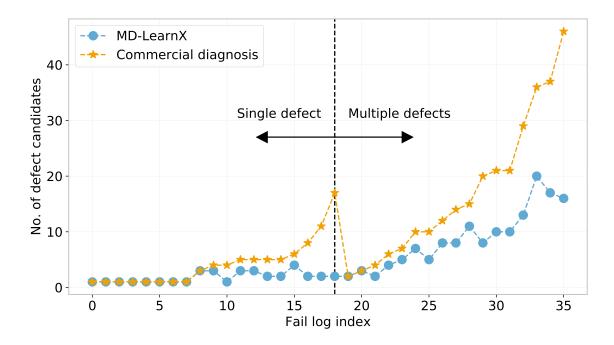

| 3.7  | Probability density distribution of precision for the design "AES"               | 90 |

| 3.8  | Probability density distribution of precision for the design "DES"               | 90 |

| 3.9  | Probability density distribution of precision for the design "L2B"               | 91 |

| 3.10 | Probability density distribution of precision for the design "B18"               | 91 |

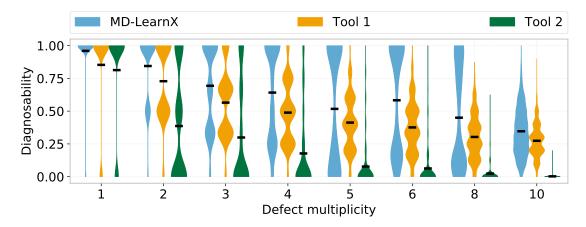

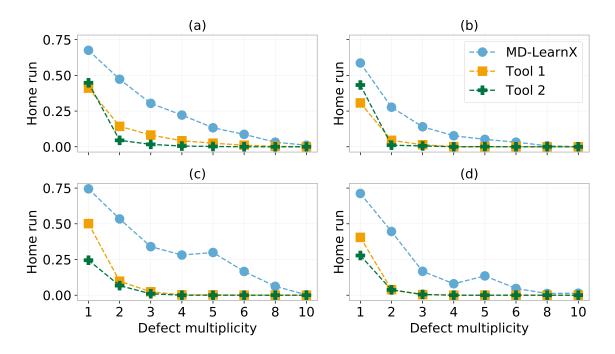

| 3.11 | Home run of MD-LearnX compared with commercial diagnosis for (a) AES,            |    |

|      | (b) DES, (c) L2B, and (d) B18                                                    | 92 |

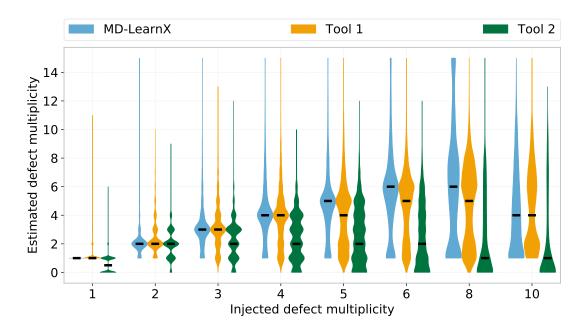

| 3.12 | Distribution of defect multiplicity estimated by MD-LearnX and commercial        |    |

|      | diagnosis.                                                                       | 93 |

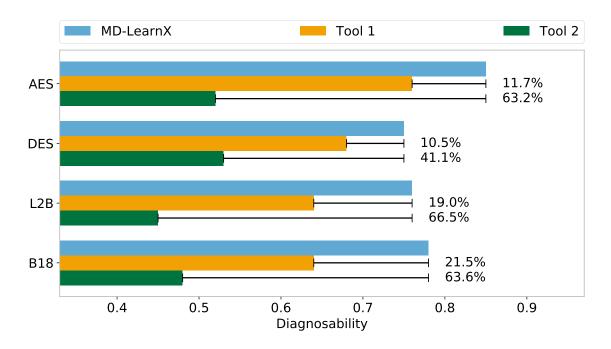

| 3.13 | Diagnosability achieved by MD-LearnX and commercial diagnosis                    | 95 |

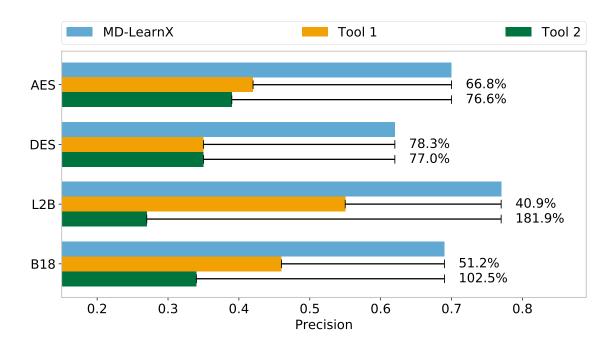

| 3.14 | Precision achieved by MD-LearnX and commercial diagnosis                         | 96 |

LIST OF FIGURES xiv

| 3.15 | Home run achieved by MD-LearnX and commercial diagnosis                          | 96  |

|------|----------------------------------------------------------------------------------|-----|

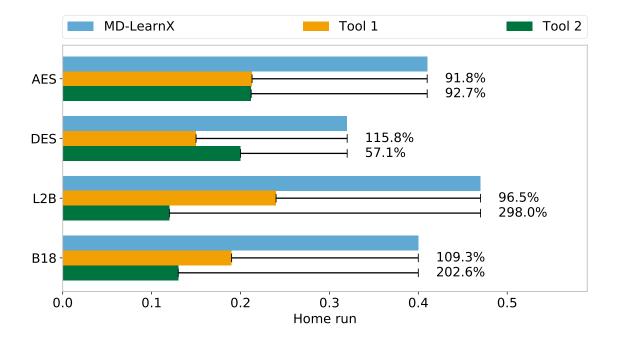

| 3.16 | Number of candidates returned by MD-LearnX and commercial diagnosis for          |     |

|      | 36 failing chips that are PFA'ed                                                 | 98  |

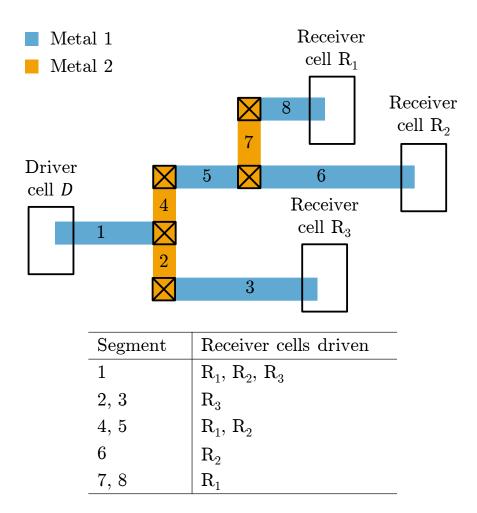

| 4.1  | Illustration of net partitioning into segments such that each segment drives a   |     |

|      | distinct set of receiver cells [147, 161]                                        | 105 |

| 4.2  | Net segmentation based on the topology of the net and its physical neighbors     |     |

|      | [149]                                                                            | 106 |

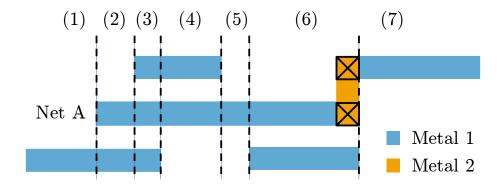

| 4.3  | Example illustrating the neighborhood identified by DIAGNOSIX for net ${\cal A}$ | 109 |

| 4.4  | Example showing how all neighbors of a net, as identified from DIAGNOSIX,        |     |

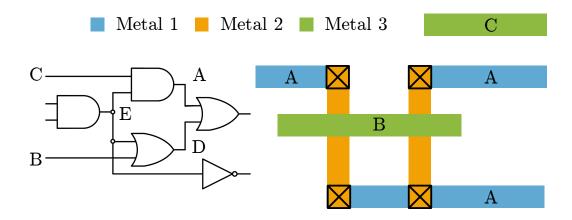

|      | are not relevant to excite a bridge defect                                       | 111 |

| 4.5  | Example showing how all neighbors of a net, as identified from DIAGNOSIX,        |     |

|      | are not relevant to excite a bridge defect                                       | 112 |

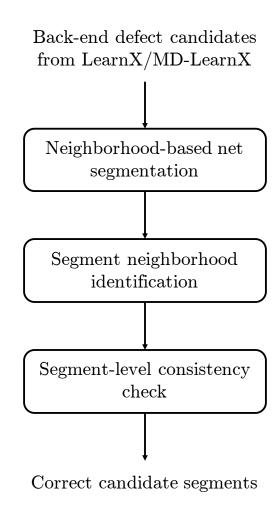

| 4.6  | An overview of the proposed back-end diagnosis methodology, PADLOC               | 114 |

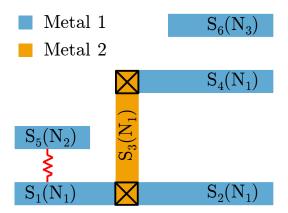

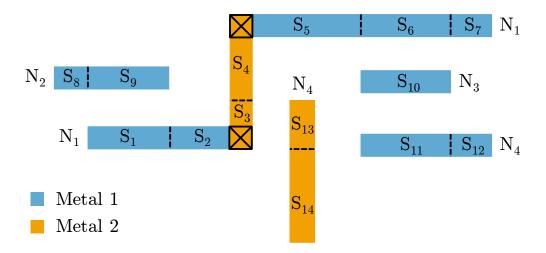

| 4.7  | Illustration of net partitioning into segments for localizing bridge defects     | 115 |

| 4.8  | Illustration of net partitioning into segments for localizing open defects       | 117 |

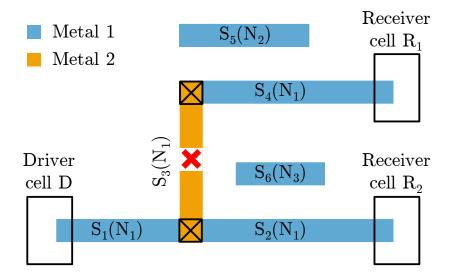

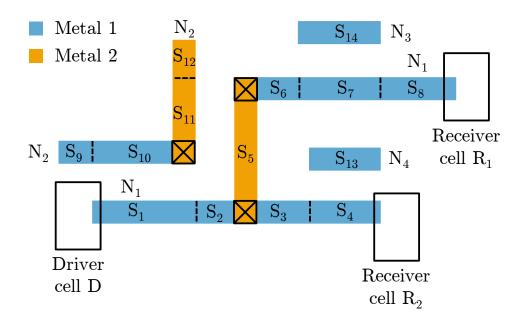

| 4.9  | An example defective circuit illustrating the identification of relevant logical |     |

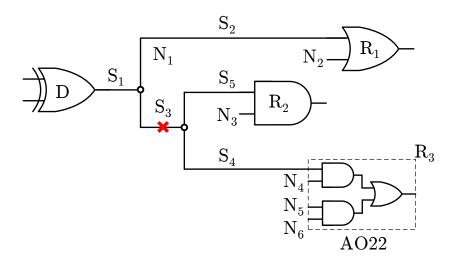

|      | neighbors                                                                        | 118 |

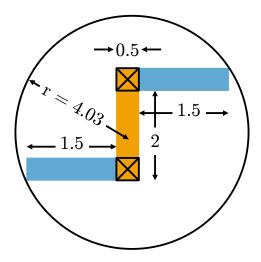

| 4.10 | A simple example illustrating the computation of two diagnostic metrics,         |     |

|      | bounding circle diameter and area union                                          | 122 |

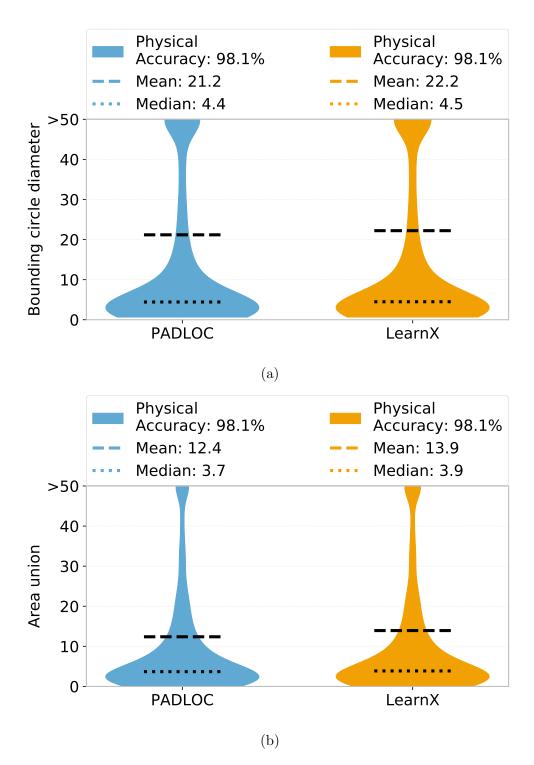

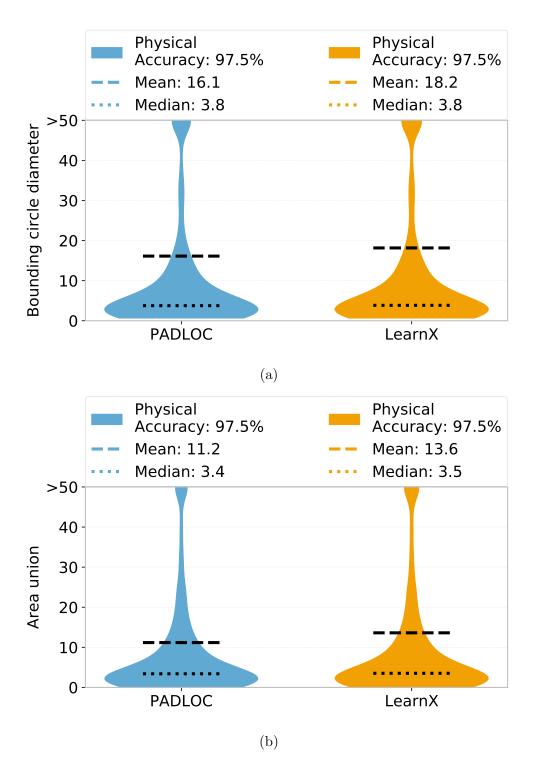

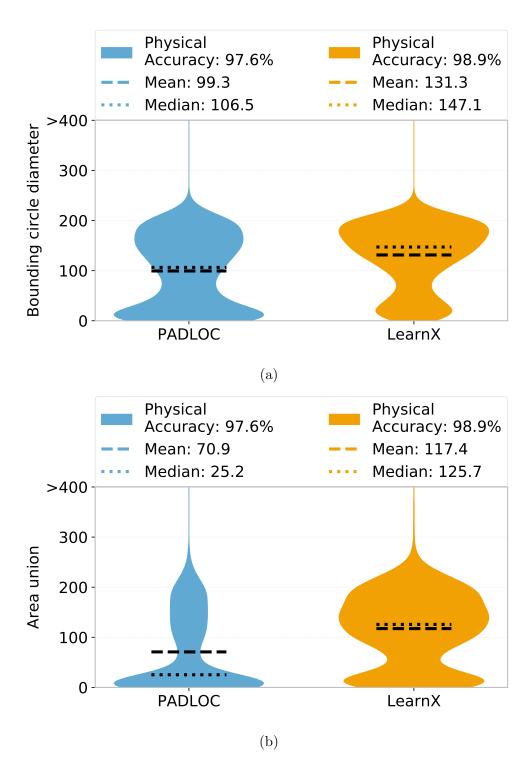

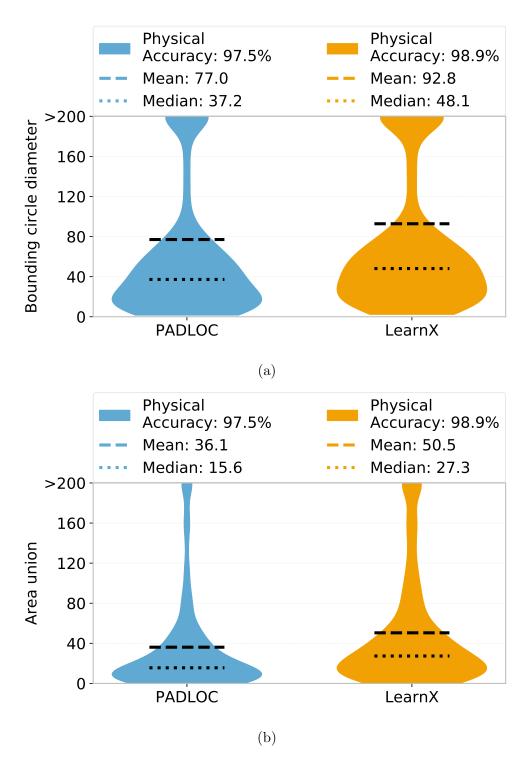

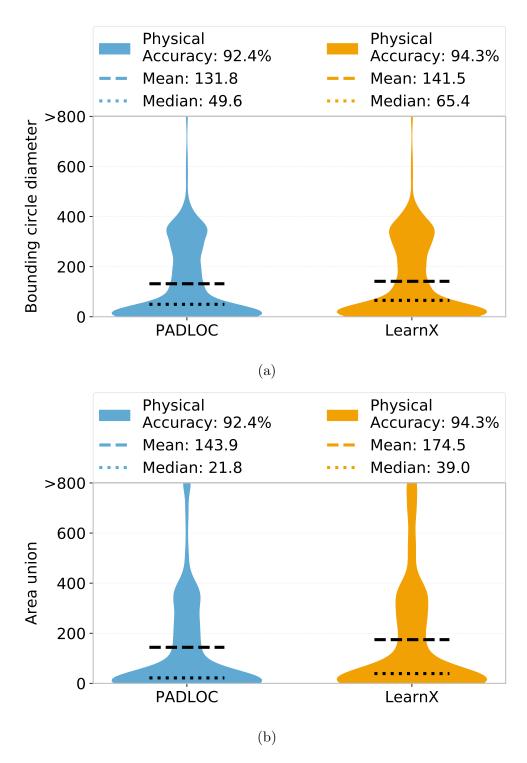

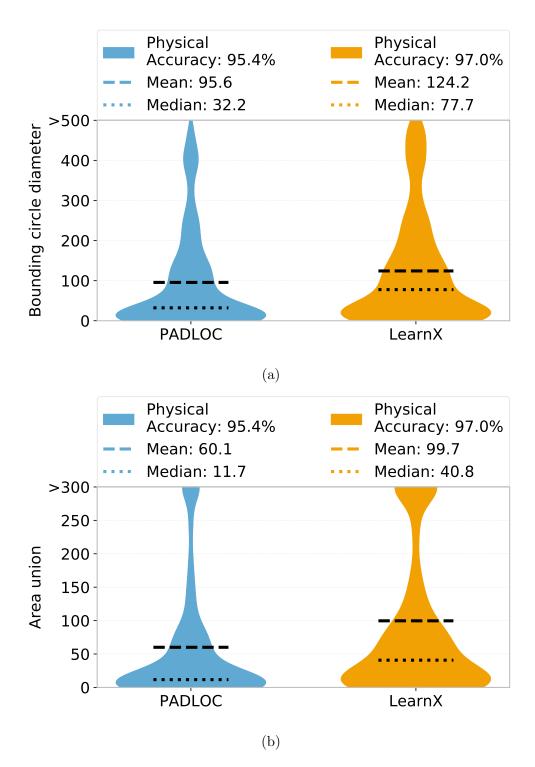

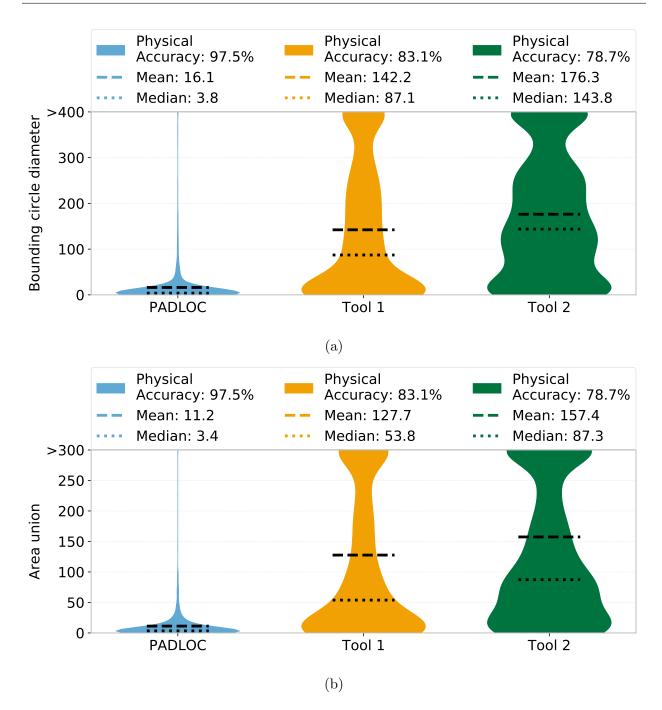

| 4.11 | Probability density distribution of (a) bounding circle diameter and (b) area    |     |

|      | union for the design "AES", when bridge defects are diagnosed by PADLOC          |     |

|      | and LearnX                                                                       | 130 |

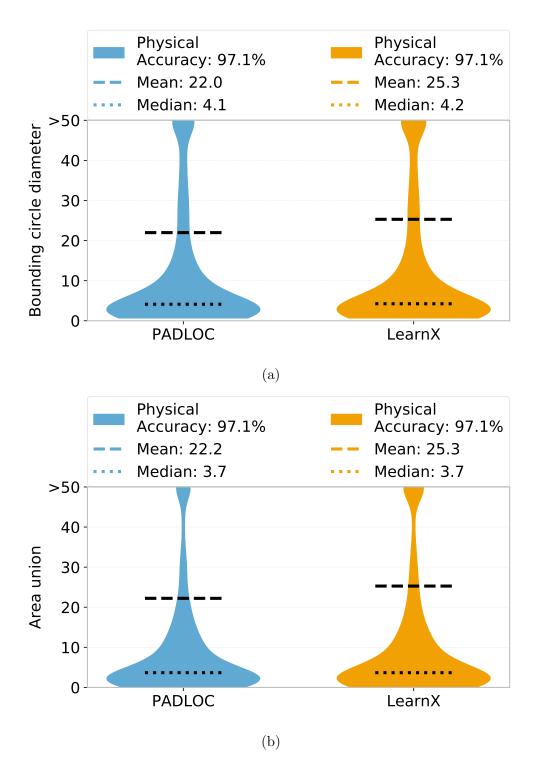

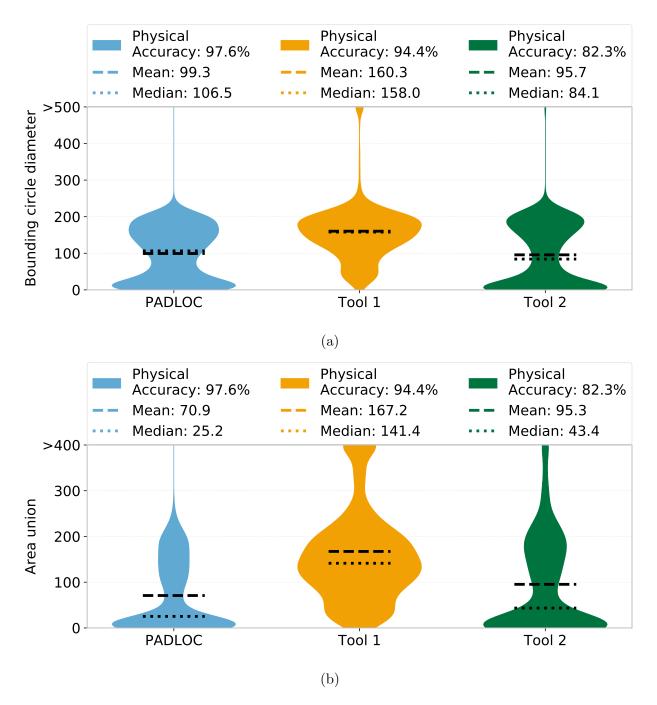

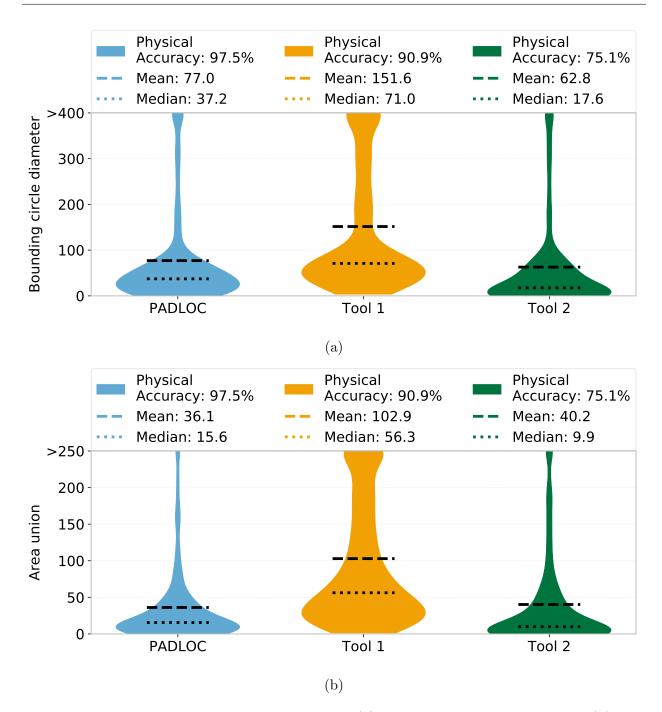

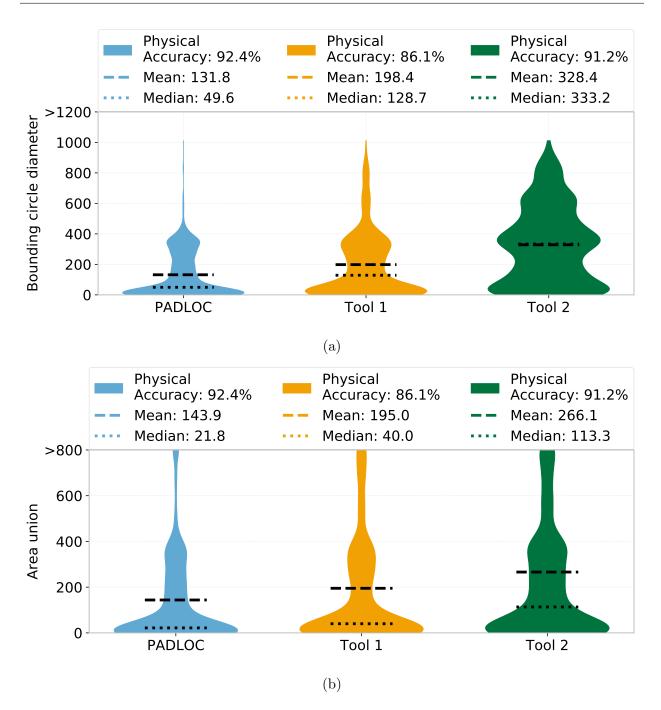

| 4.12 | Probability density distribution of (a) bounding circle diameter and (b) area    |     |

|      | union for the design "DES", when bridge defects are diagnosed by PADLOC          |     |

|      | and LearnX                                                                       | 131 |

LIST OF FIGURES xv

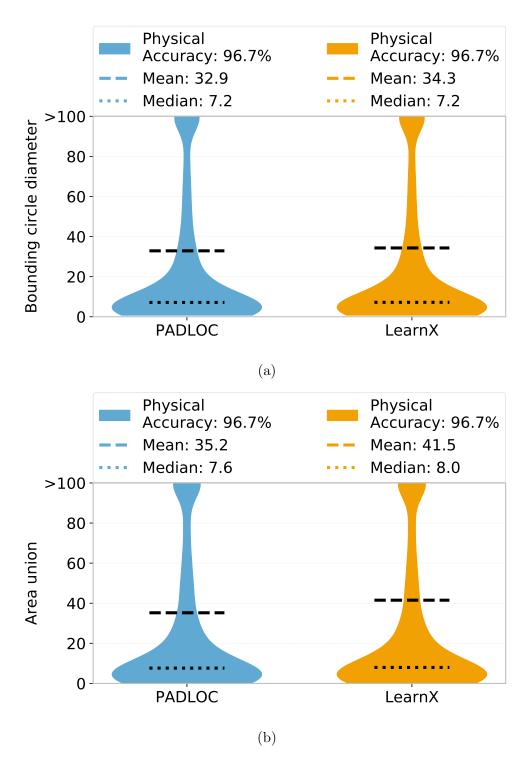

| 4.13 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|------|-------------------------------------------------------------------------------|-----|

|      | union for the design "L2B", when bridge defects are diagnosed by PADLOC       |     |

|      | and LearnX                                                                    | 132 |

| 4.14 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "B18", when bridge defects are diagnosed by PADLOC       |     |

|      | and LearnX                                                                    | 133 |

| 4.15 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "AES", when open defects are diagnosed by PADLOC         |     |

|      | and LearnX                                                                    | 134 |

| 4.16 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "DES", when open defects are diagnosed by PADLOC         |     |

|      | and LearnX                                                                    | 135 |

| 4.17 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "L2B", when open defects are diagnosed by PADLOC         |     |

|      | and LearnX                                                                    | 136 |

| 4.18 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "B18", when open defects are diagnosed by PADLOC         |     |

|      | and LearnX                                                                    | 137 |

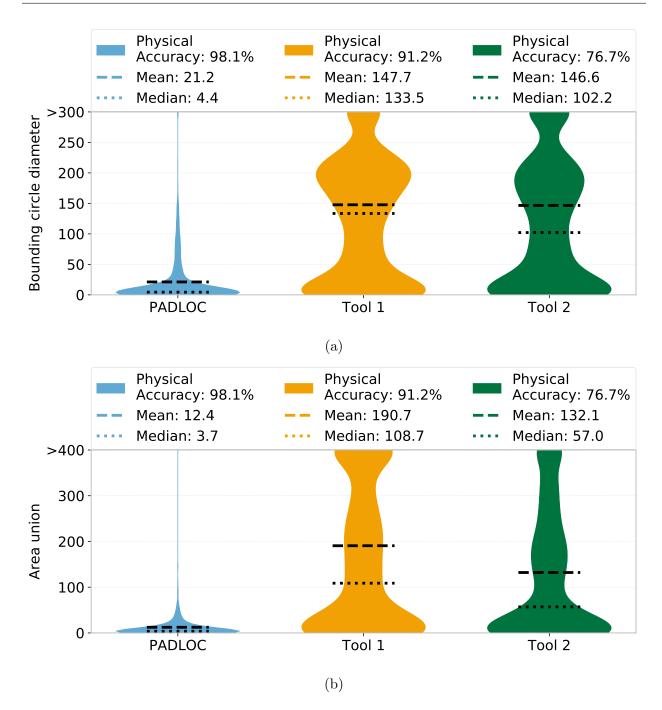

| 4.19 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "AES", when bridge defects are diagnosed by PADLOC       |     |

|      | and commercial diagnosis                                                      | 139 |

| 4.20 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "DES", when bridge defects are diagnosed by PADLOC       |     |

|      | and commercial diagnosis                                                      | 140 |

LIST OF FIGURES xvi

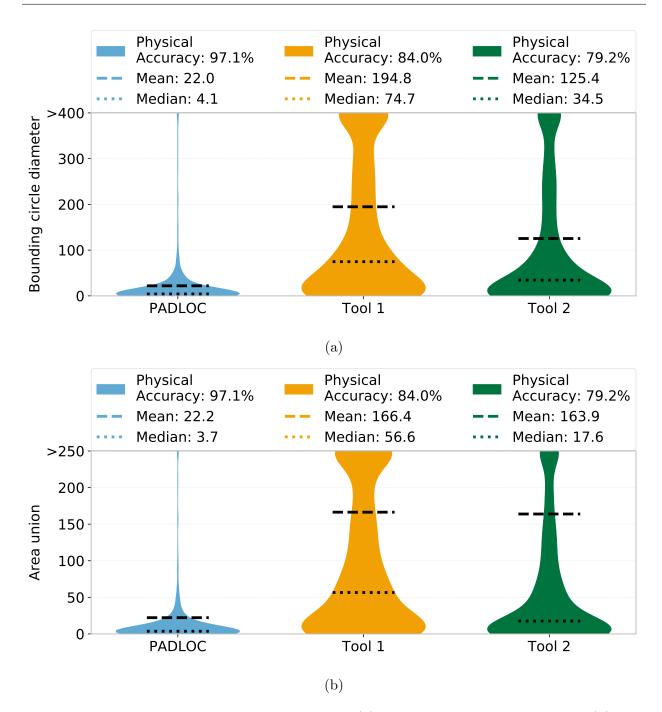

| 4.21 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|------|-------------------------------------------------------------------------------|-----|

|      | union for the design "L2B", when bridge defects are diagnosed by PADLOC       |     |

|      | and commercial diagnosis.                                                     | 141 |

| 4.22 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "B18", when bridge defects are diagnosed by PADLOC       |     |

|      | and commercial diagnosis                                                      | 142 |

| 4.23 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "AES", when open defects are diagnosed by PADLOC         |     |

|      | and commercial diagnosis.                                                     | 147 |

| 4.24 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "DES", when open defects are diagnosed by PADLOC         |     |

|      | and commercial diagnosis                                                      | 148 |

| 4.25 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "L2B", when open defects are diagnosed by PADLOC         |     |

|      | and commercial diagnosis                                                      | 149 |

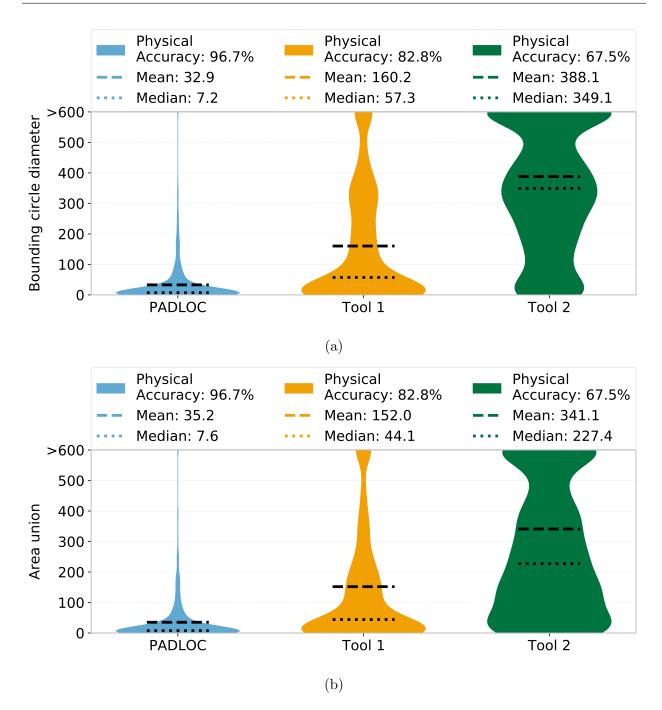

| 4.26 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union for the design "B18", when open defects are diagnosed by PADLOC         |     |

|      | and commercial diagnosis                                                      | 150 |

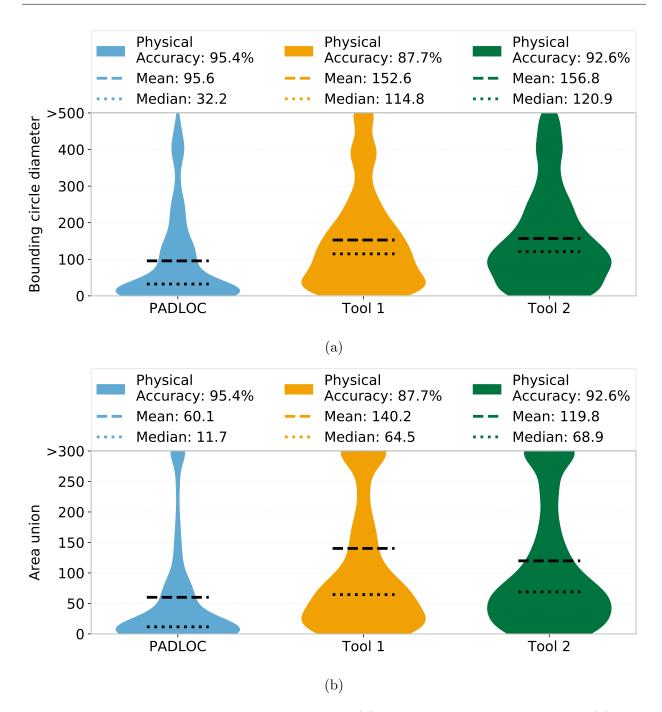

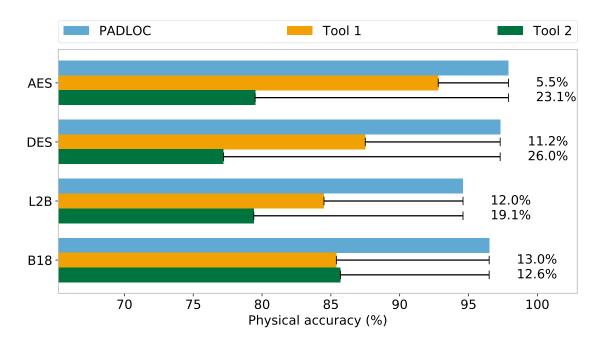

| 4.27 | Physical accuracy achieved by PADLOC and commercial diagnosis                 | 153 |

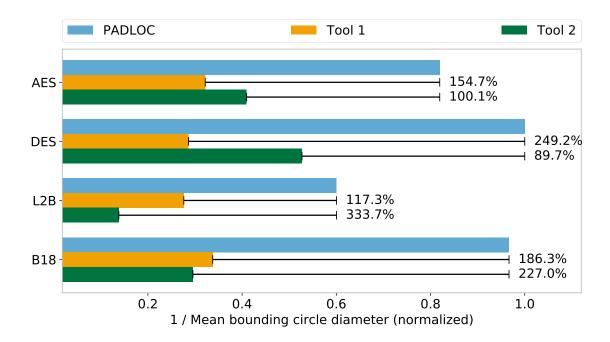

| 4.28 | $Bounding\ circle\ diameter$ achieved by PADLOC and commercial diagnosis      | 153 |

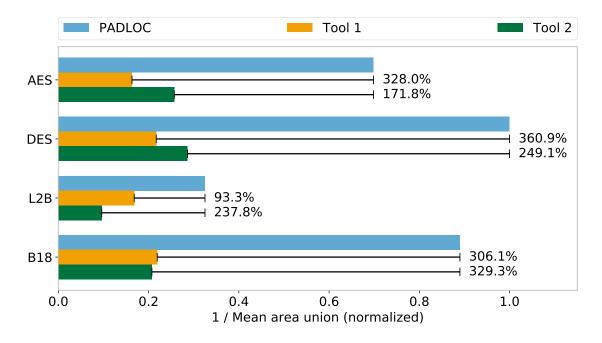

| 4.29 | Area union achieved by PADLOC and commercial diagnosis                        | 154 |

| 4.30 | Probability density distribution of (a) bounding circle diameter and (b) area |     |

|      | union when 2,400 silicon failures are analyzed by PADLOC and commercial       |     |

|      | diagnosis.                                                                    | 157 |

| 4.31 | Bounding circle diameter for 36 failing chips that are PFA'ed                 | 158 |

| 4.32 | Area union for 36 failing chips that are PFA'ed                               | 158 |

LIST OF FIGURES xvii

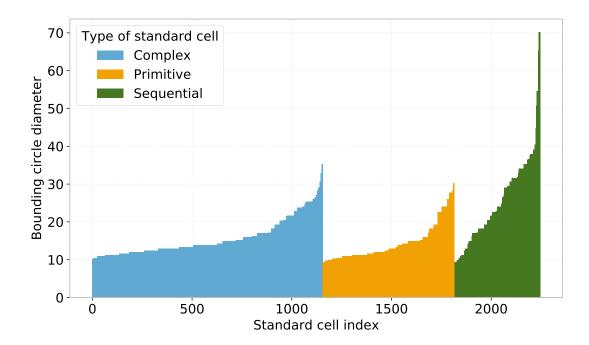

| 5.1  | Physical area (quantified by bounding circle diameter and normalized by the           |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | metal-1 pitch) of each cell in a 14nm commercial standard-cell library                | 165 |

| 5.2  | An overview of the proposed front-end diagnosis methodology, NOIDA                    | 173 |

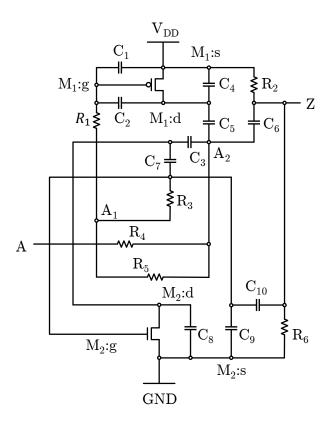

| 5.3  | A schematic view of an inverter cell with parasitics extracted. Parasitics            |     |

|      | affecting power rails are not shown for clarity                                       | 174 |

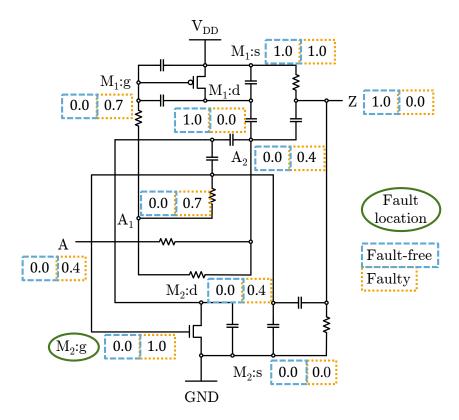

| 5.4  | Analog voltage obtained at each intra-cell node when an inverter is simulated         |     |

|      | by adding a near-zero resistor between $M_2:g$ and $V_{DD}$ (to emulate $M_2:g$       |     |

|      | stuck-at 1) for $A = 0$                                                               | 176 |

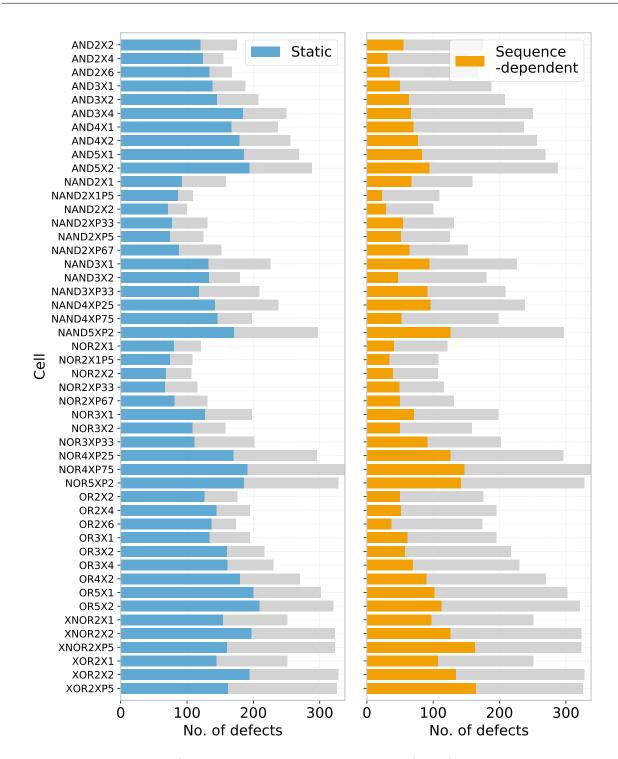

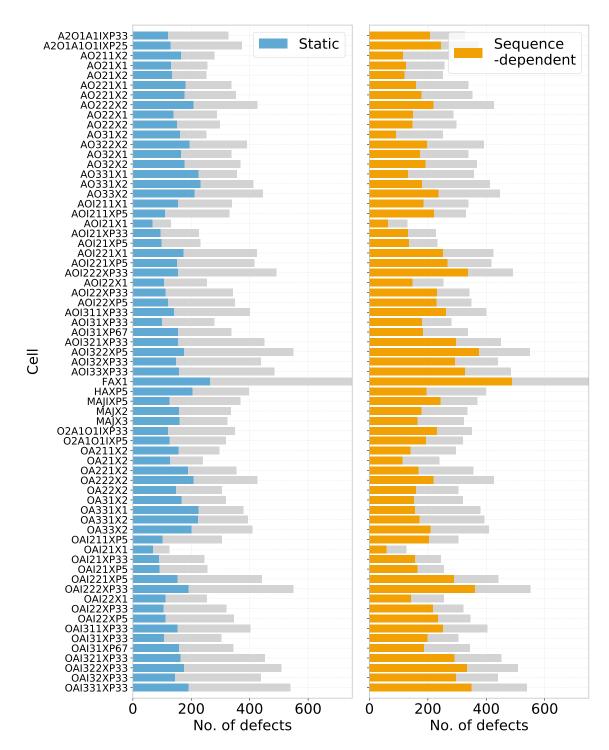

| 5.5  | Distribution of static and sequence-dependent defects for primitive cells in a        |     |

|      | 7nm standard-cell library                                                             | 183 |

| 5.6  | Distribution of static and sequence-dependent defects for complex cells in a          |     |

|      | 7nm standard-cell library                                                             | 184 |

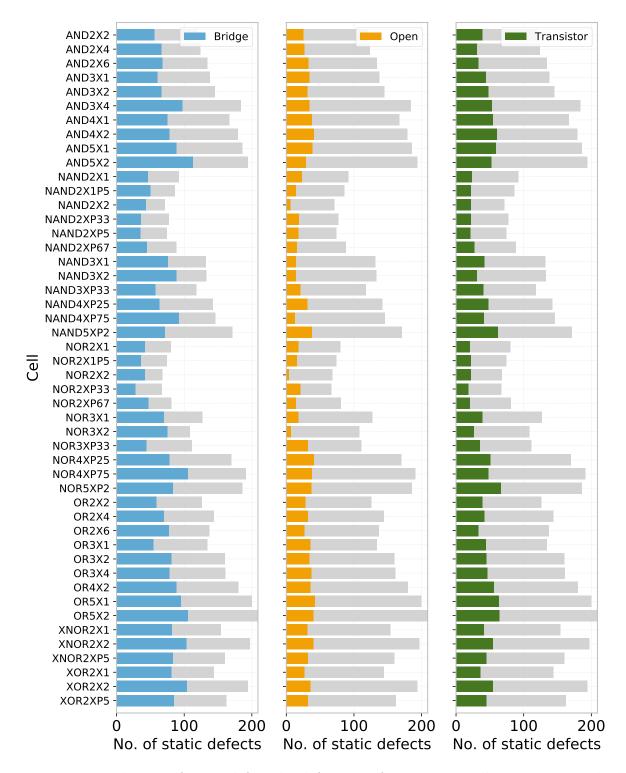

| 5.7  | Distribution of static defects by defect type for primitive cells in a 7nm            |     |

|      | standard-cell library                                                                 | 186 |

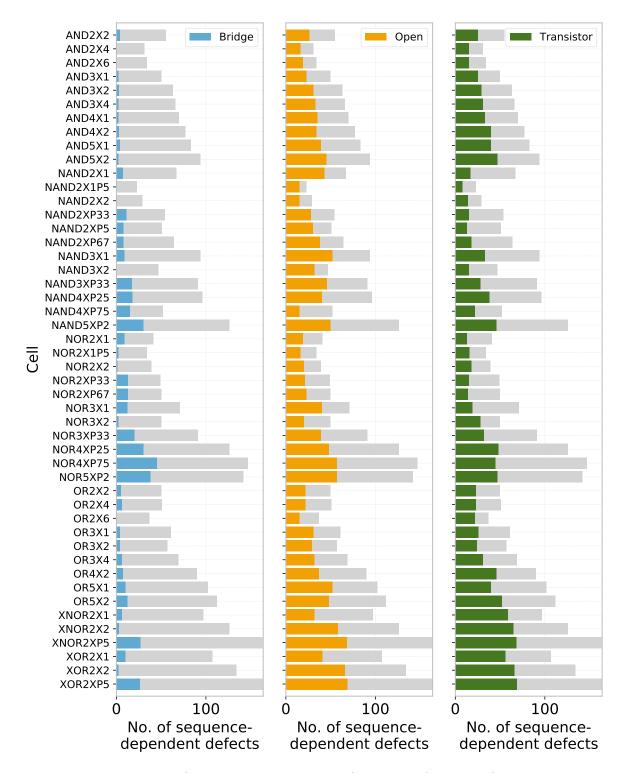

| 5.8  | Distribution of sequence-dependent defects by defect type for primitive cells         |     |

|      | in a 7nm standard-cell library                                                        | 187 |

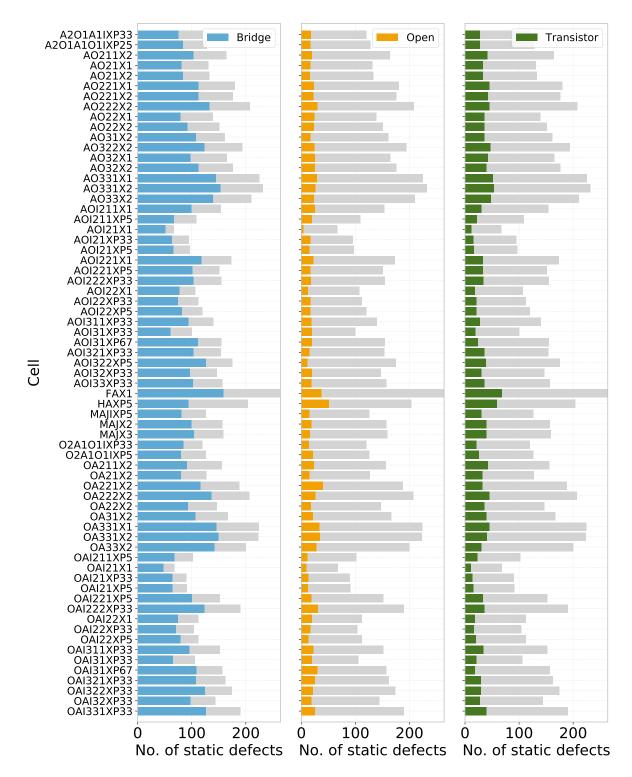

| 5.9  | Distribution of static defects by defect type for complex cells in a 7nm standard- $$ |     |

|      | cell library.                                                                         | 188 |

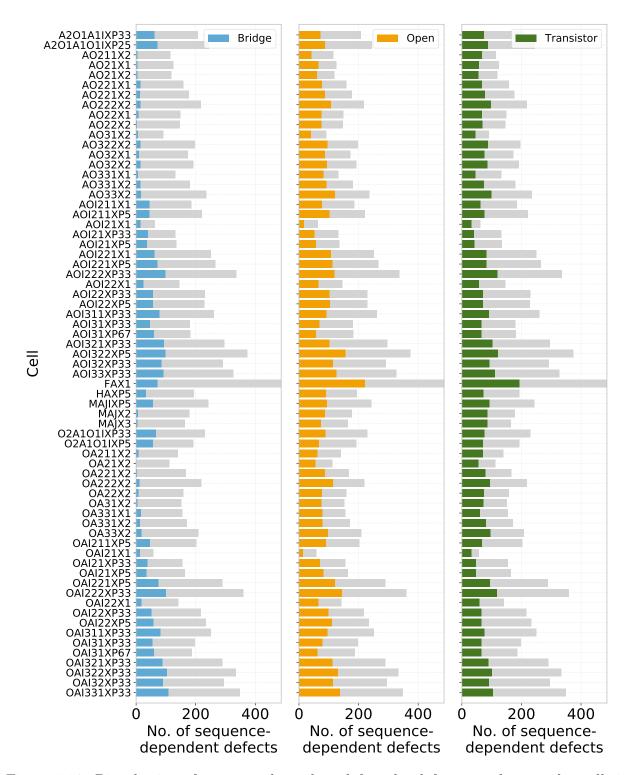

| 5.10 | Distribution of sequence-dependent defects by defect type for complex cells in        |     |

|      | a 7nm standard-cell library                                                           | 189 |

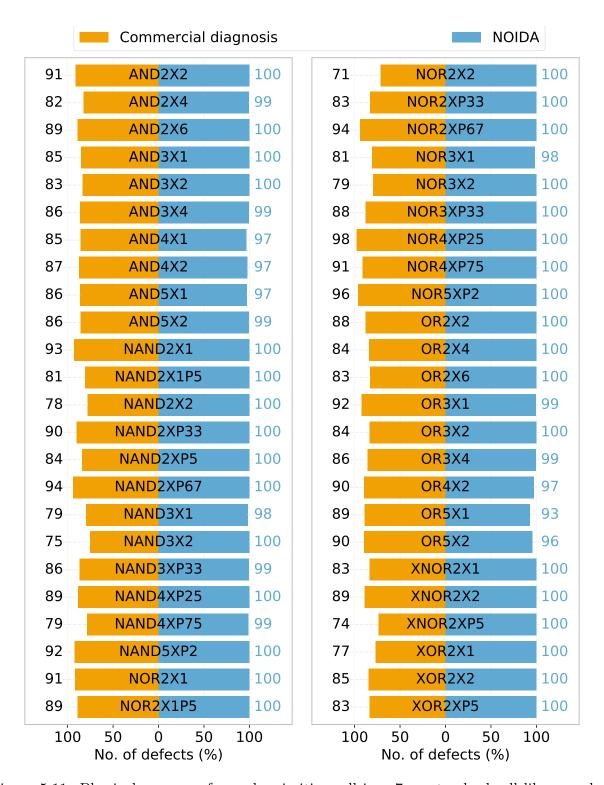

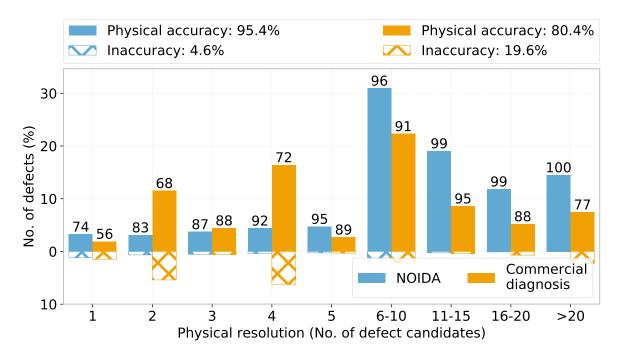

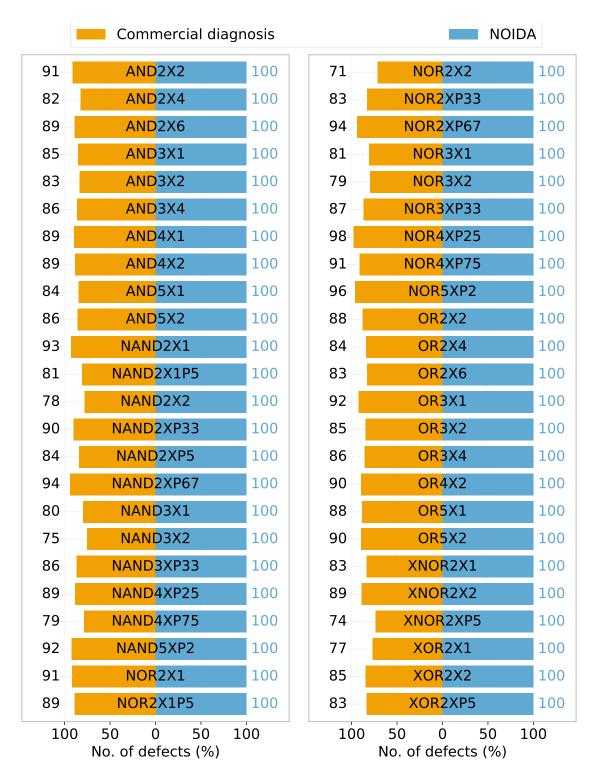

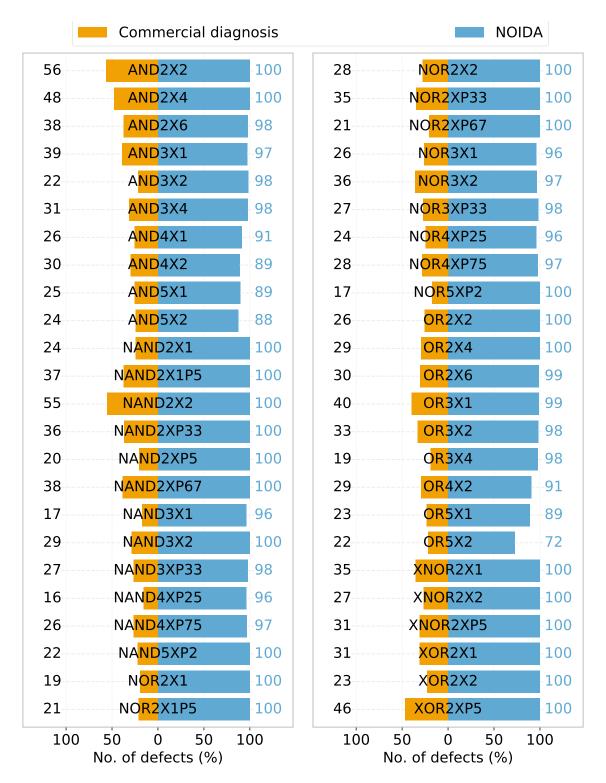

| 5.11 | Physical accuracy for each primitive cell in a 7nm standard-cell library, when        |     |

|      | each cell is exhaustively tested                                                      | 193 |

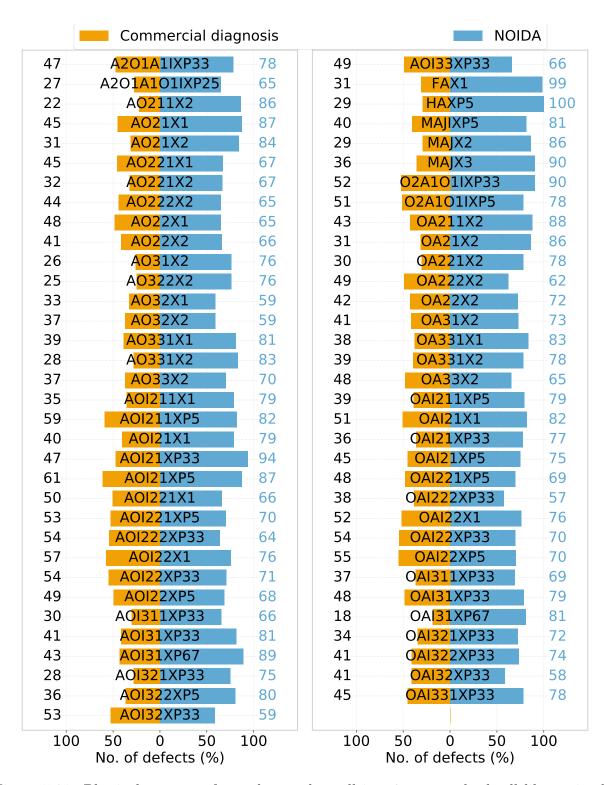

| 5.12 | Physical accuracy for each complex cell in a 7nm standard-cell library, when          |     |

|      | each cell is exhaustively tested                                                      | 194 |

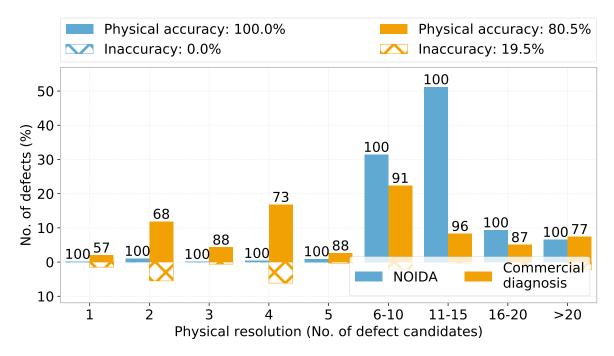

| 5.13 | Distribution of physical resolution for primitive cells in a 7nm standard-cell        |     |

|      | library, when each cell is exhaustively tested                                        | 195 |

LIST OF FIGURES xviii

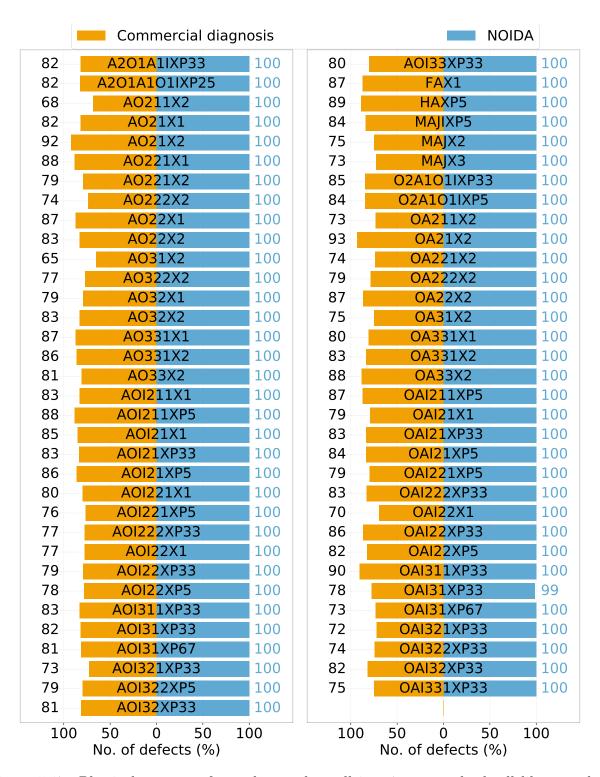

| 5.14 | Distribution of physical resolution for complex cells in a 7nm standard-cell    |     |

|------|---------------------------------------------------------------------------------|-----|

|      | library, when each cell is exhaustively tested                                  | 195 |

| 5.15 | Ratio of test set sizes obtained from a commercial cell-internal ATPG tool      |     |

|      | and exhaustive testing for a 7nm standard-cell library                          | 197 |

| 5.16 | Physical accuracy for each primitive cell in a 7nm standard-cell library, when  |     |

|      | each cell is tested with an ATPG test set                                       | 200 |

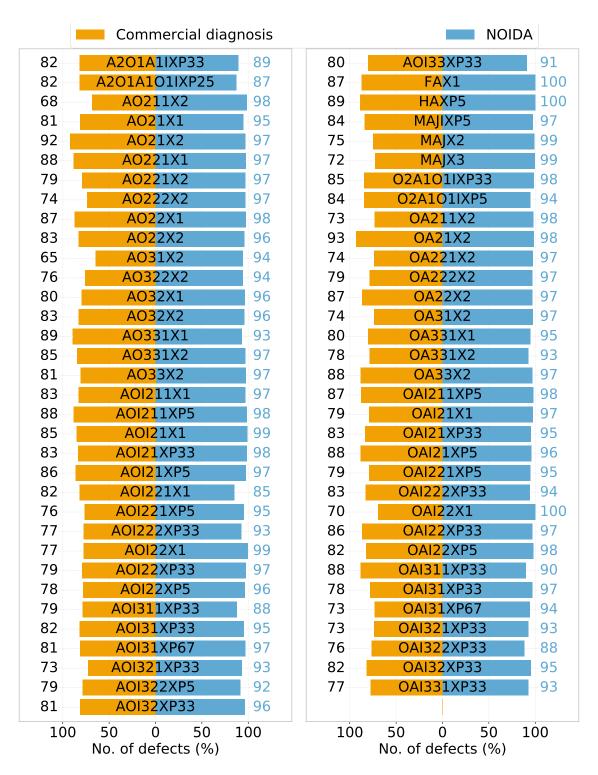

| 5.17 | Physical accuracy for each complex cell in a 7nm standard-cell library, when    |     |

|      | each cell is tested with an ATPG test set                                       | 201 |

| 5.18 | Distribution of physical resolution for primitive cells in a 7nm standard-cell  |     |

|      | library, when each cell is tested with an ATPG test set                         | 202 |

| 5.19 | Distribution of physical resolution for complex cells in a 7nm standard-cell    |     |

|      | library, when each cell is tested with an ATPG test set                         | 202 |

| 5.20 | Physical accuracy for each primitive cell in a 7nm standard-cell library in the |     |

|      | presence of circuit-level noise                                                 | 205 |

| 5.21 | Physical accuracy for each complex cell in a 7nm standard-cell library in the   |     |

|      | presence of circuit-level noise                                                 | 208 |

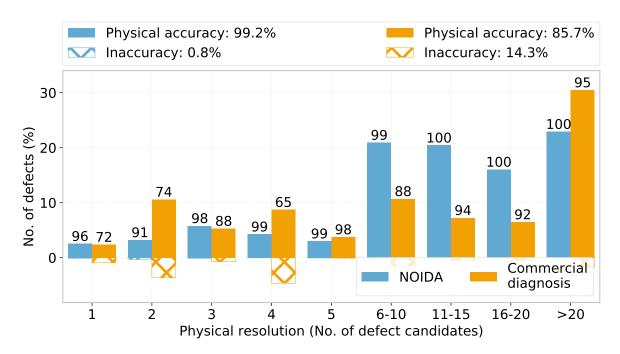

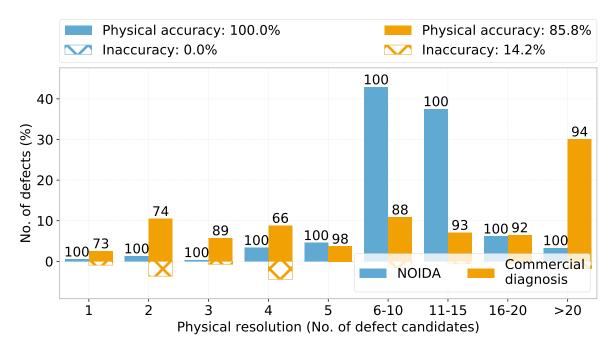

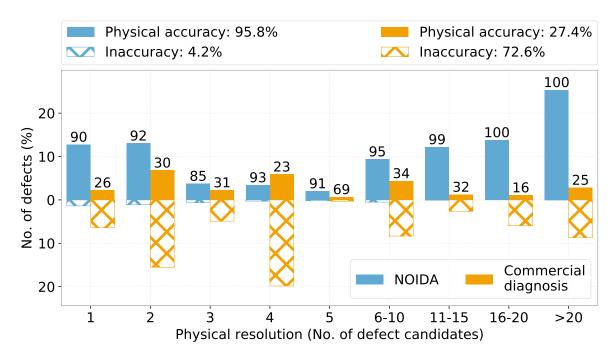

| 5.22 | Distribution of physical resolution for primitive cells in a 7nm standard-cell  |     |

|      | library in the presence of circuit-level noise                                  | 209 |

| 5.23 | Distribution of physical resolution for complex cells in a 7nm standard-cell    |     |

|      | library in the presence of circuit-level noise                                  | 209 |

# List of Tables

| 2.1 | Features extracted from the test data for Phase 1                                    | 35 |

|-----|--------------------------------------------------------------------------------------|----|

| 2.2 | Rule criteria for Phase 1                                                            | 36 |

| 2.3 | Pattern-level features extracted from the test data for Phase 2. Six features        |    |

|     | for each type of simulation are identified, resulting in a total of 12 pattern-level |    |

|     | features                                                                             | 41 |

| 2.4 | Output-level features extracted from the test data for Phase 2. Sixteen fea-         |    |

|     | tures for each type of simulation are identified, resulting in a total of 32         |    |

|     | output-level features                                                                | 42 |

| 2.5 | Number of defects of each type diagnosed by Phase 1 and Phase 2 for four             |    |

|     | designs                                                                              | 48 |

| 2.6 | Accuracy and home run for each defect type achieved by LearnX (Phase 1)              |    |

|     | and two commercial tools for each of the four designs analyzed                       | 52 |

| 2.7 | Accuracy and home run for each defect type achieved by LearnX (Phase 2)              |    |

|     | and two commercial tools for each of the four designs analyzed                       | 57 |

| 3.1 | Summary of silicon test data from chips manufactured across various process          |    |

|     | nodes and organizations highlighting the percentage of failing chips affected        |    |

|     | by multiple defects                                                                  | 68 |

| 3.2 | Class and multiplicity of defects targeted by each phase of MD-LearnX                | 77 |

| 3.3 | Rules for each candidate fault type in Phase 1 of MD-LearnX                          | 80 |

LIST OF TABLES xx

| 3.4 | Features extracted from the test data for Phase 3. Sixteen features for each         |      |

|-----|--------------------------------------------------------------------------------------|------|

|     | type of simulation are identified, resulting in a total of 32 pattern-level features | . 83 |

| 4.1 | Illustration of consistency check. Candidate $A$ is inconsistent because the         |      |

|     | state 000 is established for a TPSF and a TFSF pattern. Candidate $B$ is             |      |

|     | consistent because the failing states and the passing states are distinct            | 110  |

| 4.2 | Physical neighborhood for each segment of net $N_1$ (illustrated in Figure 4.7)      |      |

|     | for bridge defect diagnosis                                                          | 115  |

| 4.3 | Physical neighborhood for each segment of net $N_1$ (illustrated in Figure 4.8)      |      |

|     | for open defect diagnosis                                                            | 117  |

| 5.1 | Summary of silicon test data from chips manufactured across various process          |      |

|     | nodes and organizations highlighting the percentage of failing chips affected        |      |

|     | by a front-end defect                                                                | 164  |

| 5.2 | Intra-cell neighborhood for each intra-cell node in the inverter that is illus-      |      |

|     | trated in Figure 5.3. Each neighbor of a node is capacitively coupled to it          | 177  |

### Chapter 1

### Introduction

More than 50 years ago, it was predicted (rather, observed) that the transistor density of an integrated circuit ("chip") would double every year [1]. Ten years later, the prediction, popularly known as the Moore's law, was revised to doubling every two years [2]. Robert Dennard, around the same time, observed that the chip power density remains constant with decreasing transistor sizes [3]. His postulation, widely known as Dennard scaling, has been one of the primary propellants of Moore's law. In conjunction with Dennard scaling, it implies that the energy efficiency (performance per watt) would double even faster than two years.

Moore's law (along with Dennard scaling) has since then become a de facto standard in the semiconductor industry [4–6]. Moore's law has been the driving force behind the technological advancements for semiconductor industry growth. Numerous inventions and breakthroughs have been sustaining Moore's law to advance semiconductor manufacturing, resulting in an increased chip performance and/or improved power efficiency [6–8]. These innovations include (and are not limited to):

• Decreased transistor sizes, where the transistor density (measured in terms of the number of transistors per  $mm^2$ ), for instance, has proliferated from less than 500 in

the early 1970s [9–11] to more than a 100M in 2019 [12–17].

- Creative transistor structures such as non-planar transistors (e.g., a fin field effect transistor (FinFET) [17–20] and a gate-all-around FET (GAAFET) [21, 22]).

- New materials, such as the use of hafnium instead of silicon dioxide as a transistor gate dielectric in a 45nm process node [23], and using germanium instead of silicon to build a transistor [24–26].

- Three dimensional monolithic and heterogeneous integration [27–31].

- Next-generation lithography strategies such as optical proximity correction (OPC) [32], phase shift mask [33], multiple patterning [34–40], and extreme ultraviolet lithography (EUV) [40–42].

- Novel processor microarchitectures [43–46].

Unfortunately, the increase in the density and complexity of a chip, which causes an increase in its performance (and energy efficiency), is also accompanied by significant manufacturing challenges.

As a consequence, the task of fabricating a working chip has become extremely difficult to accomplish. Human and equipment errors, contaminants, interactions between the design and the manufacturing process, and/or a complication at any fabrication step can introduce a defect into a manufactured chip. A defect is an unforeseen physical irregularity in a manufactured chip that may lead to its failure. A systematic defect stems from some flaw in the design, deficiency in the manufacturing process, or interactions between the design and the process. A random defect, in contrast, arises due to intermittent equipment excursions or contaminants in the fab.

Besides manufacturing defects, poor design, environmental factors such as temperature and humidity, wearout and process variations can render a manufactured chip inadequate. The proportion of working chips fabricated is called *yield*. Yield loss is further aggravated by diminishing time-to-volume, time-to-market and time-to-money requirements of the semi-conductor industry.

Various strategies are used to identify and characterize the sources of yield loss, and consequently, increase yield. The process of rectifying sources of yield loss to improve chip design and manufacturing is called yield learning.

In-line defect inspection [47, 48], for example, optically examines a wafer to identify imperfections in a chip during manufacturing. However, with shrinking technology, its effectiveness to locate a defect is decreasing because it only inspects the wafer surface, which means that only the defects that are visible on the wafer can be identified by an in-line inspection equipment. In addition, not all defects captured by in-line inspection are "killer" defects<sup>1</sup> [49,50]. Moreover, its use is limited due to its cost, throughput and ineffectiveness to determine the nature of a defect (i.e., whether it is an open, short, etc.).

Specialized test structures such as comb drives, serpentine structures and ring oscillators are custom designed to easily observe specific defect mechanisms [51–53]. They are transparent to failure and can provide quick feedback early in the yield learning phase to make modifications in the manufacturing process. However, such structures are elementary and do not reflect the range of layout patterns used in random logic; hence, their use is limited to evaluating the process parameters in the early stages of yield learning. During volume production, on the other hand, test structures are only deployed in the scribe lines between customer chips, and thus their ability to find defects is restricted.

Bitmap analysis of a memory is yet another way to identify sources of yield loss during the early/intermediate phases of yield learning [48, 54]. A bitmap visually represents the location of the failing bits within a memory. Because of their regular architecture, memories are transparent to failure; the configuration of a bitmap can be investigated to find the root

<sup>&</sup>lt;sup>1</sup>A killer defect causes a chip to malfunction.

cause of failure. One advantage of using a memory as a yield learning vehicle is that, in contrast to custom test structures, they may undergo all the processing steps in the entire fabrication flow. Even then, however, because of their regularity, memories utilize only the first few process layers. As a result, they are unable to catch defects in the upper metal layers. In addition, due to their regular design, memories contain limited layout patterns, and hence are unfit to monitor the defects resulting from diverse layout geometries typically found in random logic.

An alternative to memory is a logic test chip that is implemented using a standard automated place-and-route tool [55–62]. Short-flow logic test chips, that may contain diverse layout patterns and are fabricated using a subset of metal layers, face a similar drawback as memories – they are ineffective in identifying a source of yield loss that may otherwise be detected if the entire manufacturing flow is employed. Full-flow logic test chips (including legacy designs retrofitted for the latest technology node), on the other hand, utilize all the process layers and thus are more suited to analyze/monitor yield during the later stages of yield ramp.

Finally, manufacturing test is used to pinpoint the sources of yield loss in a logic test chip and the random logic used in a customer chip. Specifically, the knowledge of how a chip fails manufacturing test is used to identify the location and nature of a defect to increase yield. This process, known as software-based diagnosis (or simply, diagnosis), is the first step in failure analysis (FA). Diagnosis offers several advantages (which are discussed in detail later in Section 1.1). For example, diagnosis makes in-line inspection more effective; the outcome of diagnosis can be correlated with the in-line inspection data to discern killer defects.

Additionally, a statistically significant number of diagnoses can be correlated to discover the underlying yield detractor(s). The corresponding chips can then be physically inspected to verify and characterize the yield detractors. As opposed to diagnosis that is expeditious and non-invasive, physical failure analysis (PFA) is time-consuming and destructive. Nevertheless, PFA provides indisputable confirmation of the presence of a defect and explores its underlying physical cause. It aims to provide a critical understanding of how a defect is introduced in the manufacturing process and thus is crucial to yield learning. The feedback obtained from physical failure analysis is used to prevent similar defects in the future, and consequently, amend the design and/or manufacturing process to increase yield.

This dissertation concentrates on employing manufacturing test to identify the sources of yield loss that influence the random logic in a chip (a customer or a logic test chip). In other words, the focus is on logic defect diagnosis, i.e., the analysis and comprehension of the test failure data to determine the location and the behavior of a defect that affects the logic sub-circuit of a chip, to identify logic yield limiters. The role of diagnosis is especially significant during (a) yield ramping, when logic test chips are deployed and/or customer chips are manufactured prematurely; (b) high-volume manufacturing of customer chips for continuous yield learning/monitoring; and (c) yield excursion (i.e., when yield plummets abruptly from its stable value), when diagnosis can be exploited to uncover the underlying source of yield loss and, consequently, stabilize yield.

The next section, Section 1.1 details the role of manufacturing test and diagnosis in failure analysis that, in turn, facilitates yield learning and monitoring. It also lays the groundwork for the work developed in this disseration. Section 1.2 previews the diagnosis methodology developed and highlights the superior performance achieved by our diagnosis methodology when compared to state-of-the-art commercial diagnosis. Section 1.3 presents the organization of the rest of this dissertation.

#### 1.1 Diagnosis Guided Yield Learning

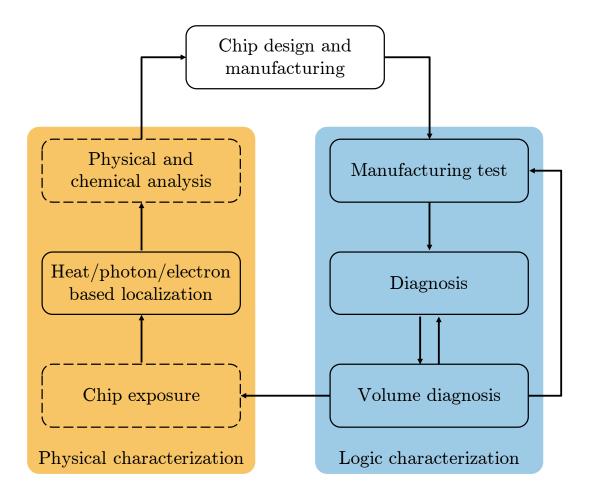

Figure 1.1 illustrates a simplified flow that depicts the role of manufacturing test and diagnosis in yield analysis, learning and monitoring. The flow is partitioned in two parts – the

Figure 1.1: A simplified flow depicting the role of manufacturing test and diagnosis in guiding yield analysis, learning and monitoring.

"right" part of the flow (in blue) characterizes a defect at a logic level and the "left" part of the flow focuses on the physical level. While logic characterization focuses on identifying the logic properties of a defect such as its logic behavior and x - y - z location in the circuit, physical characterization aims to uncover the physical features of a defect such as its shape, size, composition and root cause. Each step of the flow depicted with a dashed outline denotes that it is a destructive process. The remaining steps depicted with a solid outline are non-destructive in nature.

The flow begins with the design and manufacturing of a chip. Process-design interac-

tions, design marginalities, and/or complications at any step of the convoluted and precisely regulated fabrication flow can introduce one ore more defects in a produced chip. It should be recalled that the focus of this dissertation is on defects that affect the logic sub-circuit of a chip; thus, the flow of Figure 1.1 will be discussed while considering only defects that affect the logic.

The next step is manufacturing testing<sup>2</sup>, where a set of input values called *test patterns* are applied to a logic circuit and the observed circuit response to each pattern is compared with the expected correct response. A circuit that fails testing is classified as defective. Thus, test functions as a binary filter – it is used to differentiate the good chips from the malfunctioning ones. However, testing is not perfect; some good chips can be categorized as defective and vice versa. The fraction of good chips that fail testing is called *test yield loss*. This misclassification is generally due to factors such as a test equipment error and an unsuitable test environment for the circuit under test. The proportion of defective chips that pass testing is termed as *defect level*. This misclassification, where a defective chip escapes test, is due to the inability of a testing approach to detect a defect.

Ideally, a testing technique should detect all possible defects that could render a chip malfunctioning. However, defects are unpredictable, and design- and process-dependent. It is thus impractical to track the sheer number of ways in which a defect may manifest. Testing is made tractable through the use of fault models. A fault model is an abstraction from actual defects at a high level. It is a set of assumptions that describes the behavior of a defect and/or its impact on the circuit. Because a fault is defined at a higher level of abstraction than a defect, many defects can map to a single fault. In this way, fault modeling mitigates the complexity of generating a test for each possible defect.

<sup>&</sup>lt;sup>2</sup>We will focus here on manufacturing testing, which is performed after manufacturing and before chips are shipped to a customer. Other types of testing include characterization testing, which is performed to find design errors and determine the exact operating conditions of the design before fabrication, and acceptance testing, which is carried out by a customer.

Fault models can be defined at different levels of abstraction such as logic (or standard-cell), circuit (or transistor) and physical layout levels. For example, the single stuck line (SSL) fault model (also known as the stuck-at fault model) assumes that a signal in the logic circuit is permanently stuck at either logic-0 or logic-1. The wired-AND (wired-OR) bridge fault model assumes that logic-0 (logic-1) at one of the bridged signals overrides logic-1 (logic-0) at the other bridged signal [63,64]. The X-fault model assumes an unknown value (X) at a potential defect location [65]. The aforementioned models are defined at the logic level. The transistor stuck-closed (stuck-open) fault model, which is defined at the circuit level, assumes a transistor to be conducting (non-conducting) permanently [66,67].

A variety of fault models at different abstraction levels with varying complexity exist in the literature to represent ever-evolving defects. Notable examples include the input-pattern [68–70], voting bridge [71,72], cell-aware [73–78], inductive [79,80], path-delay [81] and transition [82,83] fault models.

An alternative approach to increase the quality of a test set is to specify/measure the thoroughness of a test set. For example, the N-detect metric requires at least N detections for each stuck-at fault in the circuit [84,85]. The gate-exhaustive test metric generates a test set such that each standard cell in the circuit is exhaustively tested<sup>3</sup> [86,87].

After a high-quality test set is generated (while considering different fault models and test metrics) using an Automatic Test Pattern Generation (ATPG) tool, the next step in the yield learning flow (shown in Figure 1.1) is diagnosis. Diagnosis is a software-based process to determine the possible locations (often called candidates) and the corresponding defect types within a failing chip by analyzing and understanding the observed circuit response. The quality of diagnosis is typically measured by the number of candidates identified, the corresponding implicated physical area (i.e., the layout area occupied by the candidates

$<sup>^{3}</sup>$ The gate-exhaustive test metric is equivalent to the input-pattern fault model applied at the standard-cell level.

suspected by diagnosis), and whether the candidate set contains an actual defect location.

Numerous methods have been proposed in the past to enhance the quality of diagnosis. A cause-effect approach compares the tester response with a set of simulated faulty behaviors to find candidates [88–103]. However, because the defect universe is expanding with advancing technology, it is unreasonable to simulate faults that represent all possible defects that could affect a chip. Design size, defect multiplicity and defect behavior variability further restrict the practical applications of a cause-effect approach.

An effect-cause approach, on the other hand, follows an orthogonal approach – it analyzes the observed circuit response to deduce candidates [91, 104–114]. An effect-cause technique such as path tracing [108–110], by itself, however, suffers from poor resolution; because it is cautious about removing a correct candidate, several incorrect candidates are implicated as well.

Methods that include [115–145] use a combination of a cause-effect and an effect-cause approach to benefit from both types of methods. Those techniques usually perform diagnosis in three steps – an effect-cause technique to identify the failing region, simulation of faults within the failing region, and a candidate-scoring procedure to determine possible candidates. Layout information can further be utilized to pinpoint a physical location of a defect residing outside a standard cell [142–161] or within a cell [80, 162–181].

Besides the development of a better algorithm, the effectiveness of diagnosis can also be improved via targeted test generation to distinguish diagnostic candidates [182–212] and/or by altering the design itself [59,212–216].

The next step in the flow of Figure 1.1 is volume diagnosis, where diagnosis results for a population of failing chips are statistically examined to find yield-limiting design and/or manufacturing issues, in hope of determining if a significant percentage of chips are failing due to a common root cause [144,217–232]. Chips with yield-limiting defects can then be further inspected to unearth the physical characteristics of a defect.

In addition to assisting/accelerating the subsequent failure analyses, volume diagnosis provides useful information to improve test and diagnosis as well. For example, it can be used to estimate defect-type distribution, which can then be used to reduce test escapes via adaptive testing [233–235]. In [236], diagnosis data is used to find the efficiency of new and existing fault models and test metrics, instead of relying on time-consuming test set silicon experiments. It has also been shown that information obtained from diagnoses can be used to estimate defect density and size distributions (DDSDs) for each metal layer to understand the impact of random defects [237, 238]. In [239], diagnosis is used to predict chip defect level and monitor chip quality. In [240–243], the effectiveness of Design-for-Manufacturability (DFM) guidelines is evaluated using volume diagnosis results.

The steps of Figure 1.1 discussed up to this point enable logic characterization of a defect. The next sequence of steps seeks to physically characterize a defect and investigate its underlying origin.

Based on the output of volume diagnosis, selected chips are further analyzed. The first step towards physical characterization of a defect is exposing the chip, i.e., removing the connections between the chip and its packaging, while ensuring that the chip is electrically functioning. The process of exposing a chip so that it can be inspected visually is called decapsulation (or delidding) [244, 245]. Decapsulation can be accomplished by acid [246], plasma [247, 248], laser [249–251] or thermo-mechanical [252, 253] based methods.

The next step is to isolate the defect location reported by (volume) diagnosis via mechanical, thermal, optical, or electron probing methods. For example, fluorescent microthermal imaging (FMI) studies the temperature-dependent fluorescence emitted by a film coated on the surface of a chip to detect a defect [254–257]. Techniques such as laser-induced voltage alteration (LIVA) [258] and laser-assisted device alternation (LADA) [259] study the interactions of a defect with photons. Other popular probing methods include photon emission microscopy (PEM) [260], optical beam induced current (OBIC) [261], opti-

cal beam induced resistance change (OBIRCH) [262], thermally induced voltage alteration (TIVA) [263], electron beam induced current (EBIC) [264,265], and charge-induced voltage alteration (CIVA) [266]. In general, those methods are non-destructive in nature, and their goal is to further pinpoint and/or verify the defect location implicated by diagnosis.

Once the presence of a defect is confirmed by non-destructive means, the chip is physically inspected to determine the physical cause of the underlying failure. The investigation begins with a process known as deprocessing (also called delayering) [244], where process layers are carefully removed one at a time until the layer where the defect is suspected is reached. Deprocessing is essentially the reverse of the manufacturing process. An alternative to chip deprocessing is chip cross sectioning, where the chip is grinded and polished perpendicular to its surface to expose all the layers and the transistors simultaneously [244].

Deprocessed or cross-sectioned chips are then inspected via a microscope to observe the physical features of a defect. Defect images can be analyzed, documented and stored to comprehend the physical root cause. Several chip microscopy techniques exist in the literature that aid in the understanding of the physical characteristics of a defect. Some of the popular physical inspection methods include scanning electron microscopy (SEM) [267, 268], scanning probe microscopy (SPM) [269], and transmission electron microscopy (TEM) [268, 270–272]. Chip sample preparation and physical inspection are not necessarily carried out in sequence only once. Defect images obtained from physical inspection can be utilized to guide the process of sample preparation until the defective region of interest is reached. The defective region can further be analyzed via techniques such as energy-dispersive X-ray spectroscopy [273] to chemically characterize the defect, or specifically, identify the atomic structure and composition of a contaminant causing the defect.

Although physical failure analysis (PFA), i.e., the collective process of preparing the chip sample, and physically and chemically inspecting the prepared sample for defect characterization, is a time-consuming, meticulous and invasive process, it provides irrefutable evidence

of the existence of a defect. In addition, the knowledge of the physical and chemical properties of the defect can suggest useful information regarding its origin or root cause. Corrective actions can then be taken to adjust the design or the manufacturing process to increase yield.

High diagnosis quality is thus extremely important for improving design, test and manufacturing of a chip. An inaccurate diagnosis, for example, can direct volume diagnosis to find false correlations within diagnosis results, which, in turn, can steer PFA to physically inspect incorrect locations. The destructive and resource-intensive nature of PFA constrains it to being performed on only a small number of chips and considerable amount of resources can be wasted if diagnosis is inadequate. Additionally, PFA is becoming challenging because of increasing chip density and decreasing critical defect size with advancing technology. Therefore, a highly effective diagnosis methodology makes PFA more successful, and more cost-and time-efficient.

To summarize, diagnosis is an invaluable engine that critically impacts the

- derivation of DDSDs for each metal layer to understand the effect of random defects on yield,

- construction of a pareto of likely failure mechanisms that decrease yield,

- quality of an adaptive test set that reduces test escapes,

- comprehension of the relative performance of new and existing fault models and test metrics to optimize test quality and cost, and

- success rate and the efficiency of PFA.

As a consequence, diagnosis, in all likelihood, accelerates/facilitates yield analysis, learning and monitoring.

#### 1.2 Dissertation Overview

Determining the location of a defect is the traditional objective of diagnosis. Ideally, diagnosis should go beyond localization to characterizing both the nature and root cause of a defect. Because diagnosis is non-invasive, has a quick turnaround time, is becoming useful for other applications, and, more importantly, plays a vital role in aiding yield analysis, learning and monitoring (illustrated in Figure 1.1 and described in Section 1.1), it is imperative that diagnosis continue to improve and move toward characterization.

Therefore, the goal of diagnosis should be twofold.

- 1. Accurately pinpoint the x y z layout location of a defect.

- 2. Precisely derive the logic behavior of a defect, i.e., deduce the precise impact of a defect on circuit behavior (with minimal assumptions), and identify the defect type.

The accomplishment of the aforementioned two objectives of diagnosis accelerates the overall flow of Figure 1.1. For example, the onus of characterization of a defect that is typically on cost- and time-intensive PFA can be shared by cost- and time-effective diagnosis that adheres to the above-mentioned goals. An ideal diagnosis would thus minimize the need for PFA, thereby, further enabling rapid yield analysis.

Numerous methods have been recommended in the literature to enhance the quality of diagnosis. Diagnosis quality can essentially be improved in three ways – better algorithms, better tests and/or better design. Diagnosis methods that develop new algorithms can further be differentiated based on the type of fault model exploited at the logic level (whether a binary error or an unknown value is assumed at a candidate location), the scoring technique employed (deterministic vs. statistical), how precisely a defect is localized (i.e., whether a defect candidate is reported at a logic, back-end layout or front-end layout level), and whether multiple defects affecting a single chip can be analyzed/identified adequately.

To the best of our knowledge, no prior diagnosis methodology simultaneously focuses on the two objectives of an ideal diagnosis method, i.e., accurate defect localization at a physical-level as well as precise defect behavior identification at a logic-level.

A comprehensive diagnosis methodology is presented in this dissertation that attempts to accomplish each of the two goals of diagnosis. The focus is on improving the quality of diagnosis via designing a better algorithm; approaches that manipulate a test set or alter the design itself complement and strengthen our work [59, 182–216].

Our developed methodology can be divided into three stages. Specifically,

• LearnX [274] is a physically-aware diagnosis methodology that focuses on accurate defect localization. Besides employing the widely used (temporary) stuck-at fault model to identify "simple" defects, LearnX takes the advantage of the X-fault model [65] to locate a defect that misbehaves arbitrarily. The X-fault model allows an error to propagate conservatively and thus (likely) precludes the elimination of a correct candidate.

Additionally, instead of manually devising a candidate ranking procedure by intuition and/or domain knowledge that may or may not work for ever-changing defects, machine learning is exploited to construct a data-driven ranking model that learns the hidden correlations between the observed circuit response and the (fault simulation response of the) correct candidate. Moreover, it utilizes design layout information to find the candidates that are physically feasible to identify their defect types.

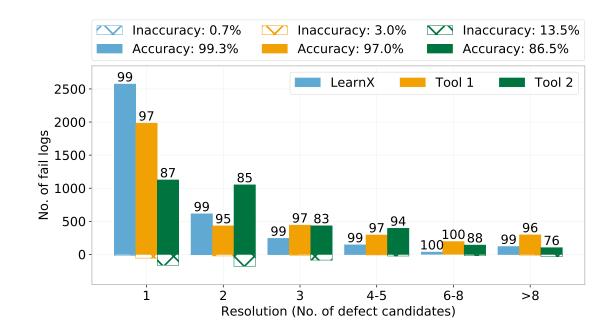

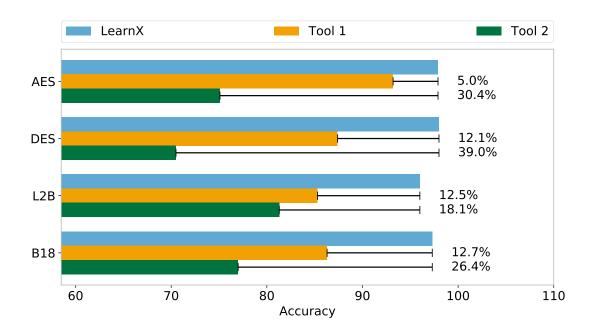

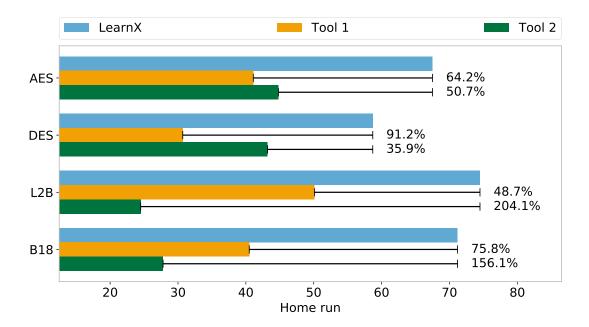

Simulation-based experiments conducted for four different designs demonstrate the potential of LearnX. LearnX identifies the correct candidate for 97.3% fail logs, which is 10.5% better than leading-edge commercial diagnosis. In addition, LearnX returns an ideal diagnosis (i.e., a single correct candidate) significantly more often than commercial diagnosis. Specifically, LearnX reports an ideal diagnosis for 67.9% fail logs, which

is 67.5% better than one commercial tool and almost double the second commercial tool.

Moreover, significance of LearnX is affirmed by diagnosing 2,400 silicon fail logs from a design fabricated in an advanced process technology. It is revealed that LearnX returns an ideal resolution for 46.9% fail logs, which is almost twice more than what commercial diagnosis achieves. Additionally, LearnX returns 7.1 fewer candidates per fail log, on average.

The effectiveness of LearnX is further corroborated by inspecting 19 failing chips that are PFA'ed. LearnX is able to correctly locate a defect in each failing chip, while reporting fewer candidates than state-of-the-art commercial diagnosis. It is observed that LearnX returns an ideal diagnosis for 52.9% fail logs, which is 12.6% better than commercial diagnosis.

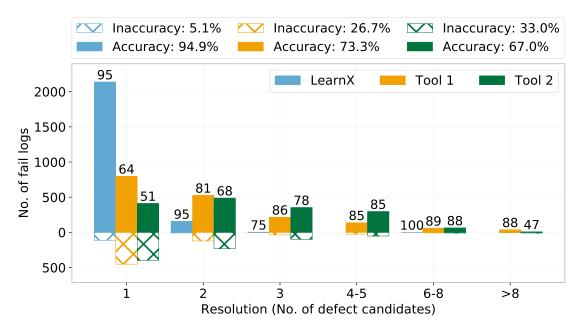

The experiment results thus far underscore the performance of LearnX when a single defect affects a failing chip. A diagnosis methodology called MD-LearnX [275], which builds on LearnX, is developed to effectively tackle multiple defects in a failing chip. MD-LearnX employs the X-fault model as well to avoid the effects of error masking and unmasking that are prominent due to the interaction of multiple defects, and deploys machine learning to identify the best candidate for each defect.

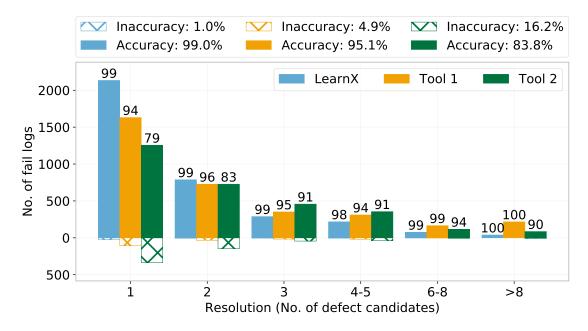

A thorough simulation-based experiment is conducted to assess the capability of MD-LearnX to identify multiple defects, where a total of 28,000 faulty circuits with varying defect multiplicities and behaviors are created and analyzed. Three metrics, namely, diagnosability (i.e., proportion of injected defects that are correctly located), precision (i.e., proportion of reported defects that are correctly identified) and *home run* (i.e., when a single correct candidate is reported for each injected defect), are employed to measure the performance of MD-LearnX.

It is observed that MD-LearnX achieves an average diagnosability and precision of 0.78 and 0.7, respectively, which is 15.4% and 57.0% better than leading-edge commercial diagnosis. MD-LearnX delivers a home run for 40.0% of fail logs, which is twice as often as commercial diagnosis.

The efficacy of MD-LearnX is impressive for large values of defect multiplicity. Specifically, when the number of injected defects is at least five, the diagnosability of MD-LearnX is 22.8% higher than commercial diagnosis, on average. MD-LearnX returns a correct candidate for each reported defect 2.4X more often than commercial diagnosis. Moreover, MD-LearnX delivers a home run for 6.8% fail logs; however, commercial diagnosis returns an ideal diagnosis for less than 0.3% of fail logs.

The capability of MD-LearnX to diagnose multiple defects is further demonstrated with a silicon experiment, where 17 failing chips that are suspected to be affected by multiple defects are diagnosed. It is seen that MD-LearnX returns fewer candidates than commercial diagnosis for 88.2% of the fail logs, without sacrificing accuracy. Moreover, MD-LearnX reports 8.5 fewer candidates per fail log, on average.

• PADLOC, which stands for Physically-Aware Defect LOcalization and Characterization, specializes in accurate physical localization and behavior derivation of a back-end defect (i.e., a defect that affects one or more interconnects and resides outside a standard cell) [146]. It analyzes the back-end defect candidates reported by LearnX/MD-LearnX. PADLOC partitions a candidate net into one or more segments by analyzing the topology of the net and its physical neighbors, and examines the logical activity on the adjacent segments to deduce defect excitation conditions.

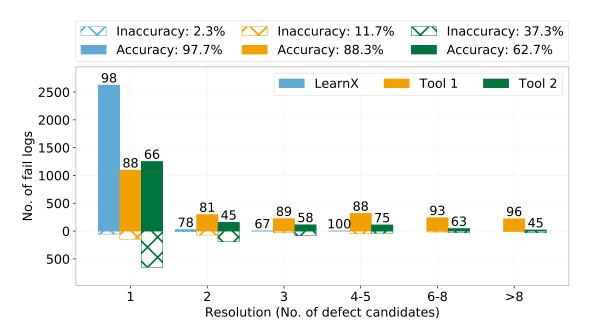

Results from a comprehensive simulation-based experiment reveal that PADLOC pinpoints a defect accurately for 96.5% fail logs, which is 10.3% better than state-of-the-art commercial diagnosis. More impressive, however, is the physical resolution attained by PADLOC. It is observed that the average bounding circle diameter, which is defined as the diameter of the smallest circle enclosing the suspected layout regions, for PADLOC is 61.2, and is 33.0% better than commercial diagnosis.

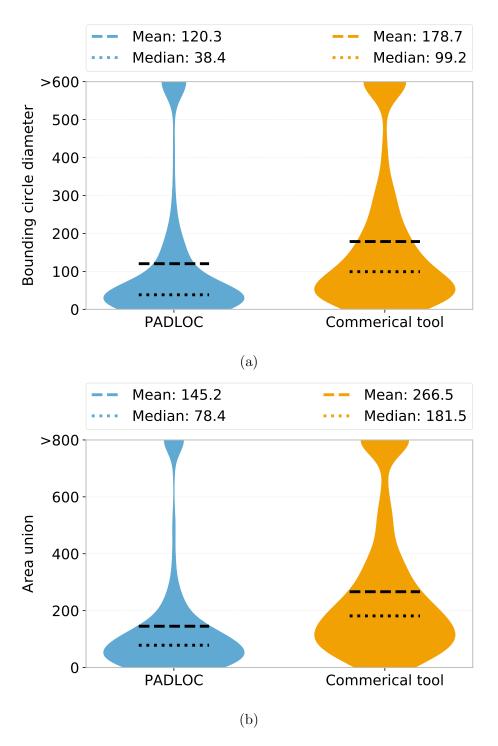

A silicon experiment is also conducted to demonstrate the capability of PADLOC. Silicon failure data corresponding to 2,400 failing chips fabricated in an advanced process technology is examined. The analysis reveals that PADLOC reports a smaller bounding circle for 68.8% of fail logs, when compared with commercial diagnosis. In addition, the *bounding circle diameter* for PADLOC is 120.3, on average, which is 32.7% smaller (i.e., better) than commercial diagnosis.

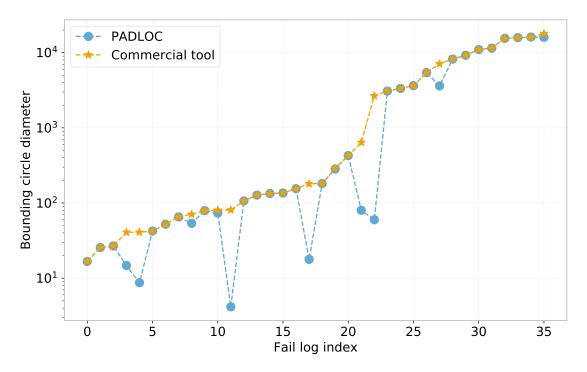

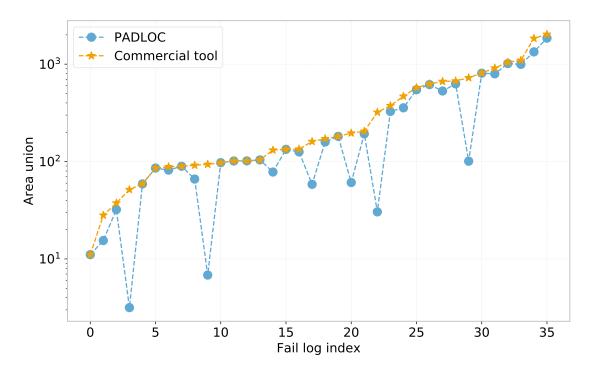

PADLOC is further validated by inspecting 36 failing chips that are PFA'ed. PADLOC is able to physically locate a defect in each failing chip correctly, while suspecting a smaller layout region than state-of-the-art commercial diagnosis. It is seen that PADLOC improves bounding circle diameter for 47.2% of fail logs, and achieves up to 44X improvement.

• NOIDA (<u>NO</u>ise-resistant <u>Intra-cell Diagnosis Approach</u>) concentrates on diagnosing a front-end defect, i.e., a defect that resides inside a standard cell [162]. It analyzes the standard cell candidates reported by LearnX/MD-LearnX. Rather than relying on an existing fault model or creating a new model via potentially inaccurate SPICE models, NOIDA derives the precise impact of a defect within the standard cell by monitoring the logical activity of its physical intra-cell neighborhood. The output of NOIDA is a set of intra-cell candidates, where each candidate is characterized with respect to its physical location inside the cell and its likely behavior.

A comprehensive simulation experiment is conducted to study the effectiveness of NOIDA. NOIDA is evaluated on over 34,000 front-end defects that are distributed over 115 standard cells within a 7nm standard-cell library.

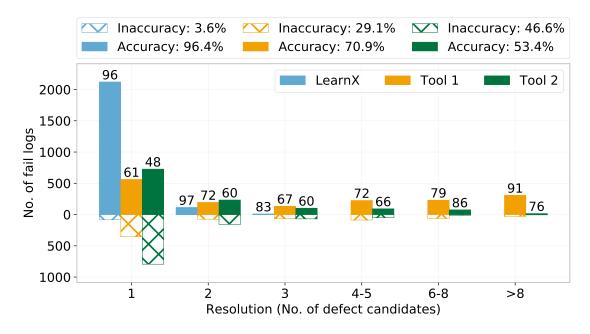

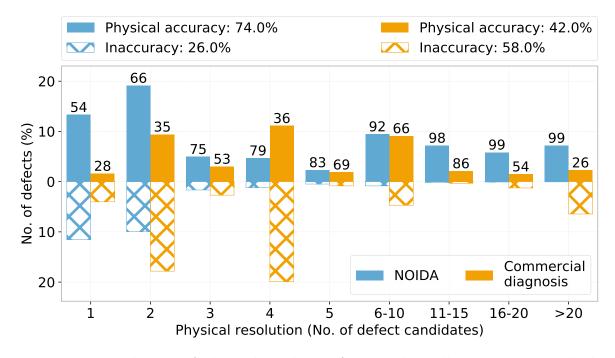

When each defective cell is exhaustively tested, NOIDA accurately diagnoses 96.6% of defects, which is an improvement of 17.7% over state-of-the-art commercial diagnosis. In addition, NOIDA reports an ideal diagnosis for 50.5% more defects.

When each defective cell is tested with a test set generated by a commercial ATPG tool, it is observed that the average accuracy for NOIDA is 100.0%, which is 21.8% better than commercial diagnosis. Among the defects diagnosed with a single candidate, NOIDA is correct for 38.0% more fail logs.

More importantly, NOIDA is robust to circuit-level noise (that might stem from approximate SPICE modeling) compared to leading-edge commercial diagnosis. Experiment results indicate that NOIDA correctly diagnoses 78.5% of the front-end defects, which is more than twice as often as commercial diagnosis. NOIDA returns an ideal diagnosis for 13.2% defects, which is 7.6X times commercial diagnosis.

### 1.3 Dissertation Organization

The rest of the dissertation is organized as follows. Chapter 2 describes LearnX, a physically-aware diagnosis methodology that concentrates on defect localization. It discusses LearnX while assuming that a single defect is residing in a failing chip. Chapter 3 extends that discussion to multiple defects, and presents a diagnosis methodology called MD-LearnX. Chapter 4 sheds light on PADLOC (Physically-Aware Defect Localization and Characterization), which specializes in characterizing a back-end defect candidate reported by LearnX/MD-LearnX with respect to its physical location and logic behavior. Chapter 5 elucidates NOIDA (Noise-resistant Intra-cell Diagnosis Approach), which pinpoints a physical location and derives the behavior of a defect candidate within a standard cell that is suspected to be failing as reported by LearnX/MD-LearnX. Each chapter critiques related prior work, and motivates the need for the development of the corresponding diagnosis methodology. The superior

performance attained by each diagnosis method over leading-edge commercial diagnosis is demonstrated with extensive simulation-based and silicon experiments. Finally, Chapter 6 emphasizes the main contributions of our work and provides promising directions for future work.

## Chapter 2

# LearnX: A Deterministic-Statistical Single Defect Diagnosis Methodology

The goal of software-based diagnosis is to determine the location, and ideally, the precise logic behavior of a defect. This goal is accomplished in multiple stages in this dissertation. This chapter focuses on the first stage of diagnosis, which is defect localization. This chapter describes a two-phase, physically-aware diagnosis method called LearnX to effectively localize a defect (and determine its type) in a failing chip.

The first stage of diagnosis, in particular, is significant because it affects the performance of the subsequent stages. The output of LearnX is used as an input to the back-end and the front-end layout analysis techniques (called PADLOC [146] and NOIDA [162], respectively) developed in this dissertation. As a result, any loss in the accuracy of LearnX directly impacts the effectiveness of PADLOC and NOIDA. Thus, the quality of defect localization achieved by LearnX is crucial to the success of our overall diagnosis methodology.

As alluded to earlier, LearnX is two-phase diagnosis approach. The first phase attempts to diagnose a defect that manifests as a well-established fault behavior (e.g., the stuck-at or bridge fault models). The second phase uses machine learning to build a model (separate for