# Reducing Performance Overhead of Direct Access NVM Storage Redundancy

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Department of Electrical and Computer Engineering

## Rajat Kateja

B.Tech., Mathematics and Computing, Indian Institute of Technology Guwahati

Carnegie Mellon University Pittsburgh, PA

May, 2020

© Rajat Kateja, 2020 All Rights Reserved Dedicated to my mother, Alpana Kateja.

#### Acknowledgments

It is always about the people. Reflecting on my graduate school experience, I value the people that made it all possible much more than the knowledge and skills I acquired.

In one of our first meetings, Greg asked me to think about how NVM devices are different from decades old battery-backed DRAM systems, a question that haunts me to this day. Over the years, Greg asked many such challenging questions and helped me develop a taste for novel research problems. In addition to research, he has also shaped my writing and presentation styles. Early on in my PhD, Greg's overnight (magic-like) transformations to paper intros left me wondering if I actually did the awesome work that the intros described. Over time, I picked up some writing skills, and although I am still working on improving my exposition, I am happy that my graphs now have Greg-approved thick-enough lines and big-enough fonts. Unfortunately, even with impeccable fonts, I faced one too many paper rejections, but his support helped me look beyond them. Through all the ups and downs, Greg has let me be in the driver's seat, be it in choosing paper deadlines or in choosing a career path. He helped me think through my decisions by going over the pros and cons of various options (sometimes spread across multiple meetings), but he never forced a particular decision. Although being the final decision maker was sometimes overwhelming, I am glad to have had that freedom. Thanks, Greg. for a wonderful graduate school experience.

The process of getting Andy and Nathan involved in my projects contributed significantly towards strengthening the motivation for this dissertation. Brainstorming sessions with them, along with Greg, were critical in finalizing the designs of Vilamb and Tvarak. Andy kept me on track by setting long term as well as weekly goals; this helped me make consistent progress and develop a work routine with a healthy work life balance that I still follow. Andy has also been incredibly helpful with his candid feedback on my writing, research, and job search. I thank Nathan for his patience as I learnt the ropes of computer architecture research, trade secrets of writing an architecture-y paper, and sometimes even basic computer architecture concepts. Nathan has also been generous with his time to discuss my career trajectory and helped me think through the decision of an industry vs academic job.

I thank Kim and Vijay for their time and effort as part of my thesis committee. The seeds of this dissertation were sown across multiple conversations, one of which was with Kim at FAST 2017. Thanks, Kim, for the many insightful discussions over the years. Although I haven't had the fortune of meeting Vijay in person yet, I have benefitted from his advice on Twitter, and thoroughly enjoyed the storage research from his group and interactions with his students. I look forward to meeting and learning more from him.

In addition to my committee members, I have received valuable guidance from my internship mentors and other faculty at CMU. Anirudh, Sriram, and Bikash helped me get started with NVM research at Microsoft, and Anirudh has continued to be a mentor throughout my PhD. Working with Niket and Mustafa at Google helped me understand the many practical challenges with NVM deployments, one of which this dissertation tries to address. I thank Phil for the amazing courses and for ever so often making time to guide me in my research, Michael Kozuch for his regular check-ins and feedback on my research, Saugata for his kind presence and mentorship throughout my PhD, Vyas for his career advice, Rashmi for the technical discussions, Ram for his technical and career guidance, and Garth, Majd, and George for the rewarding conversations.

The PDL, ECE, and CyLab staff—Karen, Chad, Mitch, Jason, Charlene, Joan, Bill, Nathan Snizaski, Brittany, Brigette, and Ivan—made my life easier and enabled me to focus on my work. Karen has helped me with almost every administrative aspect in the last five years, be it conference travels, expense reimbursements, reserving conference rooms, finding the right shirt size, or the awesome food in PDL group meetings. Chad, Mitch, and Jason have debugged numerous operational issues to help set up and start my experiments, and waived max-duration time-outs to ensure that they finish as well. Charlene's passion for life is something I hope to emulate. Joan's help and patience with posters makes me wonder how I would ever make a poster after leaving CMU. Of course, thanks to all the PDL staff for their herculean efforts towards the PDL retreats and visit days. These have been defining events year-after-year for me, and I'll dearly miss the PDL retreats.

I thank VMware and the companies of the PDL consortium—Alibaba, Amazon, Datrium, Facebook, Google, Hewlett Packard Enterprise, Hitachi, IBM Research, Intel, Micron, Microsoft Research, NetApp, Oracle, Salesforce, Samsung, Seagate, and Two Sigma—for funding this research. I thank my thesis committee—Greg Ganger (chair), Andy Pavlo, Nathan Beckmann, Kimberly Keeton, and Vijay Chidambaram—for supporting me through the PhD milestones.

My family has been pivotal in helping me reach this stage of my career. Thank you for the innumerable ways in which you have made this possible, right from teaching me physics and scolding me for my math to taking care of all my needs so that I can focus on my studies and trusting my career choices. In particular, I am indebted to my mother for her unshakable belief in me. For always putting me (and the family) before herself, I dedicate this dissertation to her.

I have had the fortune of having an amazing group of friends. Sahu, Joshi, Sachin, Garg, and Gupta have continued to spark joy in my life well beyond our undergrad. Meeting Joshi in Seattle was the highlight of my first year in graduate school, and trips with Sahu, Joshi, and Sachin provided much needed break over the years. Abhilasha was a constant presence and support during the bulk of my PhD; thank you for exploring Pittsburgh with me, for often being the only person I talked to in a day, and for being my best friend (at CMU). Ankur, Samarth, and Mansi made the last phase of my graduate school much more enjoyable with all the shared meals and movie nights. Thanks Ankur for the existential memes and never-ending topics, Samarth for the music, uno, and squash, and Mansi for the banana cakes and for bringing a positive balance to our cynical group discussions. I am glad that I met and got to spend time with Sruti, Vignesh, Amit, Ankush Desai, Sandeep, Sanghamitra, Raj, Rajshekhar, Dhivya, and Prashasti. Thank you Sruti for entertaining my drop-by visits to your desk (sometimes multiple in a day), Vignesh for the last minute help with my papers and for the regular check-ins about our research progress (or the lack thereof), Amit for easing my transition to CMU with our daily lunches, and Ankush for sharing your experiences and insights into graduate school during and after our Microsoft internship.

A special shout out to Madhuri for improving my overall well-being. Thank you for entertaining my stories (and giving me many new ones), for the silly puns and jokes, for breaking my over-thought life algorithms with unexpected inputs, for putting me back in touch with my priorities, and for the most happening summer of my life so far.

I thank my awesome PDL and CyLab colleagues—Aaron, Abutalib, Akarsh, Alexey, Andrew, Angela, Ankush Jain, Anuj, Cui, Dana, Hongyi, Jack, Janos, Jason, Jinliang, Kevin, Lianghong, Lin, Mahmood, Michael Kuchnik, Nandita, Niranjini, Pardis, Pratik, Rahul, Sara, Saurabh, Sindhoora, Soo-Jin, Thomas, Tian, Vivek, and Yixin—for their friendly presence. I have thoroughly enjoyed Aaron's dry humor that made CIC 2220 more lively and the deadline night-outs more bearable, learnings from Soo-Jin's approach to life and career, Saurabh's contagious passion for storage research, Jinliang's kind and supporting words during my job search, Niranjini's research and grocery/cooking advice, and exchanging notes with Angela about myriad things as we stepped through graduate school in lockstep.

Lastly, I would like to thank a whole bunch of content creators and characters for providing me on-demand entertainment. Thank you, Biswa Kalyan Rath, Kenny Sebastian, Rahul Dua, Rahul Subramanian, Anshu Mor, Aakash Mehta, Abhishek Upamanyu, Sahil Khattar, Sucharita Tyagi, Anupama Chopra, Aaron Marino, Jeff Cavaliere, Michael Scott, Walter White, Jesse Pinkman, and many others that I am currently forgetting.

#### Abstract

Non-volatile memory (NVM) based storage is poised for mainstream deployment. DIMM form-factor NVM devices reside on the memory bus and offer DRAM-like access granularities and latencies along with non-volatility. NVM's Direct Access (DAX) interface enables applications to map persistent data into their address space and access it with load and store instructions, eliminating system software overheads.

Production deployment of DAX NVM storage would require that the storage system offer resilience against firmware-bug-induced data corruption, akin to conventional storage systems. Protection against firmware-bug-induced data corruptions requires the storage system to maintain system-level redundancy, which we refer to as system-redundancy. With DAX interfacing, the lack of interposed system software makes it challenging to identify data reads and writes that should trigger system-redundancy verification and updates, respectively. Further, the DAX granularities (e.g., 64-byte cache-lines) are incongruent with typical system-redundancy granularities (e.g., 4K pages), leading to high performance overhead in maintaining system-redundancy.

This dissertation demonstrates that DAX NVM storage systems can efficiently maintain system-redundancy by relaxing the data coverage guarantees or by leveraging a hardware offload. We support the thesis with two case studies: Vilamb and Tvarak. The Vilamb library maintains system-redundancy asynchronously, avoiding critical path interpositioning and amortizes the overhead of system-redundancy updates across multiple writes to a page. As a result, Vilamb provides  $3-5\times$  the throughput of the state-of-the-art software solution at high operation rates. For applications that need system-redundancy with high performance, and can tolerate some delaying of data redundancy, Vilamb provides a tunable knob between performance and time-to-coverage. Even with the delayed coverage, Vilamb increases the mean time to data loss due to firmware-induced corruptions by up to two orders of magnitude in comparison to maintaining no system-redundancy.

Tvarak is a software-managed hardware offload to efficiently maintain systemredundancy for direct-access (DAX) NVM storage. Tvarak reconciles the mismatch between DAX granularities and typical system-redundancy granularities by introducing cache-line granular checksums (only) for DAX-mapped data. Tvarak also uses caching to reduce the number of extra NVM accesses for maintaining and verifying system-redundancy. Applications' data access locality leads to reuse of system-redundancy that Tvarak leverages with a small dedicated on-controller cache and configurable LLC partitions. Simulation-based evaluation demonstrates Tvarak's efficiency. For example, Tvarak reduces Redis set-only performance by only 3%.

# Contents

| 1        | Intr         | oducti  | on                                                         | 1        |

|----------|--------------|---------|------------------------------------------------------------|----------|

|          | 1.1          | Thesis  | statement                                                  | 2        |

|          | 1.2          | Contri  | ibutions                                                   | 3        |

|          | 1.3          | Outlin  | ie                                                         | 3        |

| <b>2</b> | Bac          | kgrour  | nd                                                         | <b>5</b> |

|          | 2.1          | 0       | Storage                                                    | 5        |

|          | 2.2          | DAX I   | NVM Storage Management                                     | 6        |

|          | 2.3          |         | adancy for Firmware Bug Resilience                         | 7        |

|          |              | 2.3.1   | Firmware-bug-induced data corruption                       | 7        |

|          |              | 2.3.2   | System-checksums for detection                             | 8        |

|          |              | 2.3.3   | Parity for recovery                                        | 10       |

|          |              | 2.3.4   | System-Redundancy for DAX NVM                              | 10       |

|          | 2.4          | Solutio | ons for DAX NVM System-Redundancy                          | 10       |

| 0        | <b>T</b> 7•1 |         |                                                            |          |

| 3        |              |         | low overhead asynchronous redundancy for direct-access NVM |          |

|          | stor         | -       |                                                            | 13       |

|          | 3.1          |         | b Design and Implementation                                | 14       |

|          |              | 3.1.1   | Asynchronous System-Redundancy                             | 14       |

|          |              | 3.1.2   | Repurposing Dirty Bits                                     | 15       |

|          |              | 3.1.3   | Failure Coverage                                           | 15       |

|          |              | 3.1.4   | Implementation                                             | 17       |

|          | 3.2          |         | ation                                                      | 19       |

|          |              | 3.2.1   | Key Evaluation Takeaways                                   | 20       |

|          |              | 3.2.2   | YCSB with Redis                                            | 20       |

|          |              | 3.2.3   | PMDK Key-Value Stores                                      | 22       |

|          |              | 3.2.4   | NVM Transaction Microbenchmarks                            | 23       |

|          |              | 3.2.5   | Fio Microbenchmarks                                        | 24       |

|          |              | 3.2.6   | Cost of Checking/Clearing Dirty Bits                       | 25       |

|          |              | 3.2.7   | Battery Capacity Requirements                              | 26       |

|          |              | 3.2.8   | Reliability Analysis                                       | 27       |

|          | 3.3          | Conclu  | usion                                                      | 28       |

| 4            | Tva                                     | rak: S | Software-managed hardware offload for redundancy in direct    | .—        |  |  |

|--------------|-----------------------------------------|--------|---------------------------------------------------------------|-----------|--|--|

|              | acce                                    | ess NV | /M storage                                                    | <b>29</b> |  |  |

|              | 4.1                                     | Tvara  | k Design                                                      | 30        |  |  |

|              |                                         | 4.1.1  | Tvarak's Goals and Non-Goals                                  | 30        |  |  |

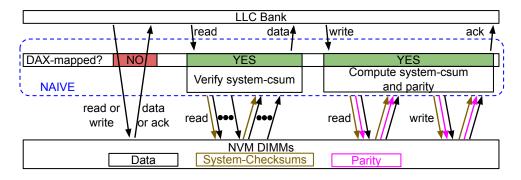

|              |                                         | 4.1.2  | Naive System-Redundancy Controller Design                     | 30        |  |  |

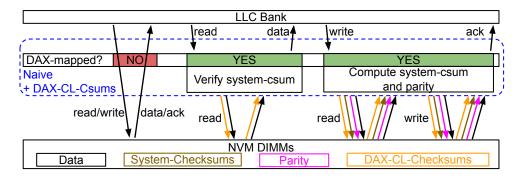

|              |                                         | 4.1.3  | Efficient Checksum Verification                               | 32        |  |  |

|              |                                         | 4.1.4  | Efficient Checksum and Parity Updates                         | 33        |  |  |

|              |                                         | 4.1.5  | Putting it all together with Tvarak                           | 34        |  |  |

|              | 4.2                                     | Evalu  | ation                                                         | 36        |  |  |

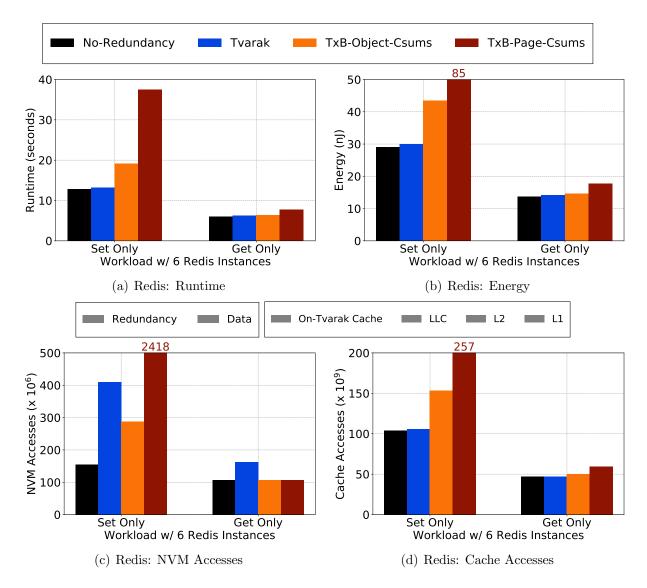

|              |                                         | 4.2.1  | Key Evaluation Takeaways                                      | 38        |  |  |

|              |                                         | 4.2.2  | Redis                                                         | 38        |  |  |

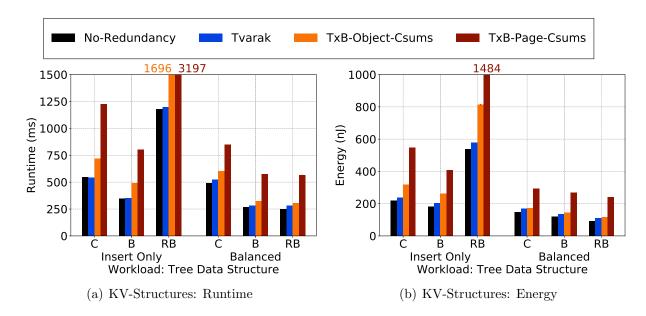

|              |                                         | 4.2.3  | Key-value Data Structures                                     | 40        |  |  |

|              |                                         | 4.2.4  | N-Store                                                       | 40        |  |  |

|              |                                         | 4.2.5  | Fio Microbenchmarks                                           | 42        |  |  |

|              |                                         | 4.2.6  | Stream Microbenchmarks                                        | 43        |  |  |

|              |                                         | 4.2.7  | Comparison with Vilamb                                        | 44        |  |  |

|              |                                         | 4.2.8  | Impact of Tvarak's Design Choices                             | 44        |  |  |

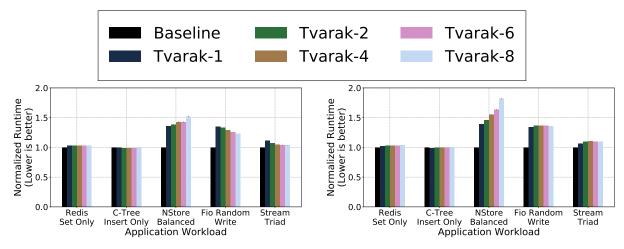

|              |                                         | 4.2.9  | Sensitivity Analysis                                          | 45        |  |  |

|              | 4.3                                     | Concl  | usion                                                         | 47        |  |  |

| <b>5</b>     | Con                                     | clusio | n and Future Directions                                       | 48        |  |  |

|              | 5.1                                     | Futur  | e Directions                                                  | 49        |  |  |

|              |                                         | 5.1.1  | Automated tuning of Tvarak's LLC partition sizes              | 49        |  |  |

|              |                                         | 5.1.2  | Study of firmware-bug-induced failures in NVM storage         | 49        |  |  |

|              |                                         | 5.1.3  | Extending Vilamb and Tvarak for cross machine DAX NVM storage |           |  |  |

|              |                                         |        | replication                                                   | 49        |  |  |

| $\mathbf{A}$ | Other Related Research of the Author 50 |        |                                                               |           |  |  |

# List of Figures

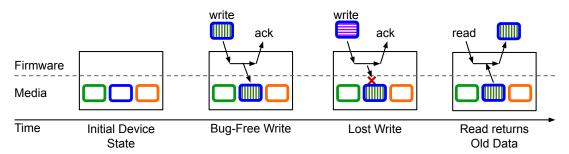

| 2.1  | Lost Write Bug Example.                                 | 8  |

|------|---------------------------------------------------------|----|

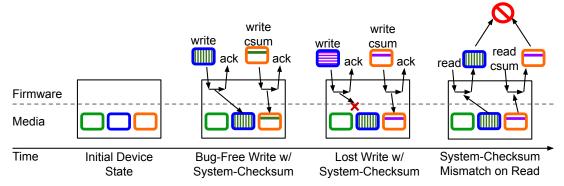

| 2.2  | Misdirect Write Bug Example                             | 9  |

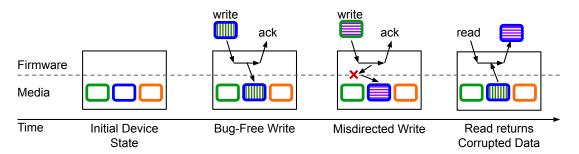

| 3.1  | Vilamb Delayed Checksum Computation Example             | 14 |

| 3.2  | Vilamb's Implementation                                 | 17 |

| 3.3  | Vilamb Evaluation: YCSB with Redis                      | 20 |

| 3.4  | Vilamb Evaluation: PMDK Key-Value Stores                | 22 |

| 3.5  | Vilamb Evaluation: PMDK Key-Value Stores                | 23 |

| 3.6  | Vilamb Evaluation: NVM Transaction Latencies            | 24 |

| 3.7  | Vilamb Evaluation: NVM Overwrite Throughput             | 25 |

| 3.8  | Vilamb Evaluation: Fio Microbenchmarks                  | 26 |

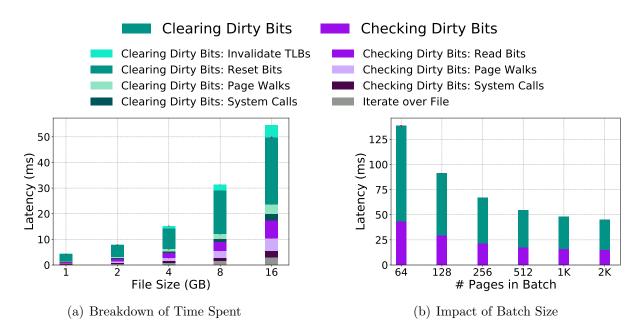

| 3.9  | Vilamb Evaluation: Cost of Checking/Clearing Dirty Bits | 27 |

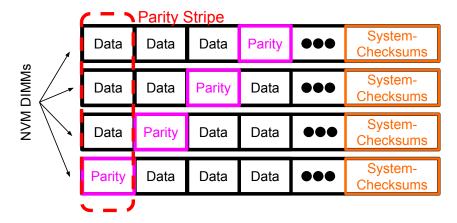

| 4.1  | System-redundancy Layout                                | 31 |

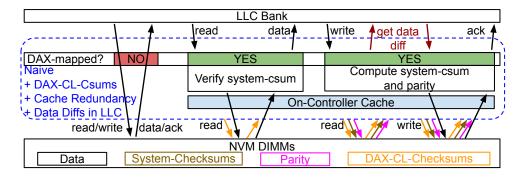

| 4.2  | Tvarak Naive System-Redundancy Controller Design        | 32 |

| 4.3  | Tvarak Efficient Checksum Verification                  | 33 |

| 4.4  | Tvarak Efficient Checksum and Parity Updates            | 34 |

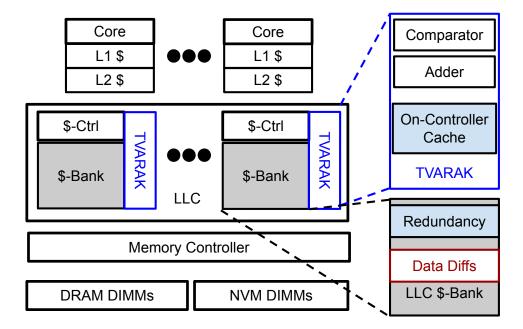

| 4.5  | Tvarak's Components                                     | 35 |

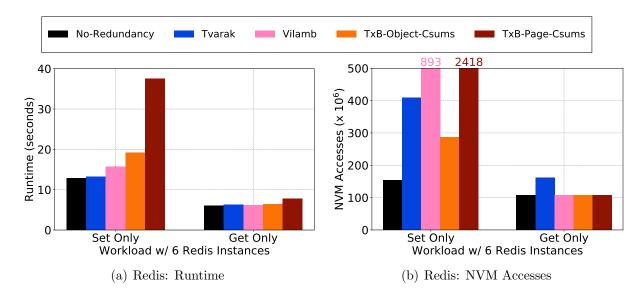

| 4.6  | Tvarak Evaluation: Redis                                | 39 |

| 4.7  | Tvarak Evaluation: PMDK key-value stores                | 41 |

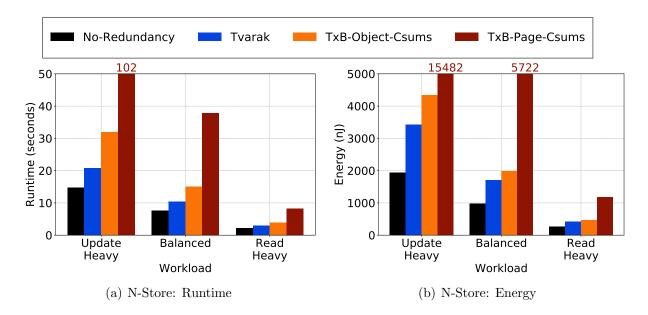

| 4.8  | Tvarak Evaluation: N-Store                              | 41 |

| 4.9  | Tvarak Evaluation: Fio Microbenchmarks                  | 42 |

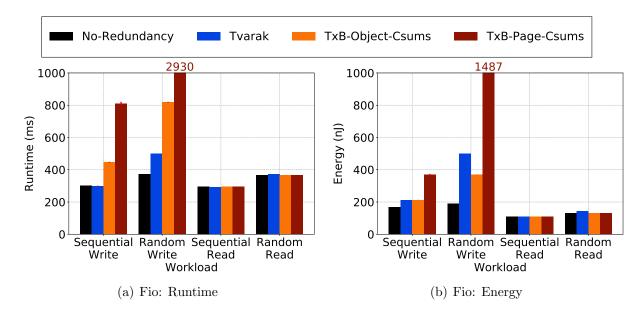

| 4.10 | Tvarak Evaluation: Fio Microbenchmarks                  | 43 |

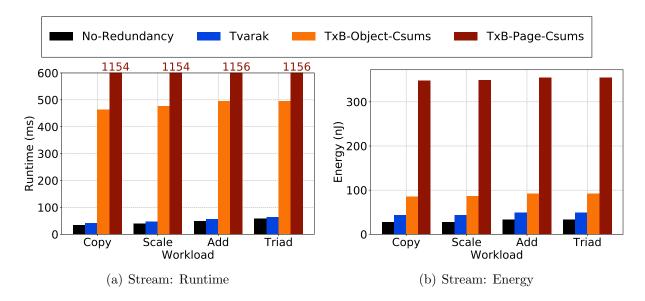

| 4.11 | Tvarak Evaluation: Comparison with Vilamb               | 44 |

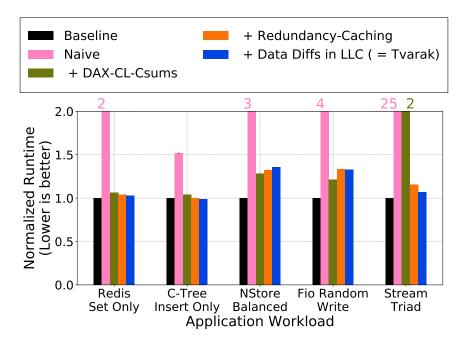

|      | Tvarak Evaluation: Impact of Tvarak's Design Choices    | 45 |

| 4.13 | Tvarak Evaluation: Sensitivity Study                    | 46 |

# List of Tables

| 2.1 | Solutions for DAX NVM storage system-redundancy and their trade-offs. | 11 |

|-----|-----------------------------------------------------------------------|----|

| 4.1 | Tvarak Evaluation: applications and their workloads                   | 36 |

| 4.2 | Tvarak Evaluation: Simulation Parameters                              | 37 |

# Chapter 1

# Introduction

Non-volatile memory (NVM) changes the way performance-sensitive applications interact with persistent data. NVM storage combines DRAM-like access latencies and granularities with disk-like durability [1, 15, 19, 56, 79]. Direct access (DAX) to NVM data exposes raw NVM performance to applications. Applications using DAX map NVM files into their address spaces and access data with load and store instructions, eliminating system software overheads associated with conventional storage interfaces.

Production storage demands more than just non-volatility and performance. A number of features that empower and simplify storage management efforts are also expected. Whereas some features extend to DAX NVM storage trivially, e.g., background scrubbing and defragmentation, others with data access inter-dependencies do not. Notably, redundancy mechanisms for fault tolerance fit poorly.

Production storage systems need to protect data from various failures. In addition to fail-stop failures like machine or device crashes, storage systems also need to protect data from silent corruption due to firmware bugs. Storage device firmware is prone to bugs because of its complexity, and these bugs can cause data corruption. Such corruption-inducing firmware bugs fall into two broad categories: lost write bugs and misdirected read or write bugs [11, 12, 43, 74, 90]. Lost write bugs cause the firmware to acknowledge a write without ever updating the data on the device media. Misdirected read or write bugs cause the firmware to read or write the data from the wrong location on the device media. Firmware-bug-induced corruptions go unnoticed even in the presence of device-level ECC, because the device-level ECC is read/written as an atom with its data during each media access performed by the firmware.

Protection against firmware-bug-induced corruption commonly relies on system-level redundancy, i.e., system-checksums for detection and parity for recovery. *System-checksums* are data checksums that the storage system computes and verifies at a layer "above" the device firmware (e.g., the file system), using separate I/O requests than for the corresponding data [11, 74, 105]. Using separate I/O requests for the data and the block containing its system-checksum (together with system-checksums for other data) reduces the likelihood of an undetected firmware-bug-induced corruption. This is because a bug is unlikely to affect both in a consistent manner. Thus, the storage system can detect a firmware-bug-induced corruption because of a mismatch between the data and its system-checksum. It can

then trigger recovery using the parity [51, 63, 68, 114]. In this paper, we use the term *system-redundancy* to refer to the combination of system-checksums and parity.

Production NVM-based storage systems will need system-redundancy mechanisms for the same reasons as conventional storage. NVM device firmware involves increasingly complex functionality, akin to that of other storage devices, making it susceptible to both lost write and misdirected read/write bugs. However, maintaining system-redundancy for DAX NVM storage, without forfeiting its performance benefits, is challenging for two reasons. First, accesses via load and store instructions bypass system software, removing the straightforward ability to detect and act on data changes (e.g., to update systemredundancy). Second, NVM's cache-line granular writes increase the overhead of updating system-redundancy (e.g., system-checksums) that is usually computed over sizeable data regions (e.g., pages) for effectiveness and space efficiency.

The state-of-the-art solutions for DAX NVM system-redundancy are transactional libraries that maintain system-checksums and parity [89, 109, 112]. To address the challenge of system software bypass, these libraries require applications to inform the library about all their data accesses. Although this enables the libraries to mediate and act on all application data accesses, it imposes a restrictive programming model. Furthermore, these solutions incur a high overhead even with optimized designs and implementations [109]. This is because library-based solutions struggle to synchronously update system-redundancy at high application write throughput rates.

## 1.1 Thesis statement

This dissertation describes our work on efficient implementation of system-redundancy mechanisms to protect DAX NVM storage from firmware-bug-induced data corruptions. In particular, we make the following thesis statement:

Direct access NVM storage can be fortified with conventional redundancy mechanisms for protection against firmware-bug-induced data corruptions at low performance overheads by relaxing the data coverage guarantees or by leveraging a hardware offload for systemredundancy computation and verification.

To support this thesis, we detail two case studies for improving the performance of DAX NVM storage redundancy:

Vilamb: Low overhead asynchronous redundancy for direct-access NVM storage (Chapter 3). Vilamb [50] provides efficient asynchronous system-redundancy for DAX NVM storage. The Vilamb user-space library maintains system-redundancy with low overhead by delaying and amortizing the system-redundancy update overhead across multiple data writes. To do so, Vilamb repurposes page table dirty bits to identify pages with outdated system-redundancy. As a result, Vilamb provides 3–5× the throughput of the state-of-the-art software solution, Pangolin [109], at high operation rates. For applications that need system-redundancy with high performance, and can tolerate some delaying of data redundancy. Even with the delayed coverage,

Vilamb increases the mean time to data loss due to firmware-induced corruptions by up to two orders of magnitude in comparison to maintaining no system-redundancy.

• Tvarak: Software-managed hardware offload for redundancy in directaccess NVM storage (Chapter 4). For DAX NVM applications with strong coverage requirements, Tvarak [49] efficiently implements synchronous system-redundancy with synchronous system-checksums and parity updates and system-checksum-verified reads. Software-only implementations of system-redundancy force a choice between reduced or delayed data protection and significant performance penalties. Offloading the update and verification of system-redundancy to Tvarak, a hardware controller co-located with the last-level cache, enables efficient protection of data from bugs in the memory controller and in NVM DIMM firmware. Simulation-based evaluation with seven data-intensive applications shows that Tvarak is efficient. For example, Tvarak reduces Redis set-only performance by only 3%.

# **1.2** Contributions

This dissertation makes the following key contributions.

#### Vilamb:

- It identifies asynchronous system-redundancy as an important addition to the toolbox of DAX NVM system-redundancy solutions.

- It describes Vilamb's efficient asynchronous system-redundancy design that improves performance for applications that can tolerate delayed coverage.

- It quantifies Vilamb's efficacy, cost, and reliability via extensive evaluation with eight macro- and micro-benchmarks.

#### Tvarak:

- It motivates the need for architectural support for DAX NVM storage systemredundancy, highlighting the limitations of software-only approaches.

- It proposes Tvarak, a low-overhead, software-managed hardware offload for DAX NVM storage redundancy. It describes the challenges for efficient hardware DAX NVM system-redundancy and how Tvarak overcomes these challenges with a straightforward, effective design.

- It reports on extensive evaluation of Tvarak's runtime, energy, and memory access overheads for seven applications, each under multiple workloads, showing its efficiency.

## 1.3 Outline

The remainder of this dissertation is organized as follows. Chapter 2 describes the background and motivation for this dissertation. It details the two broad classes of firmware bugs, presents system-redundancy as the protection mechanism, and describes the trade-offs across various DAX NVM system-redundancy solutions. Chapter 3 describes the design, implementation, and evaluation of Vilamb. Chapter 4 describes the design of Tvarak and its evaluation using the ZSim simulator [86]. Chapter 5 concludes this dissertation and presents some future research directions.

# Chapter 2

# Background

This section describes NVM storage and direct access interfacing, management features expected of production storage and implications of direct access on these features, redundancy mechanisms for protection against firmware-bug-induced corruptions, and the related work on supporting those features for DAX NVM storage.

# 2.1 NVM Storage

Non-volatile memory (NVM) refers to a class of memory technologies that have DRAM-like access latency and granularity but are also durable like disks. Various NVM technologies are already available or expected to be available soon [1, 19, 38, 56, 79]. NVM devices have orders of magnitude lower latency and higher bandwidth than conventional storage devices. This improved device performance benefits applications even with an unmodified storage stack, but more so with NVM-optimized storage stacks [8, 9, 22, 27, 44, 52, 103, 104].

The easiest way to incorporate NVM into systems is to export it to applications via existing file system interfaces. Doing so allows legacy applications to use NVM without modification. The downside is the performance overhead of system calls, data copying, and inefficient general-purpose system software code.

The DAX interface to NVM eliminates system software overheads, enabling applications to leverage raw NVM performance [27, 44, 49, 50, 57, 59, 62, 73, 81, 89, 96, 105, 109, 112]. With DAX, applications map NVM pages into their address spaces and access persistent data via load and store instructions. File systems that map a NVM file into the application address space (bypassing the page cache) on a mmap system call are referred to as DAX file systems and said to support DAX-mmap [27, 59, 105]. DAX is widely used for adding persistence to conventionally volatile in-memory DBMSs [57, 62, 73, 81, 112] and is poised as a "killer use-case" for NVM.

DAX-mmap helps applications realize NVM performance benefits, but requires careful reasoning to ensure data consistency. Volatile processor caches can write-back data in arbitrary order, forcing applications to use cache-line flushes and memory fences for durability and ordering. Transactional NVM access libraries ease this burden by exposing simple transactional APIs to applications and ensuring consistency on their behalf [14, 21,

36, 39, 97]. Alternatively, the system can be equipped with enough battery to allow flushing of cached writes to NVM before a power failure [66, 70, 113]; our work assumes this option.

## 2.2 DAX NVM Storage Management

Administrators rely on and expect a variety of storage management features to avoid data loss [31, 74, 87, 111], data theft [13, 46, 84, 102], reduce cost [23, 55, 75, 92, 115], and handle failures [31, 41, 51, 68, 69]. As NVM storage matures for use in production environments, it will be expected to provide these features as well.

We categorize storage management features into four groups based on their interrelationships with foreground data accesses (application reads and/or writes):

- Background scan/reorganization features, like scrubbing and defragmentation, occur independently of reads and writes.

- Space efficiency features, like compression, deduplication, and tiering, track data accesses to estimate data temperature; they can potentially impact read operations (e.g., when reading compressed data), but are unlikely to impact write operations because they operate on cold data.

- Data redundancy features like block checksums and cross-component redundancy are inter-dependent on writes; they may impact reads depending on how they are used (e.g., if reads require a checksum verification).

- Security features like encryption are directly involved in servicing of reads and writes.

Software bypass for direct access NVM storage has different implications for different categories of management features. For example, software bypass has no effect on purely background operations like scrubbing and defragmentation, because they do not depend on or impact any data accesses.

Space efficiency features track data access recency, but the loss of this information does not affect their correctness—only performance (e.g., if a hot page is compressed). Consequently, supporting them for direct access NVM is not overly complex. NVM storage systems can use page table accessed bits to track data accesses and not be concerned with occasionally losing this information (e.g., due to a power failure).

Data redundancy and security features have a strong dependency on write accesses—not knowing about data updates impacts their correctness. Data security features are also tightly coupled with read accesses (e.g., decryption) whereas data redundancy features may or may not be coupled with data reads (e.g., whether reads are verified). Given the tight coupling between security features and data accesses (both reads and writes), data security features demand hardware support. Introducing software encryption/decryption in the data path would annihilate the performance benefits of DAX NVM storage. Recent works have proposed memory-controller/-module support for NVM encryption [16, 60, 61, 106].

Data redundancy features will also benefit from hardware support, but can also be efficiently implemented in software if redundancy updates and verification can be moved out of the critical path. For example, if redundancy is verified only via background scrubbing, it would not longer impact application reads. However, state-of-the-art software-based approaches for redundancy rely on interposing on writes [89, 109, 112] in the critical path and introduce significant performance and programming limitations.

## 2.3 Redundancy for Firmware Bug Resilience

Production storage systems employ multiple redundancy mechanisms to address a variety of faults [31, 41, 51, 54, 65, 68, 69, 105, 110, 111]. In this work, we focus on redundancy mechanisms used to detect and recover from firmware-bug-induced data corruption (specifically, system-checksums and parity).

#### 2.3.1 Firmware-bug-induced data corruption

Large-scale studies of deployed storage systems show that device firmware bugs sometimes lead to data loss or corruption [11, 12, 43, 74, 90]. Device firmware, like any software, is prone to bugs because of its complex responsibilities (e.g., address translation, dynamic re-mapping, wear leveling, block caching, request scheduling) that have increased both in number and complexity over time. Research has even proposed embedding the entire file system functionality [47] and application-specific functionalities [2, 18, 82, 83, 100] in device firmware. Increasing firmware complexity increases the propensity for bugs, some of which can trigger data loss or corruption.

Corruption-inducing firmware-bugs can be categorized into two broad categories: lost write bugs and misdirected read/write bugs. A lost write bug causes the firmware to acknowledge a write without ever updating the media with the write request's content. An example scenario that can lead to a lost write is if a write-back firmware cache "forgets" that a cached block is dirty. Fig. 2.1(a) illustrates a lost write bug. It first shows (second stage in the time-line) a correct bug-free write to the block stored in the blue media location. It then shows a second write to the same block, but this one suffers from a lost write bug—the firmware acknowledges the write but never updates the blue media location. The subsequent read of the blue block returns the old data to the application.

A misdirected write or misdirected read bug causes the firmware to store data at or read data from an incorrect media location, respectively. Fig. 2.2(a) illustrates a misdirected write bug. As before, the first write to the block stored in the blue location is performed correctly by the firmware. For this example, the second write request shown is for the block stored in the green location. The second write request encounters a misdirected write bug wherein the data is incorrectly written to the blue media location. Notice that a misdirected write bug not only fails to update the intended block, but also corrupts (incorrectly replaces) the data of the block it incorrectly updates. In the example, the subsequent read to the block mapped to the blue location returns this corrupted data.

Although almost all storage devices maintain error-correcting codes (ECCs) to detect corruption due to random bit flips [24, 42, 94, 108], these ECCs cannot detect firmwarebug-induced corruption [11, 74]. Device-level ECCs are stored together with the data and computed and verified inline by the same firmware during the corresponding data access. So, in the case of a lost write, the firmware loses the ECC update along with the corresponding

(a) The problem: device responds to read of block that experienced the lost write with incorrect (old) data.

(b) The fix: having the higher-level system update and verify system-checksums when writing or reading data, in separate requests to the device, enables detection of a lost write because of mismatch between the data and the system-checksum.

Figure 2.1: Lost write bug example: Both sub-figures show a time-line for a storage device with three media locations. The device is shown in an initial state, and then upon completion of higher-level system's write or read to data (first, a successful write, then a "lost write", then a read) mapped to the same media location. Fig. 2.1(a) shows how the higher-level system can consume incorrect (old) data if it trusts the device to never lose an acknowledged write. Fig. 2.1(b) shows how the higher-level system can detect a lost write with system-checksums.

data update, because the data and ECC are written together on the media as one operation. Similarly, misdirected writes modify the ECC to match the incorrectly updated data and misdirected reads retrieve the ECC corresponding to the incorrectly read data.

#### 2.3.2 System-checksums for detection

Production storage systems maintain per-page system-checksums to detect firmware-buginduced data corruption. System-checksums are updated and verified at a layer above the firmware, such as the file system, stored in checksum pages (each containing checksums for multiple pages) separate from the data, and read and written using I/O requests separate from the corresponding data I/O requests [31, 54, 65, 105, 110, 111]. Separating the storage and accesses for data from corresponding system-checksums enables detection of firmware-bug-induced corruption, because such bugs are unlikely to affect both the data

(a) The problem: device responds to read with the incorrectly updated data from the blue location. Notice that the green location also has incorrect (old) after the misdirected write.

(b) The fix: having the higher-level system update and verify system-checksums when writing or reading data, in separate requests to the device, enables enables detection of a misdirected write because of mismatch between the data and the system-checksum.

Figure 2.2: Misdirected write bug example: Similar construction to Fig. 2.1, but with the second operation being a write intended for the green location that is misdirected by the firmware to the blue location.

and its system-checksum access. Even in an unlikely scenario that a bug that affect both the accesses, it is even more unlikely that the bug affects both in a consistent fashion (e.g., losing both or misdirecting both to another corresponding data and system-checksum pair) is even lower.

Fig. 2.1(b) demonstrates how system-checksums enable detection of lost writes. Although the second write to the blue block is lost, the write to the checksum block (stored in the orange location) is not. Thus, upon the data read in the example, which is paired with a corresponding system-checksum read and verification, the lost write is detected.

Fig. 2.2(b) illustrates how system-checksums enable detection of misdirected writes. A misdirected write firmware bug is extremely unlikely to affect both the data write to the green block and the corresponding system-checksum write to the orange block in a consistent manner. To do so, the firmware would have to incorrectly write the system-checksum to a location (block *and* the offset within the block) that stores the checksum for the exact block to which it misdirected the data write. In the illustration, the read of the blue block data, followed by its system-checksum read, results in a verification failure. Similarly, system-checksums also trigger a verification failure in case of a misdirected read

bug, because a bug is unlikely to affect the both the data its system-checksum read.

#### 2.3.3 Parity for recovery

To recover from a detected page corruption, storage systems store parity pages [41, 51, 63, 68, 69, 114]. Although parity across arbitrarily selected pages suffices for recovery from firmware-bug-induced corruption, storage systems often implement cross-device parity that enables recovery from device failures as well.

#### 2.3.4 System-Redundancy for DAX NVM

NVM storage systems will be prone to firmware-bug-induced data corruption and require corresponding redundancy mechanisms, akin to conventional storage systems. NVM firmware is susceptible to corruption-inducing bugs, because it is non-trivial and its complexity can only be expected to increase over time. NVM firmware already provides for address translation, bad block management, wear leveling, request scheduling, and other conventional firmware responsibilities [77, 78, 79, 88]. Looking forward, its complexity will only increase as more NVM-specific functionality is embedded into the firmware (e.g., reducing NVM writes and wear [17, 29, 61, 106, 116]) and as the push towards near-data computation [2, 4, 5, 18, 28, 35, 47, 82, 83, 100, 107] continues. Prior experience with firmwares of such complexity demonstrate that they inevitably suffer from bugs that lead to lost or misdirected reads and writes. Consequently, production NVM storage systems will need firmware-bug resiliency mechanisms.

Maintaining system-redundancy for DAX NVM is challenging for two reasons: (i) hardware controlled data movement, and (ii) cache-line granular writes.

Hardware Controlled Data Movement: Applications' data writes to DAX NVM bypass system software. This lack of software control makes it challenging for the storage software to identify updated NVM pages for which it needs to update system-redundancy.

**Cache-line Granular Writes**: Incongruence in the size of DAX writes and the size of pages over which system-redundancy is usually maintained increases the overhead of maintaining system-redundancy. Most storage systems maintain system-redundancy over sizeable blocks (e.g., 4K page checksums) for space efficiency. Cache-line granular writes require reading (at least) an entire page to update the system-redundancy. Whereas RAID systems solve a similar "small write" problem by reading the data before updating it [68], a DAX NVM storage system software cannot use this solution. As discussed above, direct access to NVM bypasses system software, prohibiting the use of pre-write values for incremental system-redundancy updates.

## 2.4 Solutions for DAX NVM System-Redundancy

Existing proposals for maintaining system-checksums and parity in NVM storage systems compromise on performance, coverage, and/or programming flexibility for DAX-mapped data. Table 2.1 presents the design choices of prior proposals as well as Vilamb and Tvarak.

| NVM Storage<br>Redundancy<br>Design   | Checksum<br>Granularity | Redundancy<br>Update for<br>DAX data | Redundancy<br>Verification for<br>DAX data | Performance<br>Overhead | Programming<br>Model               | Specialized<br>Hardware<br>Requirement |

|---------------------------------------|-------------------------|--------------------------------------|--------------------------------------------|-------------------------|------------------------------------|----------------------------------------|

| Nova-Fortis [105],<br>Plexistore [71] | Page                    | No updates                           | No verification                            | None                    | FS Interface                       | None                                   |

| Mojim [112],<br>HotPot [89]           | Page <sup>1</sup>       | On application<br>data flush         | Scrubbing                                  | High                    | Transactional<br>Library Interface | None                                   |

| Pangolin [109]                        | Object                  | On application<br>data flush         | On NVM to<br>DRAM copy                     | Moderate/High           | Transactional<br>Library Interface | None                                   |

| Vilamb                                | Page                    | Periodically                         | Scrubbing                                  | Configurable            | No Restriction                     | None                                   |

| Tvarak                                | Page                    | On LLC to<br>NVM write               | On NVM to<br>LLC read                      | Low                     | No Restriction                     | Specialized<br>Controller              |

Table 2.1: Solutions for DAX NVM storage system-redundancy and their trade-offs.

Two recent fault-tolerant NVM file systems, Nova-Fortis [105] and Plexistore [71], update and check system-redundancy during explicit file system calls but do not update or verify redundancy while data is DAX mapped.

Pangolin [109] is a user-space library that maintains DAX NVM system-redundancy synchronously by requiring applications to explicitly inform it about their data updates; applications piggyback these notifications on Pangolin's transactional interface. Pangolin offers strong coverage (immediate system-redundancy updates and verification) and does not require any specialized hardware resources (because it is a software-based solution). Pangolin addresses the mismatch of fine-grained DAX updates with large checksum ranges by requiring explicit object definitions and maintaining per-object checksums instead of per-page checksums. Pangolin also introduces micro-buffering, i.e., buffering objects that an application writes to in DRAM and updating the NVM only on transaction commits. This buffering also enables Pangolin to use data diffs to make system-redundancy updates more efficient.

Pangolin is well-tuned, including several overhead-reducing mechanisms, making it the state-of-the-art for an in-line software-only solution. Yet, Pangolin incurs significant performance overhead (up to 80%) in many cases. Fundamentally, Pangolin's synchronous system-redundancy update design requires updating system-redundancy at the same rate at which an object is being modified; this becomes costly for the high update rates enabled by NVM. Furthermore, Pangolin only works for applications that can be and are modified to use its object-based transactional interface. Applications that manage NVM data themselves using other data models, such as NVM-optimized databases [8], may not easily fit to Pangolin's interface. Pangolin's per-object checksums also incur higher space overhead for small data objects.

Mojim [112] and HotPot [89] are also library based solutions similar to Pangolin. They were developed for remote replication in DAX NVM but their design can be extended to include system-redundancy. Their interposing based design imposes the same programming restrictions as Pangolin because applications need to inform them about all application writes. Furthermore, their page granular system-checksums incur a even higher overhead

$<sup>^1</sup>$  The original Mojim and HotPot designs do not include checksums, only replication. Here we extrapolate their design to include checksums.

because of the fine-grained applications writes (Section 2.3.4).

Vilamb [50] is a software library that embraces an asynchronous approach to updating system-redundancy for updated data. Like other asynchronous redundancy-update approaches, it identifies and completes required system-redundancy updates in the background. Vilamb does not impose any programming model restrictions and does not require any specialized hardware resources. However, Vilamb reduces the data coverage guarantees by delaying system-redundancy updates. Specifically, recently modified pages may not be covered when a firmware bug affects them. Vilamb is a good option for applications that desire high performance and/or are not a good fit for Pangolin-like API and view partial system-redundancy coverage is as better than none.

**Tvarak** [49] is a hardware controller co-located with the last-level cache (LLC) that the file system can offload system-redundancy maintenance work onto. Tvarak is able to identify data updates by the virtue of being interposed in the data path. Tvarak offers synchronous system-redundancy updates and verification, does not restrict applications to any specific library/API, and is low-overhead.

# Chapter 3

# Vilamb: Low overhead asynchronous redundancy for direct-access NVM storage

This chapter describes **Vilamb**<sup>1</sup> [50], a user-space library for efficient asynchronous DAX NVM system-redundancy. Vilamb moves system-redundancy updates out of the critical path and delays them to amortize the overhead over multiple data updates. Delaying the system-redundancy updates creates a configurable trade-off between performance and the delay before updated data is covered.

Vilamb repurposes page table dirty bits to efficiently identify of data updates. Vilamb marks pages with updated system-redundancy as clean and identifies pages with invalidate system-redundancy by checking their dirty bit. We implement a kernel module that Vilamb uses for batched fetching and clearing for dirty bits. Vilamb ensures atomic and consistent system-redundancy updates for all dirty pages by using shadow copies of dirty bits and leveraging batteries that are common in production environments [26, 32, 45, 48, 53, 67, 98, 99].

For applications that can tolerate delayed data coverage, Vilamb offers an efficient alternative to synchronous software based redundancy without requiring specialized hardware. Extensive evaluation with eight macro- and micro-benchmarks demonstrate Vilamb's efficacy. Vilamb with a 1 second delay between system-redundancy updates reduces single-threaded Redis' YCSB throughput by only 1.6–17%, compared to 13–18% for Pangolin. Increasing the delay to 10 seconds further reduces Vilamb's overhead to 0.1-6%. Vilamb offers  $3-5\times$  higher throughput than Pangolin at high insert rates for all five of Intel's persistent memory development kit (PMDK) key-value stores. By protecting data that belongs to clean stripes from firmware-bug-induced corruptions, Vilamb increases the mean time to data loss (MTTDL) over maintaining no system-redundancy. For example, Vilamb with a 1 second system-redundancy update period increases Redis' MTTDL by  $15\times$  and  $74\times$  over No-Redundancy for a write-heavy and ready-heavy YCSB workload, respectively. Detailed timing breakdowns with fio microbenchmarks and battery cost analysis confirm

<sup>&</sup>lt;sup>1</sup>Vilamb means delay in Hindi.

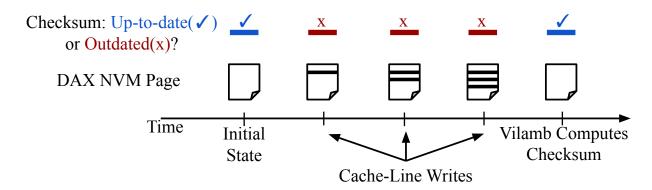

Figure 3.1: Delayed Checksum Computation Example: By computing per-page systemchecksums asynchronously, Vilamb amortizes the computation overhead over multiple cache-line writes to the same NVM page.

Vilamb's design decisions.

## 3.1 Vilamb Design and Implementation

This section begins by describing Vilamb's design elements: delayed system-redundancy updates and repurposing of dirty bits. It then describes the effect of Vilamb's design on resilience against different failures and ends with Vilamb's implementation details.

#### 3.1.1 Asynchronous System-Redundancy

Vilamb asynchronously maintains per-page system-checksums and cross-page parity for DAX NVM storage. A background thread periodically updates system-redundancy for pages which have been written to since Vilamb last updated their system-redundancy. By delaying system-redundancy updates, Vilamb amortizes the overhead over multiple cache-line writes to the same DAX NVM page.

Fig. 3.1 illustrates how Vilamb reduces work for per-page system-checksums (cross-page parity is not shown in the example, but is updated at the same time as the system-checksum). The figure shows a DAX NVM page and its system-checksum; the system-checksum can either be up-to-date ( $\checkmark$ ) or outdated (x). In the initial state, the system-checksum is up-to-date with the data. The first write to the page makes the system-checksum stale. Instead of updating the checksum immediately, Vilamb delays the update until after two more writes. By delaying the update Vilamb performs a single checksum (and parity, not shown in the example) computation, instead of three.

Vilamb scrubs the data using a separate background thread to detect data corruption. Upon mismatch between the page data and system-checksum for a clean page, Vilamb raises an error and halts the program. The OS can recover corrupted pages using the parity pages, with potential re-mapping to different physical pages [105, 109].

#### 3.1.2 Repurposing Dirty Bits

The conventional use-case of dirty bits is irrelevant for DAX NVM pages, making them available for repurposing. The dirty bit is conventionally used to identify updated, or "dirtied", in-memory pages that the storage system needs to write back to persistent storage. In case of DAX NVM storage, the file system maps NVM-resident files into application address spaces using the virtual memory system [27, 59]. Consequently, even though each mapped page has a corresponding dirty bit, the conventional semantic of these dirty bits is irrelevant because the pages already reside in persistent NVM storage.

Vilamb repurposes dirty bits to identify pages that have been written to since Vilamb last updated their system-redundancy. When a file is first DAX mapped, its pages' dirty bits are clear and system-redundancy is up-to-date (potentially updated during initialization for newly created files). A page write, which causes its system-redundancy to become stale, sets the page's dirty bit. In each successive invocation, Vilamb's background thread updates the system-redundancy for pages with their dirty bit set and then clears the corresponding dirty bits again.

Shadow Dirty Bits: Vilamb carefully orchestrates the non-atomic two-step process of updating a page's system-redundancy and clearing its dirty bit; performing these steps without any safeguard is incorrect. Clearing the dirty bit after updating the systemredundancy is incorrect because an interleaved application access can invalidate the systemredundancy. Reversing the order is not safe either. A system-checksum verification (e.g., in a scrubbing thread) after the dirty bit is cleared, but before the system-checksum is updated, would cause a spurious mismatch between the data and its system-checksum. Vilamb makes a persistent shadow copy of the dirty bit before clearing it, and clears this shadow copy only after completing the redundancy update. If either of the dirty bit or its shadow copy is set for a page, Vilamb knows that the page's redundancy is outdated.

Impact of Huge Pages: Huge pages are detrimental to Vilamb's performance. For each dirty page, Vilamb needs to read the entire page to compute its system-checksum and read other pages in its stripe to compute their cross-page parity. With huge pages, the amount of data that Vilamb has to read increases, increasing Vilamb's overhead for maintaining system-redundancy. If and when huge pages become more prevalent, Vilamb would need alternative mechanisms to track updated data. Potential options include architectural modifications to maintain multiple finer-granularity dirty bits per-huge-page, or tracking data writes using a Pangolin-like scheme that requires application modifications [109]. We leave this exploration for future work.

#### 3.1.3 Failure Coverage

Vilamb's asynchronous approach to system-redundancy introduces a tunable window of vulnerability. Pages that an application writes to remain susceptible to corruption until Vilamb updates their system-redundancy. We describe the implication of this window of vulnerability for different kinds of failures below.

**Page Corruption**: System-redundancy's primary goal is to protect data from firmwarebug-induced corruption. Additionally, system-redundancy also protects from random bit flip induced corruptions, though on-device ECC is already expected to address those. Vilamb's delayed system-checksums would detect corruption to all but recently written (dirty) pages. We illustrate this with an example lost write bug triggered in three different scenarios.

Consider a firmware that uses an on-device write-back cache and that suffers from a bug wherein the firmware (infrequently) "forgets" to destage some data from the cache to the device media.

- For the first scenario, consider an application write that is evicted from the CPU caches to the NVM device, is stored in the on-device write-back cache, and then lost by the firmware before Vilamb updates the corresponding page's system-checksum. This would lead to a silent corruption because Vilamb would use the incorrect (old) data to compute the system-checksum.

- For the second scenario, consider that Vilamb updates the page's system-checksum before the firmware bug is triggered (i.e., while the data is in the CPU caches or in the on-device cache). Vilamb would update the system-checksum correctly in this scenario and detect the subsequent corruption because of a data-system-checksum mismatch at a later point.

- For the third scenario, imagine the bug affects a clean page while the firmware is performing wear leveling. Vilamb would be able to detect this data loss in its scrubbing thread.

Among the pages that Vilamb detects as corrupted, Vilamb can recover those that belong to stripes with all clean pages (and hence, an up-to-date parity). Any dirty page in a stripe invalidates the parity. Thus, even if the corrupted page is itself clean, Vilamb can recover it only if all other pages in its stripe are also clean.

**Power Failures**: Vilamb avoids any inconsistencies between data and its systemredundancy by ensuring that the system-redundancy is made up-to-date if there is a power failure. To that end, Vilamb leverages battery backups that are common in production environments [26, 32, 33, 45, 48, 53, 98]. Conventional storage systems use batteries to flush DRAM to a persistent medium upon a power failure [26, 33, 45, 48]. NVM does not need batteries to make its contents persistent because they are already persistent. Vilamb instead leverages the battery backup to update system-redundancy upon a power failure, ensuring that no pages are left uncovered. Given that batteries are and will continue to be used to address other issues as well, e.g., brief power losses and spikes [67], Vilamb can exploit them for updating system-redundancy.

**NVM DIMM Failures or Machine Failures**: Vilamb's system-redundancy is not intended for protection against DIMM or machine failures; the storage system can protect against these using remote replication [89, 112]. Being a machine-local fault-tolerance mechanism, system-redundancy, independent of its implementation, is ineffective against machine failures. For DIMM failures, Vilamb's asynchronous system-redundancy design makes it unable to reconstruct the fraction of the pages in the failed DIMM that belonged to a stripe with outdated system-redundancy. Although the storage system could still recover a large fraction of the data (Section 3.2.8), it would need other redundancy to recover the remaining data.

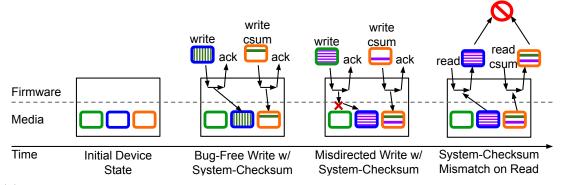

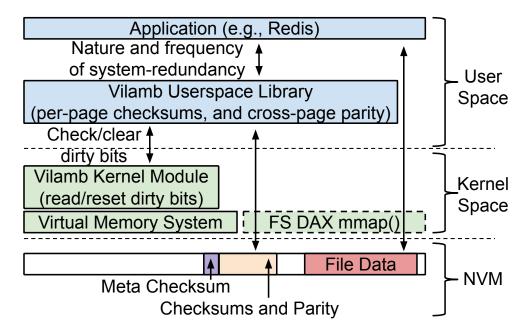

Figure 3.2: Vilamb's Implementation: The user space library performs the system-checksum and parity computations with a period that is set by the application. The kernel module checks and clears the dirty bits when requested by the user space library.

#### 3.1.4 Implementation

We implement Vilamb as a user-space library. The library exposes an API that applications can use to configure the nature of system-redundancy (e.g., type of checksum and number of pages in a stripe) and its update frequency. The library uses a periodic background thread that checks and clears the dirty bits using new system calls that we implement, and performs the system-redundancy updates for the dirty pages. Our implementation uses a stripe size of five pages by default, with four consecutive data pages and one parity page. The stripes are statically determined at the time of initialization. Fig. 3.2 shows the components of our implementation.

New System Calls: We implement two new system calls, getDirtyBits and clearDirtyBits, to check and clear the dirty bits for pages in a memory range, respectively. getDirtyBits returns a bitvector that has the dirty bits for pages in the input memory range. clearDirtyBits accepts a dirty bitvector as its parameter in addition to a memory range. It clears the dirty bit for a page in the memory range only if the corresponding bit is set in the input dirty bitvector. Since Vilamb is unaware of pages dirtied in between the checking and clearing and will not update their system-redundancy, it uses this input dirty bitvector for clearDirtyBits to clear the dirty bits only for pages that were dirty when initially checked.

**Batched Checking and Clearing**: Vilamb checks and clears dirty bits for multiple NVM pages (e.g., 512 in our experiments) as a batch for efficiency. Both checking and clearing of dirty bits require a system call and traversing the hierarchical page table; clearing

| Algorithm | 1: | System-R | edundancy | Update | Thread |

|-----------|----|----------|-----------|--------|--------|

|-----------|----|----------|-----------|--------|--------|

| 8                                                         |  |  |  |  |  |

|-----------------------------------------------------------|--|--|--|--|--|

| Parameter: Batch Size, B pages                            |  |  |  |  |  |

| <b>Parameter</b> : Number of Pages in File, N             |  |  |  |  |  |

| Parameter: Number of Pages in a Parity Group, P           |  |  |  |  |  |

| for $i \leftarrow 0$ to N increment by B do               |  |  |  |  |  |

| dirtyBitvector $\leftarrow$ checkDirtyBits( $i, i + B$ ); |  |  |  |  |  |

| dirtyBitvectorCopy $\leftarrow$ dirtyBitvector;           |  |  |  |  |  |

| $currentBatchStartingPage \leftarrow i;$                  |  |  |  |  |  |

| memoryFence;                                              |  |  |  |  |  |

| clearDirtyBits(i, i + B, dirtyBitvector);                 |  |  |  |  |  |

| for $j \leftarrow i$ to $i + B$ increment by $P$ do       |  |  |  |  |  |

| for $k \leftarrow j$ to $j + P$ increment by 1 do         |  |  |  |  |  |

| updateParity $\leftarrow$ False;                          |  |  |  |  |  |

| if bitIsSet(dirtyBitvector, $k - i$ ) then                |  |  |  |  |  |

| updateParity $\leftarrow$ True;                           |  |  |  |  |  |

| <pre>computePageChecksum(k);</pre>                        |  |  |  |  |  |

| end                                                       |  |  |  |  |  |

| end                                                       |  |  |  |  |  |

| if updateParity then                                      |  |  |  |  |  |

| computeParity $(j, j + P);$                               |  |  |  |  |  |

| end                                                       |  |  |  |  |  |

| end                                                       |  |  |  |  |  |

| memoryFence;                                              |  |  |  |  |  |

| dirtyBitvectorCopy $\leftarrow 0;$                        |  |  |  |  |  |

| end                                                       |  |  |  |  |  |

| computeMetaChecksum();                                    |  |  |  |  |  |

|                                                           |  |  |  |  |  |

dirty bits further requires invalidating the corresponding TLB entries. Each of these is a costly operation, as evinced by prior research [6], and demonstrated by our experiments (Section 3.2.6). Batching allows pages to share the system call, fractions of the page table walk, and the TLB invalidation. We found that batching reduced the amount of time spent in checking and clearing dirty bits by up to two orders of magnitude.

Algorithm: Algorithm 1 details the steps that Vilamb's background thread performs on each invocation. Vilamb loops over all the N pages in a given DAX NVM file in increments of B pages; B being the batch size for which Vilamb checks the dirty bits using a single system call (Line 2). Vilamb stores a persistent shadow copy of the dirty bits (Line 3) and then clears them (Line 6). Vilamb updates the system-checksum of each dirty page (Line 12), and the parity of a group of P pages if either of them is dirty (Line 16). Vilamb stores the system-checksums and parity separately from the data (Fig. 3.2) and then clears the shadow copy of the dirty bits (Line 20). Vilamb then updates a meta-checksum (checksum of the page system-checksums) after every iteration (Line 22 and Fig. 3.2).

As a performance optimization, instead of storing a shadow copy of the dirty bit for each page, we use a single dirty bitvector of size B along with the current batch's starting page number (Line 3 and Line 4). Together, the starting page number and the dirty bitvector copy suffice to store shadow copies of the dirty bits for pages in the current batch; pages not in the current batch do not need a shadow copy of their dirty bits because their dirty bits are not being cleared. Having a single dirty bitvector improves performance by reducing cache pollution.

Vilamb's system-redundancy verification thread (i.e., the scrubbing thread) computes and verifies the checksum only for pages that are clean, i.e., they have neither their dirty bit nor their shadown dirty bit set. If the system-checksum verification succeeds, the thread moves to the next page. In case of a system-checksum mismatch, the scrubbing thread re-checks whether the page is clean. This second check is to ensure that the page was not modified after the first check but before the system-checksum verification. If the second check also indicates that the page is clean, the scrubbing thread raises a signal to halt the application. The file system can then recover the page, if it belongs to a clean stripe (we have not implemented recovery).

Leveraging Hardware Support: Our implementation of Vilamb leverages hardwaresupport whenever possible. We use CRC-32C checksums and employ the crc32q instruction when available. Similarly, we use SIMD instructions for computing the parity whenever possible (e.g., by operating on 256-byte words in our experiments). We never flush cachelines for persistence because we assume battery-backed servers. We do, however, use fences to ensure ordering between updates. For example, the fence at Line 5 ensures that the shadow copy of the dirty bits and current batch's starting page number writes are completed before the dirty bits are cleared. Similarly, the fence at Line 19 ensures that system-redundancy is written before the dirty bits' shadow copy is cleared. We extend the same performance benefits (e.g., no cache-line flushes and SIMD parity computations) to the alternatives that we compare Vilamb with in our evaluation.

## 3.2 Evaluation

This section evaluates Vilamb and compares it to No-Redundancy and Pangolin, using eight macro- and micro-benchmarks. No-Redundancy serves as the baseline, providing the best performance but not implementing any system-redundancy. Pangolin is a state-of-the-art userspace library that updates system-redundancy when applications commit their data writes to NVM.

We obtained Pangolin's code from the authors and run it with system-checksum and parity updates enabled but system-checksum verification disabled (referred to as Pangolin-MLPC in the Pangolin paper [109]). We run Vilamb also with system-checksum and parity updates enabled and scrubbing (for background system-checksum verification) disabled. As shown in the evaluation of Pangolin [109], and confirmed by our experiments, systemchecksum verification via scrubbing at reasonable frequencies incurs negligible overhead. Pangolin can also verify system-checksums on object reads, which Vilamb cannot, but doing so reduces throughput by up to 50% for large objects [109].

Unless mentioned otherwise, Vilamb uses a 512-page batch size for checking/clearing dirty bits. To accurately quantify Vilamb's overheads, we pin it to the same core(s) as the application. For single threaded applications such as Redis, this means that the application and Vilamb run on the same logical core (i.e., same hyper-thread). Each data point in our results is an average of three runs with root mean square error bars. We use a dual-socket Intel Xeon Silver 4114 machine with Linux 4.4.0 kernel with 4K pages for our experiments. The system has 192 GB DRAM, from which we use 64 GB as emulated NVM [72].

#### 3.2.1 Key Evaluation Takeaways

Key takeaways from our evaluation include:

- Vilamb is low-overhead. For example, Vilamb with a 10 second system-redundancy update period reduces Redis' YCSB throughput by only 0.1–6% in comparison to No-Redundancy.

- Vilamb significantly outperforms Pangolin. For example, Vilamb has 3–5× higher insert throughput than Pangolin for five PMDK key-value stores. Even for low throughput applications like single threaded Redis serving YCSB, Vilamb has up to 18% higher throughput than Pangolin.

- Vilamb significantly increases the MTTDL. For example, Vilamb increases the MTTDL for PMDK key-value stores by up to two orders of magnitude.

- Vilamb offers a tradeoff between performance and time-to-coverage. For example, decreasing the delay between system-redundancy updates from 5 second to 1 second increases Redis' YCSB-A MTTDL by 3× but decreases the throughput by 10%.

- Vilamb's battery requirements are low. Across all of our workloads, the cost of batteries that Vilamb requires never exceeds \$10.

#### 3.2.2 YCSB with Redis

Redis [80] is a widely used open-source NoSQL DBMS. We modify it to use a DAX NVM file for its data heap. Our implementation uses the libpmemobj library [37] from the Intel persistent memory development kit (PMDK) [39] for No-Redundancy.

Modifying Redis to use Vilamb and Pangolin: For Vilamb, we added 10 lines of initialization and cleanup code in one file. The initialization code registers Redis' NVM heap with Vilamb and sets the system-redundancy update delay. To use Pangolin's transactional API (which is similar to but different than libpmemobj), we changed 346 lines of code across 10 files in Redis. Whereas most of these changes were to the transactional interface (e.g., using pgl\_tx\_begin), we also had to modify Redis to invoke Pangolin before reading

data from an object (using pgl\_get). Doing so enables Pangolin to determine whether the object is in NVM or in DRAM and provide Redis with the correct pointer.

**Experimental Setup**: We use three core YCSB workloads: YCSB-A (50:50 reads:updates), YCSB-B (95:5 reads:updates), and YCSB-C (read-only). We initialize the DBMS with 1M  $(1 \times 2^{20})$  key-value pairs for a NVM footprint of 10 GB and run the workloads for five minutes. The YCSB workload generator uses 20 threads and runs on a different socket than Redis.

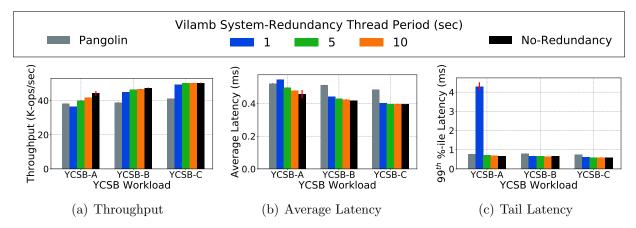

**Results**: Fig. 3.3 presents throughput and read latencies. Vilamb reduces the throughput, in comparison to No-Redundancy, by 0.1–6% for a system-redundancy update period of 10 second and by 1.6–17% for a period of 1 second. Increasing the delay for system-redundancy updates improves Vilamb's performance because it performs fewer system-redundancy updates and hogs less CPU. With aggressive system-redundancy updates every second, Vilamb increases the tail latency for YCSB-A because it stalls Redis while updating system-redundancy on the same core. This effect can be mitigated if Vilamb and Redis were to run on separate cores.

Pangolin's throughput is 13–18% lower than No-Redundancy, with a higher overhead for more read-heavy workloads. In addition to the overhead of updating system-redundancy, Pangolin incurs overhead because of two other factors, both related to its micro-buffering design. First, on every object read, Pangolin probes a cuckoo hash table to check whether the latest copy of the object is in a DRAM micro-buffer or in NVM. Second, when Redis adds an object to a transaction, Pangolin copies the entire object to DRAM for micro-buffering, rather than just the modified data ranges.

For the write-heavy workload YCSB-A, Pangolin outperforms Vilamb with a systemredundancy update period of 1 second. This is because Pangolin's micro-buffering design enables it to perform system-checksum and parity updates using the diff of the updated data. Pangolin uses the new data in the DRAM micro-buffer and the old data in the NVM to compute the data diff. In contrast, Vilamb has to read the entire page to update the system-checksum, and also read other pages in the stripe to update the parity. With 5 and 10 second system-redundancy update periods, Vilamb outperforms Pangolin by 5–7%.

For read-heavy workloads YCSB-B and YCSB-C, Vilamb reduces the throughput marginally (e.g., less than 2% for YCSB-C) whereas Pangolin reduces the throughput by 18%. This is because even though the number of system-redundancy updates reduce, Pangolin continues to incur the additional overheads described above. For example, Pangolin has to check whether the data is in DRAM or NVM for object reads.

Pangolin's moderate overhead (up to 18%) compared to No-Redundancy and Vilamb is an artifact of Redis' inefficiencies. In particular, Redis' single-threaded design causes it to have low performance (tens of thousands of operations per second) that does not fully expose the system-redundancy update overheads. In the next section, we show that multi-threaded key-value stores that perform millions of operations per second benefit significantly from Vilamb's asynchronous approach.

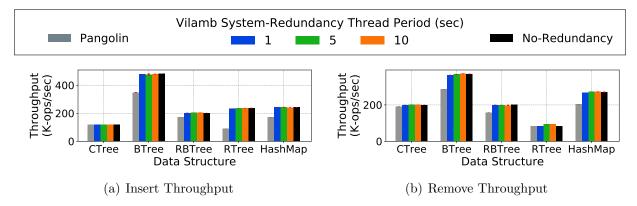

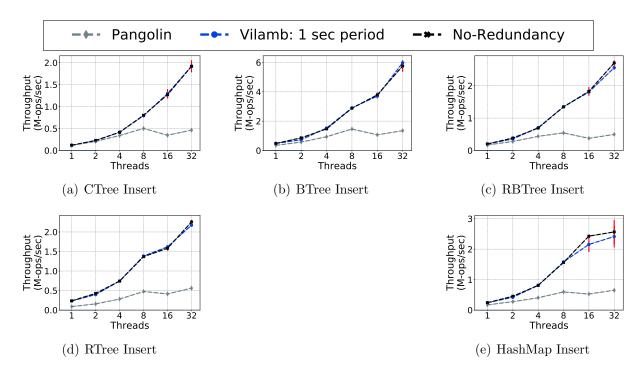

Figure 3.4: PMDK Key-Value Stores: Throughput for insert-only, remove-only benchmarks with different PMDK key-value stores.

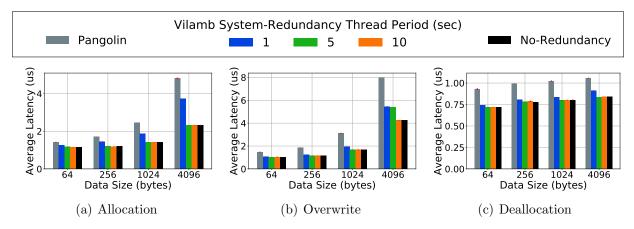

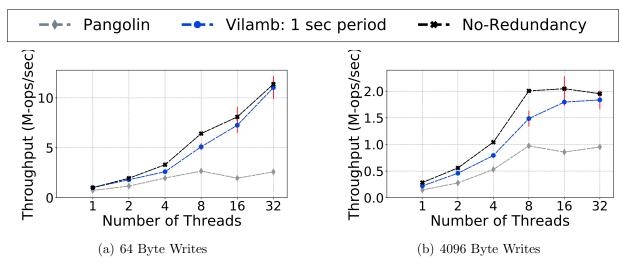

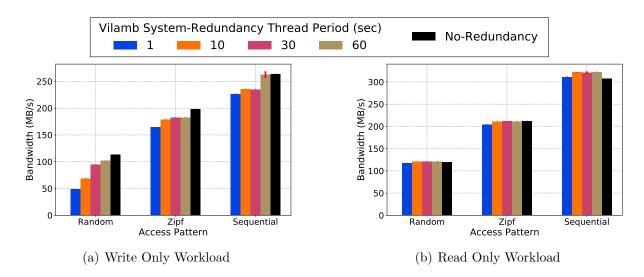

#### 3.2.3 PMDK Key-Value Stores

Intel persistent memory development kit (PMDK) [39] implements NVM-optimized keyvalue stores and includes performance benchmarks.

**Experimental Setup**: Similar to Pangolin [109], we use insert-only, and removeonly benchmarks for five key-value stores: Crit-Bit Tree (CTree), BTree, Red-Black Tree (RBTree), Range Tree (RTree) and chaining hashmap (HashMap). We first re-create the experiment and results from Pangolin [109] with a single-thread that performs 5 million operations. We then use multiple threads (1 to 32) with 100,000 operations per thread.

We modify the PMDK benchmark for multi-threaded benchmarking. In the original implementation, the threads synchronize using a coarse-grained lock; each thread holds a lock over the entire data structure for the entire duration of its transaction. Not surprisingly, the coarse-grained lock leads to poor scaling. We modified the implementation such that each thread maintains and operates on its own instance of the data structure. All the threads share the same NVM pool, but do not synchronize their changes because they operate on different data. Our modifications enabled close to linear scaling for the baseline case of No-Redundancy.