## Dynamically Managing FPGAs for Efficient Computing

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

Department of Electrical and Computer Enginnering

### Marie Nguyen

B.S., Electronics and Signal Processing, INPT-ENSEEIHT

M.S., Electronics and Signal Processing, INPT-ENSEEIHT

M.S., Electrical and Computer Engineering, Carnegie Mellon University

Carnegie Mellon University

Pittsburgh, PA

December 2020

©Marie Nguyen, 2020

All Rights Reserved

#### Acknowledgments

Doing a PhD has been an incredibly enriching journey during which I learnt how to think and teach. I would like to express my gratitude to people that have helped me along the way. First, I want to thank Prof. James C. Hoe who is a great person and advisor. James has provided very valuable guidance on my academic work and taught me how to think, write clearly and conduct high-quality research. He has always been supportive of my research and kept encouraging me during the most difficult times of my PhD. I want to thank him for his patience, the dedication he has for his students, and the effort he puts into bringing the best out of his advisees. I am very grateful for his teaching and mentoring, and will remember them well beyond my time at CMU. Thank you James for all the opportunities you gave me.

I want to thank Dasu Aravind, Prof. Srinivasa Narasimhan and Prof. Anthony Rowe for serving on my thesis committee. I would like to thank Dasu for the monthly conversations we have had over the past year that have helped me refine my thesis work. I also want to thank him for being one of my mentors during my internship at Intel. I would like to thank both Prof. Srinivasa Narasimhan and Prof. Anthony Rowe for working with me during the past years on the SmartHeadlight and the AR/VR headset projects. Specifically, I am grateful to Prof. Srinivasa Narasimhan for teaching me the basics of computer vision that I could leverage in my research.

During my time at CMU, I had the opportunity to collaborate with brilliant researchers working at Intel. Specifically, I would like to thank Eriko Nurvitadhi, Scott Weber, and Patrick Koeberl that were my supervisors during my internship at Intel along with Dasu Aravind. Eriko, Scott and Patrick have shown great interest in my research and have helped me refine it. I would like to thank them for the monthly meetings we have had for almost a year. I am grateful to Eriko and Patrick for their technical and professional mentoring. I greatly enjoyed the technical discussions with Scott, one of the world experts in partial reconfiguration. I learnt a lot about partial reconfiguration and its intricacies through these conversations. I have been fortunate to have great technical conversation with current and past students from my research group, namely, Guanglin Xu, Joe Melber, Zhipeng Zhao, Nathan Serafin, Shashank Obla, Yu Wang, Gabriel Weisz, and Michael Papamichael. I would like to thank them for proofreading my work, for their constructive feedback and for helping me with technical issues when I was struggling.

Besides my research group, I met great professors and students on A-level: Prof. Tze Meng Low, Prof. Osman Yagan, Thom Doru Popovici, Anuva Kulkarni, Daniele Spampinato, Richard Veras, Rashad Eletreby, John Filleau, Jin Huang, and Jiyuan Zhang. I have had many interesting conversations with people on A-level that taught me new perspectives on research and helped me better understand other domains. I especially want to thank Prof. Tze Meng Low that kept challenging me during my early years of the PhD and that gave much-needed feedback on my research. Thom has been a great friend during these years. I want to thank him for the great conversations we have had on the many aspects of research, and for the helpful feedbacks he gave on my writings and presentations. He has always been available and patient to answer all my questions about paper/thesis writing, and non-work related subjects. Anuva has been a good friend with whom I have had many non-technical conversations that helped me relax outside of the lab.

I also met with many great scientists and students when working on different research and class projects at CMU, to name a few, Robert Tamburo, Sezal Jain, Priya Mahajan, Adeola Bannis, and Evgeny Toropov. I would like to thank Sezal, Priya, and Adeola for the great times we have had at CMU, and Evgeny for the very entertaining board game nights and outings he organized.

Beyond CMU, I feel very lucky to have the support from my loving parents and friends from France, notably, Lou and Francois, that have always been by my side when I needed them the most. I can not thank my mom enough for all she has done for the past 30 years. She has been a source of strength, comfort and encouragement in the most difficult times. She taught me to always strive for better and be brave not matter what. Thank you mom for making me who I am today.

Finally, I would like to acknowledge Intel Corporation and Xilinx for their generous financial and equipment donation. Also, this work could not have happened without the support of the National Science Foundation (CCF-1012851) and SRC/JUMP (CONIX).

#### Abstract

Field-programmable gate arrays (FPGAs) have undergone a dramatic transformation from a logic technology to a computing technology. This transformation is pulled by the computing industry's need for more power/energy efficiency than software can achieve and, at the same time, more flexibility than ASICs. Nonetheless, FPGA designers still share a similar design methodology with ASIC designers. Most notably, at design time, FPGA designers commit to a fixed allocation of logic resources to modules in a design. In other words, FPGAs are mostly still used like an "ASIC" despite being runtime reprogrammable. Through partial reconfiguration (PR), parts of an FPGA design can be reconfigured at runtime while the remainder continues to operate without disruption. PR enables what has been possible on general-purpose processors for decades. For instance, multiple tasks can be time-multiplexed on a smaller FPGA, which can result in area/device cost, power and energy reduction, compared to statically mapping tasks on a larger FPGA. PR can become a relevant technology for an emerging class of AI-driven applications that (1) need to support many compute intensive tasks with real-time requirements and (2) are often deployed on a small, low-end FPGA due to area, cost, power or energy concerns (e.g., smart cars/robots/cameras at the Edge). For such applications, using a large expensive FPGA is typically not a viable option.

Though PR is a promising technology and has been supported by FPGA tools for over a decade, it is still a feature waiting to be proven for its commercial value. The reconfiguration time (between few to tens of milliseconds on today's FPGAs), also referred as PR time, is often considered as one of the major hurdles preventing a more widespread use of PR. While the non-trivial PR time represents a technical challenge, we believe that a more important question to address is "When, how and why should an FPGA designer consider using PR?". Addressing this question requires to (1) identify applications that can tolerate PR time and still benefit from a PR approach, (2) design good architectural and runtime management strategies to build efficient designs leveraging PR, and (3) evaluate whether the area/device cost, power or energy benefits are important enough to justify a transition from a statically mapped design.

This thesis seeks to advance the state-of-the-art in the dynamism of computing FPGAs by tackling the aforementioned challenges. Specifically, we demonstrate that a design exploiting PR can be more area/device cost, power or energy efficient than a statically mapped design (ASIC-style design) with slack. Slack occurs when all resources occupied by an ASIC-style design are not active all the time. Using PR, a designer can attempt to reduce slack by changing the allocation of resources over time. In this work, we identify slack's reduction as the most important opportunity for improvement available to PR-style designs. We refer to a

PR-style design as a design in which logic resources are allocated to different modules of one design over time using PR. We develop efficient PR allocation and execution strategies to reduce slack, and show through analytical modeling and implemented designs that a PR-style design can outperform an ASIC-style design in challenging scenarios that have to deliver required performance under strict area, cost, power, and energy constraints. Further, we leverage the findings and analysis from our theoretical investigation to develop a soft-logic-realized framework for accelerating computer vision with real-time requirements (30 + fps). This framework includes the necessary architectural and runtime management strategies to support spatial and temporal sharing of the FPGA fabric at a very fine-grain (i.e. the time interval between reconfigurations is within millisecond range) while meeting performance requirements. Using the framework, we design and implement efficient PR-style designs to quantify the performance, area/device cost, power and energy benefits of PR-style designs relative to ASIC-style designs and to software implementations. Notably, we show that a PR-style design can be more power and energy efficient than an ASIC-style design even when frequently reconfiguring the fabric (i.e. when more than half of the execution time is spent reconfiguring the fabric) and under specific conditions. We also make projections on the impact of higher PR speed on the costs and benefits of using PR at a very fine-grain. Through our study, we find that, while higher reconfiguration speed can make a PR-style more area/device cost efficient, the power/energy overhead incurred in a PR-style design due to, for instance, fabric reconfigurations and additional data movement can make a PR approach less power/energy efficient than an ASIC-style design.

# Contents

| Α  | ckno  | wledgments                                                   | iii |

|----|-------|--------------------------------------------------------------|-----|

| Li | st of | Tables                                                       | x   |

| Li | st of | Figures                                                      | xii |

| 1  | Inti  | roduction                                                    | 1   |

|    | 1.1   | Motivations, Challenges and Goals                            | 1   |

|    | 1.2   | Partial Reconfiguration for Design Optimization              | 3   |

|    | 1.3   | Contributions                                                | 6   |

|    | 1.4   | Thesis Outline                                               | 7   |

| 2  | Bac   | ekground                                                     | 8   |

|    | 2.1   | FPGA Architecture                                            | 8   |

|    | 2.2   | ASIC-Style Design for Computing                              | 9   |

|    | 2.3   | Partial Reconfiguration                                      | 10  |

| 3  | The   | e incentives for using PR                                    | 13  |

|    | 3.1   | Terminology                                                  | 13  |

|    | 3.2   | Reducing Slack for Design Optimization                       | 14  |

|    |       | 3.2.1 Slack: Inefficiency in ASIC-Style Designs              | 14  |

|    |       | 3.2.2 Partial Reconfiguration to Improve Performance or Area | 16  |

| 4  | Ana   | alytical Approach to PR                                      | 18  |

|    | 4.1   | Overview                                                     | 18  |

|   | 4.2 | ASIC-Style                                                                     | 20 |

|---|-----|--------------------------------------------------------------------------------|----|

|   | 4.3 | PR-Style                                                                       | 20 |

|   |     | 4.3.1 Ignoring PR Time: PR-Style Performance Bounds                            | 20 |

|   |     | 4.3.2 Including PR Time: Serialized Execution on one PR Region                 | 21 |

|   |     | 4.3.3 Including PR Time: Special Cases                                         | 22 |

|   |     | 4.3.4 PR Strategies to Minimize Area Given a Performance Bound                 | 23 |

|   |     | 4.3.5 Memory Requirements in PR-style designs                                  | 25 |

|   | 4.4 | Evaluation                                                                     | 26 |

|   |     | 4.4.1 Experimental Setup                                                       | 26 |

|   |     | 4.4.2 Model Validation: Case Study Results                                     | 29 |

|   | 4.5 | Summary                                                                        | 33 |

| 5 | Des | ign with PR for Domain-Specific Acceleration                                   | 35 |

|   | 5.1 | Motivations and Challenges                                                     | 35 |

|   | 5.2 | Background                                                                     | 39 |

|   | 5.3 | Spatial and Temporal Sharing of the FPGA by Multiple Computer Vision Pipelines | 39 |

|   |     | 5.3.1 Overview                                                                 | 40 |

|   |     | 5.3.2 Programming Model                                                        | 41 |

|   |     | 5.3.3 Plug-And-Play Architecture                                               | 42 |

|   |     | 5.3.4 Module Library                                                           | 43 |

|   |     | 5.3.5 Runtime System                                                           | 44 |

|   |     | 5.3.6 Real-Time Time-Sharing Support                                           | 45 |

|   | 5.4 | Evaluation                                                                     | 50 |

|   |     | 5.4.1 No Real-Time Time-Sharing Setup                                          | 51 |

|   |     | 5.4.2 No Real-Time Time-Sharing Results                                        | 54 |

|   |     | 5.4.3 Real-Time Time-Sharing Setup                                             | 59 |

|   |     | 5.4.4 Real-Time Time-Sharing Results                                           | 62 |

|   | 5.5 | Summary                                                                        | 66 |

| 6 | Qua | antifying PR Benefits on Case Studies                                          | 68 |

|   | 6.1 | Overview                                                                       | 68 |

|   |     |                                                                                |    |

|   | 6.2                                                                   | Implementation                                            | 69                                                                                                                              |

|---|-----------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|   | 6.3                                                                   | PR-Style Design Characterization                          | 70                                                                                                                              |

|   | 6.4                                                                   | Case Study 1: Interactive Application                     | 73                                                                                                                              |

|   | 6.5                                                                   | Case Study 2: Navigation Application                      | 75                                                                                                                              |

|   | 6.6                                                                   | Summary                                                   | 79                                                                                                                              |

| 7 | Pro                                                                   | jection: Overheads and Benefits of Real-Time Time-Sharing | 81                                                                                                                              |

|   | 7.1                                                                   | Overview                                                  | 82                                                                                                                              |

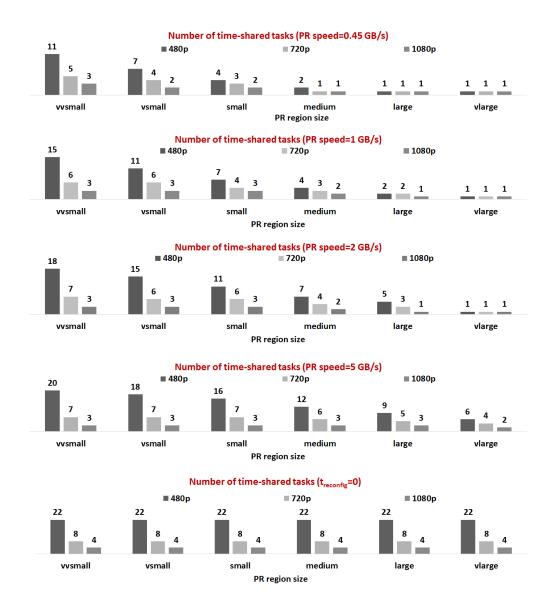

|   | 7.2                                                                   | Real-Time Time-Shared Tasks Results                       | 85                                                                                                                              |

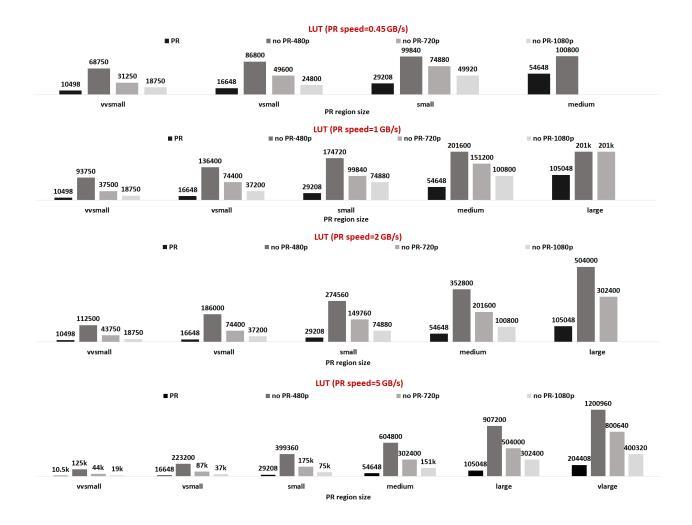

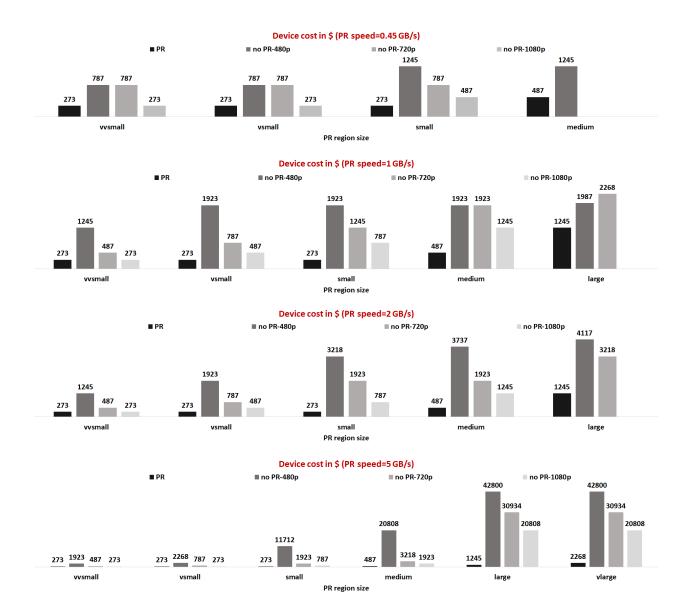

|   | 7.3                                                                   | Area and Device Cost Results                              | 88                                                                                                                              |

|   | 7.4                                                                   | Power and Energy Results                                  | 89                                                                                                                              |

|   | 7.5                                                                   | Summary                                                   | 95                                                                                                                              |

| 8 | $\mathbf{Rel}$                                                        | ated Work                                                 | 96                                                                                                                              |

|   |                                                                       |                                                           |                                                                                                                                 |

| 9 | Cor                                                                   | nclusion                                                  | 101                                                                                                                             |

| 9 | <b>Cor</b><br>9.1                                                     | nclusion<br>Summary                                       |                                                                                                                                 |

| 9 |                                                                       |                                                           | 101                                                                                                                             |

|   | 9.1<br>9.2                                                            | Summary                                                   | 101                                                                                                                             |

|   | 9.1<br>9.2<br><b>The</b>                                              | Summary                                                   | <ul><li>101</li><li>104</li><li>108</li></ul>                                                                                   |

|   | 9.1<br>9.2<br><b>The</b><br>A.1                                       | Summary                                                   | 101<br>104<br><b>108</b><br>108                                                                                                 |

|   | <ul><li>9.1</li><li>9.2</li><li>The</li><li>A.1</li><li>A.2</li></ul> | Summary                                                   | <ul> <li>101</li> <li>104</li> <li>108</li> <li>110</li> </ul>                                                                  |

|   | <ul><li>9.1</li><li>9.2</li><li>The</li><li>A.1</li><li>A.2</li></ul> | Summary                                                   | <ul> <li>101</li> <li>104</li> <li>108</li> <li>110</li> <li>112</li> </ul>                                                     |

|   | <ul><li>9.1</li><li>9.2</li><li>The</li><li>A.1</li><li>A.2</li></ul> | Summary                                                   | <ol> <li>101</li> <li>104</li> <li>108</li> <li>110</li> <li>112</li> <li>112</li> </ol>                                        |

|   | <ul><li>9.1</li><li>9.2</li><li>The</li><li>A.1</li><li>A.2</li></ul> | Summary                                                   | 101<br>104<br><b>108</b><br>108<br>110<br>112<br>112<br>113                                                                     |

|   | 9.1<br>9.2<br><b>The</b><br>A.1<br>A.2<br>A.3                         | Summary                                                   | 101<br>104<br><b>108</b><br>108<br>110<br>112<br>112<br>112<br>113<br>115                                                       |

|   | 9.1<br>9.2<br><b>The</b><br>A.1<br>A.2<br>A.3                         | Summary                                                   | <ol> <li>101</li> <li>104</li> <li>108</li> <li>110</li> <li>112</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> </ol> |

# List of Tables

| 4.1 | Model parameters.                                                                                                                           | 19 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Resource utilization of the two PR-style designs $\mathbf{P_1}$ and $\mathbf{P_2}$ post place & route $\ .\ .\ .\ .$ .                      | 26 |

| 4.3 | Resource utilization, throughput and frame latency of variants used in $\mathbf{P_1}$                                                       | 29 |

| 4.4 | Resource utilization and frame latency of the variants used in $\mathbf{P}_2$                                                               | 29 |

| 4.5 | Characterization of the ASIC-style design for the activity recognition study                                                                | 30 |

| 4.6 | Characterization of the ASIC-style design for the depth and motion estimation study $\ldots$                                                | 31 |

| 5.1 | Resource used by the plug-and-play architecture                                                                                             | 51 |

| 5.2 | Clock and measured throughput of the stereo, flow and face detection modules                                                                | 54 |

| 5.3 | Measured throughput of six modules when executed individually in the framework $\ldots$ .                                                   | 54 |

| 5.4 | Resource utilization of modules executed individually in the framework                                                                      | 55 |

| 5.5 | Xilinx ZC706 board specification                                                                                                            | 60 |

| 5.6 | Logic resource used by the PR-style design for real-time time-sharing                                                                       | 61 |

| 5.7 | Vision modules used in our evaluation                                                                                                       | 63 |

| 5.8 | Logic resource used by seven 3-branch pipelines                                                                                             | 63 |

| 6.1 | Resource utilization of the plug-and-play architecture on Zynq boards                                                                       | 71 |

| 6.2 | Resource utilization of six modules used in the interactive application post place & route $\ .$ .                                          | 72 |

| 6.3 | Resource utilization of six modules used in the navigation application post place & route $\ $ .                                            | 72 |

| 6.4 | Resource utilization of the ASIC-style design post place & route                                                                            | 74 |

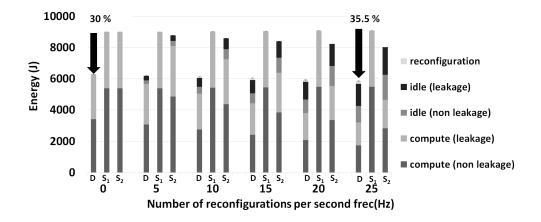

| 6.5 | Energy breakdown when $t_{\text{interval}} = 3600 \text{ s}$ and $f_{\text{rec}} = 25 \text{ Hz} \dots \dots \dots \dots \dots \dots \dots$ | 79 |

| 7.1 | Specifications for the six PR regions used in this study.                                                                                   | 83 |

| 7.2 | Module compute time and external memory bandwidth requirements                                                                              | 84 |

| A.1 Resources in runtime reconfigurable region region by workload | A.1 | Resources in | runtime | reconfigurable | region | region | by workload |  |  | . 114 |

|-------------------------------------------------------------------|-----|--------------|---------|----------------|--------|--------|-------------|--|--|-------|

|-------------------------------------------------------------------|-----|--------------|---------|----------------|--------|--------|-------------|--|--|-------|

# List of Figures

| 2.1 | FPGA architecture                                                                                                          | 9  |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | An FPGA fabric layout when using PR                                                                                        | 11 |

| 3.1 | Example of an application with two independent tasks                                                                       | 14 |

| 3.2 | Example of an interactive application with slack                                                                           | 15 |

| 3.3 | In a PR-style design, slack can be reduced with better area-time scheduling $\ldots \ldots \ldots$                         | 16 |

| 4.1 | Example timeline of an application with three dependent stages                                                             | 19 |

| 4.2 | Dependent modules share data through either external or on-chip memory                                                     | 20 |

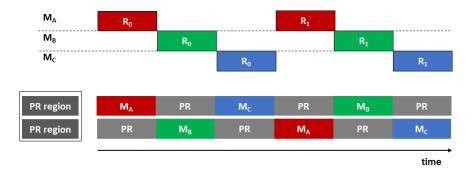

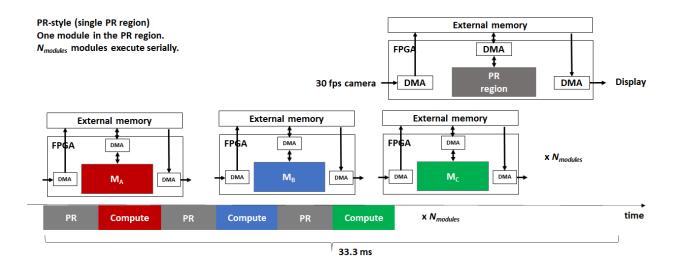

| 4.3 | Example of serialized execution in a PR-style design with one PR region                                                    | 21 |

| 4.4 | Interleaved execution on two PR regions                                                                                    | 22 |

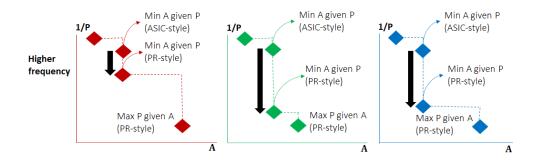

| 4.5 | The strategy for choosing module variants depends on the design objective $\ldots \ldots \ldots$                           | 23 |

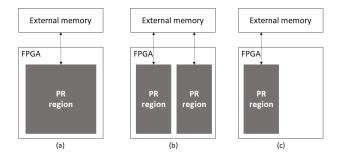

| 4.6 | Three PR-style designs are considered in these studies: (a) $\mathbf{P_1}$ with a single large PR region                   |    |

|     | on which stages are scheduled sequentially, (b) $\mathbf{P_2}$ with two almost equally-sized PR regions                    |    |

|     | on which stages are executed in an interleaved fashion, and (c) $\mathbf{P}_{1,s}$ with a single smaller PR                |    |

|     | region (one PR region of $\mathbf{P_2}$ ) on which stages are scheduled sequentially                                       | 27 |

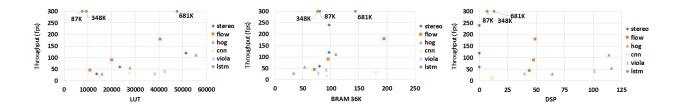

| 4.7 | Module variant throughput vs area (LUT, BRAM36k and DSP) post place & route on the                                         |    |

|     | Ultra<br>96 v2 board at 150 MHz for the six modules used in the studies. Each module has up<br>$% 10^{-1}$                 |    |

|     | to three variants                                                                                                          | 28 |

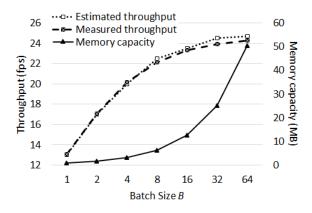

| 4.8 | Throughput of $\mathbf{P_1}$ vs. $B$ for the first case study. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 31 |

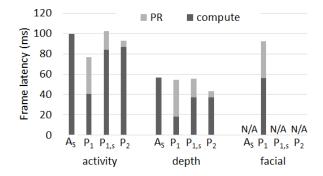

| 4.9 | Frame latency of the ASIC-style design $(A_s)$ and the PR-style designs $\mathbf{P_1},\mathbf{P_{1,s}}$ and $\mathbf{P_2}$ | 32 |

| 5.1 | Example of a computer vision application with three tasks accelerated by streaming pipelines                               | 36 |

| 5.2 | Two allocation strategies that would fail when doing real-time time-sharing                                                | 37 |

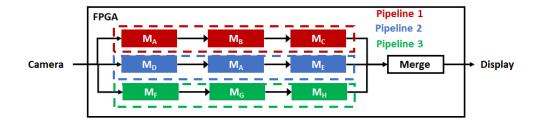

| 5.3  | Overview of the framework for spatial and temporal sharing of computer vision tasks                                | 40 |

|------|--------------------------------------------------------------------------------------------------------------------|----|

| 5.4  | Sample of the application code used to repurpose the FPGA with three tasks                                         | 41 |

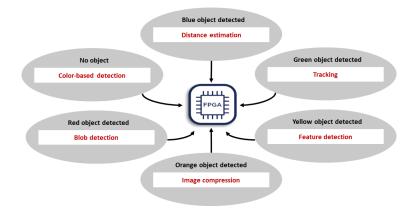

| 5.5  | Example of an interactive application built on top of the framework                                                | 43 |

| 5.6  | Time-sharing by two three-stage pipelines without staggered start                                                  | 45 |

| 5.7  | Main connectivity modes supported by the crossbar $\hdots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 47 |

| 5.8  | Time-sharing by two three-stage pipelines with staggered start                                                     | 48 |

| 5.9  | Prototype framework for repurposing                                                                                | 51 |

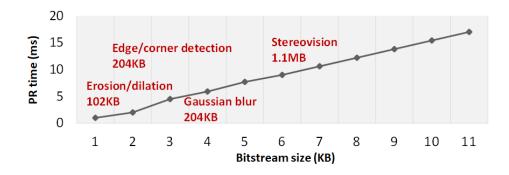

| 5.10 | PR time vs bitstream size                                                                                          | 52 |

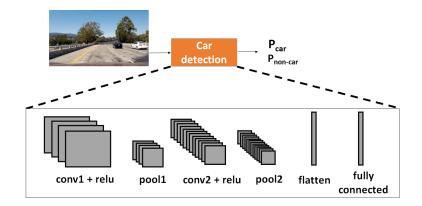

| 5.11 | Architecture of the CNN used for inference for the car detection task.                                             | 53 |

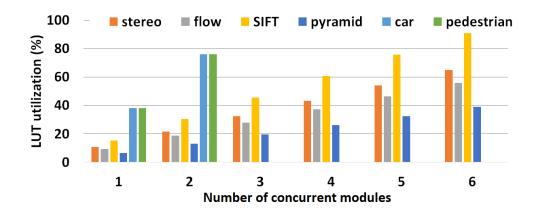

| 5.12 | LUT utilization of modules spatially sharing the fabric                                                            | 56 |

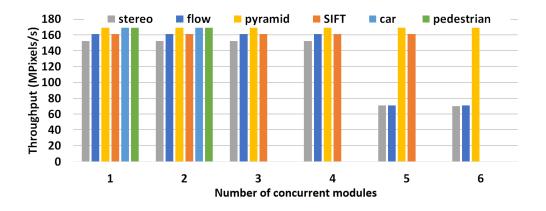

| 5.13 | Average throughput of a module executed in the repurposing framework                                               | 57 |

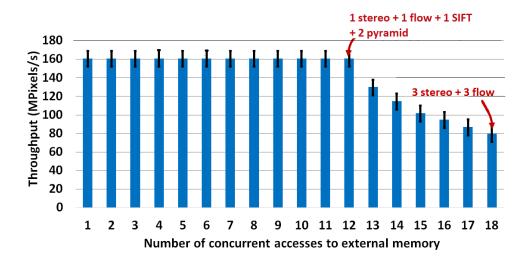

| 5.14 | Average throughput of a single module executed within a random module combination                                  | 58 |

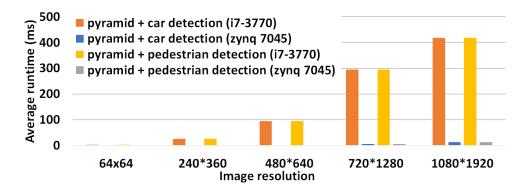

| 5.15 | Average runtime to process one image for two vision tasks                                                          | 59 |

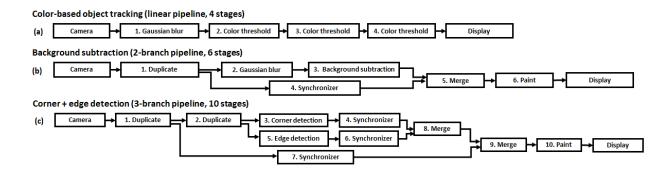

| 5.16 | Logical view of three pipeline examples                                                                            | 62 |

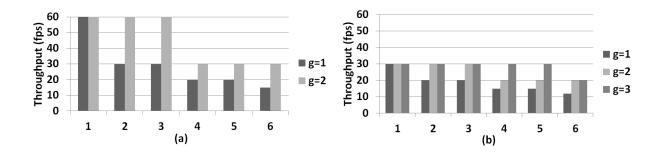

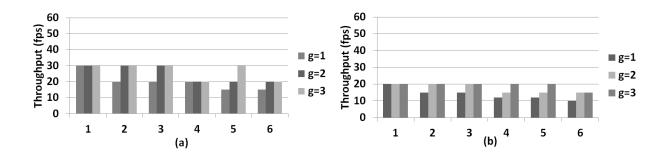

| 5.17 | Throughput of time-shared pipelines for 720p@60fps input video                                                     | 65 |

| 5.18 | Throughput of time-shared pipelines for 1080p@60fps input video                                                    | 65 |

| 6.1  | Example of an interactive application deployed on an automotive Headlight system                                   | 69 |

| 6.2  | Example of a navigation application deployed on a robotic system $\ldots \ldots \ldots \ldots \ldots$              | 70 |

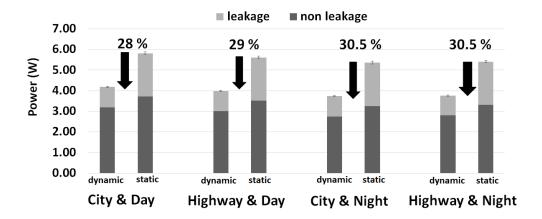

| 6.3  | Power consumption in the interactive applications                                                                  | 75 |

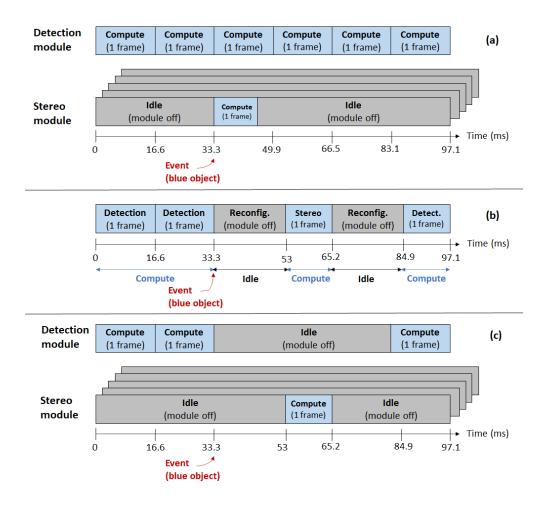

| 6.4  | Example execution timeline of the navigation application                                                           | 76 |

| 6.5  | Total energy consumed in the navigation application                                                                | 77 |

| 7.1  | PR-style design for the study                                                                                      | 82 |

| 7.2  | Number of real-time time-shared tasks at 30 fps                                                                    | 85 |

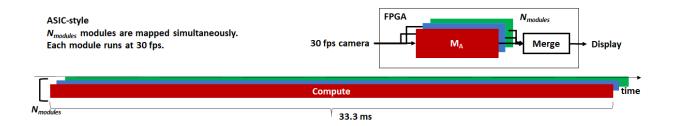

| 7.3  | ASIC-style design for the study                                                                                    | 86 |

| 7.4  | LUT utilization in ASIC-style and PR-style designs                                                                 | 87 |

| 7.5  | Device cost when mapping ASIC-style and PR-style designs                                                           | 88 |

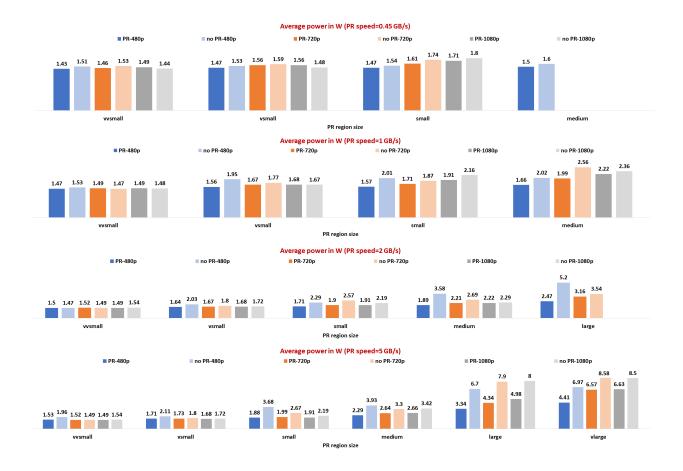

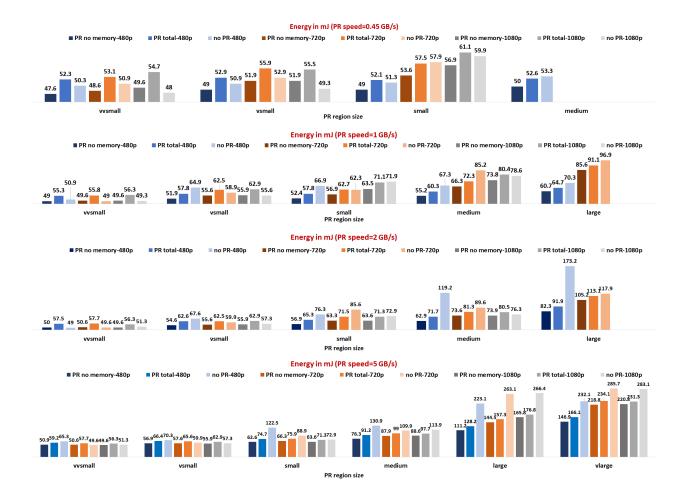

| 7.6  | Average power of ASIC-style and PR-style designs                                                                   | 91 |

|      |                                                                                                                    |    |

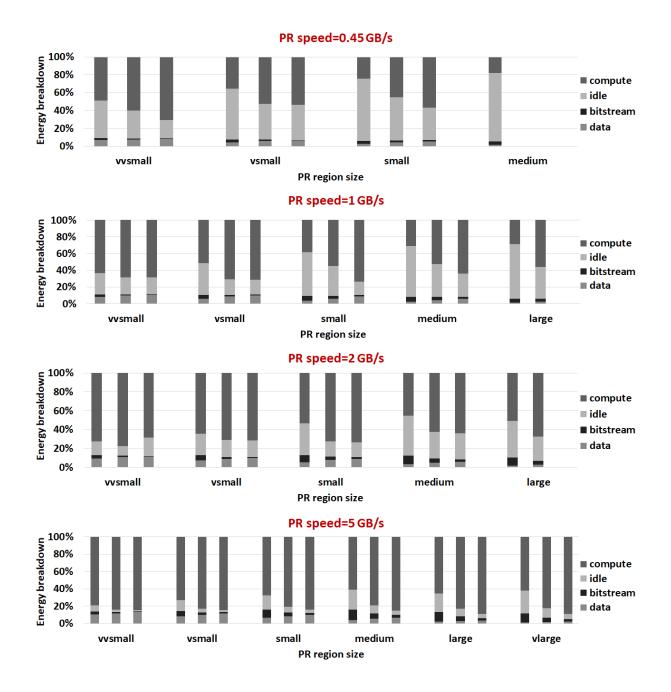

| 7.7  | Energy breakdown for PR-style designs.                                                                             | 93 |

| A.1 | An FPGA fabric layout when using PR 109                                                                   |

|-----|-----------------------------------------------------------------------------------------------------------|

| A.2 | Elements locked down in amorphous PR                                                                      |

| A.3 | A valid packing in amorphous PR                                                                           |

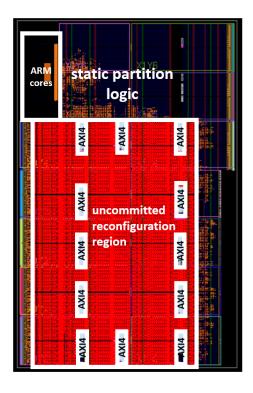

| A.4 | Screenshot of the static region floorplan on the XC7Z045 SoC FPGA                                         |

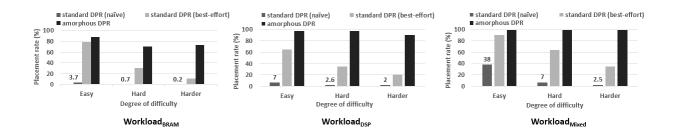

| A.5 | Placement rates with naive standard PR vs. best-effort standard PR vs. amorphous PR 117                   |

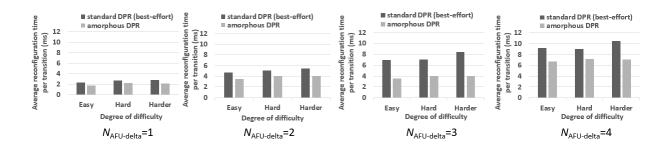

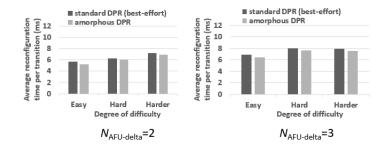

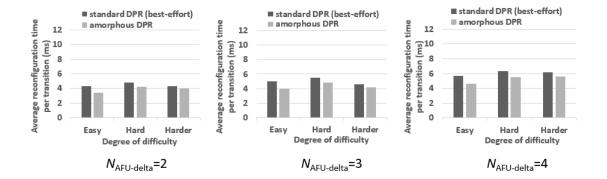

| A.6 | Average reconfiguration times with best-effort standard PR vs. amorphous PR for Workload $_{\rm BRAM}118$ |

| A.7 | Average reconfiguration times with best-effort standard PR vs. amorphous PR for Workload $_{\rm DSP}118$  |

| A.8 | Average reconfiguration times with best-effort standard PR vs. amorphous PR for Workload $_{mixed}$ 119   |

### Chapter 1

## Introduction

#### 1.1 Motivations, Challenges and Goals

Motivations. Field-programmable gate arrays (FPGAs) have undergone a dramatic transformation from a logic technology to a computing technology [14,45,65]. This transformation is pulled by the computing industry's need for more power/energy efficiency than software can achieve and, at the same time, more flexibility than ASICs. Nonetheless, FPGA designers still share a similar design methodology with ASIC designers. Most notably, at design time, FPGA designers commit to a fixed allocation of logic resources to modules in a design. In other words, FPGAs are mostly still used like an "ASIC" despite being runtime reprogrammable. Through partial reconfiguration (PR), parts of an FPGA design can be reconfigured at runtime while the remainder continues to operate without disruption. PR enables what has been possible on general-purpose processors for decades. For instance, multiple tasks can be time-multiplexed on a smaller FPGA, which can result in area/device cost, power and energy reduction, compared to statically mapping tasks on a larger FPGA.

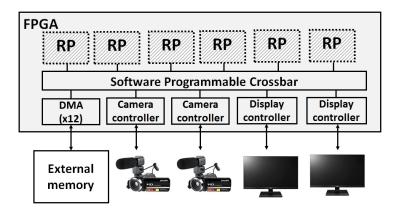

**Partial Reconfiguration Overview.** Using PR, an FPGA is divided into multiple runtime reconfigurable regions called reconfigurable partitions (RPs) or PR regions. The non reconfigurable part of the design typically includes the I/O infrastructure defining the interconnection between the PR regions to the rest of the system. The number, sizing and interconnection between reconfigurable partitions are decided at design time during the floorplanning process. Reconfigurable partitions can be reprogrammed at runtime with module bitstreams built offline. Any module built at design time can be separately mapped in a specific reconfigurable partition if the module has matching I/O interfaces with the reconfigurable partition and

consumes less resources than available in the reconfigurable partition. The set of module bitstreams built at design time constitutes a module library.

At runtime, the reconfigurable partitions can be reprogrammed with different modules over time to accelerate different tasks. The reprogramming of the PR regions can be triggered from outside the FPGA (e.g., an external CPU), by logic on the fabric, or by an embedded processor.

**Challenges.** Though PR is a promising technology and has been supported by FPGA tools for over a decade, it is still a feature waiting to be proven for its commercial value. The non-trivial reconfiguration time (between few to tens of milliseconds on today's FPGAs), also referred as PR time (assumed to be proportional to the PR region size), is often considered as one of the major hurdles preventing a more widespread use of PR. However, despite the steady improvement of PR technology over the past decade (faster PR time, better tool support), PR still remains an under-appreciated capability. While the non-trivial PR time represents a technical challenge, we believe that a more important question to address is "When, how and why should an FPGA designer consider using PR". Addressing this question requires to (1) identify applications that can tolerate PR time overhead, (2) design good architectural and runtime management strategies to build efficient designs leveraging PR, and (3) evaluate whether the area/device cost, power or energy benefits of design are important enough to justify a transition from a statically mapped design.

Goals. This thesis seeks to advance the state-of-the-art in the dynamism of computing FPGAs by tackling the aforementioned challenges. Specifically, we demonstrate that a design exploiting PR can be more area/device cost, power or energy efficient than a statically mapped design (ASIC-style design) with slack. Slack occurs when all resources occupied by an ASIC-style design are not active all the time, that is, resources are under-utilized in the ASIC-style design. Using PR, a designer can attempt to reduce under-utilization by changing the allocation of resources over time. In this work, we find that reducing slack is the most important opportunity for improvement available to PR-style designs. We refer to a PR-style design as a design in which logic resources are allocated to different modules of one design over time. In return, a PR-style design may be faster, smaller, and/or consume less power/energy than an ASIC-style design. We develop efficient PR allocation and execution strategies to reduce slack, and show through analytical modeling and implemented designs that a PR-style design can outperform an ASIC-style design in challenging design scenarios that have to deliver required performance under strict area, cost, power, and energy constraints (e.g., [48,86]).

In this work, we also leverage PR to spatially and temporally share the FPGA fabric by multiple tasks

for domain-specific acceleration. Specifically, we investigate the costs and benefits of using PR at a very fine-grain (i.e. the time interval between reconfigurations is within the millisecond range). Note that, in this work, we do not focus on using PR in a "role-and-shell" approach [9,42]. In this use-case, the FPGA is reconfigured very infrequently i.e. at a coarse-grain (minutes, hours or days between reconfigurations). Most FPGA resources are contained in a single PR region that is enclosed by a static shell region that provides I/O and isolation. Independent designs with different functionalities, or roles, can be loaded as required in the PR region over time (e.g., [9,42]). Each role is an ASIC-style design created to use the entire PR region alone, with no consideration for sharing resources or interacting with other roles.

The work presented in this thesis is especially relevant for an emerging class of AI-driven applications that (1) need to support many compute intensive tasks with real-time requirements (e.g., smart cars/robots/cameras at the Edge) and (2) are often deployed on a small, low-end FPGA due to area, cost, power or energy concerns [10,97]). For such applications, using a large expensive FPGA is typically not a viable option.

#### **1.2** Partial Reconfiguration for Design Optimization

In this thesis, we address the questions of when, how and why FPGA designers should consider using PR. Notably, we demonstrate that a PR-style design can reduce slack with better resource scheduling, and therefore, improve upon an ASIC-style. By improving upon an ASIC-style design, we mean either that (1) a PR-style design is smaller or consumes less power/energy than the ASIC-style design while achieving the same performance, or (2) a PR-style design achieves better performance and uses less area or power/energy than the ASIC-style design. The first part of the thesis covers the theoretical foundations to tackle the aforementioned questions and focuses on applications with a single task. The second part of this work leverages the analysis and findings from the first part, and discusses the practical challenges, costs and benefits of using PR for domain-specific acceleration with multiple tasks spatially and temporally sharing the fabric. In the remainder of this section, we give an overview of our work.

**Reducing Slack with PR.** In this work, we find that reducing slack is the main means for PR-style designs to improve over ASIC-style designs. Slack stems from hard-to-avoid source of inefficiencies (e.g., operation dependencies or pipeline imbalancing) and results in some of the occupied resources being left idle or under-utilized. In other words, all occupied resources in the design are not active all the time. In ASIC-style designs, a module must occupy logic resources even when it is inactive since resources are statically

allocated. Slack can result in (1) the design not running at the desired performance given an area budget, or (2) the design running at the desired performance but being too big to fit in the given area. In an ASIC-style design, the designer is not exploiting the fact that FPGA logic resources can be re-allocated over time. Using PR, a designer can attempt to reduce slack by changing the allocation of resources over time.

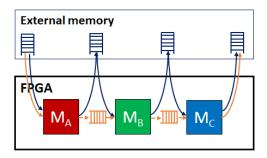

**PR Execution Strategies.** To reduce slack and improve over the performance-area Pareto front of ASICstyle designs, we develop a set of PR execution strategies (allocation and scheduling) for a non-trivial range of applications. An application consists of a set of independent tasks. A task is modeled as a directed graph where nodes are processing stages, and edges represent stage dependencies. Each processing stage is accelerated on the FPGA by a hardware module that includes the necessary FPGA logic, hardened compute block and memory resources. Modules can execute concurrently and have multiple implementation variants with different performance-area trade-offs. Dependent modules share data either through (1) external memory or (2) on-chip memory. This choice of an execution model allows to cover a range of applications that benefit from FPGA acceleration (e.g., streaming pipelines). For instance, in video analytics or image processing applications, data is streamed from an input source (e.g., camera) directly to a processing pipeline mapped on the FPGA. Pipeline stages are accelerated by modules that share data through on-chip connections.

Analytical Modeling. Further, while FPGA tools have been improving at a rapid pace, FPGA design development is still tedious and even more so when designing with PR. Consequently, it is important to determine whether a PR-style design can improve upon an ASIC-style design during the early stage of design development i.e. before crafting a PR-style design. To this end, we propose a first-order analytical model to help a designer (1) determine a suitable PR execution strategy for a given problem and (2) analyze the throughput and latency of ASIC-style and PR-style designs. The model enables quick exploration of the design space to help decide if a PR-style design can be beneficial. The model accounts for the impact of PR time on performance, and assumes the existence of a module library that has been pre-characterized in terms of latency, throughput, area, etc.

Framework for Computer Vision Acceleration. Starting from Chapter 5, we discuss our investigation on designing and implementing PR-style designs for domain-specific acceleration. Specifically, we present the design and implementation of a soft-logic-realized framework for accelerating computer vision applications with real-time performance requirements (30+ fps). Computer vision is picked as an example domain that can benefit from PR since many vision applications can (1) be accelerated by streaming pipelines, and therefore, benefit from FPGA acceleration, (2) are deployed on systems with limited area, power or energy budget, and (3) have slack and tolerance for current DPR overhead. We explain in more details the latter point in Chapter 5.

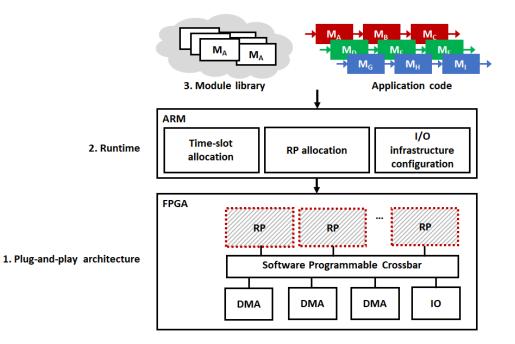

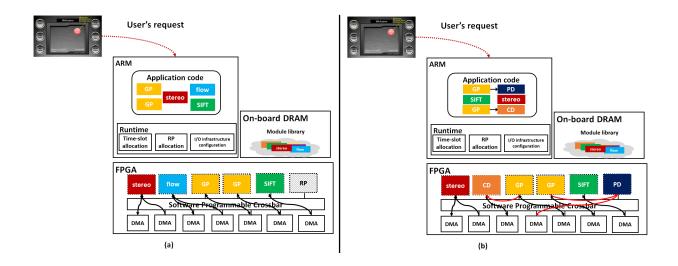

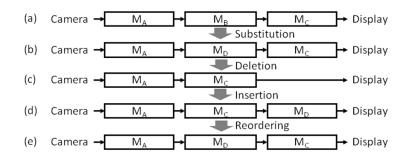

In the framework, vision tasks can spatially and temporally share the FPGA. Spatial sharing means that multiple tasks can be mapped and executed simultaneously on the FPGA. Temporal sharing means that different tasks can be reprogrammed over time. The framework has the following components:

- a plug-and-play architecture with multiple PR regions that communicate with each other and the rest of the system via a static I/O infrastructure,

- a runtime system which manages the reprogramming of the FPGA with tasks specified in an application code. In our implemented prototype, the runtime system and the application code both run on an embedded CPU.

- a module library which contains pre-built modules that are used to reprogram the PR regions.

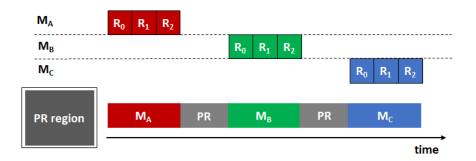

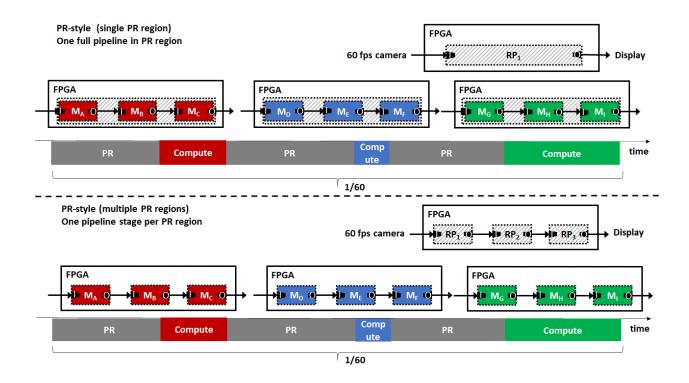

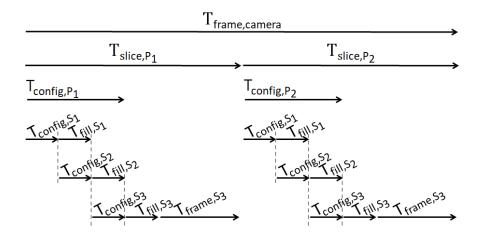

While most works use PR at a coarse grain (hours or days between reconfigurations, for instance, in a "role-and-shell" approach) due to the significant reconfiguration time on today's FPGAs, we further explore a more aggressive, fine-grain use of PR (few milliseconds between reconfiguration) referred to as real-time time-sharing. In real-time time-sharing, multiple vision pipelines can round-robin execute in the time scale of camera frame (16.7 ms): in 16.7 ms, multiple pipelines are reconfigured on the FPGA and each pipeline processes one frame. To support such an aggressive PR usage, the framework includes the necessary architectural and runtime mechanisms for hiding, amortizing, and reducing the reconfiguration time.

**PR Benefits Evaluation and Projection.** Using the framework, we implement PR-style designs for accelerating vision applications to: (1) demonstrate that real-time time-sharing is feasible despite the non-trivial reconfiguration time on today's FPGAs. By designing the appropriate architectural and runtime strategies to mitigate PR time, we show that multiple pipelines can be real-time time-shared and achieve useful performance (30+ fps). (2) quantify the area/device cost, power and energy benefits of PR-style designs relative to ASIC-style designs and software implementations in case studies of implemented designs. Notably, we demonstrate that using PR at fine-grain can be beneficial in terms of area/device cost, power or energy even when most of the execution time is spent reconfiguring the fabric.

We conduct a limit study to further our understanding of the costs and benefits when doing real-time time-sharing, and notably, make projections for higher PR speeds. Real-time time-sharing serves as a proxy for very aggressive, fine-grain PR usages that can be highly beneficial in terms of area/device cost but also incur the most overhead in terms of time and power/energy due to (1) the very frequent reconfigurations, (2) the difference in clock frequency compared to an ASIC-style design to compensate for PR time, and (3) the additional data movement required compared to an ASIC-style design (to fetch the PR bitstreams and to load/store intermediate data from/to off-chip memory). In this study, we highlight the importance of accounting for the power/energy overhead when using PR at a very fine-grain for a fair comparison between PR-style and ASIC-style designs. While the area/device cost efficiency of a PR-style design grows with increased PR speed, we demonstrate that a PR-style design can be less power/energy efficient than an ASIC-style design due to the power/energy overhead incurred when using PR. This finding emphasizes the importance of developing analytical models and performing preliminary analyses to gain a better understanding of the potential costs and benefits of a PR-style design prior to implementing a physical solution.

#### **1.3** Contributions

The work of this thesis explores the questions of when, how, and why FPGA designers should consider using PR. Specifically, the contributions are as follows:

- We identify slack as an opportunity that can be exploited by PR-style designs to improve upon ASICstyle designs. Slack occurs when some occupied resources in a design are not active all the time due to hard-to-avoid sources of inefficiencies (e.g., operation dependencies, pipeline imbalancing).

- We develop a set of PR execution strategies to reduce slack in ASIC-style designs and improve a design's performance or area. We also propose an analytical model to help the designer choose the best PR execution strategy for a given problem and evaluate whether a PR-style design is more beneficial than an ASIC-style design.

- We develop a soft-logic-realized framework for spatial and temporal sharing of the FPGA by multiple computer vision tasks. The framework includes the necessary architectural and runtime management strategies to support coarse and fine-grain temporal sharing. Notably, we investigate a specific finegrain usage of PR referred to as real-time time-sharing. In real-time time-sharing, multiple vision tasks are reconfigured on the FPGA and each pipeline processes one frame in the time-scale of a camera frame.

- Using the framework, we design and implement application examples to (1) demonstrate the feasibility

of real-time time-sharing despite the non-trivial PR time on today's FPGAs and (2) quantify the area/device cost, power and energy benefits of PR-style designs relative to ASIC-style designs and software implementations. Notably, we show that a PR-style design can be more power/energy efficient than an ASIC-style design even when most of the execution time is spent on fabric reconfiguration in a case study.

• We also make projections on the benefits and costs of doing real-time time-sharing with faster PR. While faster PR results in greater area/device cost efficiency, the power/energy overhead of a PR-style design can outweigh the benefits of using a smaller FPGA.

#### 1.4 Thesis Outline

The remainder of this thesis is organized as follows. Chapter 2 provides background information on the architecture of an FPGA and partial reconfiguration. Chapter 3 discusses the terminology used in this thesis and presents the insights behind why a PR-style design can be faster or smaller than an ASIC-style. Chapter 4 presents the PR execution and allocation strategies for developing efficient PR-style designs and explains our analytical model. Chapter 5 presents our soft-logic-realized framework for accelerating computer vision applications and details the architectural and runtime mechanisms to support real-time time-sharing. Chapter 6 presents our quantification on the area/device cost, power and energy benefits of PR-style designs relative to ASIC-style designs for applications built on top of our framework. Chapter 7 discusses the potential cost and benefits of having faster PR. Chapter 8 discusses related work. Finally, Chapter 9 presents concluding remarks and future directions.

### Chapter 2

## Background

This section first covers the basic architecture of an FPGA before discussing the motivations behind using an FPGA for computing. Finally, we explain the PR design flow in more details.

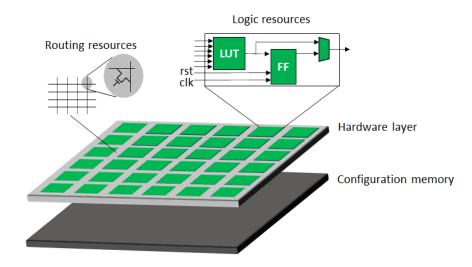

#### 2.1 FPGA Architecture

Field Programmable Gate Arrays (FPGAs) are semiconductor devices built off arrays of lookup table (LUT)based blocks referred to as configurable logic blocks (CLBs) [91] or arithmetic logic modules (ALMs) [43] in Xilinx and Intel terminology, respectively (Figure 2.1). CLBs and ALMs consist of lookup tables (LUTs), registers, and multiplexers, and are integrated with other components on an FPGA, such as embedded memory blocks, embedded digital signal processing (DSP) blocks, via programmable interconnect. Embedded memory and DSP blocks are typically organized in columns and interleaved in a specific pattern depending on the target FPGA. An FPGA fabric is subdivided into multiple regions called clock regions or sectors (terminology specific to Intel Stratix 10 FPGAs) in Xilinx or Intel's terminology, respectively. Clock regions may contain a different amount and type of resources depending on the target FPGA. The distribution of resources (LUTs and hard blocks) on the fabric is not necessarily uniform. On the other hand, sectors are homogeneously-sized, that is, they contain the same amount and type of resources.

After the device has been manufactured, FPGA hardware resources can be reconfigured to implement different functions by modifying the content of the FPGA configuration memory made of volatile memory cells (mostly static random access memory(SRAM)-based). The configuration memory is organized into an array of configuration frames which are the smallest addressable segments of the FPGA configuration

Figure 2.1: A typical FPGA architecture is comprised of two layers: a hardware logic and a configuration memory layer.

memory. Reconfigurable frames are built from a discrete number of configuration frames. A reconfigurable frame represents the smallest reconfigurable region within an FPGA. In Xilinx devices, a reconfigurable frame is one element (CLB, block RAM, DSP) wide by one clock region high [93]. The number of resources in these frames vary by device family [93]. Please refer to [93] for more detailed information, rules and restrictions. Data written to the configuration memory cells is contained in a bitstream file generated at design time. A bitstream contains all the necessary information to specify how logic resources available (CLBs, on-chip memory blocks, DSP blocks, routing resources) on the FPGA should be configured to execute a given functionality.

#### 2.2 ASIC-Style Design for Computing

The features of post-manufacturing programmability differentiate FPGAs from Application Specific Integrated Circuits (ASICs), which are hardened for application specific functions. General-purpose processors rely on a fixed architecture support to deliver software-based programmability through a set of instructions. In other words, instructions are scheduled to execute on a fixed number of compute units and leverage a fixed caching architecture that can not be changed post-manufacturing. In contrast, FPGAs' reprogrammability is hardware-based and allows to create application-specific architectures by reconfiguring the available logic and routing resources. As transistors are directly used to accelerate application-specific computations, using an FPGA may provide better silicon area utilization, potentially leading to improved performance and/or greater area, power and energy efficiency.

With the computing industry's need for more energy-efficiency than software can achieve and, at the same time, more flexibility than ASICs, there is a growing emphasis on deploying FPGAs for domain-specific acceleration [35,38,45]. FPGAs have been proven particularly beneficial for accelerating streaming computations when data is produced at a given rate by an off-board source and is directly streamed to the FPGA for processing (e.g., video analytics or network function processing). We are also starting to see FPGAs' post-manufacturing programmability being recognized as a deciding feature in selecting FPGAs over ASICs, for instance, in the data centers by the industry's largest players [9,12,68].

#### 2.3 Partial Reconfiguration

The discussion of PR in this section is based on the Xilinx PR flow [93].

Partial Reconfiguration (PR) allows some regions of the FPGA fabric, referred to as PR regions or reconfigurable partitions (RPs), to be reprogrammed at runtime [93]. At design time, the FPGA needs to be partitioned in (1) a non reconfigurable region that typically includes the I/O infrastructure, and (2) one or multiple PR regions that can be reprogrammed individually at runtime. Each PR region can be reprogrammed with partial bitstreams built for this region at design time to accelerate specific functions.

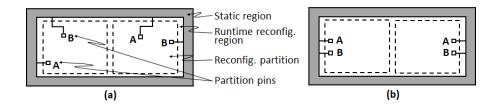

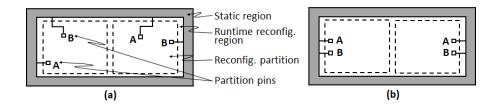

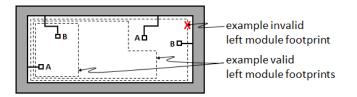

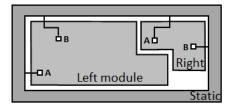

Static Region and Reconfigurable Partitions. The cartoon in Figure 2.2(a) depicts an FPGA fabric organized into a top-level static region enclosing a runtime reconfigurable region subdivided as two reconfigurable partitions. In Xilinx environment, a reconfigurable partition appears in the top-level design as a "black-box" submodule with know I/O ports but opaque internals. In Figure 2.2(a), the two reconfigurable partitions are shown to have the same port list, simply A and B in this toy example. A reconfigurable partition can have an arbitrary rectilinear outline and can cross clock regions. Resources enclosed within the outline (e.g., LUTs, BRAM blocks) are part of the reconfigurable partition and can be reprogrammed at runtime.

**Build Flow.** At design time, the locations of the PR region I/O pins, the port nets, and the physical boundary of the static and PR regions are fixed. The net for a port (whether input or output) terminates at a reserved interface point called partition pin. Partition pins are automatically created and placed by the tool when defining a reconfigurable partition. It is also possible for the designer to change the location of the partition pins. These virtual I/O are established within interconnect tiles as the anchor points that remain

Figure 2.2: An FPGA fabric organized into a top-level static region enclosing a runtime reconfigurable region subdivided as two reconfigurable partitions. The partition pins in (a) have been arbitrarily placed; the partition pins in (b) have been placed deliberately.

consistent from one module to the next. No physical resources such as LUTs or flip-flops are required to establish these anchor points, and no additional delay is incurred at these points [93]. In Figure 2.2(a), the partition pins A and B are shown as to have been placed arbitrarily by the tool. The figure also shows the placed-and-routed nets that connect the partition pins out to the static region. Figure 2.2(b) shows another version where the partition pins have been deliberately placed during floorplanning.

**Bitstream Versions.** In addition to defining a layout for the fabric at design time i.e. determining the number, shape and size of reconfigurable partitions), modules are synthesized and placed & routed for the reconfigurable partitions. Any module compiled at design time can be separately mapped in a specific reconfigurable partition if the module satisfies two requirements (1) the module has matching I/O interfaces with the reconfigurable partition (same I/O ports) and (2) the module consumes less resources than available in the reconfigurable partition. When a module can be placed in multiple RPs, the module needs to be separately placed-and-routed for the different RPs to produce non-interchangeable, partition-specific versions of bitstreams.

**Reconfiguring at Runtime.** At runtime, the reconfiguration of a reconfigurable partition can be initiated from outside the FPGA (e.g., an external CPU), by logic on the fabric, or by an embedded processor. The set of partial bistreams compiled at design time constitutes a module library that can be stored in on-chip or off-chip memory at system boot-up (e.g., from BRAM, DRAM or flash). To reconfigure an RP, the module is paused (all incoming and outgoing traffic is stopped); the incoming partial bitstream is loaded from the storage medium and passes through a PR interface to reprogram the PR region; finally, the new module is started. A PR interface is essentially a gateway to the configuration memory cells. Different PR interfaces are available on Xilinx Zynq FPGAs such as the processor configuration access port (PCAP) or the internal configuration access port (ICAP) depending on whether the reconfiguration process is triggered from a hard embedded processor or from logic on the fabric, respectively. On Intel Stratix 10 FPGAs, reconfigurations occur through the secure device manager (SDM). Note that, in this work, our PR-style designs are deployed on Zynq SoC FPGAs with embedded ARM cores. PR is managed by software running on the ARM core and bitstreams are held initially in flash, and loaded into DRAM for use at system boot-up.

While one reconfigurable partition is undergoing reconfiguration, the logic on the rest of the fabric is not affected except the portions that interact directly with the reconfigurable partition's input/output ports. The disruption during PR must be accounted for explicitly by the enclosing design with the help of auxiliary status signals that indicate the readiness of the PR module. The minimum time to reconfigure a reconfigurable partition is on the order of milliseconds. The total time is a function of the size of the loaded bitstream. For standard PR (uncompressed bitstreams), the bitstream size is a function of the reconfigurable partition size regardless of the actual degree of resource utilization within.

In summary, building an efficient PR-style design requires to find (1) a good partitioning on the FPGA at design time, that is, decide on the number, the size and the connectivity between PR regions. Note that it is not necessary that all the reconfigurable partitions be the same size. For example, if the module workload mix is known ahead of time, one could improve mappability by creating asymmetrically resourced reconfigurable partitions tuned to the module workload at design time. For example, one would want to allocate reconfigurable partitions to be large enough for the largest required module or combination of modules. In other words, a PR-style design can consist of few large PR regions, many small PR regions, or a mix of small and large PR regions depending on the use-case. (2) a good allocation and execution strategy to allocate modules to PR regions and an execution time-slot, respectively. The module-to-RP and time-slot allocation can be managed by an external processor, an embedded processor, or logic on the fabric. The allocation strategy can be decided offline or online depending on the use-case.

### Chapter 3

## The incentives for using PR

This chapter first presents the terminology used in the remainder of the thesis. We then further elaborate on the concept of slack which we find to be the most important feature to have for an application to benefit from PR. Finally, we introduce a simplified analytical model and the area-time volume representation of an FPGA to explain the intuitions behind how PR can reduce slack and improve a design's performance or area. The next chapter continues with a more complete examination of the model.

#### 3.1 Terminology

Application and Task Model. We refer to an application as a set of independent tasks. A task is modeled as a directed graph where nodes are processing stages, and edges represent stage dependencies. Each processing stage is accelerated on the FPGA by a micro or a macro hardware module that includes the necessary FPGA logic, hardened compute blocks and memory resources. Micro hardware modules accelerate processing stages that typically have low or medium compute complexity including linear algebra computations on (1) single data elements (e.g., scaling, threshold operations), (2) a small neighborhood of data elements (e.g., 2D stencil-based operations such as 2D convolutions) and (3) a large region of data elements (e.g., matrix-matrix multiplications). Macro modules are built with many micro modules and accelerate multiple processing stages at a time or even an entire task (e.g., stereo vision or optical flow computation). More examples of micro and macro modules are given in Section 5.3.4 of Chapter 5. In the remainder of the thesis, we do not make a distinction between micro or macro hardware modules, and generally refer to a micro or a macro module as a hardware module. A module can be reconfigured in a PR

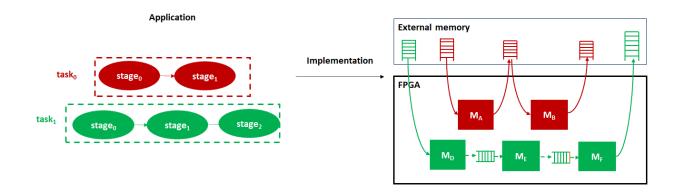

Figure 3.1: Example of an application with two independent tasks  $task_0$  and  $task_1$  accelerated on an FPGA.  $task_0$  has two stages accelerated by dependent modules that share data through external memory  $.task_1$  has three stages accelerated by dependent modules that share data through on-chip connections.

region as long as it has the same set of I/O ports and uses less resources than available in the PR region.

Modules have multiple Pareto-Optimal implementation variants with different performance-area tradeoffs, e.g., the larger the variant, the faster it is. Figure 3.1 shows an example of an application with two independent tasks  $task_0$  and  $task_1$  accelerated on the FPGA.  $task_0$  has two processing stages and  $task_1$  has three processing stages. Dependent modules in  $task_0$  share data through external memory while dependent modules in  $task_1$  share data through on-chip memory connections.

**ASIC-Style and PR-Style Designs.** When we say that an application is accelerated on the FPGA, we mean that all tasks supported by the application are accelerated on the FPGA. We refer to the FPGA implementation of the application as an FPGA design. When we say that an application is mapped statically, we mean that the design does not use PR, and we refer to it as an ASIC-style design. On the other hand, when using PR to implement the application, the design is referred to as a PR-style design. In a PR-style design, the fabric is divided into multiple PR regions or reconfigurable partitions (RP). The time to reconfigure a PR region is referred to as reconfiguration time or PR time.

#### **3.2** Reducing Slack for Design Optimization

#### 3.2.1 Slack: Inefficiency in ASIC-Style Designs

In our work, we found that applications that most benefit from PR are the ones for which the ASIC-style implementation has slack. Slack occurs when logic resources occupied by the ASIC-style design are not

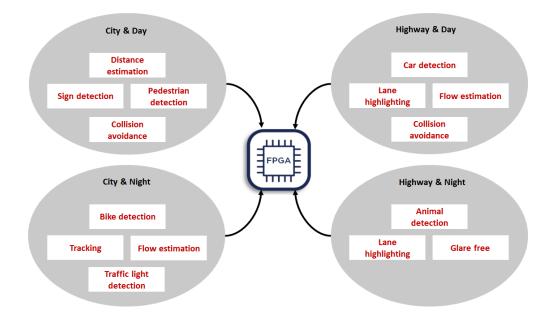

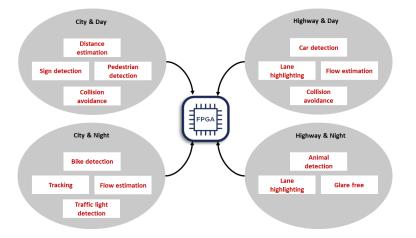

Figure 3.2: Example of an interactive application with slack deployed on an automotive system. In an ASIC-style design, some of the occupied resources are not active all the time since only a subset of tasks (tasks are shown in red) is requested by an user at a time depending on the external environment (city or highway & day or night).

actively utilized 100% of the time. Slack stems from hard-to-avoid sources of inefficiencies (e.g., operation dependencies, pipeline imbalancing) and can therefore be considered as inefficiency in a design. An example of an application with slack is shown in Figure 3.2. In this interactive application deployed on an automotive system, many tasks need to be accelerated on the FPGA but not of all them are needed at the same time. The subset of tasks needed at a given time is requested by the user depending on the environment (city or highway & day or night). Therefore, when mapping this application on the FPGA in an ASIC-style fashion, not all logic resources occupied by the design are actively utilized all the time. Instead of mapping this application statically on a possibly large FPGA, tasks could be temporally shared on a smaller FPGA with PR resulting in a reduction of device cost, and potentially, power and energy. In this work, we mostly focus on using PR for area, device cost, power or energy reduction. Another option is to use PR to execute more tasks than could be statically mapped on a given FPGA size (by swapping inactive tasks with active ones).

In the rest of this section, we use another simplified and idealized example to develop the intuitions behind how a PR-style design can either be (1) smaller while running at the same performance or (2) faster using the same area compared to an ASIC-style design with slack. Chapter 4 will present a more complete

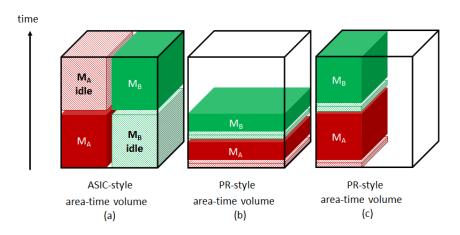

Figure 3.3: In an ASIC-style design, logic resources that are inactive must still occupy the fabric. In a PR-style design, slack can be reduced with better area-time scheduling.

model.

#### 3.2.2 Partial Reconfiguration to Improve Performance or Area

Simplified Execution Model. We consider an application with a single task that has two dependent stages,  $stage_A$  and  $stage_B$ . Each stage is accelerated by a module for which multiple implementation variants exist. Each implementation variant is characterized by the latency function  $Lat_i()$ .  $Lat_i(a)$  is the latency achieved by the module variant for  $stage_i$  using a logic resources. For a given  $stage_i$ , larger variants have lower latency i.e.,  $Lat_i(a) < Lat_i(b)$  if a > b.  $stage_B$  can start only after  $stage_A$  is finished. Each stage runs once per execution of the application. The latency of the application is the sum of the two dependent stages' latencies.

ASIC-Style Design. Consider two common design objectives: (1) minimize latency given an area budget, or (2) minimize area given a latency upper bound. For simplicity, assume  $Lat_A(a)=Lat_B(a)$  for any a. In that case, to achieve optimality in either objective, the total logic resources,  $A_{total}$ , must be equally divided between stage<sub>A</sub> and stage<sub>B</sub>'s modules ( $A_A=A_B=0.5A_{total}$ ). The latency of the application is  $2Lat_{A/B}(0.5A_{total})$ . Solving either optimization scenarios repeatedly for different latency or area targets will produce a set of ASIC-style implementations that trade off latency against logic resources. Starting from this, we ask the question: can a PR-style design improve over the Pareto front of an ASIC-style design? **PR-Style Design.** The above scenario for the ASIC-style design is shown in Figure 3.3.a. In this area-time volume representation of the FPGA, the fabric area is 100% occupied by the modules for stage<sub>A</sub> and stage<sub>B</sub>. However, due to the dependency between the two modules, only one of the two modules is active at a time. In other words, the ASIC-style design has slack since some resources available to the design are not active all the time. In the area-time volume view, we see there are slack volumes when a module is idle i.e. when resources are occupied but not used.

In contrast to an ASIC-style design where resource allocation cannot change over time, it is possible to reduce slack with better area-time scheduling in a PR-style design. Therefore, a PR-style design may be able to achieve a smaller area-time volume by being faster, by using fewer resources, or both. For instance, to minimize latency given the same area budget, we can allocate the entirety of  $A_{total}$  to a module for stage<sub>A</sub> first and then to stage<sub>B</sub> (Figure 3.3.b). By doing so, the PR-style design's latency is reduced as both modules now run faster using all the resources available. On the other hand, a PR-style design can maintain the same latency using half the resources by allocating  $0.5A_{total}$  to a module for stage<sub>A</sub> first and then to stage<sub>B</sub> (Figure 3.3.c). With slack reduced, both PR-style designs fit into smaller area-time volumes than the ASIC-style design. Notice in Figure 3.3.b and Figure 3.3.c, a small amount of slack appears when switching between modules to reflect the non-zero delay to perform PR. The full model in Chapter 4 will account for the effect of PR time.

**Other Forms of Slack.** In the area-time volume representation, slack represents inefficiency. In ASICstyle designs, slack stemming from module dependencies cannot be eliminated without changing the initial algorithm or implementation; it is a consequence of statically allocating resources. We find that reducing slack is the most important opportunity for improvement available to PR-style designs. Slack can arise in other forms in ASIC-style designs.

In our simplified example, we assume that module variants exist for any amount of resources. In practice, module variants for a stage only exist at certain performance/resource combinations. The modules selected to fit an area budget in an optimal ASIC-style design may not sum up perfectly to use all the resources. Further, when the modules of  $stage_A$  and  $stage_B$  are executed in a pipelined fashion to improve the throughput of many independent executions, it may not be possible to always find equal throughput variants for the two stages; in the resulting unbalanced pipelines, a too-fast stage has to stop or slow down to wait for the other stage. A more subtle example of slack exists when implementing a generic engine capable of accelerating different algorithms or neural networks. This generalized engine consists of a superset of features to accommodate all possibilities but only a subset of features is needed at a time (e.g., NPU [27], DPU [95]). A PR-style design could potentially reduce this type of slack (only the variant needed at a time occupies the fabric).

### Chapter 4

## Analytical Approach to PR

This chapter discusses different PR execution strategies to design area-efficient PR-style designs and presents our complete analytical model briefly introduced in the previous chapter.

#### 4.1 Overview

**Optimization Goals.** To derive our performance model, we consider the problem of maximizing an application's performance given an area budget.

- minimize the application's latency given an area budget A. We label this problem as min L given A.

- maximize the application's throughput given an area budget A. We label this problem as max T given

A.

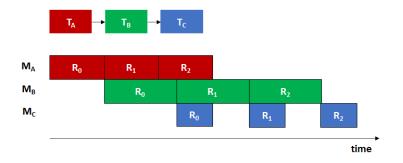

**Execution Model.** Table 4.1 lists all the parameters used in our model. In this chapter, an application consists of a single task with N dependent stages; each stage is accelerated by a module. Dependent modules share data either through external or on-chip memory depending on data size. Though our discussion focuses on tasks with dependent stages, our model also applies if stages are independent. A single start-to-finish execution of a module is referred to as a run. If a task requires multiple independent runs, modules can execute concurrently. Figure 4.1 illustrates this execution model. The example application consists of three dependent stages  $stage_A$ ,  $stage_B$ , and  $stage_C$  accelerated by three modules. In this application, each module needs to complete three runs  $R_0$ ,  $R_1$ , and  $R_2$ . Modules execute concurrently to complete the runs as quickly as possible, subject to the dependency constraints.

| Α             | Area budget                                                                   |

|---------------|-------------------------------------------------------------------------------|

| Ν             | Number of stages in a task                                                    |

| P             | Performance                                                                   |

| L             | Latency                                                                       |

| Т             | Throughput                                                                    |

| В             | Batch size                                                                    |

| R             | Execution run                                                                 |

| M             | Module                                                                        |

| $a_i$         | Area of module variant accelerating $stage_i$                                 |

| $Lat_i()$     | Latency of module variant accelerating $stage_i$                              |

| $Tput_i()$    | Throughput of module variant accelerating $stage_i$                           |

| $Time_{PR}()$ | Time to reconfigure a PR region                                               |

| F             | Scaling factor                                                                |

| $BW_i$        | Memory bandwidth requirement of the module variant that accelerates $stage_i$ |

| $BW_{total}$  | Total memory bandwidth available                                              |

Table 4.1: Model parameters.

Figure 4.1: Example timeline of an application with three dependent stages accelerated by modules  $M_A$ ,  $M_B$ , and  $M_C$ .

We consider two performance metrics, latency and throughput. Latency is defined as the start-to-finish time required for all modules accelerating a task to complete one run (including I/O time for data read and write and compute time). Throughput is defined as the number of runs completed per unit time in steady-state.

**Performance-Area Trade-offs.** For each module, a finite set of implementation variants exists. A variant accelerating  $stage_i$  is characterized by its area  $a_i$ , its latency  $Lat_i(a_i)$ , and its throughput  $Tput_i(a_i)$  as functions of area. We assume that  $Lat_*$  and  $Tput_*$  are monotonically increasing functions but make no further assumption on their shape, e.g., performance can scale sub-linearly or linearly with area.

Figure 4.2: In an ASIC-style design, dependent modules share data through either external (blue) or on-chip memory (orange) depending on data size.

**PR-Style Design Considerations.** We define  $Time_{PR}(a)$  as the time to reconfigure a PR region of size a, and assume that PR time is proportional to the PR region size.

#### 4.2 ASIC-Style

We first derive the equations for the ASIC-style design that are applicable whether dependent modules share data through external or on-chip memory (Figure 4.2). In both cases, the number of buffers required to hold intermediate data is N + 1. In all equations, we define I as the set of subscripts for stages in the task. **Min L Given A.** Let  $Lat_{Asic}(A)$  be the latency of the ASIC-style design given A resources.

$$Lat_{\mathsf{Asic}}(A) = \sum_{i \in I} Lat_i(a_i), \sum_{i \in I} a_i \le A$$

(4.1)

Max T Given A. Let  $Tput_{Asic}(A)$  be the throughput of the ASIC-style design given A resources.

$$Tput_{\mathsf{Asic}}(A) = \min(\{Tput_i(a_i) \mid i \in I\}), \sum_{i \in I} a_i \le A$$

$$(4.2)$$

#### 4.3 PR-Style

#### 4.3.1 Ignoring PR Time: PR-Style Performance Bounds