### Accelerating the "Motifs" in Machine Learning on Modern Processors

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

$\mathrm{in}$

Electrical and Computer Engineering

#### Jiyuan Zhang

B.S., Electrical Engineering, Harbin Institute of Technology

Carnegie Mellon University

Pittsburgh, PA

December 2020

©Jiyuan Zhang, 2020

All Rights Reserved

### Acknowledgments

First and foremost, I would like to thank my advisor — Franz. Thank you for being a supportive and understanding advisor. You encouraged me to pursue projects I enjoyed and guided me to be the researcher that I am today. When I was stuck on a difficult problem, you are always there to offer help and stand side by side with me to figure out solutions. No matter what the difficulties are, from research to personal life issues, you can always consider in our shoes and provide us your unreserved support. Your encouragement and sense of humor has been a great help to guide me through the difficult times. You are the key enabler for me to accomplish the PhD journey, as well as making my PhD journey less suffering and more joyful.

Next, I would like to thank the members of my thesis committee – Dr. Michael Garland, Dr. Phil Gibbons, and Dr. Tze Meng Low. Thank you for taking the time to be my thesis committee. Your questions and suggestions have greatly helped shape this work, and your insights have helped me understand the limitations that I would have overlooked in the original draft. I am grateful for the advice and suggestions I have received from you to improve this dissertation. This thesis would not have been possible without the guidance and patience of you.

In addition, I am extremely grateful for the endless support from the

Spiral group and colleagues at A-Level. Thank you professor James Hoe. You are such a wonderful professor to have at A-level. Your encouragement for us to think critically and to express our thoughts no matter how immature they are, has been a big encouragement for me. I am also extremely thankful for professor Tze Meng Low. It was such a luck to have you in the group when I just started graduate school. You are a great help in my research journey. Those discussions with you were very inspirational for a early-year PhD. They definitely shaped my understanding of research and taught me how to be a responsible researcher. I would also like to thank Dr. Scott McMillan for those helpful discussions and advice on my research and guiding me into the world of graph-related motifs. I cannot adequately express how thankful I am. Additionally, thank you my wonderful colleagues at A-level - Richard, Thom, Daniele, Fazle, Marie, Joe, Guanglin, Zhipeng, Ke, Senbo, Anuva. My experience in the graduate school was greatly enhanced as I was surrounded by so many wonderful friends and colleagues. I would never forget those research-related and non-research-related discussions with you guys. It has been so much fun and thought-provoking. Also, thank you my friends — Yi Lu, Zhuo Chen, Yang Gao, Qichen Huang, Chenglei Fang, Yang li, for being great friends, the source of great emotional support.

I would also like to thank my funding resources. The research in this thesis is based upon work funded and supported by DARPA under agreement HR0011-20-9-0018, DE-AC02-05CH11231, HR00111320007 and FA87501220291. This thesis is also based upon work funded and supported by the Department of Defense under Contract No. FA8702-15-D-0002 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center. Last but not least, I owe an especially deep gratitude to my parents for their never-ending love, patience, and encouragement.

JIYUAN ZHANG

Carnegie Mellon University December 2020

## Abstract

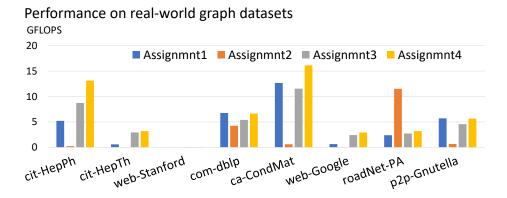

The booming growth in AI and machine learning is drastically reshaping the landscape of high performance computing. Traditional HPC addresses scientific problems that are driven by simulation, modeling and analysis in science domains. Algorithms like linear algebra and methods like differential equations are at the core of solutions to such problems. However, emerging machine learning tasks rest on a new set of algorithms and models. The computation and data movement patterns inherent in learning algorithms cannot be directly mapped to the computation motifs in the physics, chemistry, or biology simulation problems. As a result, the high performance libraries that originate in the traditional scientific domains thus cannot be straightforwardly applied to emerging ML tasks to deliver required performance.

This thesis focuses on performance optimizations of computation kernels in emerging machine learning applications, spanning across a diverse range from dense, regular to sparse and irregular kernels. In this work, we demonstrate how code specialization and generation together with expert-built performance models and learned dispatch strategies can together enable ML motifs to achieve better performance on modern processors.

First, we investigate the performance optimization of dense kernels with a focus on the convolutional neural networks (CNN). The computation of convolution layers in deep neural networks typically relies on high performance matrix-multiplication routines to improve performance. However, these routines are not optimized for performing convolution. Extra memory overhead is incurred due to data transformation, and the performance obtained is also less than conventionally expected. We demonstrate that direct convolution, when implemented *correctly*, eliminates all memory overhead, and yields performance that is between 10% to 4x better than existing high performance implementations on conventional and embedded CPU architectures. We present a model-guided optimization approach which utilizes the characteristics of system architectures to guide the optimization choices of loop ordering, blocking, and memory layout transformation. We show that a high performance direct convolution exhibits better performance scaling than expert-tuned matrix implementation, i.e. suffers less performance drop, when increasing the number of threads.

Sparse kernel is an equally important computation kernel appearing in many machine learning applications such as graph analytics and genetic sequencing. One factor that prevents sparse kernels from achieving high performance on modern processors results from the prohibitively large number of different implementations and data structures for sparse problems. We start with the observation that the complicated sparse computations can be distilled into primitive set of operators such as join, merge, and difference. To accelerate those operators on modern processors with data parallelism, we propose a vectorization and code specialization approach which can eliminate the control divergences of these operators. Next, we explore the design space for vectorization on CPUs with various vector width, based on which we present the code generation algorithm that takes the data width and operations as input and generates various implementations. We then demonstrate the acceleration of the General Sparse Matrix-Matrix Multiplication (SpGEMM) on GPUs. We show how the SpGEMM implementation can leverage join/merge operators to compose a variety of implementations. Another challenge when optimizing sparse kernels is that their performance behavior is data dependent, while the input characteristics may change online during iterative updates. To leverage the different implementations offered by the code generator, we propose a lowoverhead mechanism that collects the data characteristic information to learn online dispatch decisions over iterations.

Overall, in this thesis, we demonstrate the interplay of code specialization and generation, together with performance modeling, learned dispatch, can enable high performance kernels for the emerging machine learning applications.

## Contents

| Ackno   | wledgr | nents                                     | iii |

|---------|--------|-------------------------------------------|-----|

| Abstra  | act    |                                           | vi  |

| List of | Figur  | es                                        | xv  |

| List of | Table  | S                                         | xxi |

| Chapt   | er 1 I | ntroduction                               | 1   |

| 1.1     | Motiv  | ation                                     | 1   |

| 1.2     | Prelin | ninaries                                  | 4   |

|         | 1.2.1  | Domains and Computation Kernels           | 4   |

|         | 1.2.2  | Frameworks and Libraries                  | 5   |

|         | 1.2.3  | Code Generation                           | 8   |

|         | 1.2.4  | Performance Optimization                  | 8   |

|         | 1.2.5  | Hardware Architectures                    | 9   |

| 1.3     | Dense  | Computational Kernels in Neural Networks  | 10  |

| 1.4     | Sparse | e Computational Kernels in Data Analytics | 12  |

| 1.5            | Thesis Overview                                             | 14 |

|----------------|-------------------------------------------------------------|----|

| Chapte         | er 2 Accelerating Dense Convolutions                        | 17 |

| 2.1            | Overview                                                    | 18 |

| 2.2            | Introduction                                                | 20 |

| 2.3            | Background                                                  | 23 |

| 2.4            | High Performance Direct Convolution                         | 27 |

|                | 2.4.1 Strategy for Mapping Loops to Architecture            | 27 |

|                | 2.4.2 Parallelism                                           | 33 |

| 2.5            | Convolution-Friendly Data Layout                            | 34 |

|                | 2.5.1 Input/Output Layout                                   | 34 |

|                | 2.5.2 Kernel Layout                                         | 35 |

|                | 2.5.3 Backward Compatibility                                | 36 |

| 2.6            | Experiments                                                 | 38 |

|                | 2.6.1 Experimental Setup                                    | 38 |

|                | 2.6.2 Performance                                           | 39 |

|                | 2.6.3 Parallel Performance                                  | 40 |

| 2.7            | Chapter Summary                                             | 43 |

| Chapte         | er 3 Sparse Computational Kernels: A Preliminary            |    |

| $\mathbf{Stu}$ | dy                                                          | 45 |

| 3.1            | Expressing Computation Kernels in Sparse Applications       | 47 |

| 3.2            | Accelerating Sparse Computation: A Case Study with Triangle |    |

|                | Counting                                                    | 49 |

|        | 3.2.1  | Introduction                                     |    | 49 |

|--------|--------|--------------------------------------------------|----|----|

|        | 3.2.2  | Algorithm                                        | •  | 51 |

|        | 3.2.3  | Parallel Triangle Counting                       | •  | 52 |

|        | 3.2.4  | Preliminary Exploration on Optimizations         |    | 53 |

|        | 3.2.5  | Profiling and Analysis                           | •  | 56 |

|        | 3.2.6  | Understanding the Optimizations                  | •  | 64 |

|        | 3.2.7  | Performance Results                              |    | 65 |

| Chapte | er 4   | Accelerating Sparse Computational Kernels        | on |    |

| CPU    | Us: A  | Fast SIMD Set Intersection Approach              |    | 69 |

| 4.1    | Abstra | act                                              |    | 70 |

| 4.2    | Introd | luction                                          |    | 71 |

| 4.3    | Backg  | round and Related Work                           |    | 74 |

|        | 4.3.1  | Scalar Set Intersection Approaches               |    | 76 |

|        | 4.3.2  | Accelerating Set Intersections                   |    | 78 |

| 4.4    | The F  | ESIA Approach                                    |    | 79 |

|        | 4.4.1  | Overview                                         | •  | 80 |

|        | 4.4.2  | Data Structure                                   |    | 80 |

|        | 4.4.3  | Intersection Algorithm                           | •  | 82 |

|        | 4.4.4  | Theoretical Analysis                             |    | 83 |

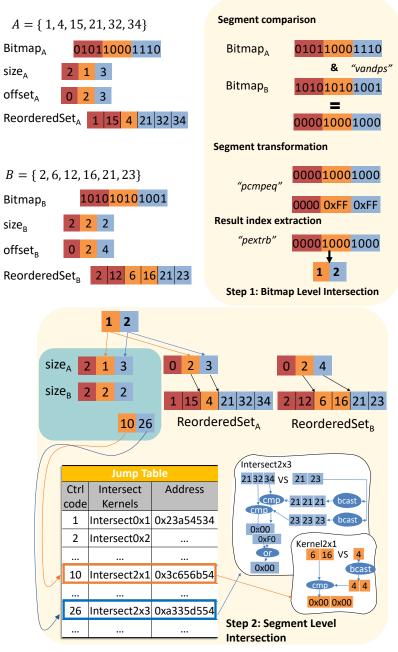

| 4.5    | Bitma  | p-Level Intersection                             |    | 85 |

| 4.6    | Segme  | ent-Level Intersection                           |    | 87 |

|        | 4.6.1  | Runtime Dispatch                                 |    | 89 |

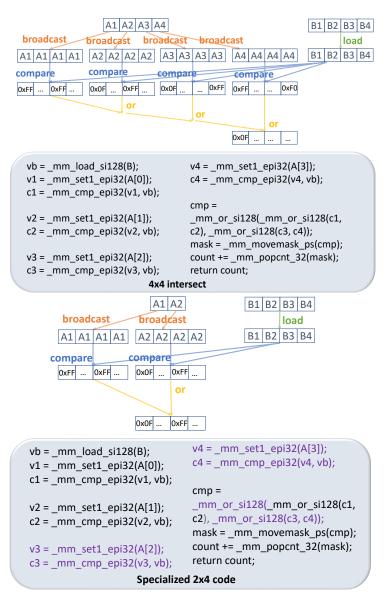

|        | 4.6.2  | Specialized vs. General Set Intersection Kernels |    | 91 |

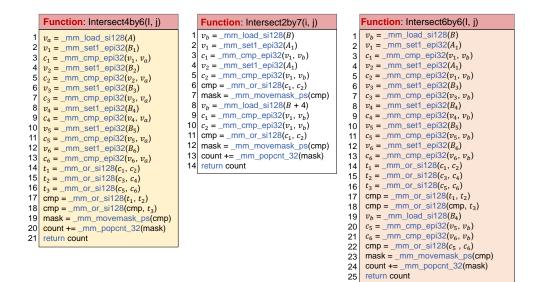

|     | 4.6.3  | Implementing Specialized Intersection Kernels with SIMD | 92  |

|-----|--------|---------------------------------------------------------|-----|

| 4.7 | Discus | sion                                                    | 96  |

| 4.8 | Exper  | iments                                                  | 99  |

|     | 4.8.1  | Experimental Setup                                      | 100 |

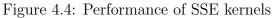

|     | 4.8.2  | Result of Specialized Intersection Kernels              | 101 |

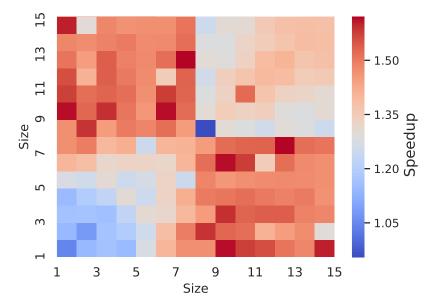

|     | 4.8.3  | Effect of Varying the Input Size                        | 103 |

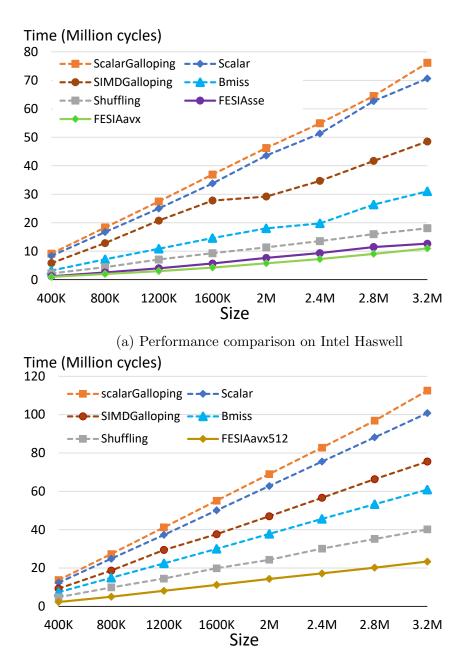

|     | 4.8.4  | Effect of Varying the Selectivity                       | 105 |

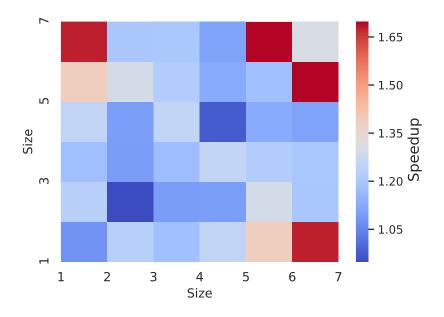

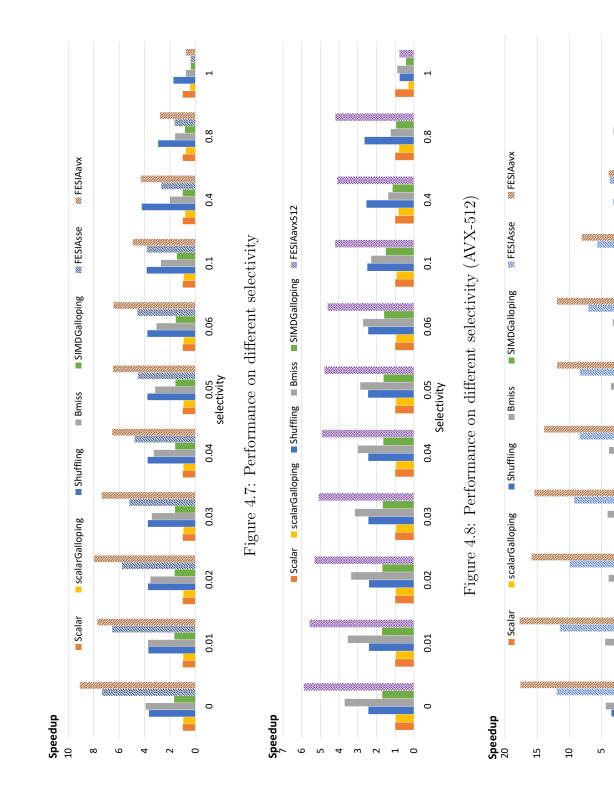

|     | 4.8.5  | Performance of Two Sets with Different Sizes            | 107 |

|     | 4.8.6  | Performance on Real-World Datasets                      | 110 |

| 4.9 | Conclu | usion                                                   | 111 |

|     |        |                                                         |     |

### Chapter 5 Accelerating Sparse Computational Kernels on

| GP  | Us     |                                  | 113 |

|-----|--------|----------------------------------|-----|

| 5.1 | Abstra | act                              | 114 |

| 5.2 | Introd | luction                          | 115 |

| 5.3 | Backg  | round and Related Work           | 118 |

|     | 5.3.1  | GPUs                             | 118 |

|     | 5.3.2  | SpGEMM and Masked-SpGEMM Problem | 121 |

|     | 5.3.3  | Sparse Data Structure            | 122 |

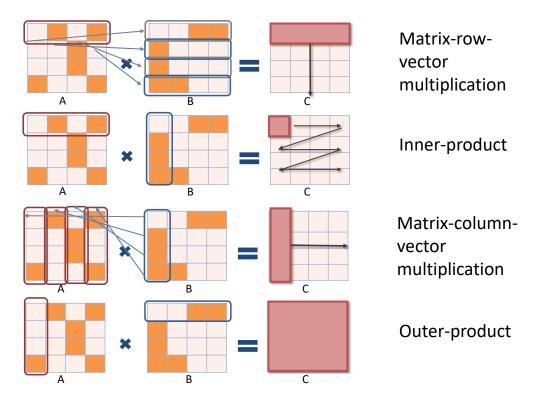

|     | 5.3.4  | SpGEMM Computations              | 123 |

| 5.4 | The F  | amily of SpGEMM Algorithms       | 124 |

|     | 5.4.1  | Matrix-Vector SpGEMM             | 125 |

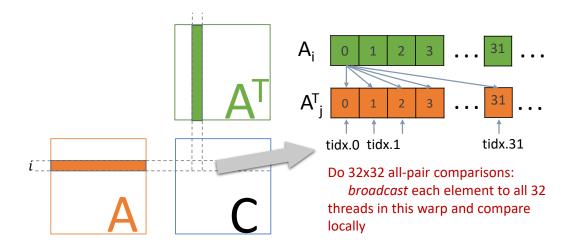

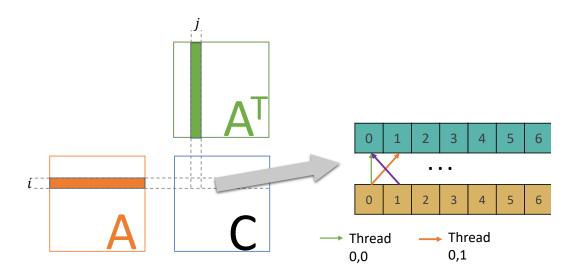

|     | 5.4.2  | Inner-Product-Based SpGEMM       | 127 |

|     | 5.4.3  | Outer-Product-Based SpGEMM       | 129 |

| 5.5    | Join-E | Based SpGEMM                                         | 130 |

|--------|--------|------------------------------------------------------|-----|

|        | 5.5.1  | The Baseline Join-Based SpGEMM                       | 130 |

|        | 5.5.2  | The Data-Parallel Join-Based SpGEMM                  | 131 |

|        | 5.5.3  | Join Using Wider Data Types                          | 133 |

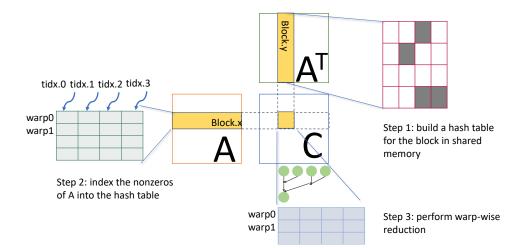

| 5.6    | Join-E | Based SpGEMM Using Hash Methods                      | 137 |

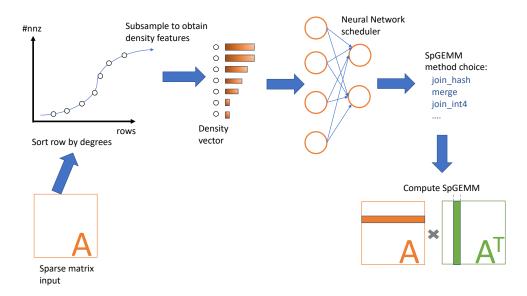

| 5.7    | Online | e Scheduling                                         | 139 |

| 5.8    | Exper  | iments                                               | 142 |

|        | 5.8.1  | Experimental Setups                                  | 142 |

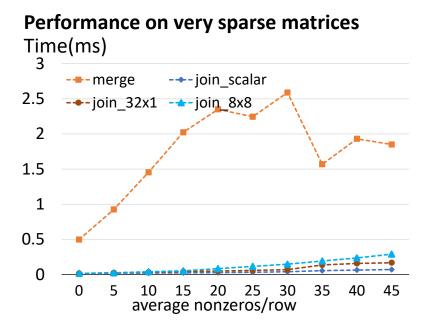

|        | 5.8.2  | Performance of GPU Joins with Very Sparse Matrices . | 145 |

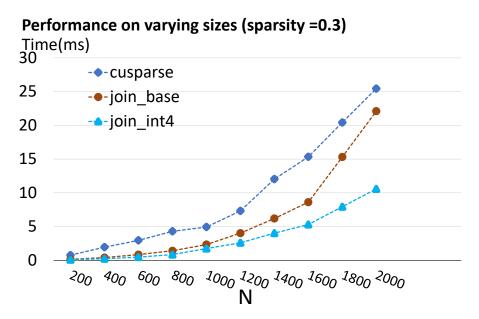

|        | 5.8.3  | Performance of Join-Based SpGEMM                     | 146 |

|        | 5.8.4  | Comparison on Different Densities                    | 147 |

|        | 5.8.5  | Performance on the Hash-Based Join Kernels           | 149 |

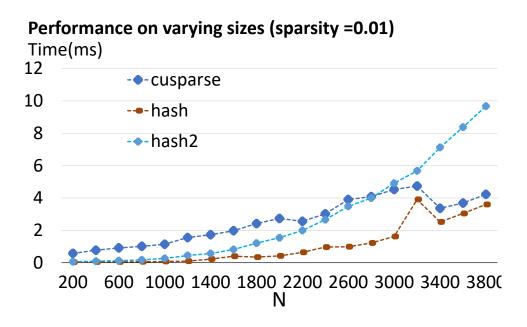

|        | 5.8.6  | Performance on Real-World Dataset                    | 153 |

|        | 5.8.7  | Performance on Real-World Graph Datasets with        |     |

|        |        | Skewed Distribution                                  | 156 |

| Chapte | er 6 S | Summary and Future Directions                        | 161 |

| 6.1    | Summ   | ary                                                  | 162 |

| 6.2    | Takea  | ways and Reflections                                 | 164 |

| 6.3    | Future | e Directions                                         | 167 |

# List of Figures

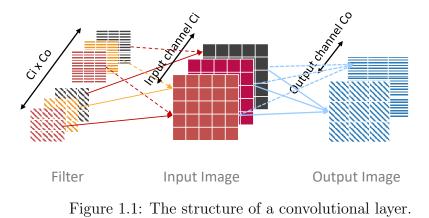

| 1.1 | The structure of a convolutional layer.                         | 11 |

|-----|-----------------------------------------------------------------|----|

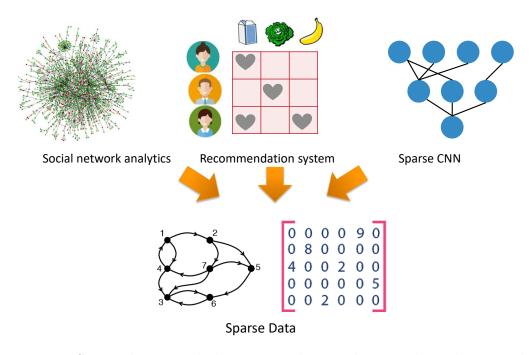

| 1.2 | Sparse data is underlying many data analytics tasks such as so- |    |

|     | cial network anlaytics, recommendation system, sparse machine   |    |

|     | learning models                                                 | 12 |

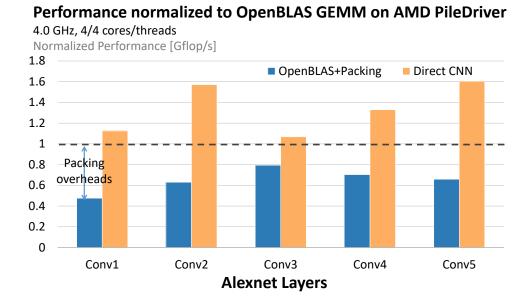

| 2.1 | High performance direct convolution implementation achieves     |    |

|     | higher performance than a high performance matrix multiplica-   |    |

|     | tion routine, whereas matrix-multiplication based convolution   |    |

|     | implementations suffers from packing overheads and is limited   |    |

|     | by the performance of the matrix multiplication routine         | 19 |

- 2.2 The 5 × 5 input image with 3 different channels (denoted with different colors) is convolved with two separate kernels to obtain a 3 × 3 output with two output channels. Packing is performed to turn three dimensional input images (left) into a two dimensional matrix (right) in order to utilize a high performance matrix multiplication routine. As  $C_o$  and/or ( $H_o \times W_o$ ) are often less than  $H_f \times W_f \times C_i$ , performance of standard matrix-matrix multiplication in many BLAS libraries are often sub-optimal.

- 2.3 Convolution-friendly layout for input/output (left) and kernel weights (right). The output data is organized into sequential blocks of  $H_o \times W_o \times C_{o,b}$ , where in each block, the fastest dimension is in the channel dimension, followed by the column and row dimension of the output. The kernel weights are organized into blocks of  $H_o \times W_o \times C_{o,b} \times C_{i,b}$ . The fastest dimension is the blocked output channel, followed by the blocked input channels, kernel width and height, input channels and then the output channels. .....

25

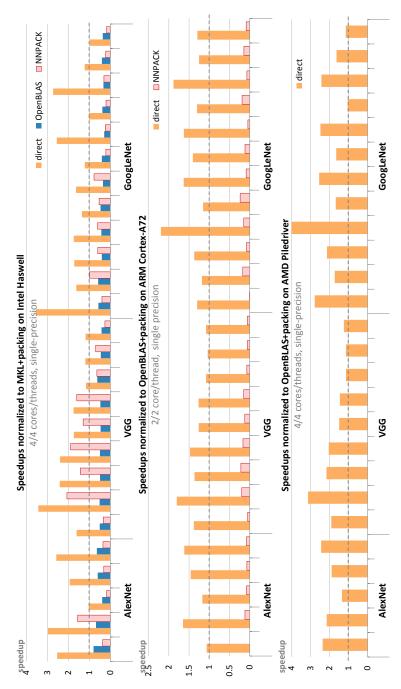

- 2.4 Performance of direct convolution against existing high performance FFT-based and SGEMM-based convolution implementations. Performances of all implementations are normalized to the performance of SGEMM +im2col routine. Direct convolution is highly competitive against all other implementations achieving between 10% and 400% improvement in performance even against a BLAS library (Intel MKL) that optimizes for matrix shapes arising from convolution layers.

- 2.5 Scaling behavior with increasing number of threads. Our direct convolution implementation retains high GFLOPs per core performance as we increase the number of threads from 1 to the number of available cores. This is indicative of an efficient parallelized algorithm. When the number of threads exceeds the number of cores, excessive contention results in a significant drop in performance per core. In contrast, SGEMM has poor scalability even when the number of threads is low (e.g. 2). . . 42

41

| 3.1 | SIMD algorithm assuming simd width is 4 elements               | 55 |

|-----|----------------------------------------------------------------|----|

| 3.2 | SIMD algorithm illusion                                        | 56 |

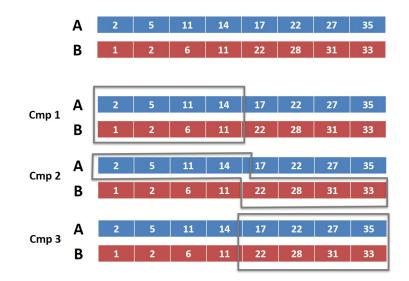

| 3.3 | Degree distribution of cit-Patents                             | 58 |

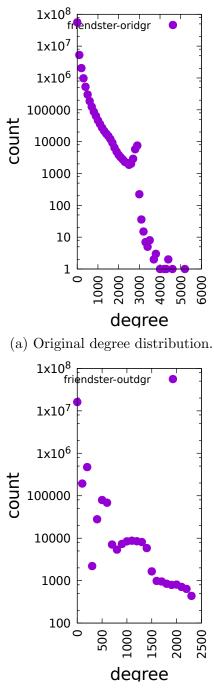

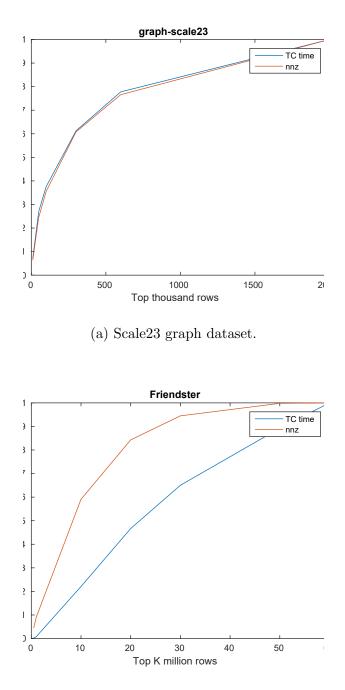

| 3.4 | Degree distribution of friendster                              | 59 |

| 3.5 | Degree distribution of graph500-scale23.                       | 60 |

| 3.6 | Theoretical computation distribution and non-zero element dis- |    |

|     | tribution on graphs with different skewness.                   | 62 |

| 3.7 | Number of Non-zero element distribution and computation time |    |

|-----|--------------------------------------------------------------|----|

|     | distribution across rows.                                    | 63 |

4.1 Illustrating the data structure and the set intersection algorithm in FESIA. There are two steps in the set intersection: (1) the bitmaps are used to filter out unmatched elements, and (2) a segment-by-segment comparison is conducted to compute the final set intersection using specialized SIMD kernels.

75

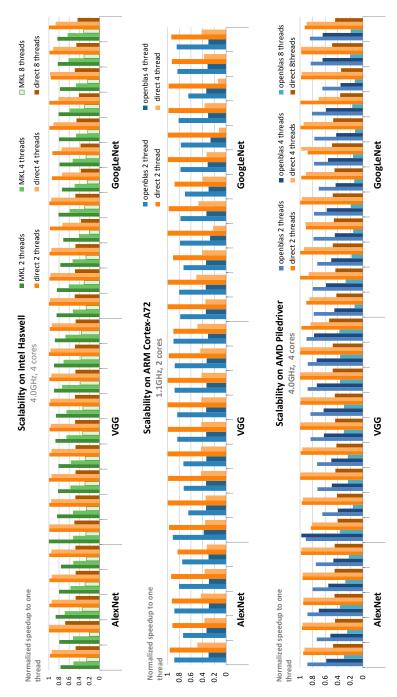

- Illustrating the difference between a general and a specialized 4.2 SIMD set intersection kernels. A general kernel is shown on the upper part of this figure, which is implemented with SSE-128 instructions and can be used for any intersection with input size less than 4-by-4. A specialized 2-by-4 kernel is shown on the bottom, which reduces unnecessary computation and memory 88 accesses (highlighted in purple). Illustrating the specialized kernels: (1) a 2-by-7 intersection 4.3 kernel (small-by-large), (2) a 4-by-5 intersection kernel (smallby-large and  $S_b$  is slightly larger than V), and (3) a 6-by-6 intersection kernel (large-by-large). 93 4.4Performance of SSE kernels 102

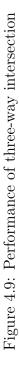

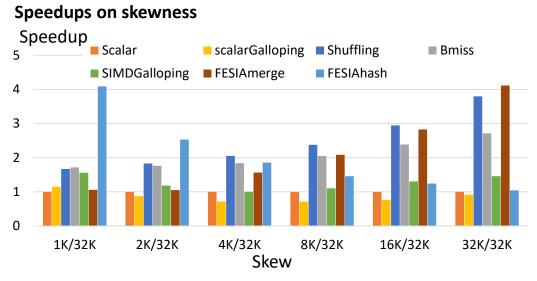

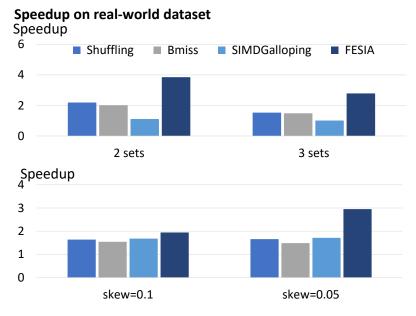

| 4.9  | Performance of three-way intersection                             | 106 |

|------|-------------------------------------------------------------------|-----|

| 4.10 | Performance comparison on varying skew                            | 108 |

| 4.11 | Results on the database query task                                | 109 |

| 4.12 | Results on the triangle counting task                             | 111 |

| 5.1  | The family of SpGEMM algorithms                                   | 119 |

| 5.2  | Complexity comparison on different sparse matrices. $N$ denotes   |     |

|      | the maximum dimension of the sparse matrix (i.e., maximum         |     |

|      | nonzero value). $k$ denotes the average nonzeros per row/column   |     |

|      | — for tall-skinny matrix, $k$ is the average nonzeros per row. If |     |

|      | the matrix is short and fat, $k$ is average nonzeros per column.  | 120 |

| 5.3  | All-pair comparison based join implementation: a 32-by-32 im-     |     |

|      | plementation.                                                     | 133 |

| 5.4  | All-pair comparison based join implementation: a 8-by-8 imple-    |     |

|      | mentation.                                                        | 134 |

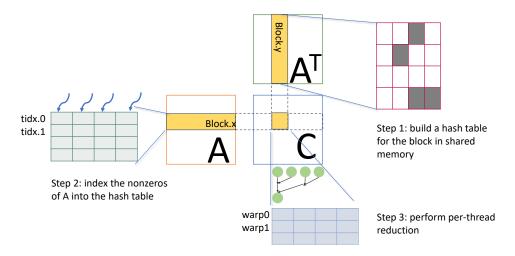

| 5.5  | Hash-based SpGEMM implementation: parallel across columns.        | 138 |

| 5.6  | Hash-based SpGEMM implementation: parallel across rows.           | 139 |

| 5.7  | Online scheduling strategy                                        | 141 |

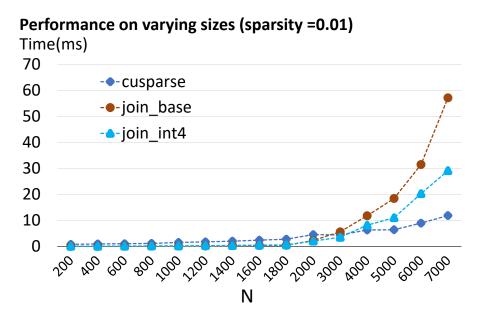

| 5.8  | Comparison of join implementations on very sparse matrices        | 146 |

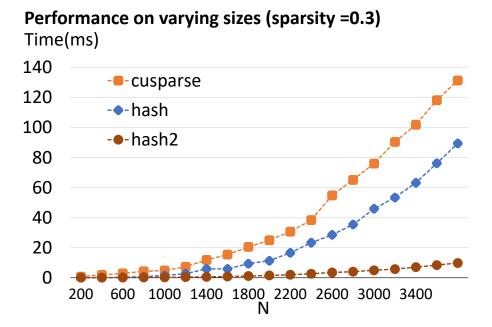

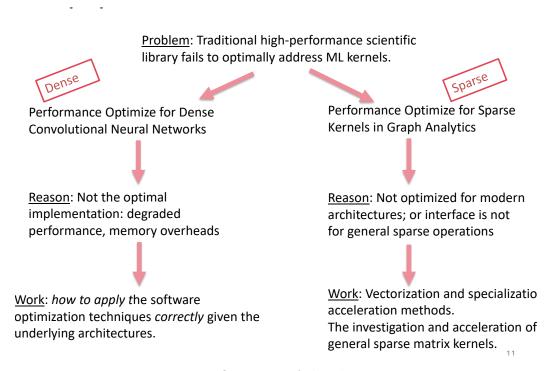

| 5.9  | Comparison of join implementations on relatively dense syn-       |     |

|      | thetic data in which the densities are 0.3                        | 148 |

| 5.10 | Comparison of join implementations on relatively sparse syn-      |     |

|      | thetic data in which the densities are 0.01                       | 148 |

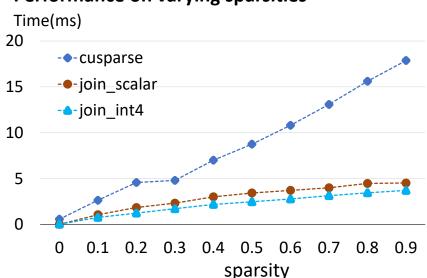

| 5.11 | Comparison of join implementations on varying sparsities          | 149 |

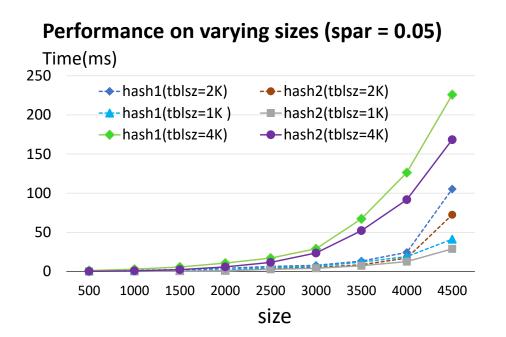

| 5.12 | Comparison of hash-based join implementations on datasets of        |     |

|------|---------------------------------------------------------------------|-----|

|      | density 0.05. The hash table size is 1KB per row. tblsz =           |     |

|      | 1K/2K/4K refers to building one hashtable for $1/2/3$ rows re-      |     |

|      | spectively.                                                         | 151 |

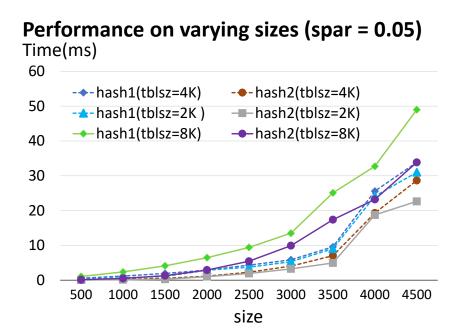

| 5.13 | Comparison of hash-based join implementations on datasets of        |     |

|      | density 0.05. The hash table size is 2KB per row. We build          |     |

|      | a hash<br>table for $1/2/3$ rows simultaneously. tblsz = $1K/2K/4K$ |     |

|      | refers to building one has<br>htable for $1/2/3$ rows respectively  | 152 |

| 5.14 | Comparison of hash-based join implementations on relatively         |     |

|      | sparse synthetic data in which the densities are $0.3.$             | 153 |

| 5.15 | Comparison of hash-based join implementations on relatively         |     |

|      | sparse synthetic data in which the densities are 0.01. $\ldots$     | 154 |

| 5.16 | Comparison of different thread assignment strategies on real-       |     |

|      | world graph datasets.                                               | 160 |

| 6.1  | Overview of this dissertation                                       | 169 |

| 0.1  |                                                                     | 102 |

## List of Tables

| 2.1 | Details of specific architecture used                          | 38  |

|-----|----------------------------------------------------------------|-----|

| 3.1 | Compression savings on Friendster dataset. Its original edge   |     |

|     | list size is 1,806,067,135                                     | 65  |

| 3.2 | Single-core performance scalar vs. SIMD                        | 67  |

| 3.3 | Small 28-core system performance                               | 67  |

| 3.4 | Performance on a HP Superdome X system with 16 sockets, 352    |     |

|     | cores                                                          | 68  |

| 4.1 | The summary of our approach vs. state-of-the-art set intersec- |     |

|     | tion approaches                                                | 72  |

| 4.2 | Hardware specifications                                        | 100 |

| 4.3 | The details of each graph dataset                              | 110 |

| 5.1 | Performance comparison on iterative SpGEMM computations        |     |

|     | with real-world datasets                                       | 156 |

| 5.2 | Graph dataset characteristics.                                 | 159 |

### Chapter 1

### Introduction

### 1.1 Motivation

Performance has always been of utmost importance in many computing tasks, which has been the driving force behind the research of high performance computing over the decades. Traditional HPC mainly focuses on the scientific computing tasks which usually arise from the simulation or modeling processes for biology, physics or chemistry problems. For example, typical scientific computing tasks include weather prediction, quantum mechanics simulation, and cosmopolitan analysis.

Solutions to these scientific tasks are usually based on mathematic methods in linear algebra or differential equations. Thus the computational kernels of these methods are centered around dense linear algebra or structured mesh. Over the years tremendous efforts are spent on researching and designing high performance implementations for those computing kernels in scientific applications. This leads to a handful of libraries and frameworks. For example, BLAS/LAPACK libraries were developed for the computing kernels in linear algebra, FFTX library was proposed targeting spectral methods, and OSKI was proposed for the sparse linear algebra kernels in differential equations.

In recent years, machine learning has made significant breakthroughs which brought transformations across many aspects of research and industry. In many real-world problems, the conventional methodologies and algorithms are now replaced by ML-based models. For example, methods such as deep learning and graph analytics are now at the core of tasks such as image classification, voice recognition or object tracking. Despite their wide adoption, however, it is still ongoing research on how to make the emerging ML models run faster and efficiently on various platforms. The computation kernels of ML models are completely different from the conventional scientific kernels, Thus high performance libraries developed for scientific computing can not be directly applied to the machine learning field.

Achieve high performance for the emerging machine learning tasks is challenging due to two reasons. Firstly, computation kernels in machine learning tasks possess a broad spectrum of distinctions in the characteristics of computation patterns and data movements. At one end of the spectrum, there is dense applications, in which the computation kernels of such tasks have regular and structured patterns. The representative dense computation tasks include convolutional-neural-networks. At the other end of the spectrum is the sparse applications, and such applications usually works with irregular and unstructured data. The representative sparse applications involves some analytics tasks in social networks or recommendation systems. Dense and sparse computation kernels present different computational characteristics, which result in different sets of challenges for software optimizations. The second performance challenge results from the complexities of the underlying hardware. In particular, with the growing computational demand for machine learning tasks, the underlying computer systems are evolving rapidly. Architecture features such as cache size, number of registers, memory bandwidth vary across platforms, which makes obtaining high performance consistently across platforms a non-trivial task.

With the growing prevalence of machine learning techniques and their widespread deployment onto a broad spectrum of systems, there is a pressing need for high performance machine learning libraries or frameworks on existing and future platforms.

The goal of this thesis is to provide understandings on the optimizations of the computation kernels of the emerging ML tasks. The computation kernels lay the backbone of understanding the interplay between software optimizations and hardware architecture, which is a fundamental step towards building a portable and efficient end-to-end ML system. In particular, in this work, we demonstrate how an analytical model, together with code specialization, and learned dispatch strategies can enable the high performance computational kernels of machine learning tasks. In the first part of this work, we demonstrate the optimization of the dense kernels in machine learning using convolution neural networks as an example. We adopt a model-based analysis to provide a systematic understanding of how the software optimizations such as loop ordering, blocking, instruction scheduling, should be applied based on the hardware architectures. In the second part of this work, we investigate the optimizations of sparse kernels. Sparse kernels present a different set of challenges compared to dense computations. We present the technique that can improve the data-parallelism of the irregular computations of sparse kernels, as well as investigating the effects of algorithm and data structure choices on the performances.

### **1.2** Preliminaries

In this section, we provide a brief overview of the computational domains and the class of operations in these domains that we target.

#### **1.2.1** Domains and Computation Kernels

Researchers from the University of California, Berkeley performed an investigation across different domains and distilled the computational kernels to characterize and represent the domain-specific computations [1]. We explain some kernels that are relevant to this thesis in the following.

**Dense linear algebra** These computations typically arise in the applications of scientific simulations. Dense linear algebra computation involves data as dense matrices or vectors. The computation pattern is regular with mostly strided memory access.

**Structured Mesh (Stencils).** These computations typically arise in the computation of PDEs using finite-difference methods. The computation of structure mesh usually involves data represented by a regular grid of n-dimensional mesh. The connection in the grid represents the relationship between this data point and its neighbors.

**Sparse linear algebra.** Sparse linear algebra can appear both in scientific computing as well as machine learning applications. Many real-world data contain a significant number of zero values. Therefore such data is usually stored in compressed matrices to reduce the storage and bandwidth requirements to access the elements. The data format examples include Compressed-Sparse-Row (CSR), Compressed-Sparse-Column (CSC), Coordinate (COO) format, etc. Because of the compressed formats, data is generally accessed with indexed loads and stores.

#### **1.2.2** Frameworks and Libraries

One approach to shifting the burden from the user is to implement libraries that contain commonly used functionality. This approach has been very successfully applied to dense computations and libraries like BLAS and LAPACK are frequently used in scientific codes.

#### Dense Linear Algebra

**Dense linear algebra in scientific computing** Basic Linear Algebra Subprograms (BLAS) specifies a set of standards for the common linear algebra operations. The linear algebra operations are categorized into Level-1, Level-2, and Level-3 routines in BLAS specification: Level-1 refers to vector operations such as vector addition, dot product. Level-2 refers to the general matrix-vector multiplication operation. Level-3 refers to the generalized matrix multiplication. A number of libraries have been proposed conforming to the BLAS specifications and are tuned for specific hardware. For example, AMD Core Math Library (ACML) has a high-performance BLAS routine implementation for AMD processors. Intel Math Kernel Library (MKL) is the BLAS implementation for Intel, and OpenBLAS provides high-performance BLAS implementations for a wide range of x86 architectures.

**Dense linear algebra in machine learning** Dense linear algebra kernels also appear in machine learning applications. Some computations in deep learning models can correspond to the BLAS operations. As a matter of fact, many machine learning frameworks heavily depend on high-performance BLAS routines. For example, the TensorFlow framework transforms the highlevel machine learning computations into primitive matrix operators such as matrix-matrix-multiplication (convolution neural network), matrix-vectormultiplication (recurrent neural network), etc.

#### Sparse Linear Algebra

**Sparse linear algebra in scientific computing** Sparse linear algebra kernels appear in both traditional scientific computing and machine learning applications. For example, the finite discretization in fluid flow simulations can be formulated using a sparse grid. Libraries have been proposed to accelerate sparse linear algebra kernels in scientific problems. For example, the Optimized Sparse Kernel Interface (OSKI) [48] exposed an autotuning API along with providing memory hierarchy aware kernels to match modern architectures, which allows library users to pass domain knowledge to these building blocks and reap the performance benefit while minimizing the amount of expensive autotuning.

**Sparse linear algebra in machine learning** Recent years, a growing body of research is focusing on sparse problems arising from the social sciences. As a result, we are seeing the development of sparse libraries and frameworks designed to accelerate graph analytics — the tasks that are underneath many social analytics problems. There are a rich amount of graph frameworks that can target a general set of graph applications [2, 3, 4, 5, 6, 7]. Those frameworks have different frontend designs. For example, [2] is based on vertex-iterator programming model where a utility function is supplied and executed on each vertex, [3] uses linear algebra language to abstract away the graph algorithms, meanwhile, [4] uses a set of DSL to describe and optimize graph operations, etc.

#### **1.2.3** Code Generation

Code generation can overcome the drawbacks of general compilers. The general compiler is capable of performing some optimizations such as autovectorization, peep-hole optimizations. However, their optimization capabilities are very limited. Firstly, the optimization effectiveness of the general compilers is highly dependent on accurate modeling of the underlying hardware, whereas it is usually hard to establish an exact model of the hardware architectures. More importantly, general compilers are unable to capture the high-level algorithmic optimizations. For example, the compiler is capable to perform auto-vectorization, but only when the code is inherently expressed as regular and iterative loops. Code generation offers an alternative approach that is capable to take into account the high-level algorithmic transformations while generating different implementations as specified by the programmers. The code generation approach can therefore ease the burden for programmers to explore different implementations, especially when facing the fast-changing and increasingly-complex hardware architectures.

#### **1.2.4** Performance Optimization

Implementing software that performs satisfactorily across platforms and hardware has become an ever-growing challenging task with the evolving complexity of today's computer systems. In conventional high performance computing, there are two approaches to achieve high performance: analytic modeling and automatic-tuning. Analytic modeling requires accurate modeling of the underlying computer architectures and analytically derive the best optimization strategies such as loop ordering, blocking strategies, parallelism, etc. Analytic modeling has been demonstrated to successfully optimize the implementation of BLAS libraries [8, 9]. Auto-tuning is another way to achieve high performance, especially when modeling the machine's behavior accurately enough is impossible on today's computers, auto-tuning can get the actual run time as feedback. By means of automatic empirical performance tuning, and apply search techniques to find the best implementation for a given target machine. Auto-tuning is applied in libraries such as Spiral [10], FFTW [11], and AT-LAS [12].

#### 1.2.5 Hardware Architectures

Vector instructions. A few years ago major vendors of general-purpose microprocessors have started to include short vector SIMD (single instruction, multiple data) extensions into their instruction set architecture (ISA) primarily to improve the performance of multimedia applications. Examples of SIMD extensions supporting both integer and floating-point operations include vectorized loads/stores, logic arithmetics, bit permutations, etc. SIMD instructions have now become the status quo on modern CPUs to exploit data parallelism. For example, Intel CPUs have SSE/AVX2 instructions to support 128-bit and 256-bit vector operations. Similarly, ARM processors have NEON instructions, and IBM Power processors have AltiVec instructions. The prevailing SIMD widths on modern processors are 128-bit and 256-bit. More recently, the Intel Skylake architecture introduced AVX512 instructions.

Hierarchical memory system. The modern processor is typically built with hierarchical memory structures. The closest to the processor is the register memory. The register file holds the temporary elements that are used for arithmetic tasks. The next level is the L1-cache (built into the processor) followed by the L2-cache. L1 caches are usually fast but small. They directly access the L2 cache which is usually larger but slower. L1-cache and L2-cache are usually private to each core. In the next level is the L3-cache which is usually shared among all the cores on the chip. The L3-cache accesses main memory which—on architectures with virtual memory—exchanges data with disk storage.

## 1.3 Dense Computational Kernels in Neural Networks

Convolution neural networks have received significant attention over recent years, as they are becoming one of the most popular models for many deep learning tasks. They are widely deployed for deep learning tasks such as image classification and segmentation, object detection, video processing, etc.

With CNN's wide adoption in varying deep learning tasks, as well as the ever-growing applications and scenarios, it also introduces new challenges and problems for computation and system designs. For example, there is a growing need of running machine learning tasks on devices like smartphones, cars, drones, etc. On such devices, the compute capability and memory capacity available are often limited. This naturally limits the size of the deep neural nets that can be placed on the system.

The computation of convolution layers in deep neural networks typically relies on high performance routines that trade space for time by using additional memory (either for packing purposes or required as part of the algorithm) to improve performance. The problems with such an approach are twofold. First, these routines incur additional memory overhead which reduces the overall size of the network that can fit on embedded devices with limited memory capacity. Second, these high performance routines were not optimized for performing convolution, which means that the performance obtained is usually less than conventionally expected. In this chapter, we demonstrate that direct convolution, when implemented *correctly*, eliminates all memory overhead, and yields performance that is between 10% to 400% times better than existing high performance implementations of convolution layers on conventional and embedded CPU architectures. We also show that a high performance direct convolution exhibits better scaling performance, i.e. suffers less performance drop, when increasing the number of threads.

## 1.4 Sparse Computational Kernels in Data Analytics

Figure 1.2: Sparse data is underlying many data analytics tasks such as social network anlaytics, recommendation system, sparse machine learning models.

Sparse computations are at the core of machine learning and data science applications. They has been employed in a broad range of tasks, such as graph analytics [13]. neural networks compressing [14], genome sequencing [15], recommendation systems [16]. The Sparse matrices in these problems are usually represented and recorded using the indices of the nonzero. And the percentage of non-zero elements in these applications can vary drastically, ranging from  $10^{-6}\%$  to 50% depending on the problem domain.

Sparse kernels are hard to attain high performance on modern processors. Unlike their counterpart in dense and regular applications, sparse applications have locally varying non-zero (NZ) patterns, leading to unpredictable control flows and unbalanced workloads which are detrimental to performance. In addition, sparse applications have irregular compute patterns that are inherently sequential, together with random and uncoalesced memory accesses. These issues can result in low occupancy as well as low resource utilization on modern processors.

On the other hand, there is a large number of different implementations and data structures for sparse problems. However, this is also a lack of understanding of the optimization techniques for sparse problems. It still remains an open question as to which algorithm or data structure best fits sparse data. One reason for this is due to the vast problem domains and the data characteristics (density, distribution) can vary drastically in different domains. Additionally, there are a large number of different methods to process and deal with sparse data, including different algorithms, parallelism schemes, etc.

In this dissertation, we start with the observation that the complicated sparse computations can be distilled into a primitive set of operators such as join, merge, and difference. To accelerate those operators on modern processors with data parallelism, we first propose a vectorization and code specialization approach that can eliminate the control divergences of these operators. Next, we explore the design space for vectorization on CPUs with various vector width, based on which we present the code generation algorithm that takes the data width and operations as input and generates various implementations. We then demonstrate the acceleration of the General Sparse Matrix-Matrix Multiplication (SpGEMM) on GPUs.

### 1.5 Thesis Overview

The goal of the thesis is to provide understandings and optimizations on the computation kernels of the emerging ML tasks including neural networks, social networks, and data analytics applications. The computation kernels lay the backbone of understanding the interplay between software optimizations and hardware architecture, which is a fundamental step towards building a portable and efficient end-to-end ML system.

In particular, this work is focusing on two sets of computational kernels: the dense computational kernels in convolutional neural networks, and the sparse kernels in data analysis tasks such as social networks. These kernels are fundamental to a majority of machine learning tasks and have received tremendous attention recently in both academia and industry.

The motivating ideas behind this thesis are: the optimization to achieve high performance is a codesign between combinatorial factors such as algorithm, implementation, platforms, etc. By correctly modeling the platform architectures, we are capable of deriving the "right" implementation that can achieve peak FLOPs on given platforms. Furthermore, different platforms can also exhibit drastic differences that are beyond parameter levels. Under such circumstances, we need to specialize in the implementations as well as algorithm choices to adapt to hardware attributes. Therefore, we demonstrate how an analytical model, together with code specialization, and learned dispatch strategies can enable the high performance for these computational kernels on modern hardware.

In Chapter 2, we demonstrate the optimization of the dense kernels in machine learning using convolution neural networks as an example. We propose a model-based analysis to provide a systematic understanding of how the software optimizations such as loop ordering, blocking, instruction scheduling, should be applied based on the hardware architectures. The work in this chapter was published in ICML 2018 [7].

In Chapter 3, we investigate the optimizations of sparse kernels. Sparse kernels present a different set of challenges compared to dense computations. We present the technique that can improve the data-parallelism of the irregular computations of sparse kernels, as well as investigating the effects of algorithm and data structure choices on the performances, using triangle counting application as an example. The work in this chapter was published in HPEC 2018 [17].

In Chapter 4, we investigate the vectorization and code specialization

approach for set intersections on CPUs. This chapter took a step forward from chapter 3 by focusing on intersections whose result sizes are much smaller than the input sizes—this property has been observed in many real-world intersection scenarios. In this chapter, we propose a specialized algorithm for the small-size intersection problem. We demonstrate the specialized algorithm has lower complexity than generalized intersection methods. Next we explore the vectorization accelerations for the specialized intersection algorithm on modern CPUs. We explore the design space for the fast vectorized intersection on CPUs with various vector widths, based on which we present the code generation algorithm that takes the data width and operations as input and generates various implementations. The work in this chapter was published in ICDE 2019 [18].

In Chapter 5, we investigate the optimization of Generalized-Sparse-Matrix-Matrix-Multiplication (SpGEMM) on GPU. We demonstrate how to break down the sparse matrix computation into a set of primitive operations of join and union. We further propose several optimizations for joinbased SpGEMM GPU implementations. We perform experimental and theoretic analysis on various implementations with both synthetic and real-world datasets. Finally we propose an online scheduling algorithm that is trained upon a neural network.

In Chapter 6, we present the concluding remarks and discuss possible directions for future work.

# Chapter 2

# Accelerating Dense Convolutions

| Contents |

|----------|

|----------|

| <b>2.1 Overview</b> 18                              |

|-----------------------------------------------------|

| <b>2.2 Introduction</b>                             |

| 2.3 Background                                      |

| 2.4 High Performance Direct Convolution 27          |

| 2.4.1 Strategy for Mapping Loops to Architecture 27 |

| 2.4.2 Parallelism                                   |

| 2.5 Convolution-Friendly Data Layout 34             |

| 2.5.1 Input/Output Layout                           |

| 2.5.2 Kernel Layout                                 |

| 2.5.3 Backward Compatibility                        |

| <b>2.6 Experiments</b>                              |

| 2.6.1 Experimental Setup                            |

| 2.7 | Chaj  | pter Summary         | 43 |

|-----|-------|----------------------|----|

|     | 2.6.3 | Parallel Performance | 40 |

|     | 2.6.2 | Performance          | 39 |

# 2.1 Overview

The computation of convolution layers in deep neural networks typically rely on high performance routines that trade space for time by using additional memory (either for packing purposes or required as part of the algorithm) to improve performance. The problems with such an approach are two-fold. First, these routines incur additional memory overhead which reduces the overall size of the network that can fit on embedded devices with limited memory capacity. Second, these high performance routines were not optimized for performing convolution, which means that the performance obtained is usually less than conventionally expected. In this chapter, we demonstrate that direct convolution, when implemented *correctly*, eliminates all memory overhead, and yields performance implementations of convolution layers on conventional and embedded CPU architectures. We also show that a high performance direct convolution exhibits better scaling performance, i.e. suffers less performance drop, when increasing the number of threads.

Figure 2.1: High performance direct convolution implementation achieves higher performance than a high performance matrix multiplication routine, whereas matrix-multiplication based convolution implementations suffers from packing overheads and is limited by the performance of the matrix multiplication routine

# 2.2 Introduction

Conventional wisdom suggests that computing convolution layers found in deep neural nets via direct convolution is not efficient. As such, many existing methods for computing convolution layers [19, 20] in deep neural networks are based on highly optimized routines (e.g. matrix-matrix multiplication) found in computational libraries such as the Basic Linear Algebra Subprograms (BLAS) [8]. In order to utilize the matrix-matrix multiplication routine, these frameworks reshape and selectively duplicate parts of the original input data (collectively known as packing); thereby incurring additional memory space for performance.

There are two problems with this approach: First, the additional work of reshaping and duplicating elements of the input data is a bandwidth-bounded operation that incurs an additional, and non-trivial time penalty on the overall system performance. Second, and more importantly, matrices arising from convolution layers often have dimensions that are dissimilar from matrices arising from traditional high performance computing (HPC) application. As such, the matrix-matrix multiplication routine typically does not achieve as good a performance on convolution matrices as compared to HPC matrices.

To illustrate these drawbacks of existing methods, consider the 4-thread performance attained on various convolution layers in AlexNet using an AMD Piledriver architecture shown in Figure 2.1. In this plot, we present performance of 1) a traditional matrix-multiply based convolution implementation linked to OpenBLAS [21] (blue) and 2) our proposed high performance direct convolution implementation (yellow). Performance of both implementations are normalized to the performance of only the matrix-matrix multiplication routine (dashed line). This dashed line is the performance attained by matrix-matrix multiplication *if packing is free*. Notice that the performance of OpenBLAS + Packing achieves less than 80% of the performance of matrix multiplication itself. This implies that the packing routine degrades the overall performance by more than 20%. In contrast, our custom direct convolution implementation yields performance that exceeds the expert-implemented matrix-matrix multiplication routine, even if packing was free. In addition, we attained the performance *without* any additional memory overhead.

It is timely to revisit how convolution layers are computed as machine learning tasks based on deep neural networks are increasingly being placed on edge devices [22, 23]. These devices are often limited in terms of compute capability and memory capacity [24, 25]. This means that existing methods that trade memory capacity for performance are no longer viable solutions for these devices. Improving performance and reducing memory overheads also bring about better energy efficiency [26]. While many work have focused on reducing the memory footprint of the convolution layer through the approximation [27], quantilization[28], or sparsification of the weights [29], few work tackle the additional memory requirements required in order to use high performance routines.

**Contributions.** In this chapter, we make the following contributions:

• High performance direct convolution. We show that a high perfor-

mance implementation of direct convolution can out-perform a expertimplemented matrix-matrix multiplication based convolution in terms of amount of actual performance, parallelism, and reduced memory overhead. This demonstrates that that direct convolution is a viable means of computing convolution layers.

• Data layouts for input/output feature maps and kernel weights. We proposed new data layouts for storing the input, output and kernel weights required for computing a convolution layer using our direct convolution algorithm. The space required for these new data layouts is identical to the existing data storage scheme for storing the input, output and kernel weights *prior* to any packing or duplication of elements.

# 2.3 Background

In this section, we highlight the inefficiency of computing convolution with existing methods used in many deep learning frameworks.

#### **Fast Fourier Transform-based Implementations**

Fast Fourier Transform (FFT)-based implementations [30, 31] of convolution were proposed as a means of reducing the number of floating point operations that are performed when computing convolution in the frequency domain. However, in order for the computation to proceed, the kernel weights have to be padded to the size of the input image, incurring significantly more memory than necessary, specially when the kernels themselves are small (e.g.  $3 \times 3$ ).

Alternative approaches have been proposed to subdivide the image into smaller blocks or tiles [32]. However, such approaches also require additional padding of the kernel weights to a convenient size (usually a power of two) in order to attain performance. Even padding the kernel weights to small multiples of the architecture register size (e.g. 8 or 16) will result in factors of 7 to 28 increase in memory requirement. This additional padding and transforming the kernel to the frequency domain can be minimized by performing the FFT on-the-fly as part of the computation of the convolution layer. This, however, incurs significant performance overhead, especially on embedded devices, as we will show in the performance section (Section 2.6).

#### Matrix Multiplication-based Implementations

Another common approach is to cast the inputs (both the image and kernel weights) into matrices and leverage the high performance matrix-matrix multiplication routine found in the Level 3 Basic Linear Algebra Subprogram (BLAS) [8] for computation. There are two major inefficiencies with this approach:

• Additional memory requirements. In order to cast the image into a matrix, a lowering operation is performed to cast the three dimensional image into a two dimensional matrix. Typically, this is performed via an operation conventionally called im2col that copies the  $W_i \times H_i \times C_i$  image into a  $(H_f \times W_f \times C_i) \times (H_o \times W_o)$  matrix which is then used as an input to the matrix-matrix multiplication call. During this lowering process, appropriate elements are also duplicated. The additional memory required grows quadratically with the problem size [20].

Cho and Brand [20] proposed an alternative lowering mechanism that is more memory efficient by reducing the amount of duplication required during the packing process. In their lowering routine, the memory footprint is reduced by an average factor of 3.2 times over im2col. This is achieved by eliminating the amount of duplication required at the expense of additional matrix-matrix multiplication calls. Nonetheless, this is still an additional memory requirement, and their computation still relies on a matrix-matrix multiplication that is often sub-optimal for matrices arising from convolution.

Figure 2.2: The 5 × 5 input image with 3 different channels (denoted with different colors) is convolved with two separate kernels to obtain a 3×3 output with two output channels. Packing is performed to turn three dimensional input images (left) into a two dimensional matrix (right) in order to utilize a high performance matrix multiplication routine. As  $C_o$  and/or ( $H_o \times W_o$ ) are often less than  $H_f \times W_f \times C_i$ , performance of standard matrix-matrix multiplication in many BLAS libraries are often sub-optimal.

• Sub-optimal matrix matrix multiplication. In most BLAS libraries (e.g. GotoBLAS [33], OpenBLAS [21], BLIS [34]), the matrix-matrix multiplication routine achieves the best performance when the inner dimensions, i.e. the dimension that is common between the two input matrices, of the input matrices are small compared to the overall dimensions of the output matrix. This particular set of matrix shapes is commonly found in scientific and engineering codes, for which these libraries are optimized. However, this particular set of shapes exercise only one out of six possible algorithms for matrix-matrix multiplication [33].

Recall that the im2col reshapes the input into a  $(H_f \times W_f \times C_i) \times (H_o \times W_o)$  matrix. This means that the inner dimensions of the input matrices are often the larger of two dimensions (See Figure 2.2). As such, the performance of matrix matrix multiplication on this particular set of input shapes is often significantly below the best achievable performance. It

has been shown that alternative algorithms for computing matrix multiplications should be pursued for shapes similar to that arising from convolution layers [35].

Another reason that matrix-matrix multiplication is inefficient for convolution layers is that parallelism in existing BLAS libraries are obtained by partitioning the rows and columns of the input matrices [36]. This partitioning of the matrices skews the matrix shapes even farther away from the shapes expected by the matrix-matrix multiplication routine. As such, the efficiency of the routine suffers as the number of threads increases.

# 2.4 High Performance Direct Convolution

A naive implementation of direct convolution (See Algorithm 1) is essentially six perfectly-nested loops around a multiply-and-accumulate computational statement that computes a single output element. Any permutation of the ordering of the loops will yield the correct result. However, in order to obtain a high performance implementation of direct convolution, it is essential that these loops and their order are appropriately mapped to the given architecture.

| Algorithm 1: Naive Convolution Algorithm                                                                |  |

|---------------------------------------------------------------------------------------------------------|--|

| <b>Input:</b> Input $\mathcal{I}$ , Kernel Weights $\mathcal{F}$ , stride $s$ ;                         |  |

| <b>Output:</b> Output $\mathcal{O}$                                                                     |  |

| for $i = 1$ to $C_i$ do                                                                                 |  |

| for $j = 1$ to $C_o$ do                                                                                 |  |

| for $k = 1$ to $W_o$ do                                                                                 |  |

| $\mathbf{for}\ \ell = 1\ \mathbf{to}\ H_o\ \mathbf{do}$                                                 |  |

| for $m = 1$ to $W_f$ do                                                                                 |  |

| for $n = 1$ to $H_f$ do                                                                                 |  |

| $\mathcal{O}_{j,k,\ell} {+}{=}  \mathcal{I}_{i,k 	imes s+m,\ell 	imes s+n} 	imes \mathcal{F}_{i,j,m,n}$ |  |

### 2.4.1 Strategy for Mapping Loops to Architecture

Our strategy for mapping the loops to a model architecture is similar to the analytical model for high performance matrix-matrix multiplication [37]. (1) We first introduce the model architecture used by high performance matrixmatrix multiplication. (2) Next, we identify loops that utilize the available computational units efficiently. (3) Finally, we identify the order of the outer loops in order to improve data reuse, which in turn will reduce the amount of performance-degrading stalls introduced into the computation. In this discussion, we use the index variables show in Algorithm 1  $(i, j, k, \ell, m, n)$  to differentiate between the loops.

#### Model architecture

We use the model architecture used the analytical model for high performance matrix-multiplication [37]. The model architecture is assumed to have the following features:

- Vector registers. We assume that our model architecture uses single instruction multiple data (SIMD) instruction sets. This means that each operation simultaneously performs its operation on  $N_{\text{vec}}$  scalar output elements. We also make the assumption that  $N_{\text{vec}}$  is a power of two. When  $N_{\text{vec}}$  is one, this implies that only scalar computations are available. In addition, a total of  $N_{\text{reg}}$  logical registers are addressable.

- FMA instructions. We assume the presence of  $N_{\rm fma}$  units that can compute fused multiply-add instructions (FMA). Each FMA instruction computes a multiplication and an addition. Each of these  $N_{\rm fma}$  units can compute one FMA instruction every cycle (i.e., the units can be fully pipelined), but each FMA instruction has a latency of  $L_{\rm fma}$  cycles. This means that  $L_{\rm fma}$  cycles must pass since the issuance of the FMA instruction before a subsequent dependent FMA instruction can be issued.

• Load/Store architecture. We assume that the architecture is a load-/store architecture where data has to be loaded into registers before operations can be performed on the loaded data. On architectures with instructions that compute directly from memory, we assume that those instructions are not used.

#### Loops to saturate computations

The maximum performance on our model architecture is attained when all  $N_{\rm fma}$  units are computing one FMA per cycle. However, because each FMA instruction has a latency of  $L_{\rm fma}$  cycles, this means that there must at least be  $L_{\rm fma}$  independent FMA instructions issued to each computational unit. As each FMA instruction can compute  $N_{\rm vec}$  output elements, this means that

$$\mathcal{E} \ge N_{\text{vec}} N_{\text{fma}} L_{\text{fma}},$$

(2.1)

where  $\mathcal{E}$  is the minimum number of independent output elements that has to be computed in each cycle in order to reach the maximum attainable performance.

Having determine that at least  $\mathcal{E}$  output elements must be computed in each cycle, the next step is to determine the arrangement of these output elements within the overall output of the convolution layer. Notice that the output has three dimensions  $(H_o \times W_o \times C_o)$  where  $H_o$  and  $W_o$  are primarily a function of the input sizes, while  $C_o$  is a design parameter of the convolution layer. Since  $\mathcal{E}$  must be a multiple of  $N_{vec}$ , i.e. a power-of-two, and  $C_o$  can be chosen (and is the case in practice) to be a power-of-two, the *j* loop is chosen as the inner-most loop.

As the minimum number  $\mathcal{E}$  is highly dependent on the number and capability of the FMA computation units, we want to ensure that there are sufficient output elements to completely saturate computation. As such, the k loop that iterates over the elements in the same row of the output image is chosen to be the loop around the j loop <sup>1</sup>.

#### Loops to optimize data reuse

The subsequent loops are ordered to bring data to the computational units as efficiently as possible.

Recall that the inner two loops (j and k) iterate over multiple output elements to ensure that sufficient independent FMA operations can be performed to avoid stalls in the computation units. As our model architecture is a load/store architecture, this means that these output elements are already in registers. Therefore, we want to bring in data that allows us to accumulate into these output elements.

Recall that to compute a single output element, all  $H_f \times W_f \times C_i$  weights are multiplied with the appropriate element from the input image and accumulated into the output element. This naturally means that the next three loops in sequence from the inner-most to outer-most are the i, n, m loops. This order of the loops is determined based on the observation that the input of most convolution layers is the output of another convolution layer. This means that

<sup>&</sup>lt;sup>1</sup>It should be noted that the choice of  $W_o$  over  $H_o$  is arbitrary as the analysis is identical.

| Algorithm 2: Reorder Convolution Algorithm                                                                   |

|--------------------------------------------------------------------------------------------------------------|

| <b>Input:</b> Input $\mathcal{I}$ , Kernel Weights $\mathcal{F}$ , stride $s$ ;                              |

| <b>Output:</b> Output $\mathcal{O}$                                                                          |

| for $\ell = 1$ to $H_o$ do                                                                                   |

| for $n = 1$ to $H_f$ do                                                                                      |

| for $m = 1$ to $W_f$ do                                                                                      |

| $\mathbf{for} \ i = 1 \ \mathbf{to} \ C_i \ \mathbf{do}$                                                     |

| for $k = 1$ to $W_o$ do                                                                                      |

| for $j = 1$ to $C_o$ do                                                                                      |

| $\mathcal{O}_{j,k,\ell} {+}{=}  \mathcal{I}_{i,k 	imes s + m, \ell 	imes s + n} 	imes \mathcal{F}_{i,j,m,n}$ |

it would be advisable if data from both the input and output are accessed in the same order. As such, we want to access the input elements in the channels (i) before rows (n), which gives us the i, n, m ordering of the loops.

Having decided on five of the original six loops, this means that *outer*most loop has to be the l loop. This loop traverses over the remaining through different rows of the output. The original loop order as shown in Algorithm 1 (i, j, k, l, m, n) is transformed to the (l, n, m, i, k, j) loop ordering as shown in Algorithm 2.

#### Blocking for the memory hierarchy

**Register Blocking.** The astute reader will recognize that we have conveniently ignored the fact that  $\mathcal{E}$ , the number of minimum output elements required to sustain peak performance, is upper bounded by the number of registers as described by the following inequality:

$$\mathcal{E} \le N_{\text{reg}} N_{\text{vec}}.$$

(2.2)

This upper bound imposed by the number of available registers means that at most  $N_{\text{reg}}N_{\text{vec}}$  elements can be kept in the registers. This means that instead of iterating over all  $C_o \times W_o$  elements, loop blocking/tiling [38] with block sizes of  $C_{o,b}^2$  and  $W_{o,b}$  has to be applied to the two inner-most loops to avoid register-spilling that will degrade performance.

Applying loop blocking to the original j and k loops decomposes a row from each of the output channel into smaller output images, each of which having a row width and output channel of  $W_{o,b}$ , and  $C_{o,b}$  respectively. Since loop blocking decomposes the overall convolution into smaller convolutions, the loop ordering previously described remains applicable. However, we now need to determine how to traverse over the smaller convolutions.

The final algorithm applying loop blocking is shown in Algorithm 3. The loops j' and k' iterate over the blocks in the channel and row dimensions of the output, respectively. We make the observation accessing input elements in the same row will require us to also access kernel weights in the same row. This suggest that the ordering of the loop should be similar to the loops traversing across the kernel weights. As such, the k' loop is nested between  $\ell$ and n loops. The j' loop is set to be the outermost loop since it is a parallel loop that facilitates parallelization.

**Cache Blocking.** On architecture with more levels in the memory hierarchy, i.e. architectures with caches, we can further partition the input dataset into smaller partitions such that they fit into the appropriate levels of

$<sup>{}^{2}</sup>C_{o,b}$  is chosen to be a multiple of the vector length  $N_{vec}$  so that SIMD instructions can be better used for computation.

the cache. Recall that the loops around jj and kk accumulates  $H_f \times W_f \times C_i$ intermediate results into the output stored in the register. Since  $H_f$  and  $W_f$ , i.e. the size of the kernel weights, are typically smaller than  $C_i$ , we choose to partition the *i* loop which iterates over  $C_i$  input channels for the next level in the memory hierarchy.

The final algorithm for high performance direct convolution is shown in Algorithm 3.

| Algorithm 3: Parallelized Direct Convolution Algorithm                          |

|---------------------------------------------------------------------------------|

| <b>Input:</b> Input $\mathcal{I}$ , Kernel Weights $\mathcal{F}$ , stride $s$ ; |

| <b>Output:</b> Output $\mathcal{O}$                                             |

| for $j' = 1$ to $C_o/C_{o,b}$ in Parallel do                                    |

| $\mathbf{for}i'=1\mathbf{to}C_i/C_{i,b}\;\mathbf{do}$                           |

| $\mathbf{for}\ell=1\mathbf{to}H_o\mathbf{do}$                                   |

| for $k' = 1$ to $W_o/W_{o,b}$ do                                                |

| for $n = 1$ to $H_f$ do                                                         |

| for $m = 1$ to $W_f$ do                                                         |

| for $ii = 1$ to $C_{i,b}$ do                                                    |

| for $kk = 1$ to $W_{o,b}$ do                                                    |

| for $jj = 1$ to $C_{o,b}$ do                                                    |

| $\mathcal{O}_{j'C_{o,b}+jj,k'W_{o,b}+kk,\ell}$ +=                               |

| $\mathcal{I}_{i'C_{i,b}+ii,sk'W_{o,b}+kk+m,\ell s+n}$ $	imes$                   |

| $\mathcal{F}_{i'C_{i,b}+ii,j'	imes C_{o,b}+jj,m,n}$                             |

## 2.4.2 Parallelism

In order to identify possible parallel algorithms, we first make the observation that all output elements can be computed in parallel. Since the output is a three dimensional object  $(H_o \times W_o \times C_o)$ , this means that parallelism can be extracted in at least three different dimensions. Our direct convolution implementation extracts parallelism in the output channel  $(C_o)$  dimension. Each thread is assigned a block of output elements to compute, where each block of output elements is of size  $H_o \times W_o \times C_o/p$ , where p is the number of threads used.

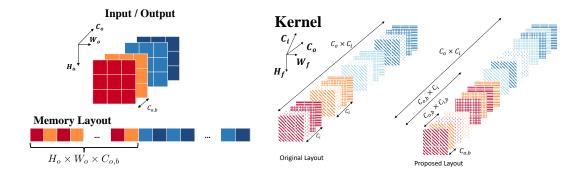

## 2.5 Convolution-Friendly Data Layout

We proposed new data layouts for the input and kernel data so that data is accessed in unit stride as much as possible. This improves data access and avoids costly stalls when accessing data from lower levels of the memory hierarchy. A key criteria in revising the layout is that the output and the input image should have the same data layout. This is because the input of most convolution layers is the output of another convolution layer. Keeping them in the same data layout will avoid costly data reshape between convolution layers. However, to ensure compatibility with original input images, we do not impose the proposed layout on the inputs to the first convolution layer.

## 2.5.1 Input/Output Layout

We want to access the output data in unit stride. Therefore, we determine the output data layout by considering how the elements are accessed using the loop ordering shown in Algorithm 3. Data accessed in the inner loops should be arranged closer together in memory than data accessed in the outer loops.

Five loops  $(j, k, \ell, kk, jj)$  iterate over the output data, which suggests

a five-dimensional data layout. However, this is sub-optimal if we were to use it for the input data. This is because  $W_f$  elements in an input row is required to compute one output element. With the five-dimensional layout, a row of the input is blocked into blocks of  $W_{o,b}$  elements. This means that output elements that require input elements from two separate  $W_{o,b}$  blocks will incur a large penalty as these input elements are separated over a large distance in memory. As such we do not layout the data according to the kk loop.

The proposed input/output layout is shown in Figure 2.3 (left). The output data is organized into sequential blocks of  $H_o \times W_o \times C_{o,b}$ , where in each block, elements are first laid out in the channel dimension, before being organized into a  $H_o \times W_o$  row-major-order matrix of pencils of length  $C_{o,b}$ .

#### 2.5.2 Kernel Layout

Similar to the input/output layout, we use the loop ordering to determine how to order the kernel weights into sequential memory. Notice that the  $\ell, k', kk$ loops in Algorithm 3 iterates over the height and width of the output in a single output channel. As all output elements in the same output channel share the same kernel weights, these loops provide no information as to how the kernel weights should be stored. As such, we only consider the remaining six loops.

The kernel layout proposed by the remaining six loops is shown in Figure 2.3 (right). The fastest dimension in the kernel layout is the blocked output channel  $(C_{o,b})$  dimension, and is dictated by the inner-most loop. The

Figure 2.3: Convolution-friendly layout for input/output (left) and kernel weights (right). The output data is organized into sequential blocks of  $H_o \times W_o \times C_{o,b}$ , where in each block, the fastest dimension is in the channel dimension, followed by the column and row dimension of the output. The kernel weights are organized into blocks of  $H_o \times W_o \times C_{o,b} \times C_{i,b}$ . The fastest dimension is the blocked output channel, followed by the blocked input channels, kernel width and height, input channels and then the output channels.

remaining dimensions from fastest to slowest are the blocked input channel  $(C_{i,b})$ , followed by the columns  $(W_f)$  and rows  $(H_f)$  of the kernel, the input channels  $(C_i/C_{i,b})$  and finally the output channels  $(C_o/C_{o,b})$ .

#### 2.5.3 Backward Compatibility

Given the successful deployment of convolution neural nets (CNN)in the field, the proposed change in data layout will mean that trained networks are unable to directly benefit from our proposed direct convolution implementation. However, in order for a trained network to use our proposed algorithm, there is only a one-time cost of rearranging the kernel weights into the proposed data layout. Other network layers such as skip layers [39], and activation layers are point-wise operations that should not require any significant change in the implementation. Nonetheless, reordering the loops used to compute these layers will likely yield better performance.

|               | Intel<br>i7-4770K  | AMD<br>FX(tm)-8350 | ARM<br>Cortex-A57  |

|---------------|--------------------|--------------------|--------------------|

| Arechitecture | Haswell            | Piledriver         | ARMv8              |

| Frequency     | $3.5 \mathrm{GHz}$ | $4 \mathrm{GHz}$   | $1.1 \mathrm{GHz}$ |

| Cores         | 4                  | 4                  | 2                  |

| $N_{vec}$     | 8                  | 8                  | 4                  |

Table 2.1: Details of specific architecture used

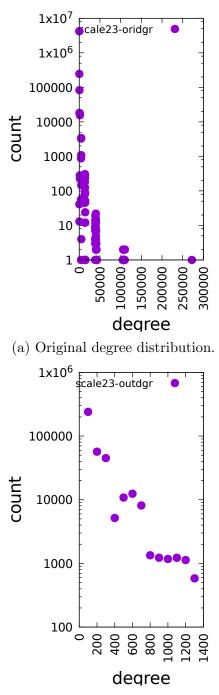

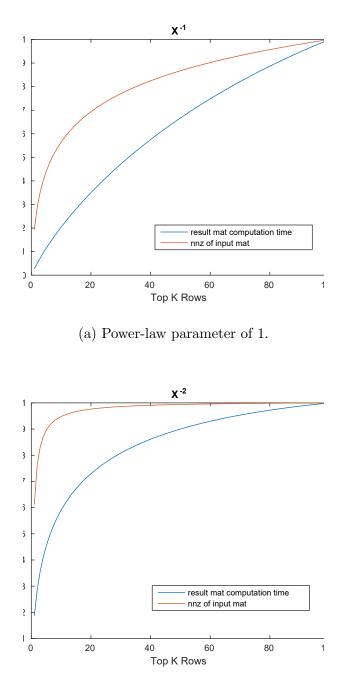

# 2.6 Experiments