## **Obfuscation and Security for Digital Integrated Circuits**

Submitted in partial fulfillment of the requirements for

the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Joseph Sweeney

B.S. Engineering Physics, Fordham University B.S. Electrical Engineering, Columbia University M.S. Electrical and Computer Engineering, Carnegie Mellon University

> Carnegie Mellon University Pittsburgh, PA

> > January 2021

© Joseph Sweeney, 2021 All rights reserved.

## Acknowledgements

Thanks to my advisor, Larry Pileggi, who has guided me in my research, given me countless opportunities, and from whom I've learned a lot.

To my committee members, Shawn Blanton, Yiorgos Makris, Marijn Heule, and Rob Rutenbar, thank you for mentorship and direction in developing this thesis.

To my collaborators and coworkers Ken Mai, Mohammad Zackriya, Samuel Pagliarini, Oguz Atli, Ruben Purdy, Danielle Duvalsaint, Xiang Lin and Deepali Garg, thanks for enabling so much of this work.

I am grateful for the funding support from the Defense Advanced Research Projects Agency under contract FA8750-17-1-0059 "Obfuscated Manufacturing for GPS (OMG)" and Honeywell Federal Manufacturing & Technologies, LLC under contract A023646.

To my friends Amrit Pandey, Onur Kibar, Prashanth Mohan, Mimi Sweeney, Antonis Manousis, Dimitrios Stamoulis and Meric Isgenc, you have truly made Pittsburgh home.

Thanks to Natalia, who supports me more than I deserve.

Finally, thanks to my family to whom I owe everything.

## Abstract

Globalization of IC manufacturing has led to increased security concerns, notably IP theft. A promising countermeasure is logic locking that adds programmable elements to a design, obfuscating the true functionality during manufacturing. Generally, logic locking techniques aim to provide IP security while avoiding large overheads. Towards this end, this dissertation makes several contributions.

First, a security analysis of existing locking techniques is presented, exposing several vulnerabilities. One class of techniques is analyzed using sensitivity, a property of Boolean functions. The analysis reveals the modified portions of a circuit with high probability, leading to deobfuscation. Another class of locking methods is used to demonstrate two modeling techniques, relaxed models and symmetry breaking, that can dramatically reduce attack times.

These vulnerabilities inform the development of latch-based logic locking, a novel obfuscation method that resists known attacks while maintaining low overheads. This balance is achieved by locking a design's clock tree, manipulating the functionality while avoiding timing-critical logic. To validate the technique, a set of common industrial designs has been locked and brought through the full manufacturing process. To demonstrate resistance to deobfuscation, the locking scheme is evaluated against existing and newly developed attack methods.

Finally, two metrics are established to better quantify the security of a given locking technique under common attack scenarios. These metrics are efficiently estimated using approximate model counting techniques. Importantly, they provide a means of analyzing the overhead-security trade-off of locking techniques, an essential aspect of integrating locking schemes into real systems.

# Contents

| C               | onten | ts      |                                                 |   |  |     | v   |

|-----------------|-------|---------|-------------------------------------------------|---|--|-----|-----|

| List of Figures |       |         | viii                                            |   |  |     |     |

| Li              | st of | Tables  |                                                 |   |  |     | xii |

| 1               | Intr  | oductio | on                                              |   |  |     | 1   |

|                 | 1.1   | Logic   | Locking for Protection of Intellectual Property | • |  |     | 1   |

|                 | 1.2   | Thesis  | s Contributions                                 | • |  |     | 2   |

| 2               | Bac   | kgroun  | ıd                                              |   |  |     | 4   |

|                 | 2.1   | Digita  | Il Integrated Circuits                          | • |  |     | 4   |

|                 |       | 2.1.1   | Structure, Operation, and Testing               | • |  |     | 4   |

|                 |       | 2.1.2   | Manufacturing Process Vulnerabilities           | • |  |     | 6   |

|                 | 2.2   | Logic   | Locking                                         | • |  | ••• | 7   |

|                 |       | 2.2.1   | Attack Models                                   | • |  |     | 8   |

|                 |       | 2.2.2   | Brief Taxonomy                                  | • |  |     | 10  |

|                 |       | 2.2.3   | Related Techniques                              | • |  |     | 12  |

|                 | 2.3   | Attacl  | ks on Logic Locking                             | • |  |     | 13  |

|                 |       | 2.3.1   | Netlist-Based Attacks                           | • |  |     | 13  |

|                 |       | 2.3.2   | Brute Force and Sensitization Attacks           | • |  |     | 14  |

|                 |       | 2.3.3   | Miter-Based Attacks                             | • |  |     | 15  |

#### CONTENTS

| 3 | Sec | urity of | f Existing Locking Schemes                  | 20 |

|---|-----|----------|---------------------------------------------|----|

|   | 3.1 | Sensit   | ivity Analysis of Strip-Functionality Locks | 20 |

|   |     | 3.1.1    | Strip-Functionality Locking                 | 21 |

|   |     | 3.1.2    | Boolean Sensitivity Attack                  | 23 |

|   |     | 3.1.3    | Resistant Locking Scheme                    | 28 |

|   |     | 3.1.4    | Attack Results                              | 29 |

|   | 3.2 | Mode     | ling Techniques for Locked Circuits         | 32 |

|   |     | 3.2.1    | Full-Lock                                   | 33 |

|   |     | 3.2.2    | Relaxed Models                              | 35 |

|   |     | 3.2.3    | Symmetry Breaking                           | 40 |

|   |     | 3.2.4    | Resistant Locking Scheme                    | 42 |

|   | 3.3 | Discu    | ssion                                       | 46 |

|   |     | 3.3.1    | Attack Insights                             | 46 |

|   |     | 3.3.2    | Shortcomings of Proposed Fixes              | 47 |

| 4 | Key | ed Seq   | uential Elements for Low-Overhead Locking   | 49 |

|   |     | 4.0.1    | Latch-Based Design and Retiming             | 50 |

|   | 4.1 | Latch    | -Based Logic Locking                        | 50 |

|   |     | 4.1.1    | Programmable Path Delay                     | 51 |

|   |     | 4.1.2    | Programmable Logic                          | 53 |

|   |     | 4.1.3    | Insertion Flow                              | 54 |

|   |     | 4.1.4    | Design for Testability                      | 57 |

|   | 4.2 | Attacl   | king Latch-Based Logic Locking              | 58 |

|   |     | 4.2.1    | Netlist-Based Attacks                       | 59 |

|   |     | 4.2.2    | Oracle-Based Attacks                        | 62 |

|   | 4.3 | Overh    | nead Analysis                               | 74 |

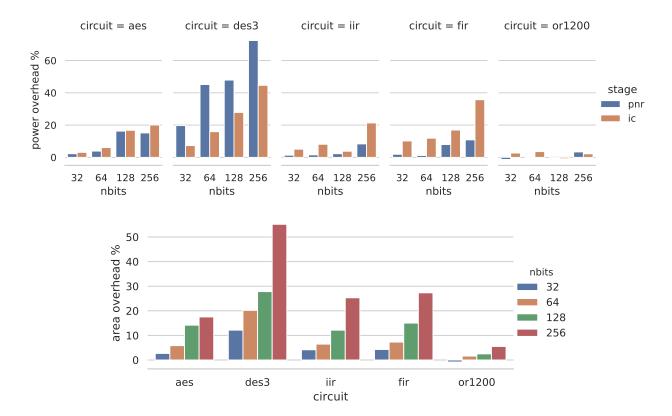

|   |     | 4.3.1    | Power, Performance, Area Overhead           | 75 |

|   |     | 4.3.2    | Testing Overhead                            |    |

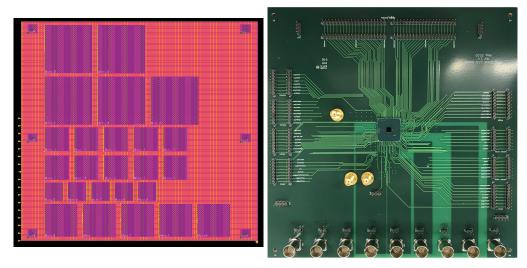

|    |       | 4.3.3   | Tapeout                                           | 78  |

|----|-------|---------|---------------------------------------------------|-----|

|    | 4.4   | Discus  | ssion                                             | 81  |

| 5  | Qua   | ntifyin | ig the Efficacy of Locking Methods                | 84  |

|    | 5.1   | Lockin  | ng Metrics                                        | 84  |

|    |       | 5.1.1   | Existing Security Metrics                         | 84  |

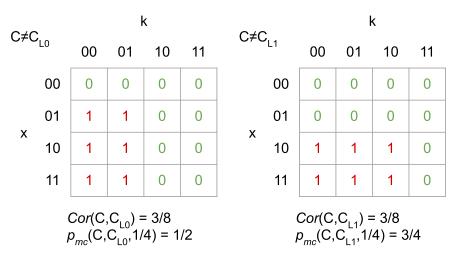

|    |       | 5.1.2   | Key Corruption                                    | 86  |

|    |       | 5.1.3   | Minimum Corruption                                | 86  |

|    |       | 5.1.4   | Estimating Metrics                                | 87  |

|    | 5.2   | Applie  | cation of Metrics                                 | 88  |

|    |       | 5.2.1   | Minimum Corruption under Netlist Attack Model     | 89  |

|    |       | 5.2.2   | Incremental Key Corruption of Oracle Attack Model | 91  |

|    |       | 5.2.3   | Overhead-Security Trade-Offs                      | 93  |

|    | 5.3   | Discus  | ssion                                             | 95  |

| 6  | Con   | clusior | n and Future Work                                 | 97  |

|    | 6.1   | Impro   | ving and Impeding Oracle-Based Attacks            | 97  |

|    | 6.2   | Securi  | ty-Aware Logic Synthesis                          | 98  |

|    | 6.3   | Concl   | usion                                             | 102 |

| Bi | bliog | raphy   |                                                   | 104 |

| A  | Sup   | porting | g Algorithms                                      | 113 |

|    | A.1   | Acycli  | c Key Constraints                                 | 113 |

|    | A.2   | Logic-  | Enhanced Banyan Locking Insertion                 | 114 |

# **List of Figures**

| 2.1 | Typical digital IC structure                                                                       | 5  |

|-----|----------------------------------------------------------------------------------------------------|----|

| 2.2 | High-level view of IC manufacturing process                                                        | 6  |

| 2.3 | XOR logic locking example                                                                          | 7  |

| 2.4 | Miter-based attack steps: (a) Miter circuit construction, (b) Unlocked (oracle)                    |    |

|     | circuit produces correct IO functionality (c) Addition of learned IO constraint                    |    |

|     | to miter circuit                                                                                   | 16 |

| 2.5 | Miter-based model checker attack steps: (a) Miter circuit unrolling, (b) Differ-                   |    |

|     | entiating sequence constraint.                                                                     | 19 |

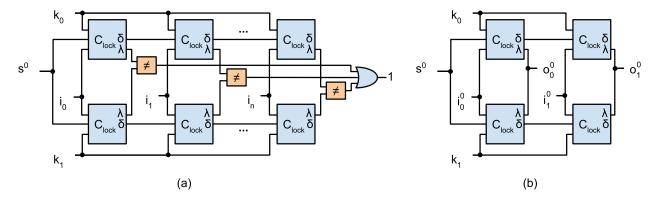

| 3.1 | Underlying structure of strip-functionality locking                                                | 21 |

| 3.2 | Truth table of circuit locked with TTLock                                                          | 22 |

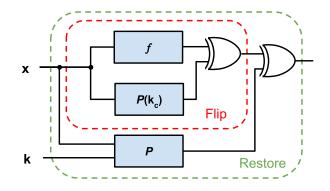

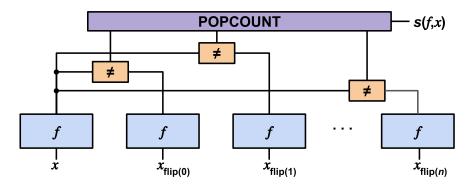

| 3.3 | Circuit that determines sensitivity where $s(f, x)$ is the sensitivity of $f$ at a                 |    |

|     | given input <i>x</i> and $x_{\text{flip}(i)}$ represents <i>x</i> with the <i>i</i> th bit flipped | 24 |

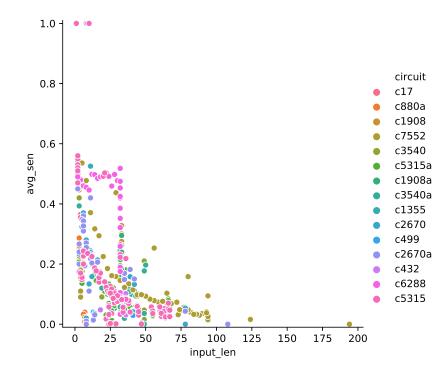

| 3.4 | Average sensitivity, $\bar{s}(f)$ , versus input width of benchmark circuits from 50               |    |

|     | samples                                                                                            | 25 |

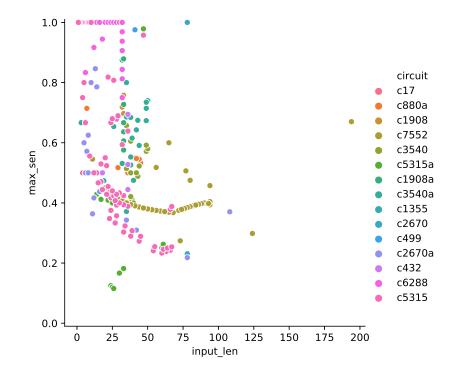

| 3.5 | Sensitivity, $s(f)$ , versus input width of benchmark circuits                                     | 26 |

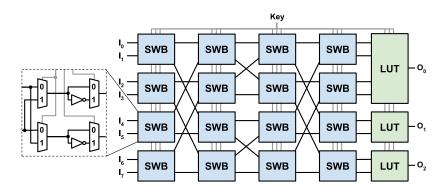

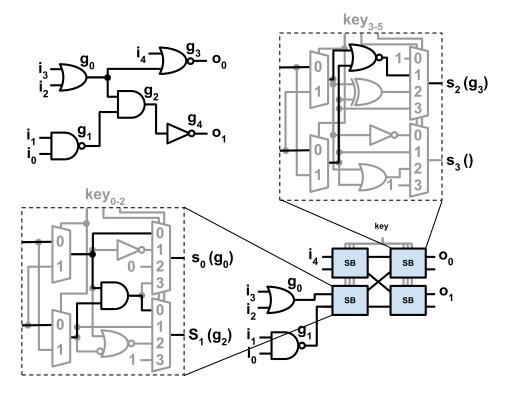

| 3.6 | Full-Lock diagram. Each LUT replaces a gate from the original circuit; the                         |    |

|     | switch boxes permute and invert their input signals                                                | 34 |

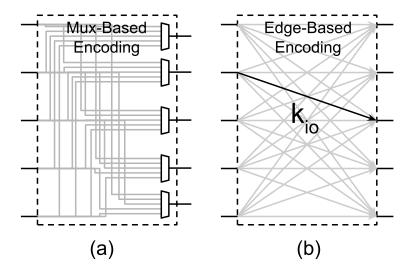

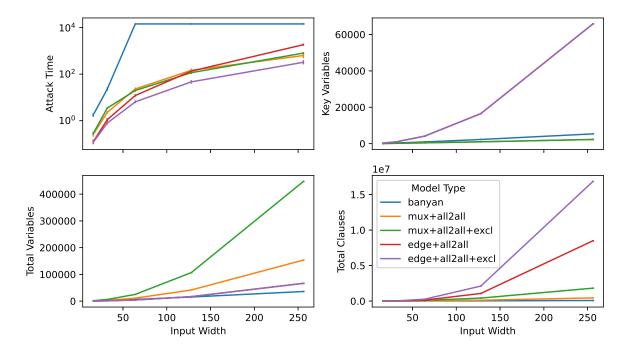

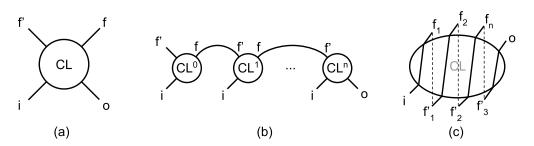

| 3.7 | Relaxed models for Banyan network                                                                  | 37 |

| 3.8 | (a) MUX-based and (b) edge-based encoding schemes for the all-to-all model .                       | 37 |

|     |                                                                                                    |    |

| 3.9  | Comparison of encoding schemes for standalone Banyan network, n=10, time-        |    |

|------|----------------------------------------------------------------------------------|----|

|      | out=4 hours                                                                      | 39 |

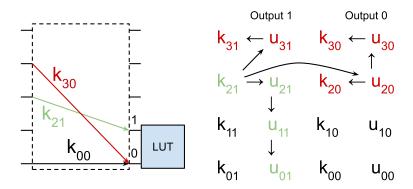

| 3.10 | Example of propagation of ordering constraints for a 2-input LUT                 | 42 |

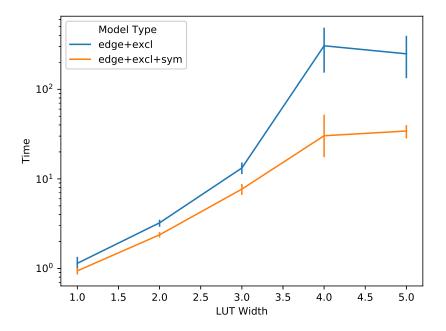

| 3.11 | Comparison of attack time at network input width of 32 between encodings         |    |

|      | with and without LUT symmetry breaking, n=10                                     | 43 |

| 3.12 | Diagram of circuit mapped to logic-enhanced Banyan network. The original         |    |

|      | circuit is shown top-left, the locked version bottom-right. The correct switch   |    |

|      | box function is highlighted in black, the decoy logic in gray                    | 44 |

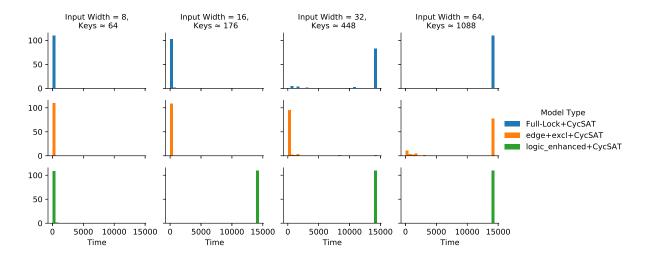

| 3.13 | miter-based attack time for ISCAS 85 circuits locked with Full-Lock and logic-   |    |

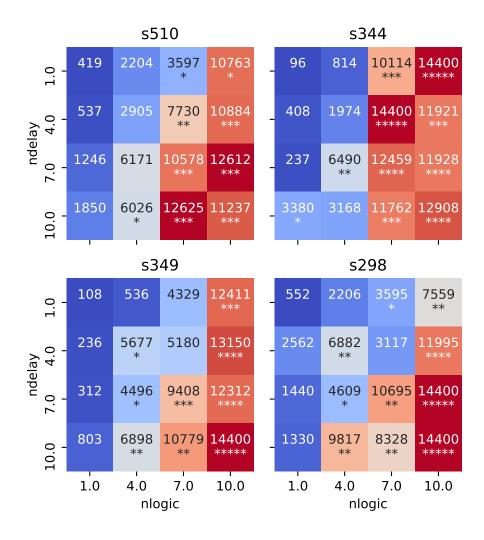

|      | enhanced Banyan locking schemes                                                  | 45 |

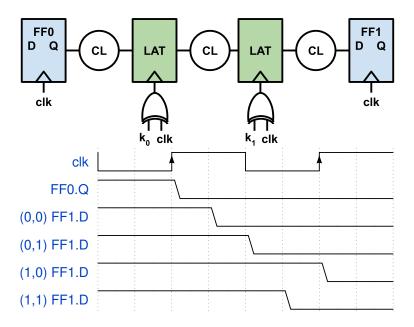

| 4.1  | Diagram and functional waveforms of logic locked with programmable path          |    |

|      | delay via latch phase modulation.                                                | 51 |

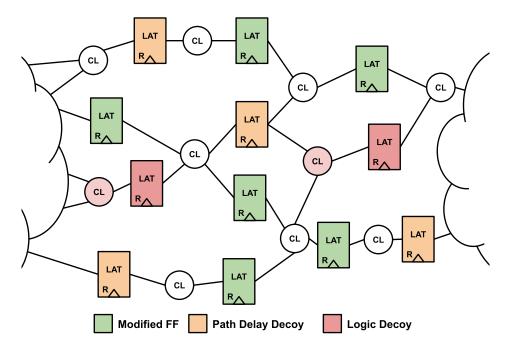

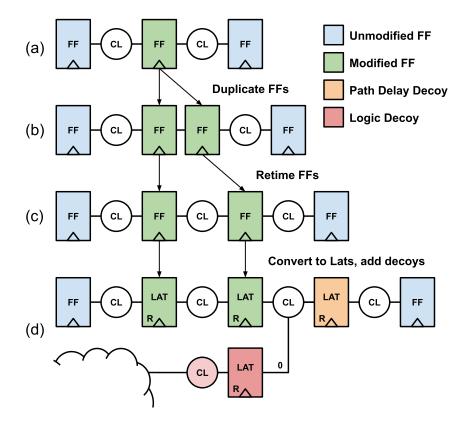

| 4.2  | Conceptual view of latch-based logic locking. A set of interconnected flip-      |    |

|      | flops is converted to programmable latches with added decoy latches and          |    |

|      | logic. Each latch can operate on either clock phase, hold clear, or output       |    |

|      | constant logic 0                                                                 | 52 |

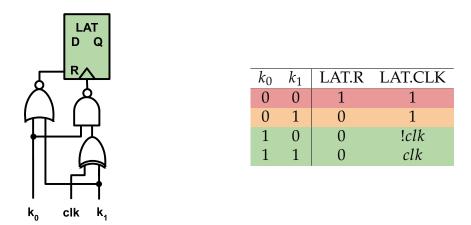

| 4.3  | Diagram and truth table of latch clock and reset control signals. Control        |    |

|      | circuitry that determines the latch function is connected to the clock and reset |    |

|      | pins. The truth table's row colors correspond to the associated latch type       | 54 |

| 4.4  | Flip-flop to latch conversion and decoy addition. A flip-flop is duplicated,     |    |

|      | retimed, and converted to latches. Two types of decoy latches can be added       |    |

|      | to the paths in the fan-in and fan-out cones of the latches. This example shows  |    |

|      | a single flip-flop, however in practice an interconnected group is converted     | 55 |

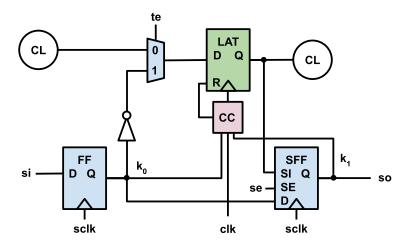

| 4.5  | Preliminary DFT infrastructure. CC represents clock and reset control cir-       |    |

|      | cuitry from Table 4.1.2.                                                         | 57 |

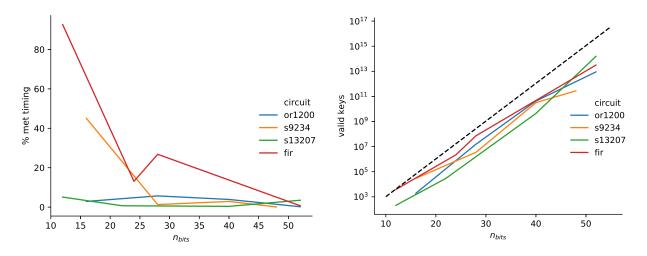

| 4.6  | Enumeration of keys that satisfy timing constraints, $n = 1000$                  | 59 |

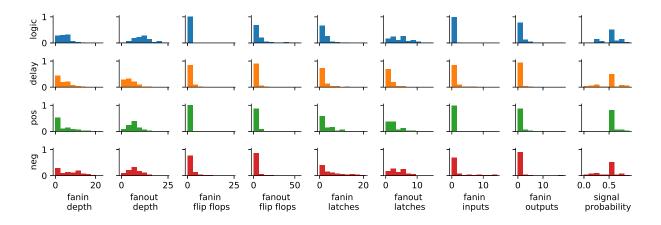

| 4.7  | Histograms, separated by latch type, for structural metrics. Plots are gener-       |    |

|------|-------------------------------------------------------------------------------------|----|

|      | ated from 60 locked circuits with varying amounts of LBLL bits                      | 61 |

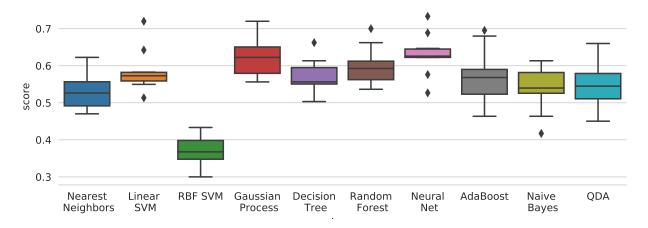

| 4.8  | Cross-validation scores on classifiers trained on the structural metric dataset.    | 62 |

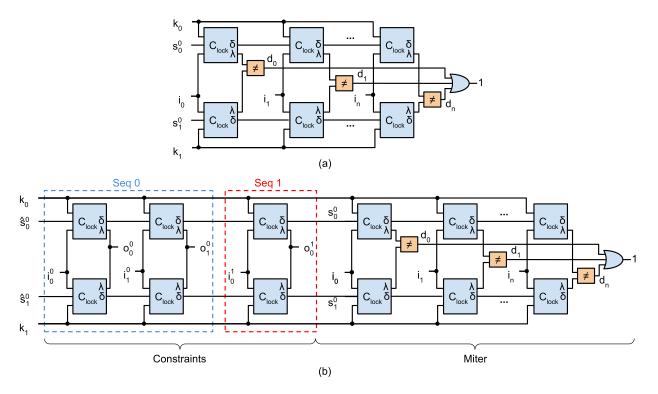

| 4.9  | (a) Miter circuit used in our modified model checker-based attack. The free         |    |

|      | variables of the system are the two key inputs, the initial state of all sequential |    |

|      | elements, and the inputs at every unrolled cycle. The circuit is unrolled by        |    |

|      | connecting the input of each state element from a cycle to the output of the        |    |

|      | same state element of the next cycle. (b) Addition of a learned IO constraint       |    |

|      | to the miter circuit. This limits the possible key and initial state pairs          | 64 |

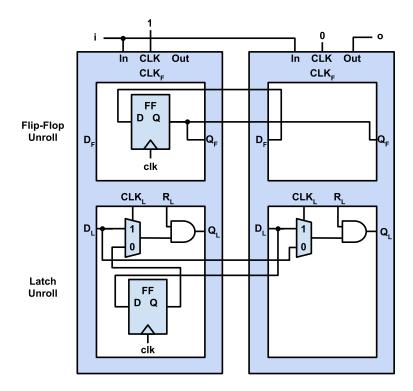

| 4.10 | Conversion of latch-based circuit to flip-flop counterpart, enabling use in         |    |

|      | generic model checkers.                                                             | 67 |

| 4.11 | (a) Cyclic circuit with cut feedback paths. (b) Acyclic, unrolled version of the    |    |

|      | circuit. (c) Visualization of longest possible path through unrolled circuit's      |    |

|      | feedback                                                                            | 69 |

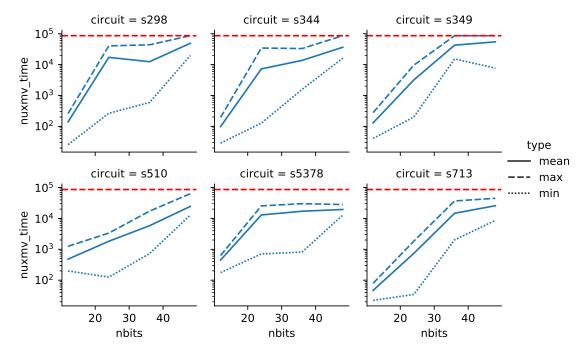

| 4.12 | Model checker attack results; timeout of 24 hours indicated by red line             | 70 |

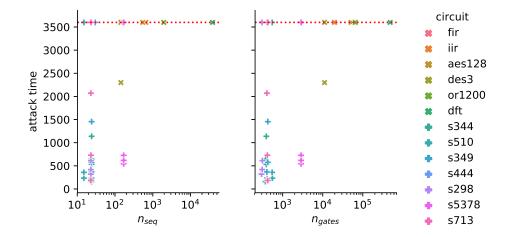

| 4.13 | Model checker attack versus circuit size                                            | 71 |

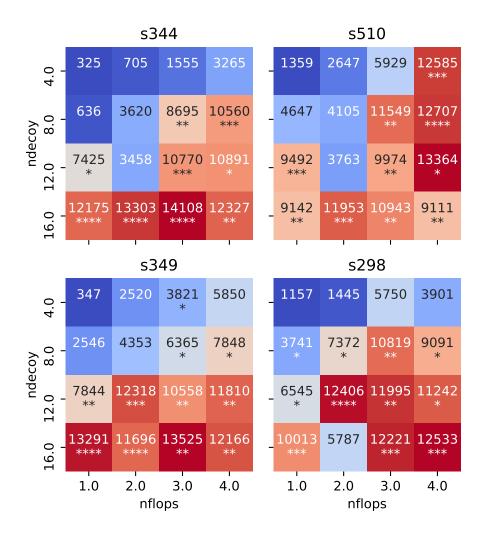

| 4.14 | Comparison of attack time with various ratios of original flip-flops converted      |    |

|      | versus decoys add. Added decoys are evenly split between delay and logic            |    |

|      | types                                                                               | 72 |

| 4.15 | Comparison of attack time with various ratios of logic versus delay decoys          | 73 |

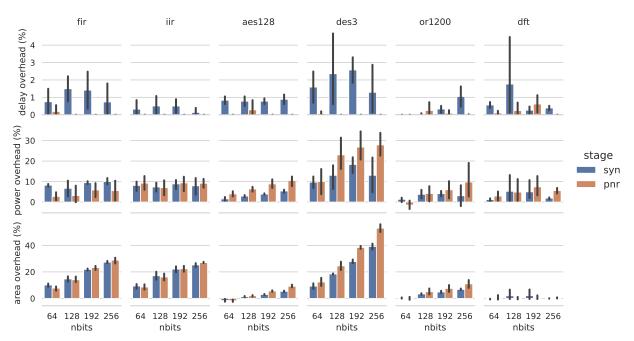

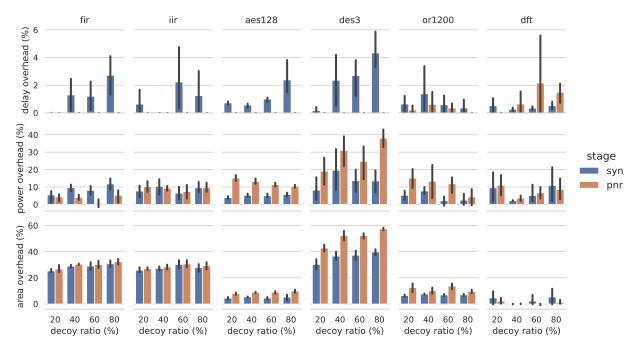

| 4.16 | Latch-based logic locking delay, power, and area overheads vs. number of            |    |

|      | key bits normalized to the original design.                                         | 75 |

| 4.17 | Latch-based logic locking delay, power, and area overheads vs. decoy ratio          |    |

|      | normalized to the original design, nbits=256                                        | 77 |

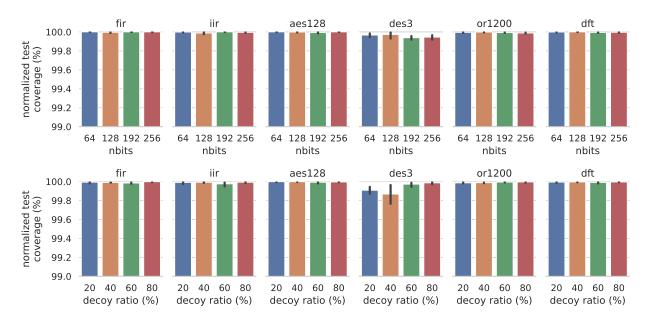

| 4.18 | Normalized SSL test coverage for circuits locked with latch-based logic locking     | 78 |

| 4.19 | GDS of test IC and PCB with IC mounted.                                             | 79 |

| 4.20 | Power and area overheads for the taped-out circuits.                                | 80 |

LIST OF FIGURES

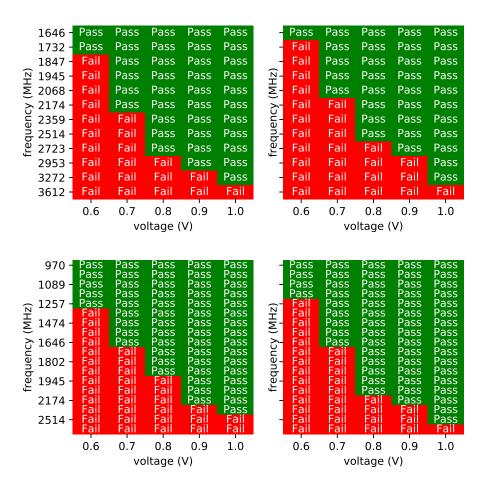

| 4.21 | Schmoo plots for AES (top left), AES with 64 bits LBLL (top right), IIR (bottom         |

|------|-----------------------------------------------------------------------------------------|

|      | left), IIR with 256 bits LBLL (bottom right)                                            |

| 5.1  | Miter truth tables and corresponding locking metrics for two locked circuits 85         |

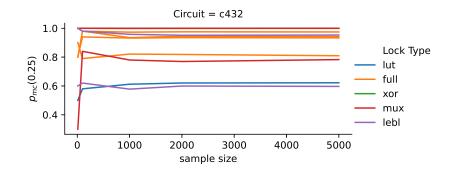

| 5.2  | Approximate $p_{mc}$ of benchmark versus #(keysamples)                                  |

| 5.3  | Approximate $p_{mc}$ of benchmark circuits locked with selected techniques. $w \approx$ |

|      | 128 and $#(keysamples) = 1000 \dots 90$                                                 |

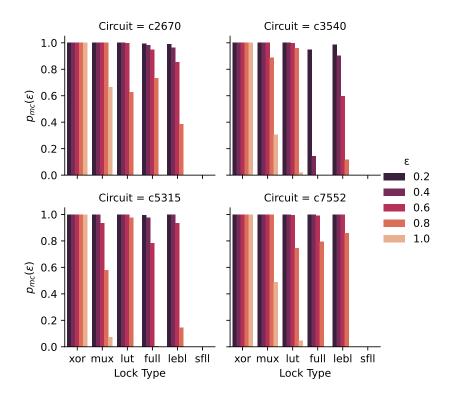

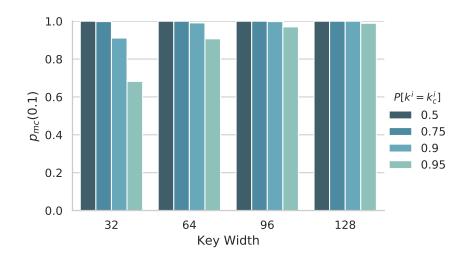

| 5.4  | Approximate $p_{mc}$ of c3540 locked with XOR-locking, sweeping key width $w$           |

|      | and $P[k^i = k_c^i]$ with #(keysamples) = 1000                                          |

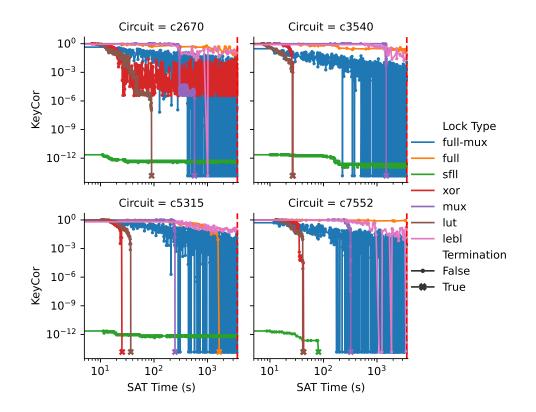

| 5.5  | Key corruption for incremental keys returned from miter-based attack, $w \approx$       |

|      | 448. The attacks are run with a timeout of 1 hour, indicated by the dashed              |

|      | red line. The zero value of key corruption is mapped to $10^{-14}$                      |

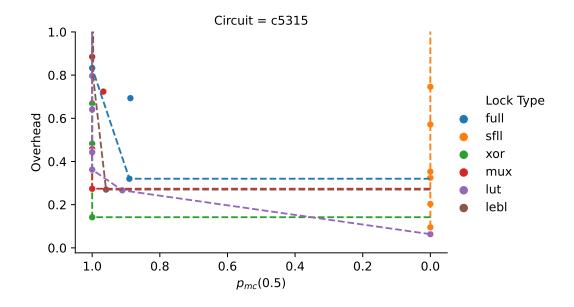

| 5.6  | Overhead vs. $p_{mc}$ Pareto fronts for selected locking techniques                     |

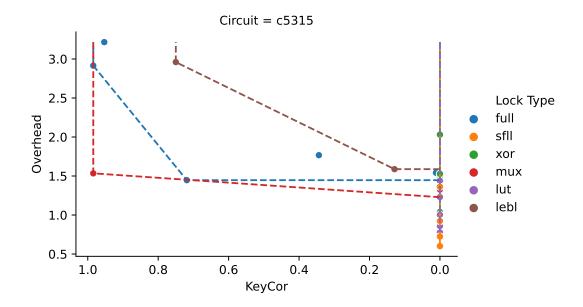

| 5.7  | Overhead vs. key corruption Pareto fronts for selected locking techniques.              |

|      | The zero value of key corruption is mapped to $10^{-19}$                                |

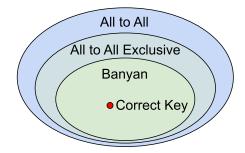

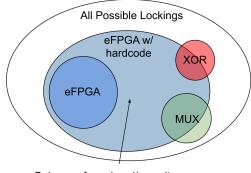

| 6.1  | Space of possible logic lockings                                                        |

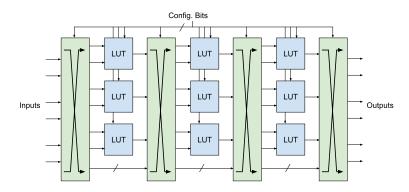

| 6.2  | Example programmable fabric construction                                                |

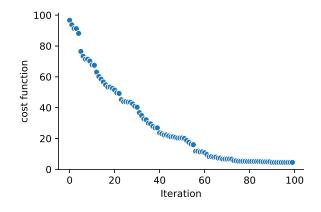

| 6.3  | Initial optimization results                                                            |

# List of Tables

| 3.1 | Sensitivity attack results for author-provided circuits using Cadence JasperGold                   | 30 |

|-----|----------------------------------------------------------------------------------------------------|----|

| 3.2 | Sensitivity attack results for generated circuits using Cadence JasperGold. For                    |    |

|     | SFLL-HD, HD = $N_{\text{bits}}/8$ and for SFLL-Flex, $N_{\text{patterns}} = N_{\text{bits}}/8$     | 31 |

| 3.3 | Sensitivity attack results for generated circuits using the SAT solver CaDiCaL.                    |    |

|     | For SFLL-HD, HD = $N_{\text{bits}}/8$ and for SFLL-Flex, $N_{\text{patterns}} = N_{\text{bits}}/8$ | 31 |

| 3.4 | 2-Input LUT symmetries under permuted inputs.                                                      | 41 |

| 4.1 | Characteristics of each considered benchmark circuit                                               | 75 |

# List of Algorithms

| 1 | Miter-Based Attack                                      | 18 |

|---|---------------------------------------------------------|----|

| 2 | Sensitivity-Based Attack                                | 27 |

| 3 | Sensitivity Attack Resistant TTLock                     | 29 |

| 4 | Logic decoy latch insertion                             | 56 |

| 5 | Delay decoy latch insertion                             | 56 |

| 6 | Model Checker-Based Attack with Non-Deterministic Reset | 66 |

# Chapter 1

# Introduction

### **1.1 Logic Locking for Protection of Intellectual Property**

The downscaling of integrated circuits (ICs) has enabled computing that underlies many essential technologies. However, due to prohibitively high research and development costs, only a few foundries are manufacturing ICs in most scaled technologies. Consequently, many IC companies tend to operate fabless, relying on third-party foundries to manufacture their designs. Once a circuit is sent for fabrication, the foundry gains full visibility of the design with minimal effort, allowing theft of intellectual property (IP). This threat undermines the significant cost associated with developing digital circuits and is a growing concern in the IC industry.

To combat IP theft, a variety of logic locking techniques have been developed. Generally, these techniques add programmable elements to the logic of an IC. When programmed incorrectly, the elements disrupt the circuit functionality. The key, which correctly programs the elements, is set post-manufacture, so the correct design is never revealed to the untrusted entity. These techniques seek to provide maximal security while maintaining low overhead in the circuit's area, power, delay, and testability.

Unfortunately, logic locking is far from realizing this goal. Corresponding with logic locking schemes, attacks have been developed that can reveal the circuit's correct key

under various attack conditions. To resist such attacks, lock designers have sacrificed greater overheads. In doing so, many schemes push the cost of locking a circuit to untenable levels. Furthermore, this cost increase is justified with notions of security that are tightly coupled to the execution time of specific attacks. In many cases, straightforward modifications to attacks lead to deobfuscation.

## **1.2** Thesis Contributions

This thesis addresses several of the preceding issues in logic locking. First, a security analysis of existing logic locking techniques is presented, exposing several weaknesses. Specifically, a new analysis method reveals locked portions of the design allowing for removal of locking circuitry and lock modeling techniques allow for significant speedups in attack time. The underlying causes of these vulnerabilities are identified, and fixes are proposed for each broken lock method. Although the security is improved, these fixed locking schemes still do not provide a satisfying security-overhead tradeoff.

This analysis informs the development of a new locking scheme, latch-based logic locking. This technique aims to provide low overhead security by exploring a new dimension in which to obfuscate a circuit. Whereas previous locks typically just manipulate a design's combinational logic, latch-based logic locking additionally keys a design's clock tree. This enables large amounts of interdependent keys to be inserted without the overheads associated with other techniques. The technique's low overhead is validated by manufacturing locked versions of several industry-standard circuits. Additionally, the security is comprehensively analyzed against existing as well as newly developed attack methods.

Finally, to enable better quantification of the security of given locking techniques, two metrics are proposed. These metrics, key corruption and minimum corruption, correspond to common attack models rather than specific attacks, enabling a designer to better discern the efficacy of various lock types. A flow for approximating these metrics on generic locked circuits is developed and evaluated several on locking techniques. We conclude with a discussion how the development of these and other metrics allows for automated logic locking schemes, reducing reliance on circuit designers for lock insertion and potentially providing substantially improved security-overhead trade-offs.

The remainder of the thesis is organized as follows:

- Chapter 2 elaborates on logic locking, providing an overview of relevant background knowledge, existing locking schemes, and attack methods.

- Chapter 3 describes new attack methods that deobfuscate locks from two classes locking methods.

- Chapter 4 introduces latch-based logic locking, a novel approach to adding programmable logic that maintains low overhead while resisting existing attacks.

- Chapter 5 proposes two new metrics that more accurately capture the security of locking techniques.

- Chapter 6 concludes with a discussion of the insights produced in this work and a promising new direction for logic locking research.

# Chapter 2

# Background

### 2.1 Digital Integrated Circuits

#### 2.1.1 Structure, Operation, and Testing

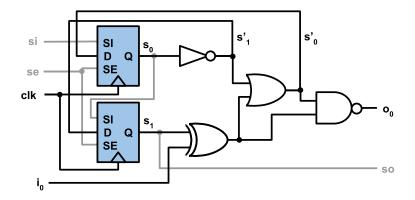

Due to their low cost, noise tolerance, and high speed, digital integrated circuits are used in the majority of computing platforms. These circuits perform computations on Boolean-valued signals, {0,1}. Generally, the circuits consist of sequential logic made from interconnected logic gates and state elements. Individually, the logic gates implement simple functions that are composed into more complex functions. These functions are referred to as a circuit's combinational logic. The state elements, also referred to as sequential elements, function as memory, storing values while the combinational logic is evaluated. Fig. 2.1 shows an example circuit with the state elements and logic gates colored blue and white, respectively.

To conduct the desired computation, the circuit moves through a set of state values based on the logic gate structure and inputs to the system, producing the desired sequence on its outputs. The evaluation of the circuit is dictated by a periodic clock signal. Each clock period, the logic gates compute the circuit's current output values and the next values of the state elements based on the current state and input values.

Figure 2.1: Typical digital IC structure

More formally, the functionality of the digital circuit can be specified as a finite state machine (FSM) using the Mealy model [1]. The model consists of a set of variables, functions, and initial states that describe how the circuit operates. We respectively denote the input, output, state and next-state variables as  $i \in \{1,0\}^n$ ,  $o \in \{1,0\}^m$ ,  $s \in \{1,0\}^l$ , and  $s' \in \{1,0\}^l$ . These variables are labeled in Fig. 2.1, where  $s_n$  is the *n*th bit of *s*. The output and next-state values are determined by an output function,  $\lambda$ , and state-transition function,  $\delta$ . Every clock period, the variables are updated as s := s', subsequently  $s' := \delta(s, i)$  and  $o := \lambda(s, i)$ . We denote the circuit's initial states as  $S^0 \subseteq \{1,0\}^l$ .

To aid in testing, digital circuits typically use a scan-chain, colored gray in Fig. 2.1. The scan-chain is formed by a serial connection between the circuit's state elements, the output of each sequential element feeds into the scan-in port, si, of the next. During *test* mode, the scan-chain is enabled (se = 1) causing the sequential elements take in data from their si port, rather than the d port used in normal operation. This enables arbitrary reading and writing of a digital circuit's state, significantly reducing the cost of exercising the circuit's logic during testing. Scan-chains allow the combinational logic of the circuit to be considered separately from the state elements, significantly improving the performance of automatic test pattern generation (ATPG) tools. For convenience, we refer to the combinational logic as C, where variables y = (s', o) and x = (s, i) are updated as y := C(x). Note that in Fig. 2.1  $x = (s_1, s_0, i_0)$  and  $y = (s'_1, s'_0, o_0)$ .

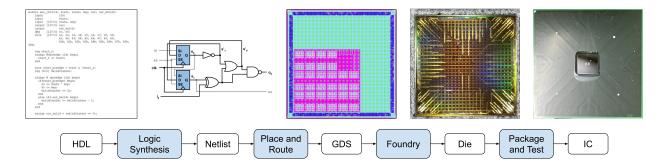

Figure 2.2: High-level view of IC manufacturing process

#### 2.1.2 Manufacturing Process Vulnerabilities

The significant cost of developing modern IC manufacturing processes has shifted the industry towards a fabless production model. A high-level diagram of the model is depicted in Fig. 2.2. First, a design team encodes the functionality of a design in a hardware description language (HDL). This description is passed to a logic synthesis tool that implements the functionality as a sequential circuit. The logic gates, sequential elements, and their interconnections are defined in a *netlist*. The netlist is passed to a place-and-route tool that maps the circuit to a 2-D grid, ultimately producing a GDS file containing a geometric description of the various transistor and metal layers to be printed. This GDS file is *taped-out*, i.e., sent to the foundry to manufacture the IC. The foundry produces bare IC dies that are then packaged and tested.

A critical security vulnerability results from third-party access to the design data. As a GDS file contains all necessary information for production, it is trivial for the foundry to *overproduce the design*. Furthermore, it is straightforward to reverse-engineer a design's functionality, extracting the netlist from the GDS. Other supply chain entities, such as the packaging company, can obtain the netlist through other means such as delayering the ICs [2]. The adversarial entity may then *leak design information* to other parties. Additionally, the foundry can *modify the design*, inserting hardware Trojans that disrupt functionality. These threats are a concern for both commercial IC design companies that invest large amounts of money in IC designs as well as government entities that produce

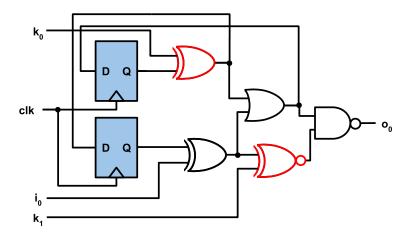

Figure 2.3: XOR logic locking example

ICs for security critical applications [3, 4, 5].

## 2.2 Logic Locking

Logic locking is a strategy for addressing these manufacturing security vulnerabilities. The designers add a set of key inputs to the circuit's netlist. The inputs are incorporated into the design such that under different values of the key inputs, the circuit's functionality changes. The foundry does not know what the proper key value is, thus any overproduced ICs or leaked design information will be incomplete. An adversary must select a functionally correct key out of the exponentially large space. After manufacturing, the correct key is applied to the circuit. A typical assumption is that the key is stored in a tamper-proof non-volatile memory.

A simple example is XOR logic locking in which parity gates (XOR/XNOR) invert signals depending on a key input [6]. The parity gates, termed key gates, are spliced into locations either selected randomly or with various heuristics maximizing corruption or interdependence [7, 8]. After insertion, the netlist is resynthesized, mixing the parity gates with the existing logic. A diagram is shown in Fig. 2.3 wherein two parity gates, highlighted in red, have been inserted into the circuit from 2.1. Note that the  $k_0$  parity gate has replaced an inverter from the original netlist. These manipulations create a large

amount of corruption within the circuit as the parity gate's entire upstream function is inverted.

Formally, a logic locking technique,  $\mathcal{L} : C(x) \to C_{lock}(x,k)$ , is a transform that takes a circuit, C(x), and produces a locked version,  $C_{lock}(x,k)$ . Under the correct key,  $k_c$ , the locked circuit produces the same behavior as the original circuit, however the exact notion of equivalence may depend on the locking technique. If the transform only modifies the combinational logic, it is sufficient to show equivalence proving that the next state logic and output logic cones are equivalent,  $\forall x C_{lock}(x, k_c) = C(x)$ . If the state elements are not preserved, sequential equivalence definitions must be used. While several different notions of sequential equivalence exist, in this work we use three-valued safe equivalence [9]. Here, each circuit node takes on a value from  $\{0, 1, X\}$ , where X represents unknown values. A locked circuit is equivalent to the original if after the application of a reset input sequence  $\mathcal{R}$ , no input sequence exists that would produce a different output sequence between the original and locked circuits. Specifically, for all reachable states after reset, the original and locked output functions are equivalent,  $(\lambda, \lambda_l) \in \{(0, 0), (1, 1), (X, X)\}$ . Generally, proving sequential equivalence is significantly harder than combinational equivalence due to the sheer size of the state spaces that might be encoded differently [10].

#### 2.2.1 Attack Models

In the characterization of the security of a logic locking technique, an attack model is used to specify assumptions regarding the adversary. Within the logic locking research community, a variety of attack models have been considered differing in regard to the artifacts, abilities, and success criteria of the adversary. As a result, understanding the targeted attack model is of utmost importance for any party implementing these locking techniques.

There are generally two artifacts to consider in defining the attack model: the locked

circuit's design data and a functioning version of the unlocked circuit. Adversarial access to the design data is a basic assumption of logic locking. However, depending on where the adversary is in the supply chain, the design data may vary. A foundry will have access to a GDS file, and thus can extract a netlist. Along, with the netlist, a foundry will have intimate knowledge of transistor and interconnect models, allowing detailed physical simulation and analysis. This would allow an adversarial foundry to obtain design features such as clock frequency. Other supply chain entities will likely have some subset of this access.

A more powerful attack model assumes access to a functioning version of the unlocked design. The unlocked circuit, referred to as an oracle, has the correct key set in its tamper-proof memory, affording the attacker black-box access. Obtaining an unlocked circuit may be trivial if the IC is available on the open market or may be the result of comprised physical security. Variations of this attack model have been considered in which the adversary does or does not have full access to the unlocked circuit's scan-chains. While scan-chains are essential in testing a design, they are also a powerful attack vector for an adversary.

Other considerations include the amount of processing power available to the adversary as well as the potential for side-channel analysis such as probing signal lines. Access to high-performance machines is cheap and foundries commonly use probing techniques to aid development of manufacturing processes and circuit failure analysis. Key values have been probed in nodes as small as 28nm [11]. However, as feature sizes continue to scale, this probing becomes more difficult, limited by spatial resolution [12]. Most work in logic locking has not directly considered this threat, relying on the validity of the tamper-proof memory assumption.

The definition of a successful attack can also vary. The most rigorous definition is finding a functionally equivalent key. In the combinational context, wherein the attacker has scan-chain access, the problem solved by the attacker is one of finding an exact key,  $k_e$ , for which the locked circuit produces the same function as the original,  $k_e$  :

$\forall x C_{\text{lock}}(x, k_{\text{e}}) = C_{\text{lock}}(x, k_{\text{c}})$ . A relaxed version of the exact recovery success criteria is approximate recovery. In this case, the attacker finds an approximate key,  $k_{\text{a}}$ , under which functionality of the locked circuit differs from the correct functionality with at most some probability  $\epsilon$ ,  $k_{\text{a}} : P_{x \in X}[C_{\text{lock}}(x, k_{\text{a}}) \neq C_{\text{lock}}(x, k_{\text{c}})] < \epsilon$ . Both definitions can be extended to sequential settings using the previous sections's definition of sequential equivalence.

#### 2.2.2 Brief Taxonomy

As in the example from Fig. 2.3, the earliest logic locking techniques inserted keyed parity gates into the original circuit's structure. Similar locks utilize multiplexors (MUXs) and Lookup Tables (LUTs) in lieu of parity gates [8, 13]. We refer to this class of techniques that generally maintain the original structure as *insertion locks*. Insertion locks can exhibit low overhead if the added gates avoid the design's critical timing paths. However, some insertion heuristics that increase security via greater key inter-dependency tend to create paths with many key gates, significantly impacting the delay. Unfortunately, under oracle attack models, these insertion locking schemes have been largely broken using a variety of methods, the most successful of which are miter-based attacks that use either satisfiability (SAT) solvers or ATPG tools to iteratively form constraints that the correct key must respect. [14]. More detail on these attacks is provided in section 2.3.

Researchers have attempted to increase the difficulty of mounting a miter-based attack by inserting attack-resilient logic blocks into the locked circuit [15, 16]. These techniques, collectively referred to as *iteration locks*, reduce the number of keys ruled out per attack iteration, significantly increasing the overall execution time. However, the logic blocks are susceptible to removal attacks since the circuitry is typically traceable through properties such as signal probability [17]. Fixes to these vulnerabilities have been proposed with the *strip-functionality* class of locking techniques that provide a better mixing scheme, but as to be detailed in section 3.1, have limited effectiveness.

Other schemes rely on circuit properties that the miter-based attack does not model. For instance, a cyclic obfuscation scheme assumes SAT solvers can only handle acyclic circuits [18]. It creates loops in the circuit's combinational logic to corrupt the miterbased attack. Another technique, delay-locking, adds tunable delay key gates to the design. Incorrect keys lead to setup and hold timing violations that the attack does not model by default. This comes at the cost of large delay overheads as the security scales, with reported average delay overheads of 60% [19]. While the security of these defenses initially seems promising, when their properties are correctly formulated within SAT, they can be easily broken [20, 21]. Moreover, commercial ATPG tools have built-in timing and loop breaking algorithms to automatically handle many of these situations [22].

Yet another class of locking mechanisms replaces portions of the design with highly configurable logic [23, 24, 25, 26]. The densely interdependent keys of these locks overwhelm SAT and ATPG solvers. A prototypical example is replacing gates with LUTs and adding configurable routing. The resulting locks resemble a field-programmable gate array (FPGA) embedded into the circuit. The existing incarnations of these locks vary in insertion methods, density, and mixing with original logic. These methods require careful integration into the system to avoid large overheads, in some cases delay overheads north of 200% have been reported. However, generally the class has been shown to be highly resistant to the typical miter-based attacks. In section 3.2, we will investigate methods of reducing these attack times.

Finally, while the preceding techniques just modify the combinational part of the design, sequential logic locking also manipulates the state elements. One such technique modifies the circuit's FSM to require a specific input sequence to transition from the reset state to the functionally correct set of states [27]. If an incorrect sequence is given, the circuit remains in a portion of the state space with incorrect behavior. This particular scheme is susceptible to a targeted removal attack [22, 28]. In general, sequential logic locking relies on limited scan-chain access to a design. However, recent work has extended the miter-based attack, originally developed for combinational circuits, into a model checker-based attack that assumes no scan-chain access [29, 30].

As clear from the preceding examples, there have been many directions explored for locking circuits. Unfortunately, none of these solutions balances security with low overhead, motivating further research in the area.

#### 2.2.3 Related Techniques

Other proposed strategies for IP security in manufacturing include fully programmable logic, split-fabrication schemes, camouflaged logic, and metering schemes.

Fully programmable logic solutions, such as FPGAs, are conceptually similar to logic locking wherein the device's configuration bits are analogous to the key. These commercially available devices enable the design functionality to be programmed post-manufacture, bypassing the IP security issues faced in circuit manufacturing. An adversary in this case has virtually no information, just the generic structure. Unfortunately, application requirements may prohibit the use of fully-programmable devices as the power, area, and delay overheads can be an order of magnitude higher compared to application specific circuits [31]. However, some applications may see significantly less overhead if they can utilize the hard-coded versions of common sub-circuits incorporated into most FPGAs.

Split-fabrication relies on two foundries producing portions of the design. Thus, barring collusion, neither foundry has full access to the design. *Split-Manufacturing* divides a design into front and back-end-of line partitions [32]. One partition contains the lowlevel metal and transistor layers, the other contains the remaining portion of the metal stack. Each partition is manufactured in a separate foundry and combined by a trusted entity. This is a potent solution but requires navigating complicated logistics between foundries. *Split-Chip* design utilizes two ICs to implement a system, a untrusted modernnode IC and a trusted legacy-node IC, providing combined security and performance [33, 34]. The trusted IC contains the security-critical control logic, and the untrusted IC contains the performance-critical components. This is a powerful solution to IP security, but requires a suitable system topology and the cost of a second IC.

Camouflage gates are logic elements that rely on subtle changes in structure to confuse delayering and imaging netlist extraction techniques. Examples of this include modifications to threshold voltages [35], dummy fill logic [36], and dummy via connections between metal layers [37]. While the foundry, which has access to the GDS, will detect these modifications, adversaries relying on netlist extraction techniques may reverse engineer an incorrect functionality. If the locations of the camouflaged gates can be identified, the possible functionalities can be modeled in a similar manner as logic locking, enabling oracle-based and potentially some netlist-based attacks.

Hardware metering consists of methods that enable tracking and controlling of ICs post-manufacturing. It is divided into passive and active categories [38]. Passive metering uniquely identifies each manufactured IC. This allows the designers to identify unlicensed copies of the design. There are several different schemes of encoding this unique identification including physically unclonable functions (PUFs), one-time programmable memories, and focused ion beam (FIB) modifications. Active metering provides a mechanism to enable or disable the IC. This can be done remotely via public-key cryptography systems [39] or locally on the IC in which case it is functionally similar to logic locking.

### 2.3 Attacks on Logic Locking

#### 2.3.1 Netlist-Based Attacks

The most critical attack model to consider is clearly the netlist-based attack. If a locked circuit can be deobfuscated in this context, there is no point to locking the circuit. Exam-

ples of these attacks have already been mentioned, specifically the removal attacks for iteration-based and sequential locks. In both cases, the lock adds some isolated structure to the circuit that is easily discernible from the original circuitry. Foiling the locking scheme is just a matter of tracing and removing the outgoing connections from the lock portion of the circuit. Section 3.1 will develop another such example, using sensitivity, a property of Boolean circuits.

Other netlist-based attacks utilize machine-learning algorithms to predict key values as seen in an attack on XOR locking [40]. The authors demonstrate that, even after synthesis, the changes to a netlist locked with parity gates are generally restricted to the immediate neighbors of a key input. Using this local structure as data, they train a classification algorithm and demonstrate prediction accuracy as high as 95%.

#### 2.3.2 Brute Force and Sensitization Attacks

Given the more powerful oracle attack model, a brute force attack establishes a baseline for the necessary key width of the circuit. This attack entails searching through the space of keys and inputs, ruling out a key if a mismatching input-output (IO) pair is found. Each key-input combination is applied to the circuit's netlist, simulating the output result. The output value is compared to the unlocked circuit's output under the same input, ruling out keys when a difference is observed. The rate at which keys can be ruled out depends on what portion of the input space is incorrect under each key and the expected number of keys to check depends on the portion of the input space that is equivalent to the functionally correct key. Assuming a typical scan-chain frequency of 100MHz and a state size of 1000 bits, a query to the oracle can occur at a rate of 100kHz. With access to 1 unlocked circuit and 1 month of attack time, an attacker can apply 2<sup>38</sup> key-input vectors.

One step beyond brute force is the use of sensitization methods to propagate a key value to an output node [41, 22]. Sensitization is essential to ATPG tools and conse-

quently is highly optimized. Sensitizing a node consists of finding an input pattern that when applied to the circuit will propagate the value (or inverse) of the node to an output. Under such an input pattern, toggling the node would toggle some output. Using sensitization as an attack is done by iterating over the key bits, applying unknown (X) values for all other key inputs. Then attempting to sensitize the current key to an output. If successful, the key value will be known and can be set to the appropriate value in subsequent iterations, simplifying the problem. This process is repeated until fixed-point where no additional key inputs can be sensitized.

#### 2.3.3 Miter-Based Attacks

Beyond brute-force and sensitization attacks, the oracle attack model enables the mounting of a more targeted, miter-based attack. This attack uses the netlist and unlocked circuit to iteratively produce input-output (IO) relationships [14]. These relationships are used to rule out all keys that do not produce the same behavior, narrowing the space of possible circuit functionalities. As previously mentioned, these attacks can be implemented using SAT solvers or ATPG tools as the underlying kernel. We focus on SAT-based version, which is used throughout this work.

#### **Propositional Satisfiability**

A common approach to deal with hard combinatorial problems, such as finding the key of locked circuits, is to encode them into propositional logic and solve the resulting propositional formulas with a satisfiability (SAT) solver. The performance of SAT solvers improved significantly in the last two decades and they are used for many applications in hardware and software verification [42, 43]. In recent years, SAT solvers have also been successfully applied to various attacks, such as hash collisions [44] and mathematical challenges [45].

The most successful class of SAT solvers are based on the conflict-driven clause learn-

Figure 2.4: Miter-based attack steps: (a) Miter circuit construction, (b) Unlocked (oracle) circuit produces correct IO functionality (c) Addition of learned IO constraint to miter circuit

ing (CDCL) algorithm [46, 47]. Briefly, CDCL solvers work by repeatedly selecting a variable through heuristics and assigning a value. Implications from the assignments are determined using a highly optimized process called *unit propagation*. If a conflict is found, a clause is added to the formula that rules out assignments causing the conflict. Then the solver non-chronologically backtracks based on the conflict and continues, repeating this process until a solution is found or the problem is found to be unsatisfiable.

The typical encoding of the SAT problem is in the conjunctive normal form (CNF). This form consists of a set of clauses that must all be satisfied. Each clause is a disjunction of literals. A circuit can be encoded into propositional logic via the Tseitin transformation [48]. This transformation can take a circuit netlist and produce a set of clauses that, when collectively satisfied, will correspond to the original circuit's behavior.

#### **Combinational Attack**

If the adversary has access to the design's scan chain, the miter-based attack can be executed considering just the circuit's combinational logic. In this case, the IO relationships are efficiently learned through a three-step procedure: **I.** First, a miter circuit, *M*, is used to determine an input that is guaranteed to rule out at least a single key. A miter circuit consists of two copies of the original circuit with the inputs tied together, the key inputs kept separate, and the outputs connected to comparators. A diagram of the connections is shown in Fig. 2.4(a). Additional key constraints, such as timing and loop breaking, can be conjuncted with the miter output. A SAT solver is used to find a setting of the shared input (x) and key inputs  $(k_0, k_1)$  such that the output of the miter circuit is logic 1. By construction, the solution to the SAT problem will have two different keys that, at that input value, disagree on the output value. The shared input value found by the solver is termed a differentiating input. **II.** Next, as depicted in Fig. 2.4(b), the differentiating input,  $x_i$ , is applied to the oracle circuit to determine the differentiating output,  $y_i$ , forming an input-output pair that the correct key must respect; any key that does not conform to this IO pair is incorrect. III. Finally, as shown in Fig. 2.4(c), the IO pair is added as a constraint to the miter circuit for the next iteration. Now, any keys that satisfy the miter circuit will also satisfy the learned IO relationship. While each relationship is guaranteed to rule out at least one key, in practice, a larger portion of the key space is ruled out due to overlapping key functionalities at a given input. These steps repeat, adding more constraints until the miter circuit is unsatisfiable. At this point, any key that respects all learned IO relationships will be a functionally correct key. We outline the pseudo-code for this attack in algorithm 1.

#### **Sequential Attack**

The sequential version of the miter-based attack uses the same oracle and miter circuit but extends the concept of a differentiating input to a differentiating input *sequence*. To handle the state elements in the design, this attack substitutes the SAT solver for a model checker. The model checker is able to automatically unroll the circuit in time, connecting the state input of one cycle to the state output of the next. Every input sequence is assumed to start from a potentially unknown, but *fixed* reset state,  $s^0$ . In the

#### Algorithm 1: Miter-Based Attack

```

Input: C_{lock}, C_{oracle}

Output: k_{attack}

1 M := C_{lock}(x, k_0) \neq C_{lock}(x, k_1);

2 D := \emptyset;

3 i := 0;

4 while SAT[M \land D] do

5 | x_i := SAT\_ASSIGNMENT_x[M \land D];

6 | y_i := C_{oracle}(x_i);

7 | D := D \land C_{lock}(x_i, k_0) = y_i \land C_{lock}(x_i, k_1) = y_i;

8 | i := i + 1;

9 end

10 return SAT\_ASSIGNMENT_{k_0}[D]

```

same fashion as the SAT-based attack, a miter circuit is used to find input sequences that produce different output sequences for different keys. The miter circuit is unrolled as in Fig. 2.5(a). These input sequences are applied to the oracle and the produced outputs form IO relationships that are again encoded into the miter circuit as unrolled constraints as depicted in Fig. 2.5(b). Aside from the reduced controllability and observability from the state elements, the most significant difference between the combinational and sequential attacks is in the termination conditions.

While a SAT solver can be used to exhaustively prove that no input can satisfy a combinational miter circuit, when state is considered, the task is a much harder. This is mainly due to the state space explosion associated with allowing the model checker to unroll the circuit indefinitely [49]. Thus, in previous work, the model checker attack relies on secondary termination conditions: a check that only one key remains and a logical equivalence check for the combinational logic fan-in into each flip-flop. Without these equivalence conditions the termination relies on unbounded model checking algorithms [50, 51]. For a more complete description of the model checker-based attack, we direct the reader to [29, 30].

Figure 2.5: Miter-based model checker attack steps: (a) Miter circuit unrolling, (b) Differentiating sequence constraint.

#### **Constraint Aided Attacks**

The miter-based attack has become the standard attack paradigm as it is able to quickly deobfuscate many existing techniques. As mentioned in section 2.2.2, logic mechanisms have been developed that utilize non-standard design practices to prevent a miter-based attack from converging. Introducing combinational loops into circuits can cause a SAT solver to non-deterministically resolve the circuit state, corrupting the attack by breaking the correspondence between the real oracle circuit and logical miter circuit. This correspondence can also be broken by introducing key elements that modulate timing in the circuit. Without knowledge of the circuit's timing, a key produced from the miter-based attack will likely have incorrect functionality via timing violations. Despite their initial promise of miter-based attack resistance, when properly modeled, these techniques are easily broken. For each technique, critical information is withheld from the SAT solver causing it to incorrectly terminate. Reintroducing this information through additional key constraints avoids corruption. In these examples adding key constraints that rule out keys with oscillating loops and modifying the netlist to encode the change functionality with changed timing characteristics allows the attack to terminate correctly.

# Chapter 3

# **Security of Existing Locking Schemes**

In this chapter, we develop deobfuscating attacks for two families of logic locking techniques. The first attack takes advantage of traces left by the locking procedure, enabling the modified portion of the circuit's input space to be isolated and corrected. The second utilizes improved attack modeling to dramatically reduce attack times. For each broken lock scheme, we develop improvements that resist our attacks. We then use these attacks and corresponding fixes to inform the development of our own locking technique in chapter 4.

### 3.1 Sensitivity Analysis of Strip-Functionality Locks

Our first attack applies to the *strip-functionality* class of locking techniques, mentioned in section 2.2.2. This class was developed in response to the miter-based attack and represents a sizeable thread of logic locking research. In this section, we explore the use of Boolean sensitivity in analyzing this class of locks. Sensitivity is shown to be a powerful signal that can reveal the key of the locked circuits. We propose an improved insertion technique that mitigates this attack, but only for certain circuits.

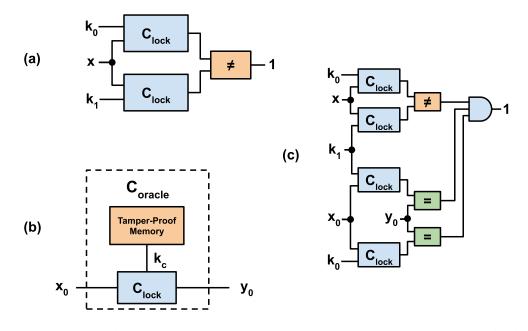

Figure 3.1: Underlying structure of strip-functionality locking

#### 3.1.1 Strip-Functionality Locking

Strip-functionality locking refers to a class of techniques that share a similar mechanism for directly defending against the miter-based attack. The locks resist the attack by reducing the number of keys ruled out per iteration, significantly increasing the overall execution time. This class of techniques currently includes TTLock [52], TTLock\* [53], SFLL-HD [54], and SFLL-Flex [54].

Under this class of locking schemes, functionality is *stripped* from the circuit by inverting the output response under certain inputs. This set of inputs is referred to as the protected inputs. The inverted functionality is re-established using restoration circuitry paired with the correct key. The restoration part of the locking circuitry can be isolated and removed by tracing key inputs, however, the resulting circuit still exhibits incorrect behavior at the protected inputs.

The generic structure of these techniques is shown in Fig. 3.1. For simplicity, we just show a single output cone of the locked circuit, which we denote as f. The locked circuit consists of two layers, flip and restore. Both layers make use of a function, P(x,k), that checks if an input, x, is part of the protected set determined by the key, k. Different values of k will produce different protected sets.

The flip layer contains the original function, f, and a instance of P with the key input hard coded at the correct value,  $k_c$ . The outputs of both functions are XOR'd together, inverting the original function for the protected inputs. We refer to the flip layer function

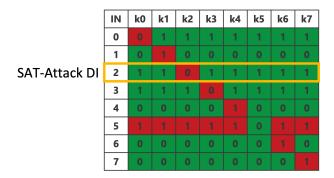

Figure 3.2: Truth table of circuit locked with TTLock

as  $f_{\text{flipped}}$ ; it is equivalent to f except at the protected inputs. The restore layer contains another instance of P, XOR'd with the output of the flip layer. When the key input, k, matches  $k_c$ , the correct functionality of the original function is restored, each protected input value's output being flipped twice. We refer to the whole function with the restore layer as  $f_{\text{locked}}$ . The whole circuit is synthesized together, mixing and reducing the logic from both layers along with  $k_c$ . It is likely that the restore layer's P function remains intact as synthesis is unable to reduce the logic. However, the flip layer's P function and  $k_c$  are usually combined with the logic of f such that they are not recognizable via inspection.

These techniques resist the miter-based attack because the overlap between the flipped input patterns for different keys is kept low. Thus, when an IO constraint is formed in the miter-based attack, only a small number of keys are ruled out at once. An example of this is shown in the truth table of Fig. 3.2 where the highlighted differentiating input only rules out a single key. Also note that input 5 is the protected input. If this input is found, the technique is broken as only a single key agrees with the correct output. While the exact scaling of the attack resistance depends on the specific technique, the class as a whole shows greatest miter-based attack resistance when the number of protected inputs is minimal. Thus, there is an inherent trade-off between attack resistance and corruption of the circuit.

The specific techniques within the class are largely similar but each can be briefly

described as following. TTLock is the original technique in this class; the method flips a single input pattern that is equal to the key. Thus, in this incarnation, P is a equality function. TTLock\* is a version of TTLock that tries to mitigate any netlist-based attacks by converting the locked circuit to a reduced order Boolean decision diagram and resynthesizing. Effectively, this technique does a better job of mixing the f with the flip layer's hard coded  $k_c$  and P function. SFLL-HD is a generalization of TTLock in which every input pattern a fixed Hamming distance from the key is flipped. In SFLL-HD, P computes the Hamming distance between the key and input, then compares this to a fixed value to determine if the input is protected. Finally, SFLL-Flex stores a set of user-specified protected input patterns in a lookup table (LUT). In this case, P is a function that is logic 0 for all inputs except the selected input values.

#### 3.1.2 Boolean Sensitivity Attack

Sensitivity is a simple complexity measure of a Boolean function [55]. Defined at a particular value in the input space, it is the number of inputs Hamming distance 1 from a particular input, for which the function produces a different value. Defined over the function, it is the maximum sensitivity of all inputs. We can specify each case more formally given a Boolean function,  $f : \{0,1\}^n \rightarrow \{0,1\}$  and an input value, x. If  $x_{\text{flip}(i)}$  represents the input value with the *i*th bit inverted, the sensitivity of f at x, s(f, x), is the following:

$$s(f,x) = \frac{\sum_{i=1}^{n} f(x) \oplus f(x_{\text{flip}(i)})}{n}$$

(3.1)

Thus, the sensitivity of f, s(f), is:

$$s(f) = \max_{x} s(f, x) \tag{3.2}$$

Finally, we define the average sensitivity of f,  $\bar{s}(f)$  as:

$$\bar{s}(f) = \frac{\sum_{x \in \{0,1\}^n} s(f,x)}{2^n}$$

(3.3)

Figure 3.3: Circuit that determines sensitivity where s(f, x) is the sensitivity of f at a given input x and  $x_{\text{flip}(i)}$  represents x with the *i*th bit flipped

Sensitivity is interesting in analyzing strip-functionality circuits because it is an easily computed metric *and its value is inverted for protected inputs*. Consider an input value,  $x_{protected}$ , chosen at random to become a protected input. In the original circuit, if the input has a low sensitivity, most inputs Hamming distance 1 away will agree. As we know, the locking procedure will invert the output value for this input value using the flip layer's *P* function. This means that most of neighboring inputs now disagree with the protected input. Specifically, where *f* is the original circuit and  $f_{flipped}$  is the locked circuit without the restoration circuitry (ie. just the flip layer), the new sensitivity is:

$$s(f_{\text{flipped}}, x_{\text{protected}}) = 1 - s(f, x_{\text{protected}})$$

(3.4)

Thus, the protected input is moved to the opposite end of the sensitivity distribution. This sensitivity inversion is potentially a usable signal to find the protected inputs.

This raises the question, what does the sensitivity distribution look like for typical circuits? To understand the behavior of sensitivity, we consider a set of benchmark circuits [56], which are commonly used in the logic locking and circuit testing communities. Each circuit contains several Boolean functions. For each function, f, we estimate the average sensitivity across all inputs,  $\bar{s}(f)$ , and find the sensitivity of the function, s(f).

The average sensitivities are determined by sampling a set of randomly selected values in the input space of each function. The sensitivity, s(f, x), is evaluated at each input value by calculating the output value of the input value and all neighbors Hamming dis-

Figure 3.4: Average sensitivity,  $\bar{s}(f)$ , versus input width of benchmark circuits from 50 samples

tance 1 away, summing the number of disagreements. This random input selection is the same method used to pick keys in the strip-functionality techniques, giving us an idea of the likely sensitivity of the protected inputs.

To find the sensitivity of each function, s(f), we build a circuit that quantifies the sensitivity at a given input. This circuit, shown in Fig. 3.3, is made up of n + 1 copies of the function, where n is the width of the function's input. The inputs of the first copy of the function are tied to the n additional copies such that a different bit is flipped for each. The outputs are fed to comparators and subsequently a population count that determines the sensitivity at the input. The circuit is loaded into a SAT solver and the output sensitivity value is constrained to value, s. Starting from n, s is decremented until a satisfying assignment can be found for the circuit. The first input found will have a sensitivity value, s/n, the highest of any input. This defines the sensitivity value of the overall function.

Figure 3.5: Sensitivity, s(f), versus input width of benchmark circuits

The results of this analysis are shown in Fig. 3.4 and 3.5, where  $\bar{s}(f)$  and s(f) versus input width are respectively plotted. We see that most circuit output functions exhibit low average sensitivity, furthermore a substantial portion have maximum input sensitivities of less than 0.5. Another clear trend is that the average and maximum sensitivity is inversely proportional to the input width. From a designer's perspective, this makes intuitive sense since specifying a complex function of many inputs is difficult. A notable outlier is c6288, a multiplier circuit, that maintains a high average local sensitivity for larger inputs. This trend implies that at a sufficiently large input width, if an input is randomly selected as a protected pattern, the new sensitivity of this input will go from an *average low* to an *outlying high* value. Selecting inputs with large input width is motivated by increased brute force and miter-based attack resistance. As the selection for the strip-functionality techniques does not consider the sensitivity of the protected pattern, it is likely that the protected input pattern will have a final input sensitivity that is an outlier in the high end of the distribution.

Algorithm 2: Sensitivity-Based Attack

```

Input: n, f, f<sub>flipped</sub>

Output: x<sub>protected</sub>

1 sen := n;

2 block := \emptyset;

<sup>3</sup> while sen > 0 do

CNF := (s(f_{\text{flipped}}, x) = sen) \land block;

4

if SAT[CNF] then

5

x_{\text{protected}} := \text{SAT}_\text{ASSIGNMENT}_x[CNF];

6

if f(x_{\text{protected}}) \neq f_{\text{flipped}}(x_{\text{protected}}) then

7

return x<sub>protected</sub>

8

end

9

block := block \land (x_{protected} \neq x);

10

11

else

sen := sen - 1;

12

end

13

14 end

```

Using the same sensitivity quantifying circuit from Fig. 3.3, we can build an attack algorithm that will detect inputs with high sensitivity. While the resulting key can only be definitively verified with access to an unlocked IC, finding the likely keys only requires access to the netlist. The first step in building such an attack is preprocessing the locked circuit netlist. We find a function,  $f_{locked}$ , in the circuit that has the restoration unit in its fan-in. This can be done by tracing the key inputs through the circuitry. The restoration unit is removed from the netlist, creating a circuit functionally equivalent to  $f_{flipped}$ . In TTLock, TTLock\*, and SFLL-Flex this entails adding constraints such that the input is not equal to the key. In SFLL-HD, the Hamming distance between the input and key must not be at the fixed value.

After obtaining  $f_{\text{flipped}}$ , we build the sensitivity quantifying circuit. We add a constraint setting the unnormalized sensitivity to the maximum value, n (the input width of the function). This instance is put into a SAT solver searching for an input with this sensitivity level. The sensitivity is decremented until a satisfying input is found. The satisfying input is then applied to the oracle, f. If the output is the same as the simu-

lated result from  $f_{\text{flipped}}$ , a constraint ruling out this input is added to a set of blocking clauses, *block*, and the process continues, searching for the next highest sensitivity input. If the output is different, it is a protected pattern. For TTLock and TTLock\* this pattern is the key. For SFLL-Flex, this process must be repeated until all protected inputs in the LUT are found. Finally, for SFLL-HD, a total of three patterns with a mutual Hamming distance of twice the fixed value are found. The value of each key bit is then determined by the taking majority of the discovered protected inputs. The pseudo-code of the attack is listed in Algorithm 2.

### 3.1.3 Resistant Locking Scheme

For certain circuits, TTLock can be adapted such that the sensitivity-based attack is no longer effective. We demonstrate this process to show the limits of our attack method, however, we do not see this fixed TTLock as a viable locking method as the amount of output corruption is too small to be meaningful.

Resisting the sensitivity-based attack can be achieved by selecting an input that, after flipping its output value, is not a sensitivity outlier. This means locking an input that will subsequently be moved to a dense part of the sensitivity distribution. Here, we implement an algorithm that targets the average sensitivity as the final value. Resistance to the sensitivity-based attack must be balanced with brute force and miter-based attack resistance in which the function's input width determines the expected number of iterations. This entails locking an output function that has at least a given number of inputs. Thus, from all output functions in the circuit with input width greater than the required value, we want to find the function, f, and input value, x, such that:

$$\arg\min_{x,f} |\bar{s}(f) - (1 - s(f, x))|$$

(3.5)

To find the optimal input, we first rule out all functions that do not meet the desired brute force and miter-based attack resistance. For each function in the list of remaining functions,  $f \in F$ , we compute a mapping of input widths,  $N : f \rightarrow n$ , and of estimates

### Algorithm 3: Sensitivity Attack Resistant TTLock

**Input:** set of functions *F*, set of input widths *N*, set of average sensitivities *A* **Output:** optimal protected input  $x_{protected}$ , function *f*

```

1 b := 0;

<sup>2</sup> while b < max(N) do

for f \in F do

3

n := N[f];

4

a := A[f];

5

CNF := |a - (1 - s(f, x))| \le b/n;

6

if SAT[CNF] then

7

x_{\text{protected}} := \text{SAT}_\text{ASSIGNMENT}_x[CNF];

8

return x<sub>protected</sub>, f

9

end

10

end

11

b := b + 1;

12

13 end

```

of the average sensitivities,  $A : f \to \overline{s}(f)$ , using the same method from Section 3.1.2. We then search for the function and input pair that has a flipped sensitivity closest to the average value for the function. This is done by iteratively relaxing a bound, *b*, until a function is found that has an input with flipped sensitivity less than b/n from the function's average sensitivity. After finding the optimal input, it is flipped following the original TTLock method. The pseudo-code of the algorithm to find the optimal protected input is shown in Algorithm 3.

Like TTLock, a sensitivity attack resistant version of SFLL-Flex can be easily created by repeating this process multiple times. However, SFLL-HD is harder to make resistant to the sensitivity-based attack. To avoid easy detection, all flipped inputs must have low sensitivity. Finding a set of inputs with this property and are all a fixed Hamming distance from a common value is unlikely.

### 3.1.4 Attack Results

To assess the strength of our sensitivity-based attack against strip-functionality locking as well as our modified version of TTLock, we ran three experiments. First using a com-

| Technique | Circuit | N <sub>bits</sub> | Time(s) | N <sub>iter</sub> |

|-----------|---------|-------------------|---------|-------------------|

| TTLock    | c5315   | 32                | 3       | 1                 |

| TTLock    | c7552   | 32                | 3       | 1                 |

| SFLL-HD   | DFX     | 256 (HD=32)       | 584     | 3                 |

Table 3.1: Sensitivity attack results for author-provided circuits using Cadence Jasper-Gold

mercially available tool, Cadence JasperGold, we demonstrate the attack's applicability on a set of locked benchmarks provided by the authors of the respective techniques from the strip-functionality class. To further validate these results, we then extend this analysis to an additional set of generated locked circuits. Finally, we implement the attack using open-source tools and repeat the analysis on the generated circuits.

All attacks are run using a 64GB, 24-core, 2.2GHz machine. JasperGold, the commercial tool, is a formal verification suite that uses a parallel execution strategy attempting to find a solution employing several different solvers at once. In this case, our attack algorithm is implemented in TCL, a widely adopted scripting language used in digital IC design tools. Our open-source flow, uses the CaDiCaL SAT solver [57] and Python to implement the attack algorithm. For all experiments, we limit each run to a timeout of 4 hours. The implementation of this flow can be found in our repository<sup>1</sup>.

In Table 3.1, we present the results of our attack on the circuits provided by the authors. For each circuit we show the number of bits used to lock it, the overall time to execute the attack, and the number of iterations (the number of inputs checked in the oracle). As seen, all circuits are broken, most in seconds, the largest in minutes. This is significantly faster than the expected miter-based attack time, which scales exponentially in the width of the key. As sensitivity is not considered in these locking schemes, in all cases the protected inputs are the highest sensitivity inputs keeping the required number of iterations small.

For the next experiments, we implement the strip-functionality locking techniques

<sup>&</sup>lt;sup>1</sup>https://github.com/jpsety/sensitivity\_attack

|         |                | TTLo    | ck             | TTLo    | ck*            | SFLL-   | HD             | SFLL-I  | Flex           | TTLock-Sen |                |

|---------|----------------|---------|----------------|---------|----------------|---------|----------------|---------|----------------|------------|----------------|

| Circuit | $N_{\rm bits}$ | Time(s) | $N_{\rm iter}$ | Time(s)    | $N_{\rm iter}$ |

| c499    | 32             | 1       | 2              | 70      | 6              | 2 3     |                | 8       | 25             | timeout    | 3106           |

| c880    | 32             | 1       | 1              | 4       | 4              | 2       | 4              | 3       | 8              | timeout    | 3480           |

| c1355   | 32             | 1       | 3              | 3849    | 181            | 2       | 3              | 5       | 14             | timeout    | 3492           |

| c1908   | 32             | 1       | 1              | 18      | 2              | 3       | 4              | 3       | 6              | timeout    | 3339           |

| c2670   | 32             | 1       | 1              | 6       | 1              | 2       | 3              | 2       | 4              | 68         | 62             |

| c2670   | 64             | 1       | 1              | 5       | 1              | 4 3     |                | 7       | 8              | 70         | 62             |

| c3540   | 32             | 2       | 2              | 24      | 1              | 2       | 3              | 2       | 6              | timeout    | 2096           |

| c5315   | 32             | 2       | 3              | 1       | 1              | 2       | 3              | 2       | 5              | timeout    | 3028           |

| c5315   | 64             | 4       | 9              | 3       | 1              | 4       | 3              | 10      | 14             | 24         | 26             |

| c7552   | 32             | 1       | 1              | 4       | 1              | 3       | 3              | 69      | 16             | timeout    | 2700           |

| c7552   | 64             | 2       | 1              | 19      | 1              | 3       | 3              | 4       | 4              | timeout    | 2568           |

| c7552   | 128            | 4       | 1              | 16      | 16 1           |         | 3              | 9       | 8              | timeout    | 1670           |

Table 3.2: Sensitivity attack results for generated circuits using Cadence JasperGold. For SFLL-HD,  $HD = N_{bits}/8$  and for SFLL-Flex,  $N_{patterns} = N_{bits}/8$ .

Table 3.3: Sensitivity attack results for generated circuits using the SAT solver CaDiCaL. For SFLL-HD, HD =  $N_{\text{bits}}/8$  and for SFLL-Flex,  $N_{\text{patterns}} = N_{\text{bits}}/8$ .

|         |                | TTLo    | ck             | TTLo                      | ck* | SFLL-   | HD             | SFLL-I  | Flex           | TTLock-Sen |       |  |

|---------|----------------|---------|----------------|---------------------------|-----|---------|----------------|---------|----------------|------------|-------|--|

| Circuit | $N_{\rm bits}$ | Time(s) | $N_{\rm iter}$ | Time(s) N <sub>iter</sub> |     | Time(s) | $N_{\rm iter}$ | Time(s) | $N_{\rm iter}$ | Time(s)    | Niter |  |

| c432    | 32             | 0.20    | 1              | 0.15 1                    |     | 0.67    | 3              | 0.63    | 4              | timeout    | 11018 |  |

| c499    | 32             | 0.06    | 2              | 26.64                     | 1   | 0.36    | 3              | 57.14   | 918            | timeout    | 12243 |  |