# Establishing Software Root of Trust Unconditionally

Virgil D. Gligor, Maverick S.L. Woo

November 7, 2018

CMU-CyLab-18-003

CyLab Carnegie Mellon University Pittsburgh, PA 15213

# Establishing Software Root of Trust Unconditionally

Virgil D. Gligor

Maverick S.L. Woo

Carnegie Mellon University CMU-CyLab TR 18-003 November 7, 2018

Abstract—Root-of-Trust (RoT) establishment ensures either that the state of an untrusted system contains all and only content chosen by a trusted local verifier and the system code begins execution in that state, or that the verifier discovers the existence of unaccounted for content. This ensures program booting into system states that are free of persistent malware. An adversary can no longer retain undetected control of one's local system.

We establish RoT *unconditionally*; i.e., without secrets, trusted hardware modules and instructions, or bounds on the adversary's computational power. The specification of a system's chipset and device controllers, and an external source of true random numbers, such as a commercially available quantum RNG, is all that is needed. Our system specifications are those of a concrete Word Random Access Machine (cWRAM) model – the closest computation model to a real system with a large instruction set.

We define the requirements for RoT establishment and explain their differences from past attestation protocols. Then we introduce a RoT establishment protocol based on a new computation primitive with concrete (non-asymptotic) optimal space-time bounds in adversarial evaluation on the cWRAM. The new primitive is a *randomized polynomial*, which has kindependent uniform coefficients in a prime order field. Its collision properties are stronger than those of a k-independent (almost) universal hash function in cWRAM evaluations, and are sufficient to prove existence of malware-free states before RoT is established. Preliminary measurements show that randomizedpolynomial performance is practical on commodity hardware even for very large k.

To prove the concrete optimality of randomized polynomials, we present a result of independent complexity interest: a Hornerrule program is *uniquely optimal* whenever the cWRAM execution space and time are simultaneously minimized.

# I. INTRODUCTION

Suppose a user has a trustworthy program, such as a formally verified micro-kernel [45] or a micro-hypervisor [89], and attempts to boot it into a specific system state. The *system state* comprises the contents of all processor and I/O registers and random access memories of a chipset and peripheral device controllers at a particular time; e.g., before boot. If any malicious software (*malware*) can execute instructions anywhere in the system state, the user wants to discover the presence of such malware with high probability.

This goal has not been achieved to date. System components that are *not* directly addressable by CPU instructions

Network and Distributed Systems Security (NDSS) Symposium 2019

24-27 February 2019, San Diego, CA, USA

ISBN 1-891562-55-X

https://dx.doi.org/10.14722/ndss.2019.23170

www.ndss-symposium.org

or by trusted hardware modules enable malware to survive in non-volatile memories despite repeated power cycles, secureand trusted-boot operations [67]; i.e., malware becomes *persistent*. For example, persistent malware has been found in the firmware of peripheral controllers [19], [53], [83], network interface cards [20], [21], disk controllers [5], [59], [71], [93], USB controllers [2], as well as routers and firewalls [5]. Naturally, persistent malware can infect the rest of the system state, and thus a remote adversary can retain long-term undetected control of a user's local system.

Now suppose that the user attempts to initialize the local system state to content that s/he chooses; e.g., malware-free code, or I/O register values indicating that the system is disconnected from the Internet. Then, the user wants to verify that the system state, which may have been infected by malware and hence is untrusted, has been initialized to the chosen content.

Root of trust (RoT) establishment on an untrusted system ensures that a system state comprises all and only content chosen by the user, and the user's code begins execution in that state. All implies that no content is missing, and only that no extra content exists. If a system state is initialized to content that satisfies security invariants and RoT establishment succeeds, a user's code begins execution in a secure initial state. Then trustworthy OS programs booted in a secure initial state can extend this state to include secondary storage and temporarily attached (e.g., USB) controllers. If RoT establishment fails, unaccounted for content, such as malware, exists. Hence, RoT establishment is sufficient for (stronger than) ensuring malware freedom and necessary for all software that needs secure initial states, such as access control and cryptographic software. However, as with secure and trusted boot, the trustworthiness of the software booted in secure initial states is not a RoT establishment concern.

**Unconditional Security**. In this work we establish RoT unconditionally; i.e., without secrets, trusted hardware modules and special instructions (e.g., TPMs [87], ROMs [22], [38], SGX [18]), or polynomial bounds on an adversary's computing power. By definition, a solution to a security or cryptography problem is unconditional if it depends only on the existence of physical randomness [13] and the ability to harvest it [37], [70]. Unconditional security solutions have several fundamental advantages over conditional ones. For example:

- they are independent of any security mechanism, protocol, or external party whose trustworthiness is uncertain; e.g., a mechanism that uses a secret key installed in hardware by a third party depends on the unknowable ability and interest of that party to protect key secrecy.

- they limit any adversary's chance of success to provably

A short version of this paper will be presented at the

low probabilities determined by the defender; i.e., they give a defender undeniable advantage over the adversary.

• they are independent of the adversary's computing power and technology used; e.g., they are useful in post-quantum computing.

In unconditional RoT establishment all the user needs is an external source of non-secret physical randomness, such as one of the many commercially available quantum random number generators, and correct system specifications. That correct system specifications are indispensable for solving any security and cryptography problem has been recognized for a long time. As security folklore paraphrases a well-known quote [92]: "a system without specifications cannot be (in)secure: it can only be surprising." For RoT establishment, specifications are necessarily low-level: we need a concrete Word Random Access Machine (cWRAM) model of computation (viz., Appendix A), which is the closest model to a real computer system. It has a constant word length, up to two operands per instruction, and a general instruction-set architecture (ISA) that includes I/O operations and multiple addressing modes. It also supports multiprocessors, caches, and virtual memory.

**Contributions and Roadmap.** We know of no other protocols that establish RoT provably *and* unconditionally. Nor do we know any other software security problem that has been solved unconditionally in any realistic computational model. This paper is organized as follows.

*Requirements Definition* (Section II). We define the requirements for RoT establishment, and provide the intuition for how to jointly satisfy them to establish malware-free states and then RoT. In Section VIII we show that these requirements *differ* from those of past attestation protocols; i.e., some are stronger and others weaker than in past software-based [7], [47], [77], [78], [80], cryptographic-based [8], [22], [27], [38], [46], [64], and hybrid [53], [94] attestation protocols.

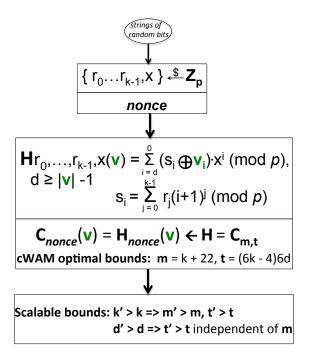

New Primitive for establishing malware-free states (Section IV). To support establishment of malware-free system states, we introduce a new computation primitive with optimal space (m)-time (t) bounds in adversarial evaluation on cWRAM, where the bounds can scale to larger values. The new primitive is a randomized polynomial, which has k-independent uniform coefficients in a prime order field. It also has stronger collision properties than a k-independent (almost) universal hash function when evaluated on cWRAM. We use randomized polynomials in a new verifier protocol that assures deterministic time measurement in practice (Section VI). Preliminary measurements (Section VII) show that their performance is practical on commodity hardware even for very large k; i.e., k = 64.

*RoT establishment* (Section V). Given malware-free states, we provably establish RoT and provide secure initial states for all software. This requirement has not been satisfied since its identification nearly three decades ago; e.g., see the NSA's Trusted Recovery Guideline [62], p. 19, of the TCSEC [61].

*Optimal evaluation of polynomials* (Section III). We use Horner's rule to prove concrete optimal bounds of randomized polynomials in the cWRAM. To do this, we prove that a Horner-rule program is *uniquely optimal* whenever the cWRAM execution space and time are simultaneously minimized. This result is of independent complexity interest since Horner's rule is uniquely optimal only in infinite fields [12] but is *not* optimal in finite fields [23], [43].

Appendix A provides a description of the cWRAM model. Appendix B contains the proofs of the theorems, lemma, and corollary of Section IV. Appendix C illustrates the implementation of the cWRAM encoding of Horner-rule steps in real processors, the selection of k for these processors, and practical ways to map strings of program words to strings of  $\mathbf{Z}_{p}$  integers; i.e., to the inputs of randomized polynomials.

# II. REQUIREMENTS DEFINITION

To define the requirements for RoT establishment we use a simple *untrusted* system connected to a *trusted* local verifier.

Suppose that the system has a processor with register set Rand a random access memory M. The verifier asks the system to initialize M and R to chosen content. Then the verifier sends a random *nonce*, which selects  $C_{nonce}$  from a family of computations  $\mathbf{C}_{\mathbf{m},\mathbf{t}}(M,R)$  with space and time bounds m and t, and challenges the system to execute computation  $C_{nonce}$  on input (M, R) in m words and time t. Suppose that  $\mathbf{C}_{\mathbf{m},\mathbf{t}}$  is space-time (i.e., *m*-*t*) optimal, result  $C_{nonce}(M,R)$  is unpredictable by an adversary, and  $C_{nonce}$  is non-interruptible. If  $C_{m,t}$  is also second pre-image free and the system outputs result  $C_{nonce}(M,R)$  in time  $t^1$ , then after accounting for the local communication delay, the verifier concludes that the system state (M, R) contains all and only the chosen content. Intuitively, second pre-image freedom and m-t optimality can jointly prevent an adversary from using fewer than m words or less time than t, or both, and hence from leaving unaccounted for content (e.g., malware) or executing arbitrary code in the system.

When applied to multiple device controllers, the verifier's protocol must ensure that a controller cannot help another undetectably circumvent its bounds by executing some part of the latter's computation; e.g., act as an *on-board proxy* [53].

### A. Adversary

Our adversary can exercise all known attacks that insert persistent malware into a computer system, including having brief access to that system to corrupt software and firmware; e.g., an extensible firmware interface (EFI) attack [63] by an "evil maid." Also, it can control malware remotely and extract all software secrets stored in the system via a network channel. Malware can read and write the verifier's local I/O channel, but does not have access to the verifier's device and external source of true random numbers.

For unconditional security, we assume that the adversary *can break* all complexity-based cryptography but *cannot* predict the true random numbers received from the verifier. Also, the adversary's malware can optimize  $C_{m,t}$ 's code on-the-fly and at *no cost*; e.g., without being detected by the verifier. Furthermore, the adversary can output the result of a different computation that lowers t or m, or both, while attempting to return a correct  $C_{nonce}(M, R)$  result.

<sup>&</sup>lt;sup>1</sup>The verifier is trusted to obtain the correct result  $C_{nonce}(M, R)$  from the execution of  $C_{nonce}$  on a trusted computer, or equivalently a trusted simulator of the trusted computer, having the same configuration as the untrusted system device. Also, optimal time bound t may vary among different computer systems in reality, and hence the trusted verifier obtains it from the trusted computer.

# B. Code Optimality in Adversary Execution

*Concrete-Optimality Background.* Recall that a computation's upper time and space bounds are given by an algorithm for that computation whereas the lower bounds are given by a proof that holds for all possible algorithms for it. An algorithm is space-time optimal if its bounds match the space and time lower bounds of its computation.

Note that a verifier can use neither  $C_{m,t}$  computations that have *asymptotic* lower bounds nor ones that have only theoretical ones; i.e., bounds that cannot be matched by any program, as illustrated below. If C<sub>m,t</sub>'s lower bounds are asymptotic, a verifier can never prove that an adversary is unable to find an algorithm with better concrete bounds, by improving the constants hidden in the asymptotic characterizations. If the verifier measures the computation time against a theoretical lower bound, it returns 100% false positives and renders verification useless. If it measures time against a value that exceeds the theoretical lower bound, it can never prove that an adversary's code couldn't execute faster than the measured time, which renders verification meaningless. If the memory lower bound is theoretical and the adversary can exercise space-time (m-t) trade-offs, a time measurement dilemma may arise again: if m is scaled up to a practical value, t may drop to a theoretical one.

A verifier needs  $C_{m,t}$  algorithms with *concrete* (i.e., nonasymptotic) space-time optimal bounds in realistic models of computers; e.g., models of general ISAs, caches and virtual memory, and instruction execution that accounts for I/O and interrupts, multiprocessors, pipelining. If such algorithms are available, the only verifier challenge is to achieve precise space-time measurements, which is an engineering, rather than a basic computation complexity, problem; viz., Section VI. In practice, finding such C<sub>m,t</sub> algorithms is far from a simple matter. For example, in Word Random Access Machine (WRAM) models, which are closest to real computers (e.g., Appendix A), the lower bounds of even simple computations such as static dictionaries are asymptotic even if tight [1], [60]. For more complex problems, such as polynomial evaluation, lower bounds in WRAM have been purely theoretical. That is, they have been proved in Yao's cell (bit) probe model [91], where only references to memory cells are counted, but not instruction execution time. Hence, a WRAM program can never match these lower bounds<sup>2</sup>; see *Related Work*, Section VIII.

Concretely optimal algorithms exist for some classic problems in computation models that are limited to very few operations; e.g., Horner's rule for polynomial evaluation. However, lower bounds in such models do not hold in a WRAM model with a general ISA or a real processor. For instance, lower bounds for integer *gcd* programs obtained using integer division (or *exact division* and *mod* [57]) can be lowered in modern processors where an integer division by a known constant can be performed much faster by integer multiplication [34], [39]; also a right shift can replace division by a power of two. Furthermore, a  $C_{m,t}$  program must retain its optimality when *composed* with system code; e.g., initialization and *I/O* code. Its lower bounds must not be invalidated by the composition.

Adversary execution. Most optimality results assume honest execution of  $C_{m,t}$  code. An execution is honest if the  $C_{m,t}$  code is fixed before it reads any variables or input *nonce*, and returns correct results for all inputs. Unfortunately, the optimality in honest execution does not necessarily hold in *adversarial* execution since an adversary can change  $C_{m,t}$ 's code both before and after receiving the *nonce*, or simply guess the  $C_{nonce}(M, R)$  result without executing any instructions. For example, the adversary can encode a small *nonce* into immediate address fields of instructions to save register space and instruction execution. More insidiously, an adversary can change  $C_{m,t}$ 's code and *nonce* to that of  $C'_{m',t'}$  and *nonce'* where  $(C'_{nonce'}, M', R') \neq (C_{nonce,}, M, R)$ , such that  $C'_{nonce'}(M', R') = C_{nonce}(M, R)$  and t' < t, m' = m or t' = t, m' < m or t' < t, m' < m. If the adversary can output correct result  $C'_{nonce'}(M', R')$  with only low probability over the choices of *nonce*, we say that result  $C_{nonce}(M, R)$  is *unpredictable*. Otherwise, the adversary wins.

The adversary can also take advantage of the optimal *code composition* with initialization and *I/O* programs. For instance, if the input of  $C_{m,t}$ 's variables and *nonce* requires multiple packets, the adversary can pre-process input in early packet arrivals and circumvent the lower time and/or space bounds; viz., end of Section III for an example. Also, in a multi-device system, a device can perform part of the computation of another device and help the latter undetectably circumvent its optimal bounds, as illustrated below.

# C. Verifier Protocol Atomicity in Adversary Execution

The verifier's protocol begins with the input into the system and ends when the verifier checks the system's output; i.e., result-value correctness and timeliness. Protocol atomicity requires integrity of control flow across the instructions of the verifier's protocol with *each* system device; i.e., each device controller and the (multi)processor(s) of the chipset. Asynchronous events, such as future-posted interrupts, hardware breakpoints on instruction execution or operand access [47], and inter-processor communication, can violate control-flow integrity *outside* of  $C_{m,t}$ 's code execution. For instance, malware instructions in initialization code can post a future interrupt before the verifier's protocol begins execution. The interrupt could trigger *after* the correct and timely  $C_{nonce}(M, R)$ result is sent to the verifier, and its handler could undetectably corrupt the system state [52]. Clearly, optimality of  $C_{m,t}$ code is insufficient for control-flow integrity. Nevertheless, it is necessary: otherwise, a predictable  $C_{nonce}(M, R)$  result would allow time and space for an *interrupt-enabling* instruction to be executed undetectably.

Verifiable control flow. Instructions that disable asynchronous events must be executed before the  $C_{m,t}$  code. Their execution inside  $C_{m,t}$  code would violate optimality bounds, and after  $C_{m,t}$  would be ineffective: asynchronous events could trigger during the execution of the last instruction. However, verification that an instruction is located before  $C_{m,t}$  code in memory (e.g., via computing digital signatures/MACs over the code) does *not* guarantee the instruction's executing  $C_{m,t}$ 's code. Hence, verification must address the apparent cyclic dependency: on the one hand, the execution of the event-disabling instructions before  $C_{m,t}$  code requires control-flow integrity, and on the other, control-flow integrity requires the execution of those instructions before  $C_{m,t}$  code.

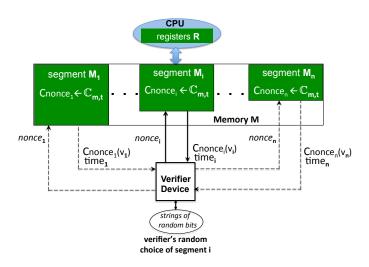

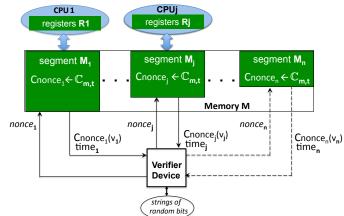

Concurrent-transaction order and duration. Let a system comprise c connected devices, where device i has random

<sup>&</sup>lt;sup>2</sup>The irrelevance of the cell-probe model *in practice* has not escaped complexity theorists: "the true model is the [W]ord RAM, but the bitprobe model is sometimes interesting as a mathematical curiosity [68]."

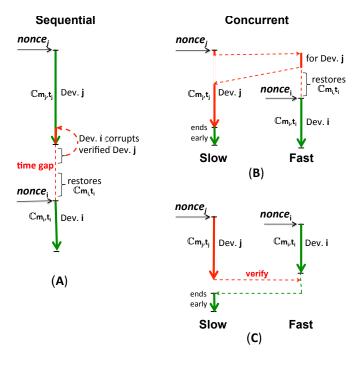

Fig. 1: Sequential and Concurrent Transaction Execution

access memory  $M_i$  and processor registers set  $R_i$ . Assume for the moment that space-time optimal  $C_{m_1,t_1},\ldots,C_{m_e,t_e}$ programs exist and that the control-flow integrity of the verifier's protocol is individually verifiable for each device *i*. Then the verifier protocol must be *transactional*: either *all*  $C_{nonce_i}(M_i, R_i)$  result checks pass or the verification fails. In addition, it must prevent two security problems.

First, the protocol must prevent a time gap between the end of the  $C_{m_j,t_j}$ 's execution and the beginning of  $C_{m_i,t_i}$ 's,  $i \neq j$ . Otherwise, a time-of-check-to-time-of-use (TOCTTOU) problem arises. A malicious yet-to-be-verified device controller can perform an unmediated peer-to-peer I/O transfer [54], [55] to the registers of an already verified controller, corrupt system state, and then erase its I/O instruction from memory before its attestation begins<sup>3</sup>. This is shown in Figure 1(A) and implies that  $C_{m_1,t_1}, \ldots, C_{m_e,t_e}$  must execute *concurrently*: none may end before another starts<sup>4</sup>.

Second, the protocol must assure correct execution *order* and *duration* of  $C_{m_i,t_i}$  programs. That is, the difference between the start times and/or end times of any two programs  $C_{m_i,t_i}$  and  $C_{m_j,t_j}$  must be small enough so that neither device *i* nor *j* can undetectably perform any computation for the other enabling it to lower its bounds and circumvent attestation.

For instance, if the verifier challenges fast device i to start  $C_{m_i,t_i}$  a lot later than slower device j to start  $C_{m_j,t_j}$ , device i can execute some of  $C_{m_j,t_j}$ 's instructions faster, or even act as an *on-board proxy* [53], for j. Then device i can undetectably

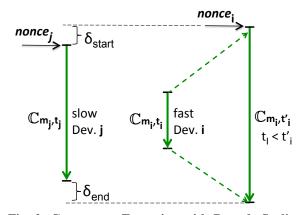

Fig. 2: Concurrent Execution with Bounds Scaling

restore its correct  $\mathbf{C}_{\mathbf{m}_i,\mathbf{t}_i}$  code before its challenge arrives. This is illustrated in Figure 1(B). Or, if  $\mathbf{C}_{\mathbf{m}_i,\mathbf{t}_i}$  ends well before  $\mathbf{C}_{\mathbf{m}_j,\mathbf{t}_j}$  ends, malicious device *j* can act as the verifier and fool attested device *i* into completing  $\mathbf{C}_{\mathbf{m}_j,\mathbf{t}_j}$ 's execution faster. This is illustrated in Figure 1(C). (Recall that, even if attested, devices cannot securely authenticate and distinguish unattested-device requests from verifier's requests and deny them.) Note that slower devices can also help faster ones lower their bounds. Nevertheless, the faster  $\mathbf{C}_{\mathbf{m}_i,\mathbf{t}_i}$  to slower  $\mathbf{C}_{\mathbf{m}_j,\mathbf{t}_j}$ execution order [53] helps ensure that start-time and end-time differences are small enough; e.g., see small differences  $\delta_{start}$ and  $\delta_{end}$  in Figure 2.

Scalable bounds. Given an optimal  $C_{m,t}$  program, one must be able to obtain other optimal  $C_{m_i,t_i}$  programs from it, where  $m_i > m$ ,  $t_i > t$ . Furthermore, given an optimal  $C_{m_i,t_i}$  program for a fast device *i*, one must be able to obtain an optimal program  $C_{m_i,t'_i}$  for it, where time bound  $t'_i \ge \max(t_i), i = 1, \ldots, c$ , independent of  $m_i$ ; see Figure 2. This is intended to prevent the on-board proxy attacks as described above. Neither scaling is obvious.

For example, an intuitive scaling of  $\mathbf{C}_{\mathbf{m},\mathbf{t}}$  to  $\mathbf{C}_{\mathbf{m}_i,\mathbf{t}_i}$  might copy  $\mathbf{C}_{\mathbf{m},\mathbf{t}}$  code  $k \geq \lfloor m_i/m \rfloor$  times in  $M_i$  and then challenge the k optimal copies sequentially; and the scaling from  $C_{m_i,t_i}$ to  $\mathbf{C}_{\mathbf{m}_i,\mathbf{t}'_i}$  might execute  $\mathbf{C}_{\mathbf{m}_i,\mathbf{t}_i}$  on  $k' \geq \lfloor t'_i/t_i \rfloor$  nonces. Neither achieves optimal bounds in adversary execution. Consider the second scaling; the first has similar drawbacks. The k'executions  $C_{nonce_0}(M_i, R_i), \ldots, C_{nonce_{k'-1}}(M_i, R_i)$  must be linked to avoid exploitable time gaps, as noted above. If linking is done by the verifier,  $C_{nonce_i}(M_i, R_i)$ 's code cannot end its execution until it inputs the next nonce,  $nonce_{i+1}$ , from the verifier [53]. Then  $C_{m_i,t_i}$  can no longer be optimal, since the variable input-synchronization delays in  $C_{m_i,t_i}$  invalidate the optimal  $t_i^5$ . If the synchronization buffers  $nonce_{i+1}$ , optimal  $m_i$  also becomes invalid. The alternate linking whereby  $nonce_{j+1} = C_{nonce_j}(M_i, R_i)$  is inadequate since nonces are no longer random, or even pseudo-random [47], [77].

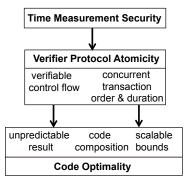

Figure 3 summarizes the relationships among requirements for RoT establishment on an untrusted system. The engineering requirements for *time-measurement security* and a new mechanism that satisfies them are presented in Section VI.

<sup>&</sup>lt;sup>3</sup>Powering off all *stateful* devices and then powering them individually to perform one-at-a-time verification is inadequate because some (e.g., chipset) devices cannot be powered-off without system shutdown. The TOCTTOU problem is still *not* solved because malicious firmware can still corrupt already verified devices in the time gap between device power-on and attestation start.

<sup>&</sup>lt;sup>4</sup>TOCTTOU attacks generalize to remote attestation in networks [22], [27]: a yet-to-be-attested host can reinfect an already-attested host and then reboot itself to a clean software copy before its attestation. Reinfection is possible because attestation does not guarantee correctness of the attested software [67]. *Duqu* 2 illustrates similar malware mobility [42].

<sup>&</sup>lt;sup>5</sup>Synchronization delays for  $nonce_{j+1}$  input in a  $checksum_j$  computation on a network interface card (Netgear GA 620) can be as high as 0.4t with a standard deviation of about 0.0029t; see [53], Sections 5.4.2-5.4.4.

Legend: ----> denotes a dependency

# Fig. 3: RoT Establishment on an Untrusted System

D. Satisfying the requirements – Solution Overview

Individually, the two properties presented below are necessary but insufficient to satisfy the  $C_{m,t}$  requirements. However, jointly they do satisfy all of them.

1. *k-independent (almost) universal hash functions.* The soundness of the verifier's result-value check requires that  $C_{m,t}$  is second pre-image free in a one-time evaluation. That is, no adversary can find memory or register words whose contents differ from the verifier's choice and pass its check, except with probability close to a random guess over *nonces.* Also, inputting the  $C_{m,t}$  variables and *nonce* into an untrusted device must use a small constant amount of storage. *k*-independent (almost) universal hash functions based on polynomials satisfy both requirements. Their memory size is constant for constant *k* [16], [65] and they are second pre-image free. We introduce the notion of *randomized polynomials* to construct such functions for inputs of  $d+1 \log p$ -bit words independent of *k*; i.e., degree *d* polynomials over  $Z_p$  with *k*-independent, uniformly distributed coefficients; see the Corollary in Section IV-D.

2. Optimal polynomial evaluation. The soundness of the verifier's result-timeliness check requires a stronger property than second pre-image freedom. That is, no computation  $C'_{m',t'}$  and nonce' exists such that  $C'_{nonce'}(M', R') = C_{nonce}(M, R)$  and either one of its bounds, or both, are lower than  $C_{m,t}$ 's in a one-time cWRAM evaluation, except with probability close to a random guess over nonces. Concrete space-time optimality of randomized polynomials in adversary evaluation on cWRAM yields this property; viz., Section IV-D. Its proof is ultimately based on a condition under which a Horner-rule program for polynomial evaluation is uniquely optimal in an honest one-time cWRAM evaluation; see Theorem 1 below.

Why are these combined properties sufficient for RoT establishment? Randomized polynomials enable a verifier to check the *integrity of control flow* in the code it initializes on an untrusted cWRAM device (Theorem 6). In turn, this helps implement *time-measurement security*; viz., Section VI. They also assure bounds scalability<sup>6</sup>, which enables the verifier to satisfy the transaction *order* and *duration* requirement and leads to the establishment of malware-free states on a multidevice system (Theorem 7). Finally, the verifier uses ordinary

universal hash functions to establish RoT in malware-free states (Theorem 8).

# III. FOUNDATION: OPTIMAL POLYNOMIAL EVALUATION

In this section we provide the condition under which a Horner-rule program for polynomial-evaluation is uniquely optimal in the concrete WRAM (cWRAM) model, which we use for proving the optimality of randomized-polynomial evaluation in Section IV. We begin with a brief overview of the cWRAM model and illustrate the challenges of proving optimality of universal hash functions in it. A detailed description of cWRAM is in Appendix A.

## A. Overview of the cWRAM model

The cWRAM model is a concrete variant of Miltersen's practical RAM model [60]; i.e., it has a constant word length and at most two operands per instruction. It also extends the practical RAM with higher-complexity instructions (e.g., mod, multiplication), as well as I/O instructions, special registers (e.g., for interrupt and device status), and an execution model that accounts for interrupts. The cWRAM includes all known register-to-register, register-to-memory, and branching instructions of real system ISAs, as well as all integer, logic, and shift/rotate computation instructions. In fact, any computation function implemented by a cWRAM instruction is a *finite-state* transducer; see Appendix A. (The limit of two operands per instruction is convenient, not fundamental: instructions with higher operand arity only complicate optimality proofs.) All cWRAM instructions execute in unit time. However, floatingpoint instructions are not in cWRAM because, for the same data size, they are typically twice as slow as the corresponding integer instructions in latency-bound computations; i.e, when one instruction depends on the results of the previous one, as in the Horner-rule step below. Thus they cannot lower the concrete space-time bounds of our integer computations. Likewise, non-computation instructions left out of cWRAM are irrelevant for our application.

Like all real processors, the cWRAM has a fixed number of registers with distinguished names and a memory that comprises a finite sequence of words indexed by an integer. Operand addressing in memory is immediate, direct and indirect, and operands comprise words and bit fields.

## B. Proving optimality of universal hash functions in cWRAM

The immediate consequence of the constant word length and limit of two single-word operands per instruction is that any instruction-complexity hierarchy based on *variable* circuit fan-in/fan-out and depth collapses. Hence, lower bounds established in WRAM models with *variable* word length and number of input operands [1], [60], [65] and in branchingprogram models [56] are irrelevant in cWRAM. For example, lower bounds for universal hash functions show the necessity of executing multiplication instructions [1], [56]. Not only is this result unusable in cWRAM, but proving the necessity of any instruction is made harder by the requirement of unit-time execution for all instructions.

In contrast, concrete space-time lower bounds of cryptographic hash functions built using circuits with *constant* fanin, fan-out, and depth [3], [4] would be relevant to cWRAM computations. However, these bounds would have to hold in adversary execution, which is a significant challenge, as seen in Section II-B. Even if such bounds are eventually found,

$<sup>{}^{6}</sup>k$ -independent universal hash functions with *constant time* bounds and very good *space-time trade-offs* exist in a standard WRAM model [17]. However, these bounds aren't (concretely) optimal and don't allow *independent* time-bound scalability. Hence these functions are impractical for this application.

these constructions allow only bounded adversaries and hence would not satisfy our goal of unconditional security.

Since we use polynomials to construct k-independent (almost) universal hash functions, we must prove their concrete optimality in cWRAM evaluations. However, all concrete optimality results for polynomial evaluation are known *only* over infinite (e.g., rational) fields [12], and the gap between these bounds and the lower bounds over finite fields (e.g.,  $\mathbf{Z}_{\mathbf{p}}$ ) is very large [43]. Furthermore, optimality is obtained using only two operations (i.e.,  $+, \times$ ) and cannot hold in computation models with large instruction sets like the cWRAM and real processors. We address these problems by adopting a complexity measure based on *function locality* [60], which enables us to distinguish between classes of unit-time computation instructions, and by providing an evaluation condition that extends the unique optimality of Horner's rule to cWRAM.

## C. Unique optimality of Horner's rule in cWRAM

*Horner's Rule.* Let p be a prime. Polynomial  $P_d(x) = a_d \times x^d + a_{d-1} \times x^{d-1} + \dots + a_1 \times x + a_0 \pmod{p}$ is evaluated by Horner's rule in a finite field of order p as  $P_d(x) = (\dots (a_d \times x + a_{d-1}) \times x + \dots + a_1) \times x + a_0 \pmod{p}$ .

Horner-rule step and programs. A program that evaluates  $a_i \times x + a_{i-1} \pmod{p}$  as a sequence of four instructions integer multiplication (·), mod p, integer addition (add), mod p in cWRAM, or  $mod(add(mod(\cdot(a_i, x), p), a_{i-1}), p)$  in infix notation, is called the Horner-rule step. If arithmetic is in  $mod \ 2^{w-1}$  where w - 1 bits represent an unsigned integer value of a w-bit word, the Horner-rule step<sup>7</sup> simplifies to the multiply-add sequence; i.e.,  $add(\cdot(a_i, x), a_{i-1})$ .

A cWRAM loop that executes a Horner-rule step d times to evaluate  $P_d(x)$  is a Horner-rule *program*. Note that there may be multiple encodings of a Horner-rule program that evaluate  $P_d(x)$  in the same space and time.

*Initialization.* If  $p < 2^{w-1}$ , the initialization of a Hornerrule program is a cWRAM structure of d + 11 storage words comprising 6 instructions (i.e., 4 for a Horner-rule step and 2 for loop control) and d + 5 data words; i.e., d,  $a_i(0 \le i \le d)$ , x, p, and output z. If arithmetic is mod  $2^{w-1}$ , the structure has d + 8 storage words; i.e., 4 instructions and d + 4 words.

One time, honest evaluation. Polynomial  $P_d(x)$  is evaluated one time if nothing is known about coefficients  $a_i$  and input x before the evaluation starts; i.e.,  $a_i$  and x are variables. The evaluation of  $P_d(x)$  is honest if its program code is fixed before constants are assigned to variables  $a_i$  and x (i.e., before constants are input and initialized in cWRAM memory) and returns correct results for all inputs. In a dishonest (e.g., adversarial) evaluation, program code can be changed after xor any  $a_i$  become known; e.g., if x = 0,  $P_d(0) = a_0$  can be output without code execution.

**Theorem 1.** Let

$$w > 3$$

be an integer,  $2$

a prime, and  $P_d(\cdot) = \sum_{i=0}^d a_i \times x^i \pmod{p}$  a polynomial over

$\mathbf{Z}_{\mathbf{p}}$ . The honest one-time evaluation of  $P_d(x)$  by a Horner-rule program is *uniquely space-time optimal* whenever the cWRAM execution time and memory are simultaneously minimized; i.e., no other programs can use fewer than both d+11 storage words and 6d time units after initialization.

The proof of this theorem and of all others are in *Appendix B*. Briefly, since a Horner-rule program provides the upper bounds, we only need to prove the lower bounds that match them in cWRAM. To prove the lower bounds, we use finite field properties, linear polynomials over  $Z_p$ , locality-based cWRAM instruction complexity, and the two-operand per instruction limit. First, we show that a four-instruction Horner-rule step is optimal when the cWRAM evaluation space and time for linear polynomials are simultaneously minimized. Then, we use the facts that the evaluation is one-time and honest to show that a Horner-rule step is uniquely optimal. Finally, we define a polynomial, and show that its evaluation requires a unique two-instruction loop-control sequence that must iterate *d* times over the Horner-rule step.

A similar proof holds over  $\mathbf{F}_{\mathbf{q}}$  when q > 2 is a prime power. To illustrate, we outline it for the important case  $q = 2^{w-1}$ . Here the Horner-rule program needs only d + 8 words and 4d time units after initialization.

Theorem 1 answers A. M. Ostrowski's 1954 questions regarding the optimality of Horner's rule [12] in a realistic model of computation. However, both bounds t = 6d and m = d+11 depend on d, and thus t cannot scale independently of m. If t needs to be large, d becomes large. Hence not all d+1 coefficients of  $P_d$  could always be input at the same time; e.g., in one packet. This would enable an adversary's code to pre-process the coefficients that arrive early and circumvent the optimal bounds; e.g., with pre-processing, the lower bound for  $P_d$ 's evaluation drops from d to (d+1)/2 multiplications [72].

# IV. RANDOMIZED POLYNOMIALS AND MALWARE FREEDOM

In this section we define a family of *randomized polynomials*, prove their space-time optimality in adversary evaluation on cWRAM (Theorem 5), and show that they have stronger collision-freedom properties than *k*-independent (almost) universal hash functions in cWRAM (Corollary). These properties enable the verifier to establish control-flow integrity on a single device (Theorem 6), and scale bounds for correct transaction order and duration in a multi-device untrusted system. This helps establish malware-free states (Theorem 7).

# A. Randomized Polynomials – Definition

Let p be prime and d > 0, k > 1 integers. A degree-d polynomial over  $\mathbb{Z}_p$  with k-independent (e.g., [16]), uniformly distributed coefficients  $s_i$

$$P_{d,k}(\cdot) = s_d \times x^d + \dots + s_1 \times x + s_0 \pmod{p},$$

is called the (d, k)-randomized polynomial<sup>8</sup>.

If  $v_d, \ldots, v_0 \in \mathbf{Z}_{\mathbf{p}}$  are constants independent of  $s_i$  and x, and  $\oplus$  is the bitwise *exclusive-or* operation, then polynomial

$$H_{d,k}(\cdot) = (v_d \oplus s_d) \times x^d + \dots + (v_1 \oplus s_1) \times x + (v_0 \oplus s_0) \pmod{p}$$

is called the *padded*<sup>9</sup> randomized polynomial.

Each padding constant  $v_i$  will be used to represent the least significant log p bits of a memory word i or of a special

$<sup>^{7}</sup>$ In many processors, this is implemented by a single *three-operand* multiply-accumulate instruction.

<sup>&</sup>lt;sup>8</sup>Our notion of *randomized polynomial* differs from Tarui's [85] as we cannot input variable numbers (i.e., d + 1) of random coefficients.

$<sup>^9</sup>$ Of course, other padding schemes not based on the  $\oplus$  operation exist, which preserve the *k*-wise independence and uniform distribution of the padded coefficients.

processor-state register; whereas the k of random numbers (which generate the  $s_i$ ) will fill the least significant log p bits of all general-purpose processor registers; e.g., see the device initialization in Section IV-E1 below.

Theorem 2 below shows that  $H_{d,k}(\cdot)$  is second pre-image free, has uniform output, and is k-independent. Everywhere below,  $\stackrel{\$}{\leftarrow}$  denotes a uniform random sample.

**Theorem 2.** Let p > 2 be a prime and  $u \in \mathbf{Z}_{p}$  a constant.

1.

$$Pr[x \stackrel{\$}{\leftarrow} \mathbf{Z}_{\mathbf{p}}, \exists y \in \mathbf{Z}_{\mathbf{p}}, y \neq x : H_{d,k}(y) = H_{d,k}(x)$$

$\leq \frac{1}{(p-1)}$

2.  $Pr[x \stackrel{\$}{\leftarrow} \mathbf{Z}_{\mathbf{p}} : H_{d,k}(x) = u] = \frac{1}{p}$

3.  $H_{d,k}(\cdot)$  is k-independent.

The proofs of parts 1 and 2 follow from two notable facts. First, let x, m be positive integers. If gcd(x,m) = 1, then equation  $\alpha \cdot x = y \pmod{m}$  has a unique solution mod m. Hence, for all  $y \in \mathbf{Z}_{\mathbf{p}}$  and  $x \in \mathbf{Z}_{\mathbf{p}}^+$  there exists a unique  $\alpha$  such that  $y = \alpha \cdot x \mod p$ , and thus  $H_{d,k}(y) - H_{d,k}(x)$  becomes a univariate polynomial in x. Second, any univariate polynomial over  $\mathbf{Z}_{\mathbf{p}}$  whose free coefficient is uniformly distributed and independent of input x has uniform output in  $\mathbf{Z}_{\mathbf{p}}$  when evaluated on a uniform, random x. For part 3, we evaluate  $H_{d,k}(\cdot)$ at k distinct points and obtain a system of k linear equations with d + 1 unknowns  $v_i \oplus s_i$ , k of which are independent. We fix any d - k + 1 unknowns, evaluate their terms, and obtain a system of k linear equations that has a unique solution. Now the independence result follows by definition [90].

Below we define the k-independent uniform elements  $s_i$  for a family of randomized polynomials **H** in the traditional way [16], [90]. We use family **H** in the rest of this paper.

**Family H.** Let p > 2 be a prime and  $r_j, x \stackrel{\$}{\leftarrow} \mathbf{Z}_p$ . Let  $v = v_d, \ldots, v_0, v_i \in \mathbf{Z}_p$ , be a string of constants independent of  $r_j$  and x. Family **H** is indexed by tuples  $(d, r_0, \ldots, r_{k-1}, x)$  denoted as (d, k, x) below.

$$\mathbf{H} = \{ H_{d,k,x}(\cdot) \mid H_{d,k,x}(v) = \sum_{i=0}^{d} (v_i \oplus s_i) \times x^i \pmod{p}, \\ s_i = \sum_{j=0}^{k-1} r_j \times (i+1)^j \pmod{p} \},$$

where  $v_i \oplus s_i$  is represented by a *mod* p integer.

Note that  $H_{d,k,x}(\cdot) \in \mathbf{H}$  has properties 1 and 2 of  $H_{d,k}(\cdot)$ in Theorem 2 in a *one-time* evaluation on  $x \stackrel{\$}{\leftarrow} \mathbf{Z}_{\mathbf{p}}$ . The proof of its k-independence is similar to that of part 3.

Notation. For the balance of this paper, p is the largest prime less than  $2^{w-1}$ , w > 4. The choices made for the random uniform selection of nonce  $H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}$  are denoted by  $S = \{r_j, x \stackrel{\$}{\leftarrow} \mathbf{Z}_{\mathbf{p}}, 0 \le j \le k-1\}$ .

# B. Code optimality in honest evaluation

In this section, we prove the optimal space-time bounds in a *honest* one-time evaluation of  $H_{d,k,x}(\cdot)$ . The only reason we do this is to set the bounds an adversary must aim to beat.

Let  $Horner(H_{d,k,x}(\cdot))$  denote a *Horner-rule program* for the honest one-time evaluation of  $H_{d,k,x}(\cdot) \in \mathbf{H}$  on input string v. That is,  $Horner(H_{d,k,x}(\cdot))$  is implemented by a nested cWRAM loop using the recursive formula  $z_{i-1} = z_i \times x + (v_{i-1} \oplus s_{i-1})$ , where  $z_d = v_d \oplus s_d$ ,  $z_0 = H_{d,k,x}(v)$ ,  $1 < i \leq d$ . (We omit the correctness proof of the Horner loop invariant since it's a simple exercise.) Both the outer loop  $\sum_{i=0}^{d} (v_i \oplus s_i) \times x^i \pmod{p}$  and the inner loop  $s_i = \sum_{j=0}^{k-1} r_j \times (i+1)^j \pmod{p}$  are Horner-rule programs.

Upper bounds. We show that the upper bounds are m = k + 22 storage words and t = (6k - 4)6d execution time units in cWRAM, after variable initialization. By Theorem 1, the inner and the outer loops of  $Horner(H_{d,k,x}(\cdot))$  can be implemented by 6 instructions each. For each of coefficient,  $v_i \oplus s_i$ , 2 instructions are sufficient whenever word indexing in v is sequential; i.e, an *addition* for indexing in v and an *exclusive-or*. The *addition* is sufficient when  $d+1 \le |v|$ , where |v| is the number of words comprising memory M and the special processor registers. If d + 1 > |v|, indexing in v also requires a mod |v| instruction.

Modular indexing in v increases the instruction bound by 1 but does not affect the concrete optimality proofs since fewer instructions cannot simulate memory addressing in cWRAM. Furthermore, indexing to access a special processor register (e.g., asynchronous event status bits) contained in v assumes that the register is mapped in physical memory. When it isn't, accessing it via its index in v would require a couple of extra instructions. Again, these instructions would only insignificantly increase the memory and time bounds, but not affect their optimality. Thus, for simplicity of exposition and without loss of generality, we assume coefficient padding requires only 2 instructions. Hence, 14 instructions comprising 2 nested 6-instruction loops and the 2 instructions for computing a coefficient  $v_i \oplus s_i$  are sufficient. Thus,  $Horner(H_{d,k,x}(\cdot))$ 's time bound is t = [6(k-1)+2]6d = (6k-4)6d time units.

By the definition of family **H**, the operands of these instructions are evident; i.e., k + 8 data words comprising the  $H_{d,k,x}(\cdot)$ 's index in **H**, namely  $(d, r_0, \ldots, r_{k-1}, x)$ , degree k-1, index i+1, coefficient  $s_i$ , modulus p, output  $z = v_d \oplus s_d$ , and  $v_i$ 's word index in v. Thus k + 8 data words and 14 instruction words, or k+22 (general-purpose processor register and memory) words, is  $Horner(H_{d,k,x}(\cdot))$ 's space bound.

Lower bounds. The upper space-time bounds of  $H_{d,k,x}(\cdot)$ are unaffected by the excess memory and register space required by the programs for processor-state (i.e., special processor register) initialization, I/O, and general-purpose register initialization (Init) in cWRAM; see Section IV-E1. However, excess space prevents us from using Theorem 1 to prove the lower bounds since the execution space is no longer minimized. To avoid this technical problem, we assume these programs are space-optimal and memory M contains only the additional k+22 words. We also take advantage of the fact that an honest program does not surreptitiously modify the settings of the special processor registers after its code is committed. The above assumption is only used to simplify the concreteoptimality proof for the honest evaluation of  $H_{d,k,x}(\cdot)$ . It is unnecessary for the optimality proof of  $Horner(H_{d,k,x}(\cdot))$ code in adversarial evaluation; see Section IV-C. There we use the collision-freedom properties of  $H_{d,k,x}(\cdot)$  in cWRAM (e.g., Corollary, Section IV-D) and its uniform distribution of output, which we can avoid here thanks to the assumption made.

**Theorem 3 (Optimality in Honest Evaluation).** Let M comprise space-optimal processor-state initialization, I/O, and

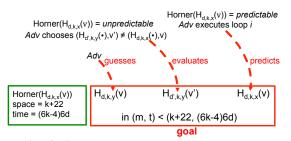

Fig. 4: Adversary goal and strategy space

Init code, and k + 22 words. The honest one-time evaluation of  $H_{d,k,x}(\cdot)$  on v by  $Horner(H_{d,k,x}(\cdot))$  is optimal whenever the cWRAM execution time and memory are simultaneously minimized; i.e., no other programs can use both fewer than k+22 storage words and (6k-4)6d time units after initialization.

The proof of this theorem follows from Theorem 1, k-independence, and honest one-time evaluation.

# C. Code optimality in adversary evaluation

Adversary Goal. By Theorem 3, the adversary's goal is to output  $H_{d,k,x}(v)$  using only m words of storage and time t such that at least one of the lower bounds is lowered; i.e., m < k+22 and t = (6k-4)6d, or m = k+22 and t < (6k-4)6d, or m < k+22 and t < (6k-4)6d. We denote this goal by (m,t) < (k+22, (6k-4)6d).

Strategy Space. We partition the adversary's strategy space into mutually exclusive cases 1 - 3 below, which s/he can select at no cost, and bound the probability of success in each case. These cases are summarized in Figure 4.

1. Guess  $H_{d,k,x}(v)$ . The adversary predicts  $H_{d,k,x}(v)$  independent of nonce  $H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}$  and v; i.e., the prediction is a constant relative to the random choices made in  $H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}$ . Hence, the probability of adversary's success in a one-time evaluation within bounds (m,t) is  $\frac{1}{p}$ , by Theorem 2-2.

For any evaluation that depends on *nonce*  $H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}$ , the adversary must execute a program which inputs at least one of the random choices y made by  $H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}$ , or a function thereof; e.g.,  $y \in \{x, r_j, 0 \le j < k\}$ ,  $y = s_d$ . The choice of program instructions depends on whether  $Horner(H_{d,k,x}(v))$ is predictable: either the adversary executes at least one Horner-rule step (i.e., at least one outer loop execution) and then outputs the result prediction or s/he executes an entirely different instruction sequence in (m, t).

2. Horner $(H_{d,k,x}(v))$  is unpredictable. In this case, the adversary does not execute any Horner-rule step. Instead, s/he chooses a sequence of cWRAM instructions which inputs at least a  $y \in \mathbf{Z}_{\mathbf{p}}$  that depends on nonce  $H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}$ , executes the sequence, and outputs its result in  $\mathbf{Z}_{\mathbf{p}}$ . That is, the chosen sequence evaluates a function  $f_H(\cdot) : \mathbf{Z}_{\mathbf{p}} \to \mathbf{Z}_{\mathbf{p}}$  on an input y and outputs  $f_H(y)$  in (m, t). Its instructions may read and write multiple values in  $\mathbf{Z}_{\mathbf{p}}$ ; e.g., they may read and modify the values of the general-purpose processor registers, and/or those of v. Since  $H_{d,k,x}(v)$  is unknown before  $f_H(y) = H_{d,k,x}(v)$ .

Note that the execution of *any* instruction sequence with input and output in  $\mathbf{Z}_{\mathbf{p}}$  represents the evaluation of a unique polynomial  $Q_{d'}(\cdot)$  of degree  $d' \leq p-1$  on some input y over  $\mathbf{Z}_{\mathbf{p}}$ . This follows from a well-known fact that establishes the

one-to-one correspondence between functions and polynomials  $Q_{d'}(\cdot)$  in finite fields<sup>10</sup>. Hence, the adversary can *always* find a pair  $(Q_{d'}(\cdot), y) \neq (H_{d,k,x}(\cdot), v)$  whose cWRAM evaluation has desired bounds (m,t) < (k+22, (6k-4)6d). To upper bound the probability of adversary's success, we write  $Q_{d'}(\cdot)$ 's coefficients  $a_i$   $(0 \leq i \leq d')$  as  $a_i = s_i \oplus v'_i$  for some  $v' = v'_{d'}, \ldots, v'_0$ , where  $s_i = \sum_{j=0}^{k-1} r_j \times (i+1)^j \pmod{p}$  and  $r_j \stackrel{\$}{\leftarrow} \mathbf{Z_p}$  are the same values used to generate  $H_{d,k,x}(\cdot)$ 's coefficients. If for any index i < d' coefficient  $a_i = 0$ , we set  $v'_i = s_i$ . Thus,  $Q_d(y) \equiv H_{d',k,y}(v')$  and  $(H_{d',k,y}(\cdot), v') \neq (H_{d,k,x}(\cdot), v)$ .

Let  $Adv(H_{d,k,x}(\cdot), v) = H_{d',k,y}(v')$  denote the adversary's choice of polynomial, input v', and evaluation result output in (m, t). We denote event  $[S, Adv(H_{d,k,x}(\cdot), v) = H_{d',k,y}(v') : H_{d',k,y}(v') = H_{d,k,x}(v) | (m,t)]$  succinctly by  $[S : H_{d',k,y}(v') = H_{d,k,x}(v)]$ . Lemma 4 bounds the adversary's probability of success,  $Pr[S : H_{d',k,y}(v') = H_{d,k,x}(v)]$ .

**Lemma 4.** Let  $H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}$  and v be its input. For any one-time choice of  $(H_{d',k,y}(\cdot),v') \neq (H_{d,k,x}(\cdot),v)$ , let the adversary output  $H_{d',k,y}(v')$  in (m,t) < (k+22,(6k-4)6d). Then  $Pr[S: H_{d',k,y}(v') = H_{d,k,x}(v)] \leq \frac{3}{p}$ .

To prove this lemma, we partition all adversary's onetime choices of  $(H_{d',k,y}(\cdot), v')$  into mutually exclusive attack events, given *nonce*  $H_{d,k,x}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H}$  and v. Then we use the definition of family  $\mathbf{H}$ , Theorem 2, and two notable facts. The first is that  $\mathbf{Z}_{\mathbf{p}}^+$  is closed under multiplication. The second is the first fact used in the proof of Theorem 2 above.

3.  $Horner(H_{d,k,x}(v))$  is predictable. Alternatively, the adversary decides that, for the given nonce  $H_{d,k,x}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H}$  and v,  $Horner(H_{d,k,x}(v))$  can be predicted within bounds (m,t). Hence, s/he executes at least one Horner-rule step (i.e., at least one outer loop of  $Horner(H_{d,k,x}(v))$  and then predicts  $H_{d,k,x}(v)$  without completing  $Horner(H_{d,k,x}(v))$ . The bounds goal (m,t) is met:  $m \leq k+22$  and t < (6k-4)6d.

Let us denote the event of adversary's success by  $[S : Adv(Horner(H_{d,k,x}(\cdot), v) = H_{d,k,x}(v) | (m,t)]$ , or succinctly by  $[S : H_{d,k,x}(v) = predictable]$ .

In the proof of Theorem 5 below we show that the bound of  $Pr[S: H_{d,k,x}(v) = predictable]$  is not higher than the bound in Lemma 4. This theorem shows that the concrete optimality requirements of Section II-B are satisfied for a  $Horner(\cdot)$  program with bounds m = k + 22, t = (6k - 4)6d, which is invoked with  $nonce = H_{d,k,x}(\cdot) \xleftarrow{\$} \mathbf{H}$  on input v. This is summarized in Figure 5.

# Theorem 5 (Optimality in Adversary Evaluation).

In a one-time cWRAM evaluation of  $H_{d,k,x}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H}$  on van adversary can lower either the space or the time bound of  $Horner(H_{d,k,x}(v))$ , or both, with probability at most  $\frac{3}{p}$ .

The proof of this theorem follows from the definition of result (un)predictability in a one-time evaluation, Theorem 2 and the second notable fact used in its proof, Lemma 4, and the definition of family  $\mathbf{H}$ .

<sup>&</sup>lt;sup>10</sup>By L. E. Dickson (1897) and C. Hermite (1854); viz., Lemma 1.1-1.2 [79].

Fig. 5: Optimality of C<sub>m,t</sub> with Family H

## D. Collision Freedom of H in cWRAM

The corollary below shows not only that **H** is a family of k-independent (almost) universal hash functions, but also that an adversary is unable to find a function in  $\mathbb{Z}_{\mathbf{p}}$  whose onetime cWRAM evaluation on an input y collides with  $H_{d,k,x}(v)$  within bounds (m, t) < k + 22, (6k - 4)6d.

## Corollary.

1. **H** is a k-independent (almost) universal hash function family.

2. Let (m,t) < (k+22, (6k-4)6d). For a given one-time evaluation of  $H_{d,k,x}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H}$  on input v in cWRAM,  $\Pr[H_{d,k,x} \stackrel{\$}{\leftarrow} \mathbf{H}, v, \exists f, u \in \mathbf{Z}_{n}: f(u) = H_{d,k,x}(v) \mid (m,t)] \leq \frac{3}{2}$ .

$$\Pr[\Pi_{d,k,x} \leftarrow \mathbf{n}, v, \exists j, y \in \mathbf{Z}_{\mathbf{p}} : j(y) = \Pi_{d,k,x}(v) \mid (m, v)] \leq \frac{1}{N}$$

Part 1 follows by a similar proof as in Lemma 4 and the

Part 1 follows by a similar proof as in Lemma 4, and the k-independence follows along the same lines as the proof of Theorem 2-3. Part 2 follows directly from Theorem 5.

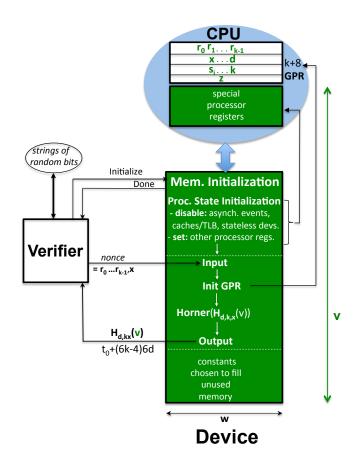

# E. Device Initialization and Atomicity of Verifier's Protocol

1) Device Initialization: Upon system boot, the verifier requests each device's boot loader (e.g., akin to U-boot in Section VII) to initialize the device memory with the verifier's chosen content, as described in steps (i) - (v) below, and then transfer control to the first instruction of the processor-state initialization program. The boot loaders may not contain all and only the verifier's chosen code, and hence are untrusted.

*i) Processor-state initialization.* This is a straight-line program that accesses special processor registers to:

- disable all asynchronous events; e.g., interrupts, traps, breakpoints;

- disable/clear caches, disable virtual memory, TLBs<sup>11</sup>, and power off/disable stateless devices;

Fig. 6: Device Initialization and Verifier Protocol Execution

• set all remaining state registers to chosen values; e.g., clock frequency, *I/O* registers.

When execution ends, the *Input* program follows in straight line.

*ii) Input/Output programs.* The *Input* program busy-waits on the verifier's channel device for input. Once *nonce*  $H_{d,k,x}$  arrives, the *Init* program follows in straight line. The *Output* program sends result  $H_{d,k,x}(v)$  to the verifier after which it returns to busy-waiting in the boot loader for further verifier input.

*iii) Init program.* This is a straight-line program that loads the k random values of nonce  $H_{d,k,x}$  into the general-purpose processor registers so that no register is left unused; e.g., if 16 registers are available, k = 16. Its execution time,  $t_0$ , is constant since k is constant. When execution ends, the  $Horner(H_{d,k,x}(\cdot))$  program follows in straight line.

$iv)Horner(H_{d,k,x}(\cdot))$  program. This comprises 14 instructions whenever the address space is linear in physical memory. When execution ends, the *Output* program follows in straight line and outputs  $H_{d,k,x}(v)$ .

v) Unused-memory initialization. After the initialization steps (i) - (iv) are performed, the rest of the memory M is filled with verifier's choice of constants.

The device initialization and the verifier's protocol with the device are illustrated in Figure 6.

2) Control Flow Integrity: Recall that the verifier's protocol begins with the input of nonce  $H_{d,k,x}$  into a device and

<sup>&</sup>lt;sup>11</sup>Disabling/clearing caches/TLBs prevents an adversary from loading chosen content *before* the timed protocol starts and circumvent time measurements; viz., Sections VI-B and VII.

ends when the verifier checks the device's output.

**Theorem 6 (Verifiable Control Flow).** Let the verifier request a device's untrusted boot loader to initialize its memory, and constant  $t_0$  be the time required by the *Init* program on cWRAM. Let the verifier receive  $H_{d,k,x}(v)$  in  $t_0 + (6k - 4)6d$  time units in response to *nonce*  $H_{d,k,x}$ . Then

a) there exists a verifier choice of instruction encoding and sequencing for the *processor-state initialization*, *Input*, or *Init* programs such that the omission of any instruction execution modifies at least a word of input v to  $Horner(H_{d,k,x}(\cdot))$ ;

b) a control flow deviation in the verifier-protocol code on the device remains undetected with probability at most  $\frac{6}{p}$ .

In the proof of a), we use the fact that a verifier can choose instruction encoding and sequencing for the three programs such that the lower log p bits of their memory words form a unique sequence of distinct words of the input v to  $Horner(H_{d,k,x}(\cdot))$ . For part b) we show that, given the the verifier's choice of instruction encoding and sequencing, any control flow deviation from it requires either a modification of input v or a violation of  $Horner(H_{d,k,x}(\cdot))$ 's bounds, or both. The probability of the former event is bounded by Lemma 4 and of the latter by Theorem 5.

Scalable Bounds. By Theorem 6, the  $Horner(H_{d,k,x}(\cdot))$  code bounds for device *i* must scale from m = k + 22 to  $m_i = k_i + 22$ ,  $k_i > k$ , and from t = (6k - 4)6d to  $t_i = (6k_i - 4)6d_i$ ,  $d_i = |v^i| - 1 > d$ , where  $|v^i|$  is the number of memory and special processor-register words. To scale execution time  $t_i$  for a constant  $k_i$  (and hence  $m_i$ ), the verifier can increase  $d_i$  past constant  $|v^i| - 1$  to whatever value is required by transaction duration. In this case, indexing in  $v^i$  would require an additional  $mod |v^i|$  instruction execution.

3) Concurrent-transaction order and duration: Let a system comprise c devices with the smallest word size of w bits and  $p < 2^{w-1}$ . Let the verifier request an untrusted boot loader to initialize device i with chosen content  $v^i$  as described in Section IV-E1. Then  $Init_i$  initializes the  $k_i$  general-purpose registers on device i in constant time  $t_{0_i}$ . If  $t_{0_j} + t_j$  is the slowest  $Horner(H_{d_j,k_j,x_j}(\cdot))$  execution time on any device's  $v^j$ , then the verifier selects values of  $d_i, k_i$  for the other device nonces  $H_{d_i,k_i,x_i}$  such that  $t_i = t_{0_i} + (6k_i - 4)6d_i$  equals  $t_{0_j} + t_j$ , or exceeds it by a very small amount, to satisfy the duration requirement. Then the verifier's chosen concurrent-transaction order can assure that the start times and end times do not allow malicious devices to circumvent lower bounds.

**Theorem 7 (Malware-free state).** Let a verifier initialize an untrusted *c*-device system to  $v^i$   $(i \in [1, c])$ , where *c* is small; i.e., 10c << p. Then the verifier challenges the devices concurrently in transaction order, with device *i* receiving *nonce*  $H_{d_i,k_i,x_i}$  whose  $t_i$  satisfies the duration requirement. If the verifier receives result  $H_{d_i,k_i,x_i}(v^i)$  at time  $t_i$  for all *i*, the probability that malware survives in a system state is at most  $\frac{9c}{p}$ . If the verifier runs the protocol *n* times, the malwaresurvival probability becomes negligible in *n*; i.e.,  $\epsilon(n) = [\frac{9c}{n}]^n$ .

The proof follows directly from the concurrent transaction order and duration property of the verifier's protocol, Theorem 6, and Lemma 4.

*Example.* For w = 32 and w = 64 bits, the largest primes  $p < 2^{w-1}$  are  $2^{31} - 1$  and  $2^{63} - 25$ . In practice  $c \le 16$  as we rarely encounter commodity computer systems configured

with more than eight CPU cores and eight peripheral-device controllers whose non-volatile memories can be re-flashed with code<sup>12</sup>. For w = 32 (w = 64), the probability of malware survival for n = 1 is less than  $2^{-23}$  ( $2^{-55}$ ), for n = 2 is less than  $2^{-46}$  ( $2^{-110}$ ), etc. Hence, n < 2 is sufficient, in practice.

## V. UNCONDITIONAL ROOT OF TRUST ESTABLISHMENT

Theorem 7 establishes a malware-free, multi-device system state. However, this is insufficient to establish RoT. While the general-purpose registers contain w-bit representations of the k random numbers, the memory and special processor registers of a device comprise w-bit words, rather than the log p-bit fields  $v_{d_i}^i, \ldots, v_0^i$  words, where  $p < 2^{w-1}$  is the largest prime. Hence, a sliver of unaccounted for content exists.

To establish RoT, the verifier can load a *word-oriented* (almost) universal hash function in each malware-free device memory and verify the results they return after application to memory and special processor register content. Note that space-time optimality of these hash functions and verifier's protocol atomicity are unnecessary, since malware-freedom is already established. A pairwise verifier - device<sub>i</sub> protocol checking device memory and special register content is sufficient. Let  $\mathbf{H}_{\mathbf{w}}$  be such a family and V comprise the set of w-bit words of a device's memory and special processor registers.

Fact (e.g., Exercise 4.4 [88]). Let  $q > 2^w$  be a prime,  $|V| = q/2^w$ , and  $a, b, c \stackrel{\$}{\leftarrow} \mathbf{Z}_{\mathbf{q}}$  be the function index of family  $\mathbf{H}_{\mathbf{w}}$ , where  $\mathbf{H}_{\mathbf{w}} = \{H_{a,b,c}(\cdot) \mid w_i \in [0, 2^w), H_{a,b,c}(w_{|V|-1} \dots w_0)$

$$= ((a \times (\sum_{i=0}^{|V|-1} w_i \times c^i) + b) \mod q) \mod 2^w \}$$

is a family of almost universal hash functions, with collision probability of  $2^{-(w-1)}$ . The probability is computed over the choices of  $H_{a,b,c}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H}_{\mathbf{w}}$ .

**Theorem 8 (RoT Establishment)**. Let a verifier establish a malware-free state of a *c*-device system in *n* protocol runs, as specified in Theorem 7. Then let the verifier load  $H_{a_i,b_i,c_i}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H_w}$  on device *i* and check each result  $H_{a_i,b_i,c_i}(M_i)$  received. If all checks pass, the verifier establishes RoT with probability at least  $(1 - \epsilon(n))(1 - c \cdot 2^{w-1})$ , where  $\epsilon(n) = [\frac{9c}{p}]^n$ ; e.g., higher than  $1 - \frac{10c}{p}$  for n = 1.

The proof is immediate by Theorem 7 and the Fact above.

Implementation considerations of the cWRAM model in real processors for suitable choices of prime p are discussed in *Appendix C*.

Secure Initial State. After the verifier establishes RoT, it can load a trustworthy program in the system's primary memory. That program sets the contents of all secondary storage to verifier's choice of content; i.e., content that satisfy whatever security invariants are deemed necessary. This extends the notion of the *secure initial state* to all system objects.

# VI. TIME-MEASUREMENT SECURITY

Past software-based attestation designs fail to assure that a verifier's time measurements cannot be bypassed by an adversary. For example, to account for cache, TLB, and clock

<sup>&</sup>lt;sup>12</sup>Although GPUs have many cores, GPU malware is *cannot* persist, as it cannot survive GPU power-offs/reboots [76] by *processor-state initialization*.

jitter caused primarily by pseudo-random memory traversals by  $C_{m,t}(\cdot)$  computations and large t, typical verifiers' measurements build in some slack time; e.g., 0.2% - 2.6% of t [47], [52], [53], [77]. An adversary can easily exploit the slack time to undetectably corrupt  $C_{m,t}(\cdot)$ 's memory [47], [52]. In this section we show how to counter these threats.

## A. Verifier Channel

The verifier's local channel must satisfy two common-sense requirements. First, the channel connection to any device must not pass through a peripheral device controller that requires RoT establishment. Otherwise, malware on the controller could pre-process some of the computation steps for the verifier's protocol with that device and help it to circumvent the time measurements. Second, the channel's delay and its variation must be small enough so that the verifier time measurements can reliably detect all surreptitious untrusted-system communication with external devices and prevent both *memory-copy* [52] and *remote-proxy* [53] attacks.

We envision a verifier device to be attached to the main system bus via a DMA interface, similar in spirit to that of Intel's Manageability Engine or AMD's Platform Security Processor, but without flaws that would enable an attacker to plant malware in it [63]. These processors can operate independently of all other system components; e.g., even when all other components are powered down [83]. The external verifier could also run on a co-processor connected to the main system bus, similar in spirit to Ki-Mon ARM [51]. In both cases, the verifier would have direct access to all components of the system state. An advantage of such verifiers is that their communication latency and variation of the local channel are imperceptible in contrast with the adversary's network channel.

# B. Eliminating Cache and TLB jitter

To perform deterministic time measurement, it is necessary to eliminate cache/TLB jitter and interprocessor interference, and avoid clock jitter in long-latency computations.

Preventing Cache, Virtual Memory, and TLB use. In contrast with traditional software-based attestation checksums (e.g., [47], [52], [77], [78]), the execution-time measurements of  $Horner(H_{d,k,x}(v))$  is deterministic. Most modern processors, such as the TI DM3730 ARM Cortex-A8 [6], include cache and virtual-memory disabling instructions. Hence, processor-state initialization can disable caches, virtual memory, and the TLB verifiably (by Theorem 6). In addition, the Horner-rule step is inherently sequential and hence unaffected by pipelining or SIMD execution. The only instructions whose execution could be overlapped with Horner-rule steps are the two loop control instructions, and the corresponding timing is easily accounted for in the verifier's timing check.

Preventing Cache pre-fetching. In systems where caches cannot be disabled, the *inherent* sequentiality of  $Horner(H_{d,k,x}(v))$  code and the known locality of the instruction and operand references helps assure that its execution-time measurements are deterministic. However, the adversary's untrusted boot loader could perform undetected cache pre-fetches before the verifier's protocol starts, by selectively referencing memory areas, and obtain better timing measurements than the verifier's; viz., Section VII. To prevent pre-fetching attacks the *processor-state initialization* can *clear caches verifiably* (by Theorem 6), so that *Init* and

$Horner(H_{d,k,x}(v))$  code can commence execution with clean caches. Hence, cache jitter can be prevented.

Alternately, the verifier's processor-state initialization could warm up caches [77] by verifiable pre-fetching. Nevertheless, verifiable cache clearing is often required; e.g., in ARM processors instruction and data caches are not hardware synchronized, and hence they have to be cleared to avoid malware attacks [52]. Furthermore, cache anomalies may occur for some computations where a cache miss may result in a shorter execution time than a cache hit because of pipeline scheduling effects [24]. This makes cache clearing a safer alternative.

## C. Handling clock jitter and inter-processor interference

When  $Horner(H_{d,k,x}(v))$  executes in large memories it can have large latencies; e.g., several minutes. These may experience small time-measurement variations in some systems due to uncorrected random clock jitter at high frequencies [84], and multi-processor interference in memory accesses. These timing anomalies are typically addressed in embedded realtime systems [24]. For such systems, we use a random sequential protocol. This protocol leverages smaller memory segments and the verifiable choice of clock-frequency setting such that random clock jitter becomes unmeasurable by an adversary. It also ensures that different processors access *different* memory segments to eliminate interprocessor interference. The protocol also provides an alternate type of bounds scaling. For example, in controller devices can complete verification concurrently with the first memory segments without having to scale their space-time optimal computations to meet the large time bound of a primary memory verification.

Random Sequential Evaluation. Let  $F = \{f_1, f_2, \ldots, f_n\}$ be a family of n functions and  $K_i \stackrel{\$}{\leftarrow} [1, n], i = 1, \ldots, N$ , be identifiers of their random invocations.  $f_{K_1}, f_{K_2}, \ldots, f_{K_N}$  are evaluated on inputs  $x_1, x_2, \ldots, x_N$ , and  $\bot$  denotes the event that an *invalid* result is returned by a function evaluation. The protocol for the random sequential evaluation of F, namely  $(f_{K_1}(x_1), f_{K_2}(x_2), \ldots, f_{K_N}(x_N))$ , is as follows: 1)  $N = n \cdot \log n$ ; 2) if  $f_{K_i}(x_i) \neq \bot$ , then  $f_{K_{i+1}}(x_{i+1}), 1 \leq i < N$ ; and 3)  $Pr[K_i \stackrel{\$}{\leftarrow} [1, n] : \forall j > i, f_{K_j}(x_j) = y_j \mid f_{K_i}(x_i) = y_i, \cdots, f_{K_1}(x_1) = y_1] = Pr[K_i \stackrel{\$}{\leftarrow} [1, n] : f_{K_j}(x_j) = y_j]$ . The evaluation terminates *correctly* if  $f_{K_i}(x_i) \neq \bot$  for all i, and *incorrectly*, otherwise.

Condition 1) implies that the evaluation invokes *all* randomly selected functions with high probability *at least once* [25], [77]. Condition 2) defines the sequential evaluation rule. Condition 3) implies that the *j*-th function evaluation is independent from the previous i < j evaluations.

Verifier Initialization. Let the verifier request the boot loader to initialize M to n memory segments each comprising processor-state initialization, I/O, Init, and  $Horner(H_{d,k,x}(\cdot))$  programs. Then verifier's boot loader transfers control to the first instructions of the processor-initialization program.

*Verifier Protocol.* Let F be family  $\mathbf{H}$ ,  $f_{K_i}$  be  $Horner(H_{d_i,k_i,x_i}(\cdot))$ , where  $K_i \stackrel{\$}{\leftarrow} [1,n]$ , and  $H_{d_i,k_i,x_i}(\cdot) \stackrel{\$}{\leftarrow}$

Fig. 7: Random Sequential Evaluation Protocol

H; i.e., the random selection of a memory segment<sup>13</sup>. If the random sequential evaluation protocol terminates incorrectly or the termination is untimely, or both, the verifier *rejects*. Otherwise, the verifier *accepts*. This is the verifier's protocol for *the n-segment memory model*. The protocol is illustrated in Figure 7.

Specifically, the verifier writes the values denoting the choice of  $H_{d_i,k_i,x_i}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H}$  separately to each of the *n* memory segments. Furthermore, the verifier's *Output* code is modified so that it returns to the *Input* busy-waiting code after outputting an evaluation result, which transfers to the first instruction of the *Input* code of the next randomly chosen segment. The address of the next segment's *Input* code is provided by the verifier along with the next *nonce*  $H_{d_i,k_i,x_i}(\cdot) \stackrel{\$}{\leftarrow} \mathbf{H}$ .

Note that the size of the segments shown in Figure 7 can vary. Memory M can be initialized with segments that are small enough such that their evaluation time becomes smaller than the round-trip time necessary for a *remote proxy* attack, where the remote proxy is powerful enough to evaluate any randomized polynomial in zero time [53]. Hence, if malware attempts to enlist the help of an adversary of unbounded power to bypass the optimal space-time bounds of all the smallmemory segments, the verifier protocol fails.

In a multiprocessor system where j processors share RAM memory M, the *Init* programs would start the concurrent execution of all j processors in *different* memory segments along with those of the device controllers; see Figure 8. The assignment of segments to processors can be done by selecting j segments at random without replacement from the  $n \ge j$  segments. Thus no two processors or more can interfere in accessing the same segment at the same time.

**Theorem 9 (Malware-free Segmented Memory).** Let a verifier initialize memory M of a (e.g., multiprocessor) device to n segments and perform the verifier's protocol for the

Fig. 8: Processors Accessing Different Memory Segments

segmented memory. If the verifier accepts the result, the device state is malware-free, except with probability at most  $\frac{9n}{p}$ .

The proof of this theorem follows from the definition of the verifier's initialization of memory M including the modified I/O instruction sequences, by the verifier's protocol for the segmented memory model, and by Theorem 6 and Lemma 4.

# VII. PERFORMANCE

In this section, we present preliminary performance measurements for the Horner-rule evaluation of randomized polynomials. The only goal here is to illustrate implementation practicality on a commodity hardware platform. For this reason, we compare these measurements to those of Pioneer – the best-known attestation checksum [77] – on the same hardware configuration [52]. Presenting a study of randomizedpolynomial performance is beyond the scope of this paper.

Our measurements also illustrate the importance to provably clearing (or disabling, when possible) caches for deterministic time measurements. We noticed no timing anomalies due to uncorrected clock jitter in our single-processor configuration for a fairly large memory. This suggests that the random sequential evaluation for large memories (Section VI) may be useful primarily to prevent inter-processor interference.

*Hardware*. Our measurements were done on a Gumstix Overo FireSTORM-P Computer-On-Module (COM), which is the ARM-based development platform for embedded hardware used by Li *et al.* [52]. This gives us an opportunity to compare the performance of Horner's rule for randomized polynomials with that of the Pioneer checksum. This platform features a 1GHz Texas Instruments DM3730 ARM Cortex-A8 32-bit processor and 512MB of DDR SDRAM [86]. The processor has a 32KB L1 instruction cache and a 32KB L1 data cache, both with 16 bytes per cache line. In addition, it also features a 256KB L2 unified cache [6].

Recall that the parameter |M| must reflect the total amount of primary storage in the device. Besides the 512MB of SDRAM, our particular Gumstix also features 64KB of SRAM and also a large address space for device control registers with 5,548 registers. Summing these up as bits, we set |M| to 4,295,669,120.

Software. Our measurements are implemented inside a popular secondary boot loader known as U-Boot, which in a

<sup>&</sup>lt;sup>13</sup>A *non-random* sequential selection would enable malware to take control after a correct and timely result is returned by a memory segment evaluation, modify the memory of an already evaluated segment or prefetch instructions, and then overwrite itself with correct evaluation code before the next input arrives from the verifier.

typical application would be responsible for loading the Linux kernel on the COM. For our purpose, however, we extend U-Boot with measurement capabilities; i.e., U-Boot 2015.04-rc4 is cross-compiled with Linaro gcc 4.7.3.

We implemented Horner's rule for several polynomials in  $\mathbf{Z}_{\mathbf{p}}$ , where  $p = (2^{32} - 5)$  is the largest prime that can fit inside a 32-bit register. Since the DM3730 ARM Cortex-A8 CPU does *not* support the udiv (unsigned integer division) instruction, *gcc* uses the <u>\_\_aeabi\_uidivmod</u> function to emulate division, which is slower than the hardware udiv instruction followed by the mls (integer multiply-and-subtract) instruction to compute the modulus. Nevertheless, an adversary cannot change the emulation since the code image is committed by the second pre-image freedom of randomized polynomials.

The first Horner-rule measurement is for ordinary polynomials; i.e., with constant, rather than k-wise independent, coefficients. This establishes the baseline, which helps calibrate the expected performance loss for increasing the values of k. The performance of Horner rule for a single polynomial of degree 128M covering the entire SDRAM is 11,739ms.

For the measurements of Horner-rule evaluation of randomized polynomials, the k random numbers are stored contiguously in memory. For values of k that match one cache line, namely k = 4, evaluating a polynomial of degree d = 128M (same as the baseline) takes 67, 769ms due to extra memory accesses and added cache contention. However, most modern processors have more than k = 4 and fewer than k = 64registers. Hence, larger values of k would have to be used to ensure that the adversary *cannot* be left with spare processor registers after loading the k random numbers.