#### Fluid:

### Raising the Level of Abstraction for FPGA Accelerator Development Without Compromising Performance

Submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Joseph G. Melber

B.S., Electrical Engineering, University at Buffalo M.S., Electrical and Computer Engineering, Carnegie Mellon University

> Carnegie Mellon University Pittsburgh, PA

> > August 2021

© Joseph G. Melber, 2021 All rights reserved.

#### Acknowledgements

Completing my PhD has been an incredibly meaningful and enriching process. First and foremost, I thank Prof. James C. Hoe for supporting me, guiding me towards interesting research and mentoring me throughout my PhD. James taught me how to think, find the essence of every question and develop an instinct for the truly interesting parts of a research project. I have grown as a researcher and most importantly as a person as a result of your guidance. Thank you.

I want to thank my committee members Prof. Tze Meng Low, Prof. Nathan Beckmann, and Dr. Kermin Elliott Fleming. Their valuable insights, constructive feedback and excellent advice helped me to refine my thesis. All of your perspectives impacted my thesis work and I am very grateful.

I thank my friends and collaborators at CMU. Thank you Siddharth Sahay, Shashank Obla and Zhipeng Zhao for your immeasurable help, research discussions, and friendship. I thank all of James' students that I had the pleasure to work and collaborate with: Gabriel Weisz, Michael Papamichael, Yu Wang, Guanglin Xu and Marie Nguyen. Thank you to all denizens of a-level for making it a great place to work, have lunch, and for your friendships. Thank you Thom Doru Popovici, Anuva Kulkarni, Milda Zizyte, Daniele Spampinato, John Filleau, Mark Blanco, Emily Ruppel, Elliott Binder, Upasana Sridhar and Bari Guzikowski. I have many fond memories of my time at CMU thanks to all of you. I truly appreciate and will miss all of the discussions, lunches and happy hours we had in Pittsburgh. Outside of CMU, I am very thankful for my friends from Buffalo and Pittsburgh for their support and for making graduate school fun.

Thank you to everyone in my family. Graduate school is a lengthy journey and your encouragement has been invaluable to the process. I would like to thank my parents for teaching me the importance of education and hard work, and for their love and support throughout my life. I also thank my in-laws, siblings, grandparents and extended family who have celebrated the highs and motivated me through the lows. I would like to thank my dog and office mate during the COVID-19 pandemic, Moose, who brings me constant

joy and companionship. Lastly, I am truly thankful for my wife, Margaret, for her unconditional love, encouragement and unending support. Without you I would not be who I am today, I love you.

Finally, I would like to thank Intel Corporation for their generous financial and equipment donations in the ISRA grant. I would also like to thank Intel Corporation and VMware Inc for their generous financial donation to and lengthy discussions within the Crossroads 3D FPGA-Academic Research Center.

v

#### Abstract

The unrestricted freedom presented to hardware accelerator developers by the inherently reconfigurable fabric of Field Programmable Gate Arrays (FPGAs) gives rise to highly optimized and efficient architectures. However, correctly navigating this same vast freedom is what makes hardware design difficult. Adding to this challenge, modern FPGAs continue to grow in logic capacity, and offer rich and varied memory and communication interfaces. FPGA accelerator developers need the same ease-of-development support software programmers have come to expect—through abstraction—to manage this complexity.

In current FPGA development flows, the lack of abstractions and proper tooling encouraging composition, encapsulation and code reuse leads to unnecessarily long development cycles. Hardware developers must manually adapt their accelerators for new platforms or, at worst, rewrite them. To address those challenges, so far, FPGA abstractions give disproportionate emphasis to reducing the design effort for algorithmic processing kernels rather than to the memory and communication architecture side of the design task. Designers are asked to build all of the datapaths for buffering, data movements, and external interfaces, as well as the state machines to coordinate these datapath activities. Bus-level integration and design abstractions remain the state-of-the-art for designing memory and communication infrastructure. Furthermore, such datapaths are often ad-hoc efforts and are not generally reusable.

This thesis presents FLUID, an FPGA-aware modular design methodology that enables higher levels of abstraction for memory, communication and system architecture. Fluid draws inspiration from service-oriented architecture concepts developed for cloud computing to separate functionality from implementation in hardware design. The Fluid design methodology encourages a decoupled design paradigm where accelerator developers are relieved of memory and communication logic within their modules. Fluid's service abstraction begins at a module's boundary. It defines a clean interface that logically decouples components in a design and enables flexible infrastructure implementations outside of the module's scope. This design methodology reduces FPGA hardware development cost by removing infrastructure from a designer's modules and enabling them to architect their accelerator at a high level without RTL redevelopment or compromising performance.

Fluid encapsulates high level memory abstractions as services that provide designers starting points higher than bus interfaces and standard DMA IPs. Fluid also raises the level of abstraction for communication; the designer's modules communicate with service modules through logically point-to-point channels and a message passing standard. Fluid's design methodology enables layers of abstraction for accelerator architects, service library designers, and infrastructure designers. Fluid (1) absorbs the complexity of memory and communication infrastructure from designers' modules without increasing overhead or compromising performance, (2) enables higher levels of abstraction for hardware design by decoupling functionality from implementation, and (3) supports designers to flexibly compose accelerator systems on FPGAs at a high level with transparent control over implementation details.

This thesis creates a working Fluid design framework equipped with a catalog of services. These services are available as an extensible library of parameterizable, composable hardware modules implementing high-level and primitive building-block functionalities. Fluid's design framework provides a communication infrastructure library to flexibly compose, connect and place services across memory and compute devices. Designers build complete accelerators with a high level design framework that enables maintainable and expressive descriptions of their design. Fluid enables designers to abstractly specify their designs at a high level maintaining control over the implementation details. Designers use Fluid's programming interface to compose a service-oriented design and generate the necessary infrastructure between modules. Using this framework, we complete an evaluation of Fluid's merits through the design and implementation of a series of applications. The evaluation demonstrates the programmability benefits Fluid facilitates by separating specification from implementation for FPGA hardware development. Fluid's methodology increases design flexibility and convenience without increasing resource utilization or reducing performance—even for large, high-performance applications.

viii

## Contents

| C  | Contents        |                                               | ix   |  |

|----|-----------------|-----------------------------------------------|------|--|

| Li | List of Tables  |                                               | xiii |  |

| Li | List of Figures |                                               | xv   |  |

| 1  | Intr            | oduction                                      | 1    |  |

|    | 1.1             | FPGAs for Computing                           | 1    |  |

|    | 1.2             | Increasing FPGA Programmability               | 3    |  |

|    | 1.3             | A Methodology for Increasing Programmability  | 5    |  |

|    | 1.4             | Working with Fluid in Practice                | 10   |  |

|    | 1.5             | Thesis Contributions                          | 11   |  |

|    | 1.6             | Thesis Organization                           | 12   |  |

| 2  | Bacl            | kground                                       | 14   |  |

|    | 2.1             | Computing with FPGAs                          | 14   |  |

|    | 2.2             | FPGA Programming and Control Abstractions     | 15   |  |

|    | 2.3             | FPGA Infrastructures and Memory Architectures | 18   |  |

|    | 2.4             | FPGA Communication Architectures              | 20   |  |

|    | 2.5             | Near Data Computing                           | 22   |  |

|    | 2.6             | Active Messages                               | 22   |  |

|    | 2.7             | Service-Oriented Architecture                 | 23   |  |

| 3  | Mer             | nory as a Service                             | 25   |  |

|    | 3.1             | Motivating Another FPGA Memory Architecture   | 25   |  |

|    | 3.2             | Memory as a Service: Scope and Assumptions    | 27   |  |

|    | 3.3             | The Principles of Memory Services             | 28   |  |

|   | 3.4 | Why Choose Services as an Abstraction?                | 29 |

|---|-----|-------------------------------------------------------|----|

|   | 3.5 | Service-Oriented Memory Architecture                  | 30 |

|   | 3.6 | Composing Services Hierarchically                     | 33 |

|   | 3.7 | A Taxonomy for Services                               | 37 |

|   | 3.8 | Services are Smart IPs                                | 39 |

| 4 | Con | nmunication as a Service                              | 42 |

|   | 4.1 | The Need for a Fluid Communication Architecture       | 42 |

|   | 4.2 | Challenges in Developing a Communication Architecture | 44 |

|   | 4.3 | The Principles of Communication as a Service          | 45 |

|   | 4.4 | A Unified Communication Interface                     | 46 |

|   | 4.5 | Active Messages                                       | 54 |

|   | 4.6 | Supported Connection Types                            | 57 |

| 5 | Con | nposing Service-Oriented Designs                      | 61 |

|   | 5.1 | Example Service-Oriented Application Design           | 61 |

|   | 5.2 | Fluid Design Composition Framework Overview           | 63 |

|   | 5.3 | Curating Services                                     | 66 |

|   | 5.4 | Instantiating Services in a Design                    | 67 |

|   | 5.5 | Platform Setup and Design Generation                  | 69 |

|   | 5.6 | Design Visualizer                                     | 70 |

|   | 5.7 | Improving Design Description Capability               | 72 |

| 6 | Bui | ding Services                                         | 76 |

|   | 6.1 | Linear Memory Services                                | 77 |

|   | 6.2 | Counters Service                                      | 82 |

|   | 6.3 | Memcopy Service                                       | 83 |

|   | 6.4 | Worklist Service                                      | 83 |

|   | 6.5 | Graph Service                                         | 85 |

|   | 6.6 | Streaming Services                                    | 88 |

| 7 | Con | structing Communication Channels                      | 93 |

|   | 7.1 | Wire and FIFO Connections                             | 93 |

|   | 7.2 | Connections Through a Network on Chip                 | 94 |

|   | 7.3 | Circular Buffer Connections in Off-Chip Memory        | 97 |

|    | 7.4         | Ethernet Network Connections                                       | 98  |

|----|-------------|--------------------------------------------------------------------|-----|

|    | 7.5         | Evaluating Channel Connections                                     | 100 |

| 8  | Eval        | uating the Fluid Methodology                                       | 107 |

|    | 8.1         | Breadth First Search Case Study Implementation                     | 107 |

|    | 8.2         | Abstracting Data Structure Complexity with Software Services       | 118 |

|    | 8.3         | Sparse Matrix Vector Multiplication Design Study                   | 119 |

|    | 8.4         | Service-Oriented Pigasus Intrusion Detection and Prevention System | 125 |

| 9  | Con         | clusions                                                           | 133 |

|    | 9.1         | Future Directions                                                  | 134 |

| Bi | bliog       | raphy                                                              | 137 |

| A  | Sou         | rce Code for the BFS Case Study                                    | 149 |

|    | A.1         | Python Service Catalog                                             | 149 |

|    | A.2         | Python System Design                                               | 152 |

|    | A.3         | Bluespec User-Level Kernel                                         | 154 |

| B  | Pyth        | on Description for the Service-Oriented Pigasus Design             | 163 |

|    | <b>B.</b> 1 | Python Service Catalog                                             | 163 |

|    | B.2         | Python System Design                                               | 172 |

#### CONTENTS

# List of Tables

| 6.1  | Read and Write Service Message Format                                                | 77  |

|------|--------------------------------------------------------------------------------------|-----|

| 6.2  | Read-Modify-Write Service Message Format                                             | 81  |

| 6.3  | Counters Service Message Format                                                      | 82  |

| 6.4  | Memcopy Service Message Format                                                       | 83  |

| 6.5  | Worklist Service Message Format                                                      | 84  |

| 6.6  | Graph: Get Vertex Neighbors Service Message Format                                   | 86  |

| 6.7  | Graph: Unlock and/or Update Neighbor Service Message Format                          | 87  |

| 6.8  | Read Stream Service Message Format                                                   | 88  |

| 6.9  | Write Stream Service Message Format                                                  | 89  |

| 6.10 | Avalon Streaming Message Format                                                      | 90  |

| 8.1  | Benchmark Graphs Used in Evaluations                                                 | 109 |

| 8.2  | Resource Utilization for Service Abstractions on the Intel Stratix 10 PAC            | 110 |

| 8.3  | Work-item Bundles Spilled to Memory                                                  | 117 |

| 8.4  | Benchmark Graphs Used in Evaluations                                                 | 120 |

| 8.5  | Resource Utilization for Pigasus Designs on the Intel Stratix 10 MX Evaluation Board | 127 |

# List of Figures

| 1.1 | Service module abstraction.                                                                     | 5  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 1.2 | Memory as a service layered system architecture.                                                | 6  |

| 1.3 | Communication as a service abstraction with generated connection implementations                | 7  |

| 1.4 | Fluid code and design flow.                                                                     | 9  |

| 3.1 | Fluid's service abstraction hides the implementation complexity of service modules and re-      |    |

|     | quired infrastructure                                                                           | 31 |

| 3.2 | The hierarchy of composable Fluid service modules                                               | 34 |

| 3.3 | A taxonomy of Fluid services                                                                    | 37 |

| 4.1 | Communication channels shown as FIFOs between a user-level kernel module to the left and        |    |

|     | service modules to the right.                                                                   | 46 |

| 4.2 | The memory service architecture in which processing kernels interact with abstracted memory     |    |

|     | services through channel interfaces.                                                            | 47 |

| 4.3 | Logical connections communication abstraction and implementation reality where connections      |    |

|     | are elaborated with wires, a FIFO, NoC, or Ethernet implementations and services are placed     |    |

|     | across multiple FPGA devices.                                                                   | 50 |

| 4.4 | Graph service, demonstrating message driven operations, that abstracts the logical complexity   |    |

|     | to aggregate data from a sparse data structure into a relevant response                         | 56 |

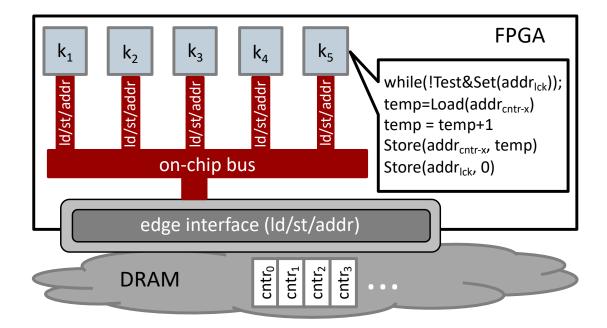

| 5.1 | Processing kernels incrementing a shared table of counters in DRAM. Each kernel must be         |    |

|     | aware of the interface and locking semantics, as well as the table data structure details.      | 62 |

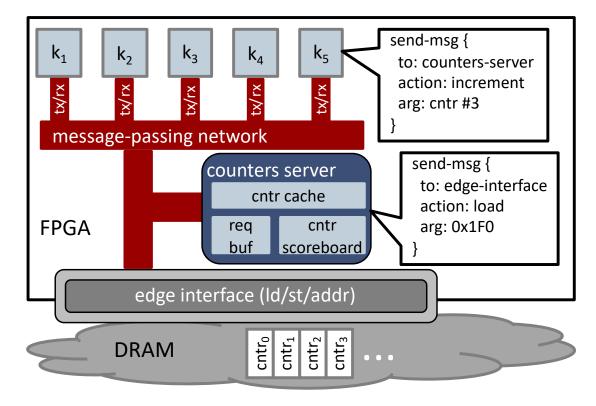

| 5.2 | A service module acts on the kernel's behalf to manipulate counters in memory in response to    |    |

|     | a message request.                                                                              | 63 |

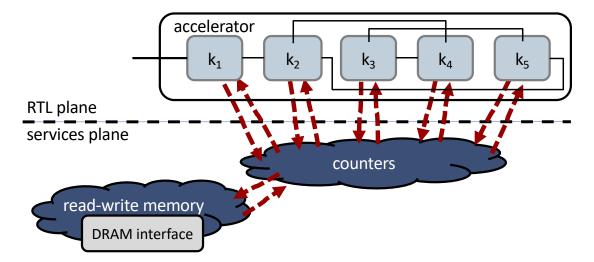

| 5.3 | A service-level sketch of the design from Fig. 5.2 showing the normal accelerator design module |    |

|     | hierarchy, abstract services and channel connections.                                           | 68 |

| 5.4 | A service-level sketch of an accelerator design generated by the design framework's system          |     |

|-----|-----------------------------------------------------------------------------------------------------|-----|

|     | visualizer                                                                                          | 71  |

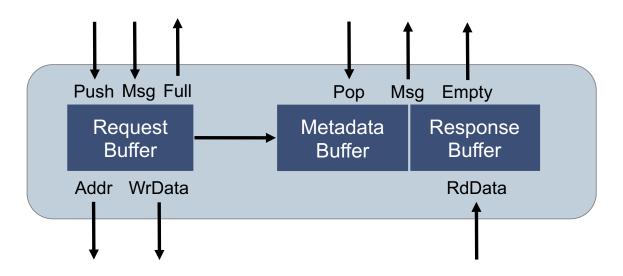

| 6.1 | A generalized read/write service microarchitecture diagram, that supports the memory service        |     |

|     | abstraction adapting edge memory interfaces to service channel interfaces.                          | 79  |

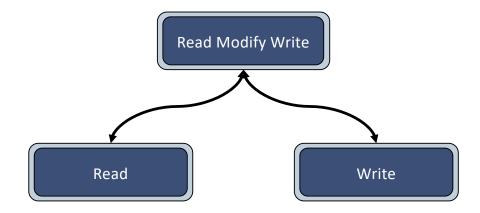

| 6.2 | The channel connection relationship for a read-modify-write service requiring read and write        |     |

|     | services on separate channel interfaces.                                                            | 81  |

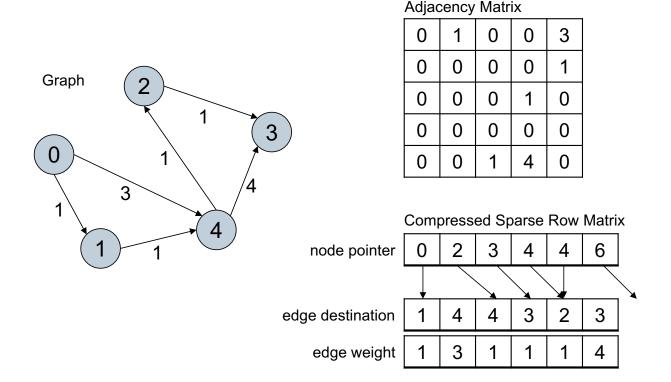

| 6.3 | A graph (left) represented in memory as an adjacency matrix (right.top) and as a compressed         |     |

|     | sparse row matrix (right.bottom)                                                                    | 85  |

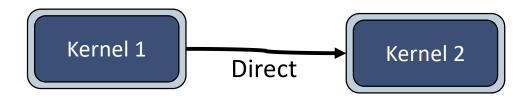

| 7.1 | Direct connection between streaming kernel modules.                                                 | 94  |

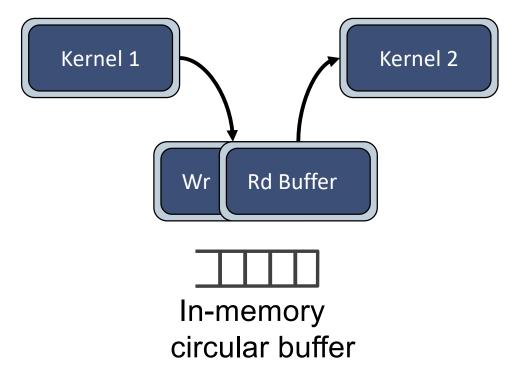

| 7.2 | Network on chip connection between streaming kernel modules                                         | 96  |

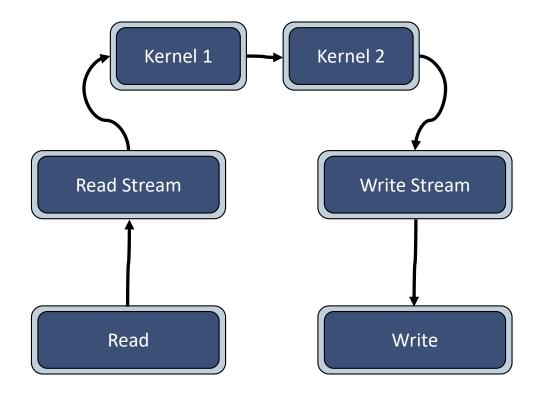

| 7.3 | Circular buffer connection between streaming kernel modules through host memory                     | 99  |

| 7.4 | Ethernet connection between streaming kernel modules through the IKL IP                             | 99  |

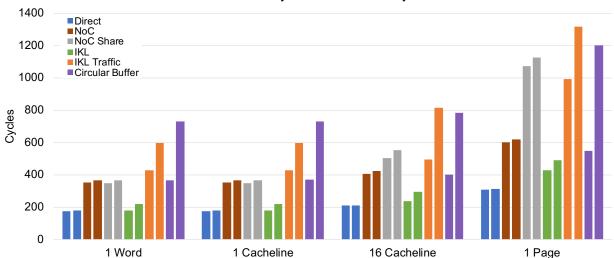

| 7.5 | Evaluation setup service system for connection substitution between channel interfaces              | 101 |

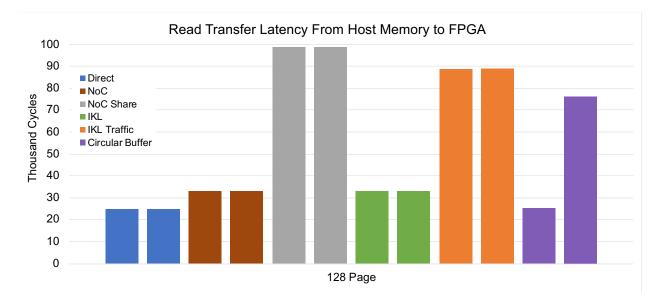

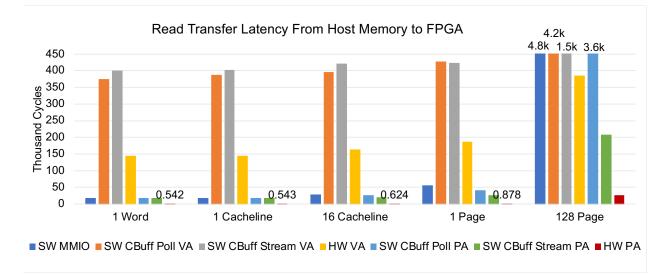

| 7.6 | Read transfer latency from host memory to FPGA comparing hardware-hardware communica-               |     |

|     | tion mechanisms with transfer sizes from one word to one page.                                      | 102 |

| 7.7 | Read transfer latency from host memory to FPGA comparing hardware-hardware communica-               |     |

|     | tion mechanisms for a large multi-page transfer                                                     | 103 |

| 7.8 | Read transfer latency from host memory to FPGA comparing hardware-software communica-               |     |

|     | tion mechanisms and hardware direct memory access.                                                  | 104 |

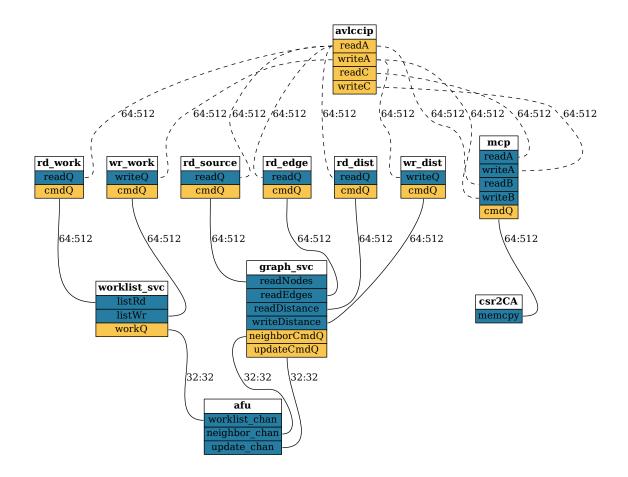

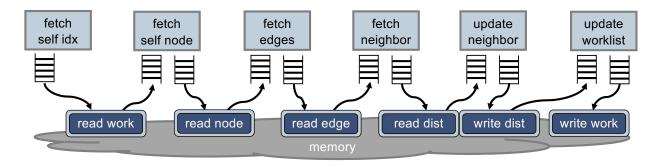

| 8.1 | Baseline BFS elastic pipeline accelerator with read/write services. Each service enables access     |     |

|     | to a part of the graph data structure in memory.                                                    | 108 |

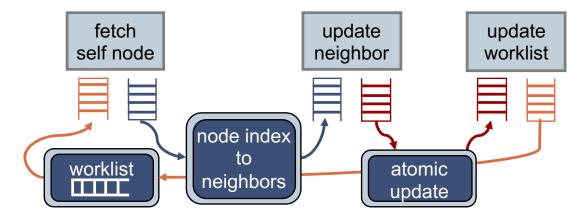

| 8.2 | Final BFS accelerator including graph services-that abstract the graph traversal and atomic         |     |

|     | neighbor distance update—and a worklist service                                                     | 108 |

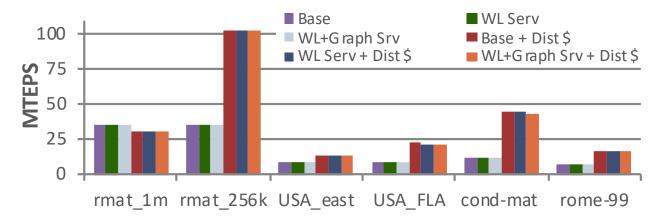

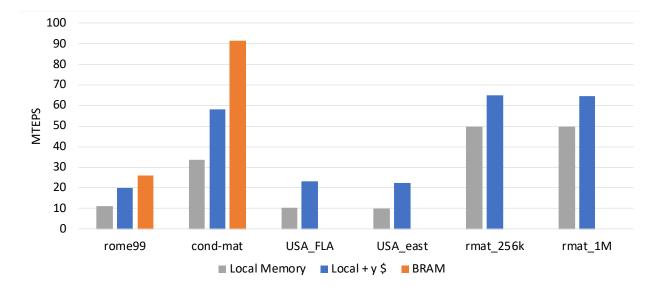

| 8.3 | Performance achieved in millions of traversed edges per second (MTEPS) for the BFS accelera-        |     |

|     | tor for the base implementation, worklist service, and graph services implementations showing       |     |

|     | that the service abstraction does not negatively impact performance                                 | 110 |

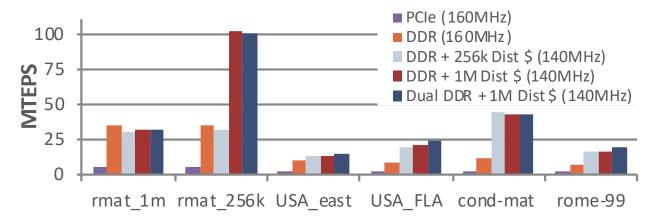

| 8.4 | Performance across memory devices available in the PAC system and node distance caching             |     |

|     | for the BFS accelerator shown in MTEPS. These results highlight the flexibility of services across  |     |

|     | diverse memory interfaces and cache configurations.                                                 | 111 |

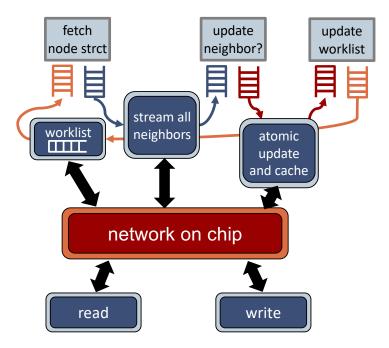

| 8.5 | The BFS accelerator with a network on chip inserted as the communication architecture be-           |     |

|     | tween higher-level services and pair of supporting read-write services at the interface. $\ldots$ . | 112 |

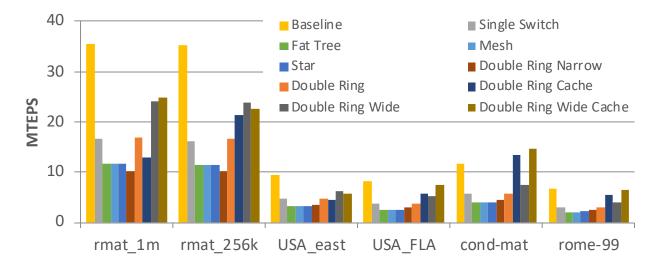

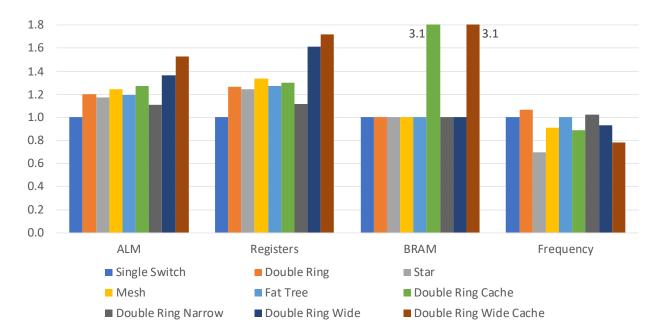

| 8.6  | Performance across a variety of NoC configurations for the BFS accelerator shown in MTEPS.     |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | These results highlight the flexbility of the communication architecture through the NoC.      | 113 |

| 8.7  | Resource utilization compared across a variety of NoC configurations for the BFS accelerator   |     |

|      | normalized to a single switch network on chip.                                                 | 114 |

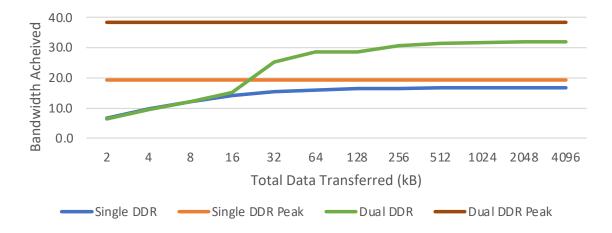

| 8.8  | Read service bandwidth microbenchmark for single and dual DDR channel infrastructure con-      |     |

|      | figurations                                                                                    | 116 |

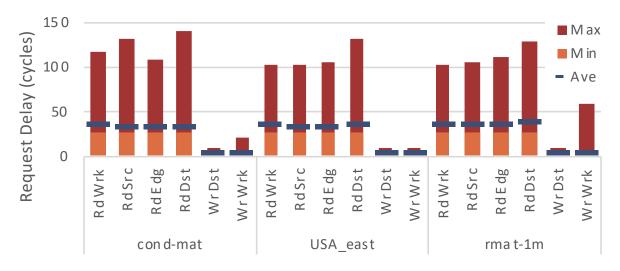

| 8.9  | Introspection of request delay, enabled by statistics sampler cores, for each edge memory seg- |     |

|      | ment service across three benchmarks from the BFS accelerator case study.                      | 117 |

| 8.10 | Transfer throughput substituting hardware and software implementations of services and tar-    |     |

|      | geting different data structures.                                                              | 119 |

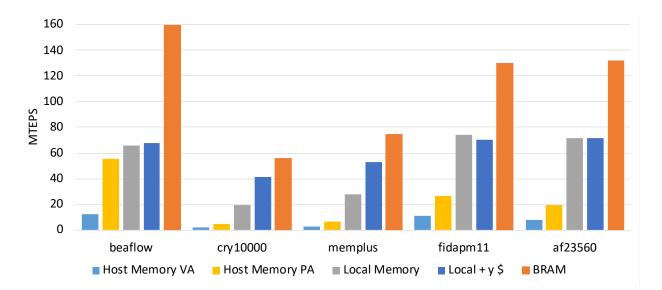

| 8.11 | Performance across memory devices available on the Intel PAC and node distance caching for     |     |

|      | the SpMV accelerator shown in MTEPS. These results use standard matrix market benchmarks.      | 123 |

| 8.12 | Performance across memory devices available on the Intel PAC and node distance caching for     |     |

|      | the SpMV accelerator shown in MTEPS. These results use the graph benchmarks from the BFS       |     |

|      | study                                                                                          | 124 |

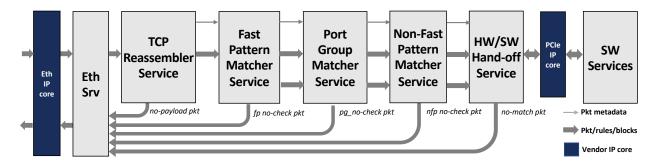

| 8.13 | Original Pigasus intrusion detection and prevention system [101].                              | 126 |

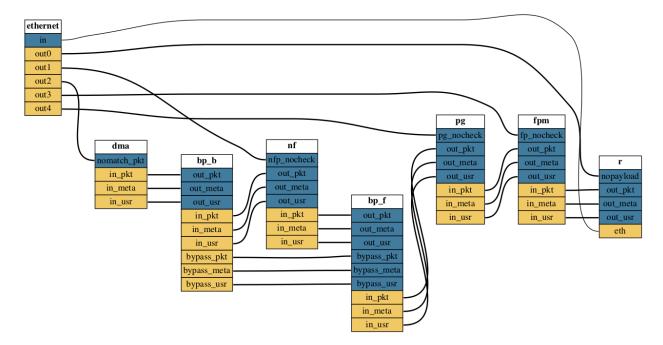

| 8.14 | Service-oriented Pigasus intrusion detection and prevention system.                            | 127 |

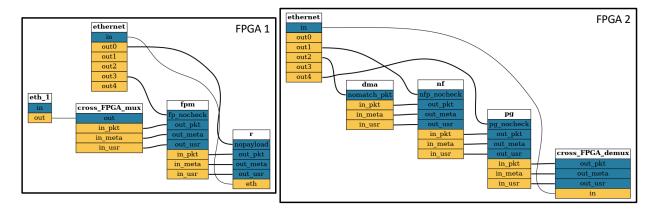

| 8.15 | Service-oriented Pigasus block diagram from the Fluid design vizualizer.                       | 128 |

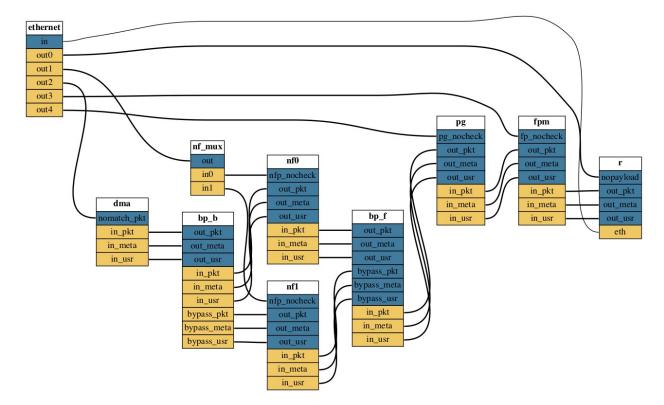

| 8.16 | Pigasus block diagram demonstrating scale out capabilities in the non-fast pattern matcher     |     |

|      | service                                                                                        | 129 |

| 8.17 | Dual FPGA Pigasus block diagram from the Fluid design vizualizer.                              | 130 |

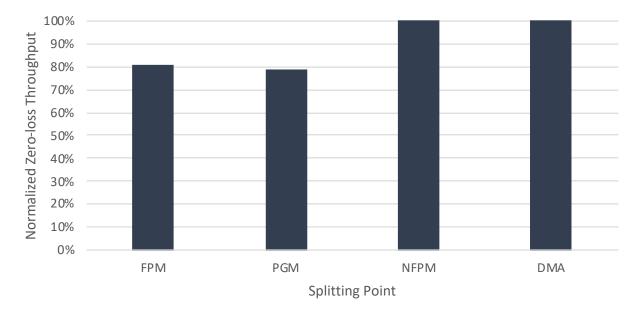

| 8.18 | Normalized throughput of Pigasus for cross-FPGA split points before the labeled service        | 131 |

## Chapter 1

## Introduction

#### 1.1 FPGAs for Computing

For decades, general-purpose CPUs have been the staple computing architecture. Their ubiquity is due, in part, to their convenient programming model. Furthermore, CPUs have steadily increased their performance capability due to transistor scaling. However, in recent years their performance gains have severely slowed due to power limitations [28]. Now, computer architects turn to hardware specialization through dedicated compute accelerators to increase efficiency while continuing to add capabilities with additional available transistors [23]. Over the last decade field-programmable gate arrays (FPGAs) have rapidly evolved from their traditional use as glue-logic or verification technologies for CPUs and ASICs into fully capable computing devices [37, 66, 67]. This evolution is spurred by the computing industry's focus on hardware accelerators to increase compute power through efficient specialized circuits, while balancing a need for more flexibility than ASICs offer.

FPGAs occupy a unique position in the computing landscape. Their field-programmable nature allows accelerator designers to achieve high performance and efficiency through specialization while maintaining flexibility to change over time. FPGAs have demonstrated capability as compute devices accelerating many workloads with highly tuned compute kernels [17, 55, 85]. The promise of performance has even led to tighter integration with general-purpose CPUs, and in some cases cache coherent access to main memory [69]. Large-scale cloud networks of FPGAs have also been successfully deployed [30, 33, 76]. Furthermore, FPGAs are growing in logic and compute capacity with additional hardened compute macro blocks [35, 53]; large on-chip and in-package high-bandwidth memories appear inside FPGA packages to feed these additional compute capabilities as well [45]. All of these additional capabilities are coupled with extremely large logic fabrics to support larger accelerators on a single FPGA device. As FPGA

devices grow, distributing data across a large logic fabric requires new design patterns as long wires

are no longer effective or efficient [2, 39]. Designers must adapt their designs to face this new reality by targeting recently available resources like hardened network-on-chips for data distribution.

While FPGAs themselves are capable and available, their programming model limits their widespread adoption-today's FPGAs are too large and complex for a single designer. Hardware designers harness the flexible potential of FPGAs controlling every bit at each cycle. While this level of control is effective for compute kernel design, it becomes tedious for application composition; namely implementing support structures and datapath state machines. Programming at the bit and cycle level limits portability and scalability when support infrastructure requires redevelopment for each additional platform. Designers must account for more heterogeneity and possibilities than ever before on today's modern FPGAs. Modern FPGA devices and platforms are rapidly evolving to meet the growing needs of the compute industry compounding the complexity of redevelopment to harness the additional compute, communication, and memory capabilities available to each new device [3,21,47]. Recently, several tools and abstractions have been introduced to simplify FPGA development which are discussed in detail in Chapter 2. Commercially available high-level synthesis tools and IP generators greatly simplify compute kernel design—and recent advances in programming abstractions facilitate simple data transfers and module connections [5, 41, 42, 95]. However, their focus remains on low-level load-store data transfers and structural connections through standard buses. While current tools assist in developing straightforward plumbing, their programming models are often tedious and error prone. FPGA designers are still responsible for more complex data access patterns and the semantics of the data transferred on module connections. Current FPGA tools and programming abstractions stop short at raising the level of abstraction for memory, communication infrastructure and design composition.

Many layers of abstraction have been built over time for general purpose processors—applying this same approach, abstraction can simplify FPGA application development. Memory is the fundamental general-purpose computing architecture, where further abstractions such as operating systems, and software libraries make software design efficient, portable, and flexible. However, not all CPU abstractions are a good fit for FPGAs, and abstractions have a different cost in hardware. Abstraction cost is incurred in logic capacity on the FPGA fabric, not time. FPGAs unique advantage as a programmable hardware technology should extend into an abstraction that increases their programmability. Hardware designers, through abstraction, should be able to start at design points higher than simple data transfers on busses. FPGA designers should be supported by specialized functionalities, available in a library, that reduce overall development time and facilitate access to data.

#### 1.2 Increasing FPGA Programmability

**Challenges.** Though abstraction is promising to increase programmability, many abstractions are insufficient or complicated for widespread adoption. Developing hardware modules is complex and time consuming, especially following best practices for reusability and flexibility [71]. However, abstractions have been demonstrated for decades in software development to increase programmability. Rather than paying for abstraction in cycles that reduce performance as in software, hardware abstraction performance overhead is low, where functionalities are spatially distributed and would ordinarily be contained within the designer's kernel modules. Much of the design complexity in hardware accelerators arises from memory and infrastructure. FPGA designers need more support from tools and abstractions as a way to digest, understand, compose, and integrate modules correctly to increase programmability. Going forward, hardware designers require starting points higher than loads and stores for accessing data in memory, while retaining the flexibility required to produce efficient hardware designs.

An abstraction that balances productivity, efficiency and expressivity to decouple functionality from implementation meets this requirement. Modules rely on functionality exposed through the abstraction and implementation choices only change performance, power, and/or area rather than correctness. Developing abstractions that support designers and promote reusability is a difficult task by itself. Software abstractions typically employ a layered approach where higher level support is built in a stack. Following a similar design pattern, high-level hardware abstractions can be built hierarchically layering support on lower-level IPs and physical devices. This reduces development efforts by virtualizing platform details and providing portability.

Integrating IPs correctly and intelligently is essential to build real systems from abstract specifications. Managing integration complexity is required to factor memory and datapath infrastructure outside of the designer's compute modules. Currently, connections are purely mechanical in FPGA design processes. Designers must wire busses to their IPs and correctly implement the protocol. Abstraction can simplify module integration and system architecture as well. A proper FPGA design interface should raise the level of abstraction, above RTL, enabling designers to conveniently and efficiently architect their accelerators and provide transparent control over the implementation details. Simply describing physical connections isn't sufficient for designers and tools to correctly build designs. It is necessary to understand the semantics and structure of the data sent between modules in order to verify that modules are correctly connected. The design abstraction must be able to provide guarantees that the required modules are instantiated and connected correctly to implement the designer's high level specification.

Goals. The key question in this thesis is: what abstractions fit for FPGA hardware development? An answer

requires (1) an identification of the boundaries and functionalities where abstraction benefits the designer, (2) a good design methodology and expressive interface to effectively and efficiently support designers, and (3) an evaluation of this methodology that demonstrates it's ability to increase programmability without negatively impacting performance.

Fluid's goal is to reduce the barrier to entry for FPGA accelerator development, without compromising performance, and enable hardware developers to conveniently and efficiently develop their ideas in hardware. Fluid develops a design methodology that supports a hierarchy of abstraction layers that enable service-oriented hardware design, and decouple memory and communication infrastructure from a hardware developer's modules. It borrows concepts from service-oriented architecture to abstract memory and communication to simplify FPGA hardware development, both for module development and design integration. This service-oriented abstraction breaks hardware into digestible units with structured interfaces where the details of communication and memory infrastructure are relieved from the module designer's concern.

Flexibility is a subtle strength inherent to FPGAs. The abstractions Fluid initiates harness and celebrate flexibility through structure rather than uninhibited freedom. Fluid demonstrates that structure reduces complexity and encourages reusability, portability and composability. It raises the level of abstraction for memory from low level primitives, such as loads and stores, to high-level semantic rich operations like graph traversals. However, it is not enough to enable high level abstractions for accessing data in memory, a communication abstraction provides the necessary facilities to integrate modules into a larger design. Raising the level of abstraction for communication and memory allows the designer to utilize high-level memory operations and flexibly compose systems increasing programmability in terms of correctness, productivity, and performance.

The support Fluid provides, through service-oriented design practices, requires a shift in the designer's thought process from a flat module hierarchy to abstract distributed services, connected logically, outside their typical RTL design flow. Providing abstractions in the right places, namely limiting abstraction to the module's boundary and outside infrastructure, increases flexibility without reducing efficiency and enables designers to focus on their contributions. Additionally, Fluid's modular design methodology enables designers to describe their accelerators at a high level without ceding all of their control over implementation details to the abstraction. Fluid aims to support RTL designers, absorbing the development responsibilities around accessing data in memory and communication infrastructure, enabling designers to integrate their modules into a larger accelerator design through a high level description.

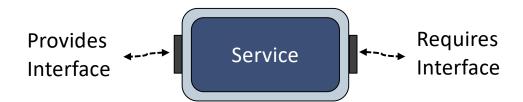

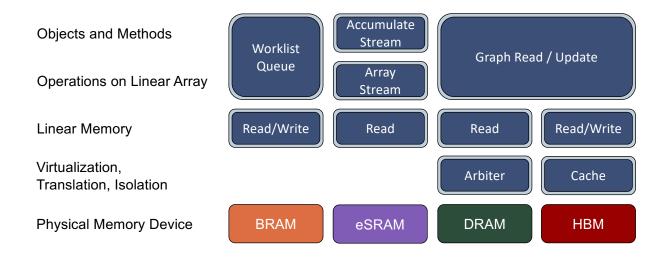

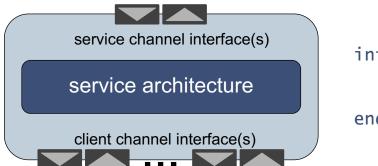

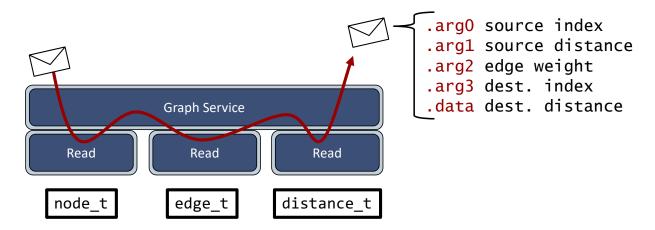

Figure 1.1: Service module abstraction.

#### **1.3** A Methodology for Increasing Programmability

Fluid develops abstractions for FPGA memory and communication by absorbing the complexity of each from hardware developer's modules to increase programmability. Fluid also provides a design framework to integrate modules adhering to these abstractions. This thesis demonstrates that Fluid's approach increases flexibility and does not increase resource utilization nor negatively impact performance. Fluid's abstractions factor memory and communication logic out of a hardware designer's kernel module. Fluid develops a service-oriented design paradigm where modules are abstracted as services as shown in Figure 1.1. The hardware designer is relieved of the tedious and error prone responsibility of developing infrastructure for accessing and communicating data in their kernel module designs. Fluid simplifies RTL modules as its primary goal, and provides a library of high-level specialized services for accessing data as starting points higher than generic load/store interfaces. The provides-requires relationship shown in Figure 1.1 develops a framework so that modules can rely on functionalities outside of their scope and design changes do not impact functional correctness. Fluid's service design methodology defines a structured module interface so that modules and connections can easily be generated from a high level description. Furthermore, the provide-requires relationship enables the design generation framework to understand the semantics of connections beyond their physical properties to ensure correctness and support composability.

A designer's modules, as clients, request and consume services through a message passing protocol that flexibly supports single transfers or streams of data. The shift in thinking required for designers to rely on services naturally extends to communication. This thesis provides a communication abstraction where module connections are purely logical, just as services abstractly provide high-level operations to access and process data. Connections between a designer's kernel modules and service modules follow latency-insensitive design practices that separate the connections implementation and performance from functionality [14, 15]. As far as the designer is concerned connections are purely logical, this makes communication trivial regardless of the IP implementation language, architecture, device or board.

While Fluid's service abstraction is fundamentally influenced by FPGA design practices and FPGA's

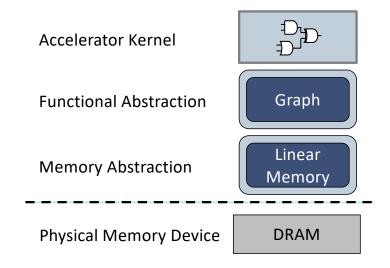

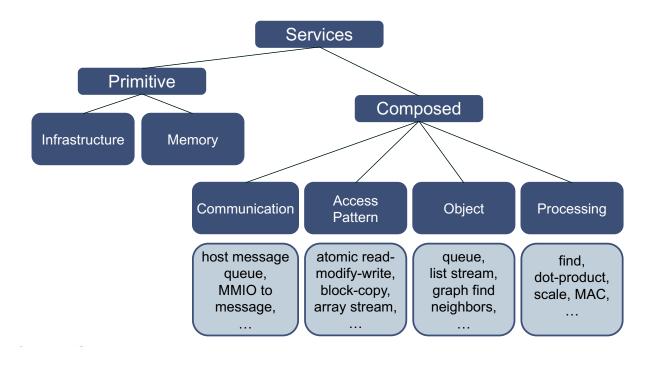

Figure 1.2: Memory as a service layered system architecture.

inherent flexibility to change over time, however it can apply to application-specific integrated circuit (ASIC) development. FPGA designs lend greater tolerance for abstraction compared to ASICs which typically have different design goals. The relatively longer ASIC development timelines leans towards extreme efficiency optimizing for every bit and cycle. However, as ASIC designs grow, module integration time increases; this is where the methodologies developed in this thesis can be applied. Fluid develops a methodology for modular design practices and abstraction where module connections carry semantic significance beyond structure and protocol. This allows tools to reduce the accidental complexities encountered in integrating modules in disaggregated designs. ASIC designers could also benefit from Fluid's high level design interface that would allow them to write expressive and maintainable descriptions of their infrastructure and accelerator's composition, and maintain them as IPs.

#### 1.3.1 Memory as a Service

**Memory Abstraction.** Any abstraction can crumble without a sound foundation. Today's FPGAs are afforded a rich landscape of memory devices from monolithic on-chip memory to in-package high bandwidth memory to large capacity persistent memory. Fluid's memory abstraction supports the portability of higher-level services across memory devices without impacting functionality. Each memory type comes with its own set of properties and protocols in addition to its physical interface to the FPGA device. In order to build support for higher-level services and ensure portability, the lowest level memory services abstract platform details. The lowest level memory services provide familiar read and write primitives to access data in linear address spaces. Read and write services support a uniform abstraction that underpins

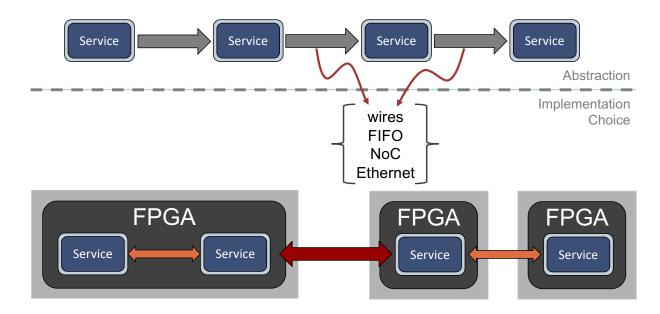

Figure 1.3: Communication as a service abstraction with generated connection implementations.

the memory as a service model by virtualizing the details of platforms and memory devices. Multiple read and write services can share a single memory device and support multiple virtual scratchpads. Additionally, read and write services are sufficiently parameterizable so that designers are unrestrained and can leverage a device's natural properties, control performance, or choose a simplified protocol. The currently available read and write services support common commercially available bus interfaces for on chip memory and off chip memory controllers: AXI, Avalon, and CCIP. Additionally, parameterizable caches are available as a performance enhancement layered on read and write services.

**Functional Abstraction.** To increase programmability and provide the same ease of use that software designers have come to expect, Fluid extends service-oriented design paradigm to provide abstract, high-level functionalities to hardware designers. Fluid's memory as a service paradigm raises the level of abstraction for hardware designers to services. The service abstraction encourages designers to disaggre-gate their design into reusable composable service modules to build more complex services in a hierarchy as shown in Figure 1.2. Even services are encouraged to be hierarchically composed of services. Services provide specialized operations to access and process data that live outside of the accelerator designer's module scope. Fluid provides a structured, uniform interface for communicating with services and a framework for linking clients' interfaces to service absorb complex operations from the designer's kernel modules such as the logic for sequencing atomic operations in memory or managing data structure interactions. A service describes an abstract functionality, and multiple implementations of a service can exist in the library for example: designs encapsulating logic for different underlying data layouts and/or with various power, performance, and area characteristics.

#### 1.3.2 Communication as a Service

**Communication Abstraction.** It is necessary to include communication as a first-class concern in any FPGA abstraction. It is insufficient to raise the level of abstraction only for memory—moving data both on- and off-chip is a major part of any non-trivial design and paramount for performance. The communication abstraction developed by Fluid defines a channel interface that relies on latency-insensitive design

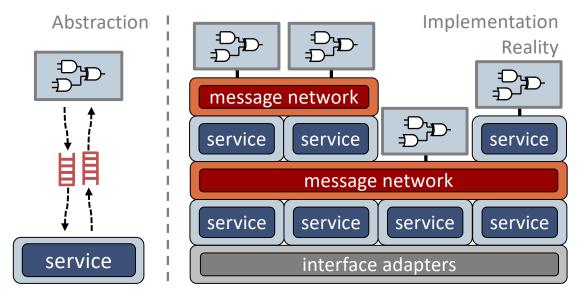

practices that guarantees in-order delivery of messages but does not specify exact timing details. Relying on abstract communication between modules increases implementation flexibility, design scalability, and introduces the ability to transparently place modules across chip boundaries. Latency-insensitive communication is well studied for hardware design and inspired Fluid's communication abstraction [15,31]. Modules send request messages, through logically point-to-point channels, to services that will satisfy the request with an appropriate response. All necessary communication infrastructure to implement the connection the channel specifies lives outside of the module's scope. Figure 1.3 shows the communication abstraction where channel connections are implemented later on by a code generator. Generated connections are expressed abstractly; substituting one connection type for another doesn't impact the functionality of the overall design. This allows designers to flexibly compose modules at a high level and incrementally support new communication substrates for connections, without modifying their existing modules. Fluid provides a library of connection types including directly connecting modules with wires to more exotic connection types including network on chip and Ethernet connections.

Hardware-Software Abstraction. Fluid abstracts away the implementation details of both the service and communication infrastructure. Consequently, this makes hardware-software communication seamless between components that adhere to the abstraction. Fluid provides libraries and infrastructure for both hardware and software so that the channel and message passing abstraction is upheld across both architectures. Services can have software and hardware implementations transparent to a client module. Software threads on a host processor allow designers to quickly prototype services and even involve software in designs for complex operations. Fluid provides a couple channel connection implementations for hardware-software communication relying either on circular buffers in the host's main memory or memory mapped input-output transactions pushed by the host. This thesis develops an understanding of the capabilities of software services and demonstrates that software services can be used to simplify hardware design efforts in testing and integration.

#### 1.3.3 Abstracting High Level System Design

Raising the level of abstraction for design composition is essential to unlock productivity and programmability gains for hardware designers using the abstractions developed by Fluid. Fluid's design composition framework provides a high level design interface that allows designers compose their systems in Python rather than RTL. The framework is transparent and flexible so that designers can logically compose their accelerator while maintaining control over implementation details. This is enabled by its expressive and extensible interface that exposes relevant design details as parameters. Fluid's design tool generates

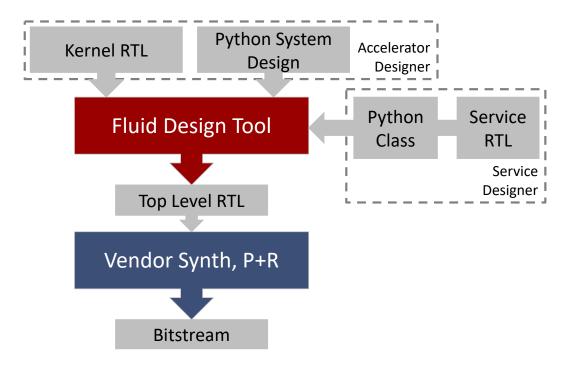

Figure 1.4: Fluid code and design flow.

the specified infrastructure to build connections between modules without completely removing the designer's influence. Additional abstraction layers and convenient functions can be built within the high level design interface to simplify the design process. Highlighting its extensibility, as FPGA devices incorporate emerging memory devices and/or hardened network on chips, designers can incrementally adopt these resources once they are introduced into the framework. Fluid encourages designers to capture the available performance and/or flexibility by regenerating their design from a high-level description now targeting the additional memories or communication resources with minimal additional effort.

A description of the design flow is shown in Figure 1.4. The accelerator designer uses a high level Python description to compose their service-oriented system design and writes their kernel modules in RTL. Designers instantiate services in their high level system design and specify connections between each module's channel interfaces. Every service has a corresponding class description in the service catalog and RTL implementation provided by the service's designer. The class describes the service, its channels, the services it provides and requires on those channels, as well as any additional wires and registers in its interface. Fluid's code generation framework takes the designer's Python description of their system and generates SystemVerilog code that instantiates modules, connections, and external interfaces. Design choices and exploration are simplified as the designer works with a high level description rather than RTL. Furthermore, the framework ensures channel connections are correctly elaborated and satisfy the provides-requires service contract.

#### 1.4 Working with Fluid in Practice

Fluid's design methodology introduces abstraction layers for memory, communication and system design. The methodology decouples the hardware development process separating module and system design. This separation of concerns simplifies the development process and enables layers of abstraction to be built that increase productivity. Fluid's design framework provides a high level interface to build service-oriented accelerator designs; the details and features of which are described and evaluated in this thesis. The memory and communication abstractions developed by Fluid address FPGA design complexity by reliving the designer of the responsibility of implementing this logic in their modules. Support for these abstractions and relevant accelerator examples are realized and evaluated as thesis contributions. A library of services is designed and implemented as a proof of concept set in this thesis. This initial set of services covers a range of useful and complex memory functionalities that demonstrate the types of operations that fit the service-oriented design paradigm. This thesis also provides a library of supporting IPs for memory and infrastructure that designers leverage explicitly and implicitly to build accelerators. Specifically, some IPs are instantiated behind the scenes to adapt and share external interfaces on the FPGA device, whereas other IPs adapt and integrate network on chips and inter-FPGA communication devices.

#### 1.4.1 Fluid Benefits Evaluation

An evaluation of Fluid's abstractions and design framework reveals the flexibility enabled by separating functionality from implementation. The evaluation also demonstrates that structured interfaces support the abstraction for designers to produce correct and efficient designs from abstract functionalities as services. Fluid is evaluated (1) in a study of the communication abstraction and library of connection types, (2) case study of a graph accelerator for the breadth-first search algorithm, (3) design and implementation of a sparse-matrix vector multiplication accelerator, and (4) through a high-performance intrusion prevention and detection accelerator. Notably, the evaluation demonstrates that Fluid raises the level of abstraction, in doing so increases programmability without impacting performance or resource utilization.

The communication abstraction is evaluated across the set of connection implementations designed and provided in the framework. The study evaluates data transfers of relevant sizes between hardware services and develops recommendations for design choices. The communication abstraction study further evaluates connection types between hardware and software services and offers a novel use-case for software services in the hardware developer's design process. These studies show that abstracting communication relieves hardware developers from the tedious task of plumbing for data movement and introduces additional flexibility to incrementally adopt new communication technologies and module placements. The breadth-first search (BFS) accelerator was selected as a challenging application which requires significant complexity in order to achieve performance. The advantages of a service-oriented design are evident where services allow the designer's modules to appear close to the algorithm pseudocode and to flexibly modify the design at a high level targeting various performance outcomes. BFS is a key algorithm in graph analytics and in recent years, as data sets have exploded in size, become a target for hardware accelerators. BFS is characterized by irregular memory access patterns that are challenging for any architecture. Furthermore, sparse representations of the input graph are often used to increase efficiency at the trade-off of added complexity. A BFS accelerator designed by an expert hardware developer serves as a baseline [90]; an evolution of this design, relying on services, absorbs the complexity around the irregular memory access patterns and data structures. Furthermore, portability and flexibility are studied where services transparently access data in a variety of memory devices and across several network on chip implementations.

Sparse-matrix vector multiplication (SpMV) is a fundamental computational kernel in many applications. A design and implementation of a SpMV accelerator generalizes and extends the BFS case study. SpMV relies on sparse data structures to represent the input matrix in memory reducing its footprint and increasing performance. The SpMV design reuses the graph service from the BFS design. Services emulated in software, transparent to the hardware services on the FPGA, were used in the accelerator development process to simplify debugging and testing of the additional services necessary to complete the SpMV accelerator.

The final application evaluated is a service-oriented adaptation of Pigasus, an expertly crafted intrusion prevention and detection accelerator that achieves 100Gbps throughput [101]. This demonstration abstracts the accelerator's modules as services and further abstracts high-level functionalities as reusable, portable services. Impressively, the final service-oriented design achieves identical performance, without appreciably increasing resource utilization. Furthermore, the service-oriented Pigasus design can be generated through a high-level design specification reducing design effort to produce design variants including multi-FPGA implementations.

#### 1.5 Thesis Contributions

Fluid is an FPGA design methodology that increases programmability by encouraging a modular design style, requiring structured interfaces. Fluid enables higher levels of abstraction to be built for memory, communication and design description. This thesis demonstrates that Fluid raises the level of abstraction for FPGA accelerator design without compromising performance, and makes the following contributions:

- The Fluid modular design methodology which defines a service abstraction for memory and communication that simplifies a module's scope—the designer is only tasked with a module's internal logic rather than infrastructure. The design methodology enables a designer to logically integrate functionalities *as a service* outside of a module internal hierarchy creating a layered abstraction that insulates designers from low level details.

- An accelerator design framework supporting the modular service-oriented design methodology, which hierarchically composes abstractions for FPGA hardware design. The design framework enables designers to efficiently and flexibly integrate modules into a system through a high level programming interface retaining transparent control over the implementation details. It further supports designers to encapsulate and reuse their infrastructure composition patterns as intellectual property.

- Development of a working infrastructural library supporting the communication abstraction and initial library of services that provide essential building blocks for memory operations and demonstrate that higher level memory abstractions, such as graph operations, can be encapsulated by the Fluid design methodology. Designers can rely on and contribute to the library of high-level memory services as starting points at an abstraction level higher than loads, stores, and addresses.

- Demonstration and evaluation that the Fluid design methodology increases FPGA programmability by raising the level of abstraction for FPGA accelerator design, and simplifies module development and integration without increasing resource utilization or decreasing performance.

#### 1.6 Thesis Organization

The remainder of this thesis is organized as follows. Chapter 2 provides background information on FP-GAs as computing devices and current research on FPGA abstractions and programming models. Chapter 3 describes the Fluid memory as a service abstraction in detail. Chapter 4 describes the communication as a service abstraction developed by Fluid. Chapter 5 details and discusses the high level design framework designers use to compose service-oriented accelerators. Chapter 6 presents the catalog for the current library of services and their implementation details. Chapter 7 discusses the implementation details of the connection types supported by the communication abstraction. Chapter 8 details the evaluation studies of the Fluid design methodology, its abstractions and design framework. Chapter 9 concludes and proposes ongoing and future work inspired by Fluid.

#### CHAPTER 1. INTRODUCTION

## Chapter 2

## Background

This chapter presents background material that informs the reasoning behind Fluid's design methodology and abstractions. Particularly, this section will cover motivations for FPGA computing, prior FPGA abstractions, FPGA computing architectures and infrastructures, FPGA communication architectures, and concepts that influenced the work in this thesis.

#### 2.1 Computing with FPGAs

FPGAs have been deployed in various settings leveraging the efficiency and flexibility of the reconfigurable logic. Typically, FPGAs have been used as prototyping devices for ASICs or glue logic in embedded systems. However, FPGAs have evolved and increasingly gained capability as compute devices [21, 35, 53]. Modern FPGA devices provide a large logic fabric featuring large memory capacity and compute capabilities. This evolution comes as general purpose processors face diminishing performance returns in the face of power constraints [28]. FPGAs provide a promising compute solution enabling hardware specialization for power-efficient computing.

Historically, FPGAs have been integrated into computing systems as external stand-alone boards or peripheral cards. In this model a host processor offloads computation to these boards over low-bandwidth IO buses or serial ports. As IO bus speeds have continued to improve, FPGA cards have become more fully featured. Modern FPGAs are available in standardized form factors, some with vendor-provided drivers that enable the FPGA fabric to access host memory, without host intervention, over the PCIe bus. These cards typically feature localized on-board and sometimes in-package high bandwidth memories. While the offload model has proven to be effective, there is recent interest in tighter integration between FPGAs and host processors. Newer systems integrate FPGAs on the primary memory bus, and in some cases with cache-coherent access to main memory to share work at a finer granularity with processors [69,75].

FPGAs are also becoming a part of datacenter infrastructure, lending their compute capabilities as data flows through Ethernet networks [30,63]. Commercial deployments with large networks of FPGAs have also been demonstrated, moving FPGAs closer to the data, supporting networked functions [101], and also large scale datacenter applications [33,76]. These new deployment and integration schemes have led to a new era for FPGAs, where specialization can be applied to an increasing set of evolving workloads. Most recently FPGAs have exploded in popularity as compute devices demonstrating capability in machine learning and data analytics [6,67,89].

While FPGAs have demonstrated capability and are increasingly used as compute devices in commercial settings, FPGAs currently only account for a small fraction of compute devices in deployment [25]. FPGAs lack the same widespread adoption of general purpose CPUs due to their cumbersome programming model. FPGAs still most commonly programmed at the bit and cycle level. This high level of control is necessary for efficiency, however it has proven to be cumbersome as devices and systems scale. FPGAs lack the same level of support from abstraction that software programmers rely on and enjoy. Abstraction increases programmability by hiding complexity when high levels of control aren't necessary. The overwhelming focus in commercial development is on increasing programmability through new programming models and languages as FPGAs mature into compute devices [97].

Even with this increased focus on programmability, FPGA accelerator designers efforts are often adhoc and single-purpose. Engineering efforts are often repeated each design even on the same device and platform. Providing structure and portability through abstraction in the right places increases programmability and allows designers to focus their efforts on tuning their computation kernels rather than on infrastructure.

#### 2.2 FPGA Programming and Control Abstractions

While FPGA devices have been promoted to first-class computing devices, their programming model is their Achilles's heel. The programming model for FPGA's has not evolved as fast as the hardware technology has. FPGAs are often programmed with RTL languages like Verilog and VHDL. These are well known hardware description languages (HDL), however they are notoriously tedious to use and difficult to debug, much like assembly language in general purpose processors. They provide absolute control over every bit each cycle, and this leads to long development cycles and complexity. HDL code further lacks software's portability as the tools and abstractions provided to HDL developers are comparatively underdeveloped. Consequently, HDL design-time burdens developers when reimplementing interface logic for new FPGA platforms. Therefore, most deployments fail to take advantage of FPGA's flexibilityin the wild they are often viewed as static, single-task accelerators.

Several attempts have been made to replace HDLs with higher level languages. Some attempts borrow from functional programming languages and make use of compilers to profile, elaborate, and generate code. Examples of such languages are Blusepec [10], Chisel [7], SpinalHDL [82], and MyHDL [64]. These tools have been used for many academic and commercial projects, including implementations of entire processors like RISC-V. These languages focus on the description of the algorithm datapath, abstracting timing and scheduling details. This simplifies some of the design task but does not apply any higher-level abstraction to compose systems. Designers must still rely on separate integration tools that are mostly manual and bus based. Fluid's design methodology is unconcerned with a module's internal logic, a module is an abstract black-box functionality that can be implemented in any hardware description language. Fluid provides a framework and design interface that simplifies integration and enables the designer to descriptively specify infrastructure at a high level.

Another major development in FPGA programming has been in high-level synthesis (HLS). In this model, designers specify hardware using a stylized C language, and a compiler maps this code to hardware. Numerous HLS tools have been developed including, Vivado HLS/Vitis [93], Intel HLS (Altera A++) [42], Catapult-C [60], Synphony-C [83], and LegUp HLS [13]. HLS compilers specialize in generating deep parallel pipelines, but heavily rely on users for compiler hints to capture parallelism and data reuse. HLS tools often fail when describing concurrent interactions between function calls and scheduling code around long latency DRAM accesses. This requires designers to develop their own logic to handle kernel-to-kernel and kernel-to-memory interactions or rely on embedded processors for high level control. Similar to the languages discussed in the previous paragraph, HLS remains focused on describing algorithms in hardware. It does not provide higher-level abstractions for integrating HLS generated modules into larger accelerator designs.

Recent work has extended HLS compilers with additional support for task parallel programs [20]. In this work, the authors employ a channel interface to capture spatial parallelism in their designs. This allows the compiler to decompose functions by these channel interfaces and support parallelism more naturally in the inherently sequential C language. Other work extends HLS with a similar channel abstraction for hardware-software communication [61]. This work enables transparent migration of functionalities between hardware and software using HLS and standard C compilers respectively. These extensions to HLS attempt to tackle the deficiencies of HLS to capture task parallelism while adding some additional capabilities in hardware-software co-design. These tool extensions could be useful in developing modules within Fluid, however software abstractions remain still fail to capture the true concurrency of hardware design and don't attempt to manage the complexity of off-chip data access. Another orthogonal approach to augment HLS compilers is by combining the concept of decoupled-access-execute to support specialized prefetching and irregular memory access patterns [18, 19, 32]. This approach decouples memory access from the computation in HLS programs and demonstrates that by doing so designs can better tolerate long latency of irregular memory access patterns. This decoupled approach and additional latency tolerance is common to Fluid's methodology. Fluid services demonstrate that by decoupling the logic responsible for irregular memory accesses, the user-level design is greatly simplified. Furthermore, Fluid demonstrates that higher-level memory operations, including irregular memory accesses, can be encapsulated into reusable modules accessed via latency-insensitive interfaces.

High-level synthesis has been further extended to compile complete programs for FPGA acceleration. These compilers profile and analyze complete programs to find targets as acceleration candidates. After generating FPGA kernels for these targeted code sections, tools build the surrounding infrastructure to support data transfer, and kernel invocation. The entire process appears seamless to programmers; software code remains untouched, however, now portions have migrated to FPGA accelerators. Altera's OpenCL is an example of this type of compiler [41]. The OpenCL framework compiles C code for computing systems with a host-processor and accelerator processing-elements. As a general framework, OpenCL can target both FPGAs and GPUs as processing-elements, therefore code with SIMD-pipeline structure and parallelism produce high quality results. LegUp is another similar HLS tool [13]. Rather than target a host-accelerator platform, the LegUp compiler generates soft processors on the FPGA for sequential code sections. Xilinx SDSoC [94] functions much like LegUp, where sequential code targets hardened ARM processor cores. While these tools abstract more of the complexity away, at their core they face many of the problems of traditional HLS tools. Scheduling around DRAM latency, and irregular parallelism rely on the application designer at best, and are impossible at worst.

Domain specific programming languages (DSLs) represent another important class of programming abstractions for describing FPGA accelerators [49]. DSLs provide higher levels of abstraction targeted to the domain of an application expert. Experts express their computations in a manner natural to their domain relying on compilers and tools to implement their algorithms. This approach has demonstrated success to design and as an interface to custom hardware accelerators in graph analytics [68], machine learning [1,73], network functions [12,40,62,81,101], and digital signal processing [34,65]. However, each language is limited in scope to its domain and the designer has minimal control over implementation details relying on the compiler to efficiently implement their intended design. Fluid's design methodology is a flexible approach allowing designers to build highly tuned hardware modules without restriction to any language, architect their accelerator at a high level, and generate the infrastructure between modules. This provides an opportunity for intersection with DSLs where service modules can be developed in a

DSL and integrated into a design by Fluid's toolset. Moreover, DSL compilers often implement their computations from a library of common building blocks. This is similar to Fluid's approach; it is conceivable that Fluid's toolset and service module library could provide building blocks to support DSL compilers on FPGAs.

#### 2.3 FPGA Infrastructures and Memory Architectures

FPGA vendors commonly support their compute-kernel design tools with infrastructure and system design tools [5,95]. These tools present a graphical interface to designers to connect components through buses, such as AXI and Avalon [43,96]. Designers may also compose kernels and application components with the help of intellectual property (IP) libraries. These infrastructures provide the necessary support for application construction. However, with new versions of the tools, buses and IPs change; this can require redevelopment costs for individual kernels and entire applications. Furthermore, buses, while simple, lead to scalability issues when many components contend to drive the bus. This has led to developing interest in network-on-chip (NOC) IP-generation tools [72] and some FPGA vendors are experimenting with hardened NOCs on FPGAs [2,3,35]. However, vendors stop short simply providing additional infrastructure without convenient tools and programming interfaces. Fluid's design framework provides a descriptive interface for designers to specify and utilize infrastructure from a high level description of their accelerator design.

System on Chip (SoC) design tools have been researched to tackle the challenges of integrating heterogeneous IPs within a system on a single piece of silicon. FuseSoC is a package manager and build tool that enables scalable HDL design through modularity, code reuse, and generation [50]. This tool could be used to support the ideas developed in this thesis and support the design framework for generating Fluid designs. The Embedded Scalable Platforms tool proposes that regularity and constraints mitigate integration complexity [58]. Chipyard similarly simplifies the SoC design process with a convenient design framework. These tools target ASIC designers that must integrate processors, accelerators, and caches in their SoC. Constraining the IPs to a regular set of interfaces allows the tool to generate systems with these IPs. While these tools are successful for IP integration, they are mostly manual and based on busses. The bus abstraction has plenty of legacy however it is limiting as SoCs and accelerators continue to scale. These tools also stop short in their design description capabilities to raise the level of abstraction for system composition. Fluid's design methodology abstracts infrastructure used to integrate modules allowing designers to logically architect their systems through its design framework. This descriptive design framework empowers designers with transparent control over the implementation of their system and infrastructure described at a high level.

RCMW is an FPGA infrastructure abstraction that targets platform portability by presenting a standard set of interfaces to user logic [51]. The interfaces presented are tailored for both burst-streaming access patterns and memory mapped patterns. Furthermore, RCMW provides a set of infrastructural components for data transfer and control, to and from the FPGA. This provides platform virtualization from both the host-processor and FPGA, however RCMW does not include virtualization support for internal FPGA resources and continues to promote a low-level load-store memory model.

FPGA "architectures" seek to conquer the programming problem by replicating the support that operating systems, and instruction set architectures bring to general-purpose processors. The LEAP architecture seeks to simplify FPGA application programming through memory and communication abstractions [4,98]. LEAP supports a latency insensitive channel as its communication primitive with abstract "named" send/receive endpoints. LEAP scratchpads present a virtual memory interface to FPGA designers with support for automatic cache hierarchy generation that includes the host processor's DRAM. LEAP further provides mechanisms for coherency among scratchpads. Both LEAP communication and memory primitives are low-level abstractions that increase portability. LEAP also provides support libraries as operating system services to aid in accelerator design for printouts, debugging, and synchronization [31].

LEAP was a key influence for the work in this thesis. LEAP scratchpad, coherent scratchpad memory and cache support is comprehensive; it could be used to underpin Fluid's read/write memory services. Working within LEAP, designers could have implemented higher level memory operations on top of their scratchpad memories, however LEAP did not explore this direction in their work. Fluid's methodology provides structure and semantics to encapsulate higher level memory abstractions and make them available to designers within the FPGA fabric. For example, Fluid encapsulates support for graph operations which are memory intensive and stress the memory infrastructure. LEAP's primary abstraction is communication and latency-insensitive channels. Latency-insensitive channels also could be used within Fluid's communication infrastructure. However, the key difference between Fluid and LEAP is in their design interface. Their interface, AWB, abstracts the channel and scratchpad implementation details, limiting the designer's input to platform choice. However, Fluid's design interface gives the designer transparent control over their implementation in the designer's high-level accelerator description. Fluid's design interface is much more descriptive and extensible compared to LEAP's AWB tool, owing its flexibility to Fluid's structured abstractions that allow hardware to easily be described in Python. AWB allowed the programmer to substitute implementations of functionalities such as platform interfaces, but it was very limited in its description capability. For example, Fluid's design tool enables the designer to transparently specify individual connection types and even build clean functions to abstract the construction of more complex infrastructure.

CoRAM simplifies FPGA programming by decoupling compute and control through a data management API [22,24]. The CoRAM architecture supports a data management API defined by SRAM blocks where software-defined control threads handle all transfers to/from SRAMs from/to memory. Compute kernels access these SRAMs with a memory-mapped interface. The CoRAM++ architecture extends the API to data-structure-specific commands and a FIFO interface to kernels [91]. The CoRAM++ architecture also enables supporting modules called agents that accelerate data-structure-specific memory commands. Fluid's methodology derives inspiration from CoRAM in decoupling compute kernels from memory and control. However, CoRAM lacks a proper communication abstraction forcing the designer to synchronize kernels through its software abstraction and explicit data transfers. This forces designers to implement kernels that handle communication internally, or communicate through memory similar to general-purpose processors. While memory is arguably the most important part of application design, it is only part of a bigger picture. Data movement is a large concern for efficient FPGA applications, and should be a principal focus of any abstraction. Fluid was influenced by CoRAM++ and preserves its goal of facilitating higher levels of abstraction for memory on the FPGA fabric. Fluid's design methodology supports designers to hierarchically develop and layer memory abstractions for FPGA computing. These abstractions include data-structure-specific memory access patterns—like CoRAM++—but also objects and containers, such as graphs and queues, abstracting their behavior and state. Fluid also enables processing within the memory system and provides support for communication between kernels outside of memory.

Researchers have also adapted operating system concepts to the FPGA design process [31,52,99]. Operating system abstractions provide a common layer of support across various FPGA devices and platforms. Memory support typically is the first level of concern in FPGA operating systems with configurations for virtual and cache coherent memory. This is important for heterogeneous processor-FPGA systems and FPGAs in the data center. While it is important and challenging to abstract memory interfaces and increase portability, FPGA operating systems remain low-level supporting the familiar load/store paradigm. Fluid's service-oriented abstraction encourages composability, encapsulation, dynamism, and high-level memory operations, richer than loads and stores, in addition to memory portability.

## 2.4 FPGA Communication Architectures

Messaging frameworks have been developed with the goal of providing a standard of communication for FPGA computing platforms. Previously mentioned as an FPGA memory architecture, LEAP also provides communication interfaces called soft connections [74]. Soft connections are used to decouple components and communicate data among them in an asynchronous, latency-insensitive model. Elastic silicon interconnects (ESI) is an abstraction that is also based on latency-insensitive communication similar to LEAP [27]. ESI is an interconnect generator that supports communication with software code and hypothesizes supporting their abstraction with standardized board support modules. Latency-insensitive connections allow flexible communication between modules and are a central tenet of the work in this thesis. Fluid is similarly based on abstract communication through latency-insensitive channels and abstracts platform interfaces with standardized interfaces. However, Fluid ascribes a functionality to each abstract channel and verifies that the correct modules providing and requesting this functionality are constructed. Connections between modules in the Fluid communication abstraction carry more semantic meaning beyond simply data-type compatibility.