### Peripheral and Power Management in Batteryless, Energy-Harvesting Systems

Submitted in partial fulfillment for the requirements for the degreee of Doctor of Philosophy in Electrical & Computer Engineering

Emily K. Ruppel

B.S., Electrical & Computer Engineering, University of Maryland, College Park M.S., Electrical & Computer Engineering, Carnegie Mellon University

> Carnegie Mellon University Pittsburgh, PA

> > August 2022

Copyright © Emily K. Ruppel, 2022. All Rights Reserved

#### Abstract

Batteryless, energy-harvesting devices enable deeply embedded sensing and computing deployments without the size, weight, or maintenance constraints of batteries. These devices harvest energy into a small capacitor bank to support short bursts of execution at a time, with power failures in between. Peripheral sensors and radios are essential to batteryless device deployments; they allow a device to sense and report information about its surroundings. However, peripherals trigger concurrent accesses to memory and account for a large percentage of the total device energy budget. The challenge for programmers is a tight coupling emerges between device hardware characteristics and application peformance. A software developer needs to have an understanding of both to write programs that behave as expected. This thesis reduces the burden of integrating peripherals into batteryless applications by managing the shared state between peripherals and the primary microcontroller.

We first address the problem of shared memory between peripheral triggered interrupts and a program's main loop by defining a programming model that prevents concurrency control violations due to power failures. Peripheral operations also affect the state of the system by changing the total operating power, e.g. by turning a sensor on or off. We demonstrate that peripheral mismanagement leads to a new class of energy bugs that cause hard-stop failures and waste energy in batteryless systems. To correct these bugs, we model changes in peripheral power over a program's execution. However, peripheral power does not fully capture the hardware state of the device. A device's power system characteristics also determine when it is safe to access a peripheral. Using a lightweight model of the power system, we correct existing scheduling algorithms for batteryless devices to accommodate high-current peripherals on volume-constrained systems. Finally, we apply the lessons learned throughout this thesis to develop the failure-aware hardware and software support for a miniature batteryless satellite. The ease with which we integrate failure-agnostic peripheral subsystems demonstrates the value of power and peripheral management in batteryless devices.

#### Acknowledgments

This thesis was made possible by the guidance, curiosity and encouragement of far more people than I can reasonably name. First, I would like to thank my advisor, Brandon Lucia, for his mentorship throughout my PhD. Brandon's enthusiasm is infectious, and my approach to research has been shaped by his willingness to shoot for the moon, literally and figuratively. Beyond guiding my research, Brandon was extremely generous with his time and effort. Whether I was learning to write papers, give talks, or interact with the research community, he was there every step of the way. So thanks for everything– for the professional opportunities, the travel, the debates about Pittsburgh coffee shops and for setting an excellent example.

This thesis sits at the intersection of several fields of research, and the members of my committee have been invaluable in navigating these spaces. Limin Jia's feedback on many a paper-draft has ironed out any number of unstated assumptions and pushed me to actually think about the shape of a paragraph. I greatly appreciate Josiah Hester's enthusiasm and advice when pivoting portions of this thesis to the world of ubiquitous computing. Thanks to Anthony Rowe for encouraging me to consider how batteryless systems fit into the wider world of sensing. And thanks for convincing me to get started on the next chapter of my career while finishing up this one. Portions of this thesis might still be in bulleted form without the resulting clarity and time sequestered on an airplane.

Beyond my committee, I was supported in graduate school by many members of the Carnegie Mellon community. I want to start by thanking all the members of the ABSTRACT research group for providing thought-provoking questions, feedback and camaraderie. Special thanks to Alexei Colin for pulling me into the world of hardware prototyping and showing me what it means to carry out a top-notch evaluation. Thanks to the other early ABSTRACT members, Kiwan Maeng and Vignesh Balaji, for their steadfast presence during many paper deadlines and conferences. Thanks to Milijana Surbatovich for patiently describing the syntax for formal modeling no matter how many times I asked and for the succinct writing that brought Culpeo to life. Thanks to Harsh Desai for the whiteboard-sessions about all things hardware and for the many conversations beyond MCUs. Thanks to Brad Denby for sharing his enthusiasm for satellites. Thanks to Nathan Serafin for his attention to detail, especially in last minute design reviews. Thanks to Graham Gobieski, McKenzie van der Hagen and Souradip Ghosh for being excellent travel companions. More broadly, I want to thank the many participants of the weekly lunch meetings. Thanks to Nathan Beckmann for his thoughtful, direct questions about this work and to the members of the CORGI research group. In particular, Brian Schwedock and Sara McAllister have listened to and provided feedback on so many talks, even as my work veered far from anything that looked like a cache. I would also be remiss if I did not acknowledge the actual corgis (Arya and Baphomet) for being delightful.

Thanks to the many CMU students, faculty and staff I have learned from, whether it was inside or outside of a classroom. Thank you to the talented students outside of ABSTRACT with whom I have collaborated, including Vaibhav Singh, Mara Kirdani-Ryan, Chad Taylor, Shize Che and Fayyaz Zaidi. Beyond direct collaboration, thanks to the members of the WiTech and WiSE labs for accommodating my inevitably last minute requests to fill tool or wireless knowledge gaps, Artur Balanuta, Elahe Soltanaghai, Akarsh Prabhakara, John Miller, Akshay Gadre, Atul Bansal, Jingxian Wang and Junbo Zhang. Special thanks to Diana Zhang and Adwait Dongare for being a remote well of laughs, cooking know-how, and RF intuition. The many denizens of the fourth floor of the CIC always offered stimulating conversations over coffee, especially Ankur Mallick, Samarth Gupta, Rachata Ausavarungnirun, Saughata Ghose and Utsav Drolia. Thanks to the members of EGO for their dedication to getting graduate students to talk to each other, especially Joe Melber, Elliott Binder, Mark Blanco, Mohammad Bakhshalipour, Anuva Kulkarni and Thom Popovici. I am grateful that Michael Kleyman, Brad Johnson, Kim Jin, Shannon Gallagher, Abby Smith and Robin Dunn got me out of the lab on many occasions. Thanks to Dimitrios Skarlatos and Akshitha Sriraman for the sage job advice exactly when I needed to hear it.

Beyond the Carnegie Mellon community, this work would not have happened without professional support from many sources. This work was funded by the National Science Foundation and the Semiconductor Research Corporation (SRC)<sup>1</sup>. Within SRC, the CONIX research center facilitated many opportunities to interact with students from across the country. The Computer Architecture Student Asso-

<sup>&</sup>lt;sup>1</sup>This work was supported by National Science Foundation Award #1751029 and the CONIX Research Center, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA.

ciation provided wonderful connections to other students while conferences were on pause for the COVID-19 pandemic. My early research mentors in and around Maryland, including Bruce Jacob, Robert Newcomb and Allen Goldstein, showed me what research can be. Numerous internship mentors shaped me as an engineer and taught me how to communicate across different levels of the stack, among them are Jim Blair, Tige Young, Stephen Glancy, Dave Cadigan, Rona Yaari, Supreet Jeloka and Brian Cline. Thanks to Tom Puzak for showing me around IBM Watson and kindling my interest in industry research. Finally, thanks to the members of the Gemstone Team BIKES for showing me what Terps can accomplish if they simply refuse to quit.

I am deeply grateful to the friends and family who provided the non-academic support that enabled this thesis. Thanks to LeAnne Young, Tammy Walsky and all of the friends from Maryland who could make a brief dinner or run between semesters feel like home. Thank you to all of the people who adventured around Pittsburgh with me, whether running, biking, backpacking, brewery hopping or a combination thereof. In particular, I want to thank Jen Brown, Megan Sharretts, Kristin Yahner, Tom Weir, Heather Adams, Nate Nypaver, Shawn Kelly, Barrie Slaymaker, Joanna Wolfe, Julie and Brett Lynch for always putting things in perspective.

Most importantly, none of this work would have been possible without the unfailing support of my family. Tom, thank you for being my sounding board, rubber duck and most trusted source on how a transistor works. In all seriousness, your love and encouragement through the highs and lows of this process mean the world to me. Thank you to my twin, Abbie, for showing me how much fun Pittsburgh could be in the first place, and for demonstrating that success is primarily living life to the fullest. Thanks to my grandmother, Helen, and my extended family for their continued support, no matter how long it seemed I would be in school. Finally, I want to thank my parents, Joe and Lisa, for encouraging a meticulous and inquisitive mindset that started with dissecting Harry Potter and has culminated in this thesis. Thank you for being in my corner from the beginning.

## Contents

| 1        | Intr | oduct   | ion                                               | 1         |

|----------|------|---------|---------------------------------------------------|-----------|

|          | 1.1  | Peripl  | herals in Batteryless Devices                     | 3         |

|          | 1.2  | Thesis  | s Statement & Contributions                       | 5         |

|          | 1.3  | Outlir  | ne                                                | 6         |

| <b>2</b> | Bac  | kgrou   | nd                                                | 9         |

|          | 2.1  | Intern  | nittent Execution                                 | 9         |

|          | 2.2  | Softwa  | are Support for Intermittent Execution            | 12        |

|          | 2.3  | Energ   | y Harvesting Power Systems                        | 14        |

|          | 2.4  | Enabl   | ing Peripherals                                   | 16        |

|          | 2.5  | Hardv   | vare/Software Co-Design for Peripherals           | 18        |

|          |      | 2.5.1   | Peripheral Constraints                            | 18        |

|          |      | 2.5.2   | Capybara Design                                   | 19        |

| 3        | Cor  | ncurrei | ncy Control for Task-Based Intermittent Execution | <b>23</b> |

|          | 3.1  | Motiv   | ation                                             | 25        |

|          |      | 3.1.1   | Concurrency in Embedded Devices                   | 26        |

|          |      | 3.1.2   | Benefits of Interrupts in Intermittent Systems    | 27        |

|          | 3.2  | The C   | Challenge of Intermittent                         |           |

|          |      | Event   | -Driven Concurrency                               | 28        |

|          |      | 3.2.1   | Interrupts + Intermittent Operation               | 28        |

|          |      | 3.2.2   | Synchronization + Privatization                   | 30        |

|          | 3.3  | Intern  | nittent Interrupts with Coati                     | 31        |

|          |      | 3.3.1   | Interaction Between Tasks and Events              | 33        |

|          |      | 3.3.2   | Multi-Task Transactional Execution                | 34        |

|          | 3.4  | Imple   | mentation Details                                 | 35        |

|   |                                               | 3.4.1                                                                                                                                     | Control Flow                           | 35                                                                                                                                                                     |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                               | 3.4.2                                                                                                                                     | Memory Access                          | 37                                                                                                                                                                     |

|   |                                               | 3.4.3                                                                                                                                     | Commit                                 | 38                                                                                                                                                                     |

|   | 3.5                                           | Buffi: A                                                                                                                                  | A Buffering-Based Alternative          | 39                                                                                                                                                                     |

|   |                                               | 3.5.1                                                                                                                                     | Buffering and Serialization            | 39                                                                                                                                                                     |

|   |                                               | 3.5.2                                                                                                                                     | Buffi Transactions                     | 39                                                                                                                                                                     |

|   |                                               | 3.5.3                                                                                                                                     | Buffi Implementation                   | 40                                                                                                                                                                     |

|   |                                               | 3.5.4                                                                                                                                     | Buffer Design                          | 42                                                                                                                                                                     |

|   | 3.6                                           | Evaluat                                                                                                                                   | ion                                    | 42                                                                                                                                                                     |

|   |                                               | 3.6.1                                                                                                                                     | Benchmarks and Methodology             | 42                                                                                                                                                                     |

|   |                                               | 3.6.2                                                                                                                                     | Correctness                            | 44                                                                                                                                                                     |

|   |                                               | 3.6.3                                                                                                                                     | Programming Effort                     | 45                                                                                                                                                                     |

|   |                                               | 3.6.4                                                                                                                                     | Events Captured                        | 45                                                                                                                                                                     |

|   |                                               | 3.6.5                                                                                                                                     | Performance                            | 46                                                                                                                                                                     |

|   | 3.7                                           | Related                                                                                                                                   | Work                                   | 48                                                                                                                                                                     |

|   | 3.8                                           | Conclus                                                                                                                                   | $\operatorname{sion}$                  | 50                                                                                                                                                                     |

|   |                                               |                                                                                                                                           |                                        |                                                                                                                                                                        |

| 4 | DI                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                     | and Annal Branch and English and Decar | ۳ ۵                                                                                                                                                                    |

| 4 |                                               | 00 0                                                                                                                                      | and Avoiding Peripheral Energy Bugs    | 53                                                                                                                                                                     |

| 4 | <b>Deb</b><br>4.1                             | Reducin                                                                                                                                   | ng Peripheral Costs                    | 55                                                                                                                                                                     |

| 4 |                                               | Reducin<br>4.1.1                                                                                                                          | ng Peripheral Costs                    | 55<br>55                                                                                                                                                               |

| 4 | 4.1                                           | Reducin<br>4.1.1<br>4.1.2                                                                                                                 | ng Peripheral Costs                    | 55<br>55<br>56                                                                                                                                                         |

| 4 |                                               | Reducin<br>4.1.1<br>4.1.2<br>Problem                                                                                                      | ng Peripheral Costs                    | 55<br>55<br>56<br>58                                                                                                                                                   |

| 4 | 4.1                                           | Reducin<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1                                                                                             | ng Peripheral Costs                    | 55<br>55<br>56<br>58<br>59                                                                                                                                             |

| 4 | 4.1                                           | Reducin<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2                                                                                    | ng Peripheral Costs                    | 55<br>55<br>56<br>58<br>59<br>60                                                                                                                                       |

| 4 | 4.1                                           | Reducin<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3                                                                           | ng Peripheral Costs                    | 55<br>55<br>56<br>58<br>59<br>60<br>62                                                                                                                                 |

| 4 | 4.1                                           | Reducin<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C                                                                 | ng Peripheral Costs                    | <ol> <li>55</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>62</li> </ol>                                                                         |

| 4 | 4.1                                           | Reducin<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C<br>4.3.1                                                        | ng Peripheral Costs                    | <ol> <li>55</li> <li>55</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>62</li> <li>63</li> </ol>                                                 |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | Reducii<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C<br>4.3.1<br>4.3.2                                               | ng Peripheral Costs                    | 555<br>556<br>558<br>59<br>60<br>62<br>62<br>63<br>64                                                                                                                  |

| 4 | 4.1                                           | Reducii<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C<br>4.3.1<br>4.3.2<br>Pudu D                                     | ng Peripheral Costs                    | <ol> <li>55</li> <li>55</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>62</li> <li>63</li> <li>64</li> <li>64</li> </ol>                         |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | Reducin<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C<br>4.3.1<br>4.3.2<br>Pudu D<br>4.4.1                            | ng Peripheral Costs                    | <ol> <li>55</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>62</li> <li>63</li> <li>64</li> <li>64</li> <li>64</li> </ol>                         |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | Reducia<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C<br>4.3.1<br>4.3.2<br>Pudu C<br>4.4.1<br>4.4.2                   | ng Peripheral Costs                    | <ul> <li>55</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>62</li> <li>63</li> <li>64</li> <li>64</li> <li>64</li> <li>64</li> </ul>             |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | Reducin<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C<br>4.3.1<br>4.3.2<br>Pudu C<br>4.4.1<br>4.4.2<br>4.4.3          | ng Peripheral Costs                    | <ul> <li>55</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>62</li> <li>63</li> <li>64</li> <li>64</li> <li>64</li> <li>66</li> <li>69</li> </ul> |

| 4 | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul> | Reducii<br>4.1.1<br>4.1.2<br>Problem<br>4.2.1<br>4.2.2<br>4.2.3<br>Pudu C<br>4.3.1<br>4.3.2<br>Pudu C<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.3 | ng Peripheral Costs                    | <ul> <li>55</li> <li>56</li> <li>58</li> <li>59</li> <li>60</li> <li>62</li> <li>62</li> <li>63</li> <li>64</li> <li>64</li> <li>64</li> <li>64</li> </ul>             |

|   |     | 4.5.1  | Hardware Setup                                                                                                                                                           |

|---|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 4.5.2  | Peripheral-Energy Bug Analysis                                                                                                                                           |

|   |     | 4.5.3  | Performance Benchmarks                                                                                                                                                   |

|   | 4.6 | Evalu  | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$                                                                                        |

|   |     | 4.6.1  | Prevalence of Intermittent Peripheral Energy Bugs 77                                                                                                                     |

|   |     | 4.6.2  | BrickBugs Case Studies                                                                                                                                                   |

|   |     | 4.6.3  | Pudu is Effective Against BrickBugs                                                                                                                                      |

|   |     | 4.6.4  | Pudu eliminates energy-waste due to BurnBugs 83                                                                                                                          |

|   |     | 4.6.5  | Pudu Supports Complex Applications    85                                                                                                                                 |

|   | 4.7 | Relate | ed Work                                                                                                                                                                  |

|   | 4.8 | Concl  | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $89$                                                                                                         |

| 5 | Cha | arge M | anagement for High Load Peripherals 91                                                                                                                                   |

|   | 5.1 | -      | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $ 94$                                                                                                                          |

|   |     | 5.1.1  | ESR Induced Voltage Drops                                                                                                                                                |

|   |     | 5.1.2  | Disregarding Voltage Breaks Past Systems                                                                                                                                 |

|   | 5.2 | Culpe  | o Overview                                                                                                                                                               |

|   |     | 5.2.1  | Defining $V^{safe}$ and $V^{\delta}$                                                                                                                                     |

|   |     | 5.2.2  | Capturing $V^{safe}$ and $V^{\delta}$                                                                                                                                    |

|   |     | 5.2.3  | Applying $V^{safe}$ and $V^{\delta}$                                                                                                                                     |

|   | 5.3 | Culpe  | o Design                                                                                                                                                                 |

|   |     | 5.3.1  | Modeling the Power System                                                                                                                                                |

|   |     | 5.3.2  | Culpeo-PG $V^{safe}$ Calculation                                                                                                                                         |

|   |     | 5.3.3  | Culpeo-R Calculation                                                                                                                                                     |

|   |     | 5.3.4  | Culpeo-R Implementation                                                                                                                                                  |

|   | 5.4 | Metho  | dology                                                                                                                                                                   |

|   |     | 5.4.1  | $V^{\sf safe}$ Evaluation                                                                                                                                                |

|   |     | 5.4.2  | Application-Level Comparison                                                                                                                                             |

|   | 5.5 | Evalu  | ation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $115$                                                                                      |

|   |     | 5.5.1  | Culpeo's $V^{safes}$ are Accurate $\ldots \ldots \ldots$ |

|   |     | 5.5.2  | $V^{safe}$ Fixes Schedulers $\ldots \ldots 117$                               |

|   |     | 5.5.3  | Culpeo Corrects Applications                                                                                                                                             |

|   | 5.6 | Relate | ed Work                                                                                                                                                                  |

|   | 5.7 | Concl  | usion                                                                                                                                                                    |

| 6  | Cas   | se Study: Supporting Peripherals in a Batteryless Satellite | 123 |

|----|-------|-------------------------------------------------------------|-----|

|    | 6.1   | Implementing a Batteryless Nanosatellite                    | 125 |

|    |       | 6.1.1 TA-1 Overview                                         | 126 |

|    |       | 6.1.2 Peripheral Interface                                  | 128 |

|    | 6.2   | Artibeus Power System                                       | 129 |

|    | 6.3   | Artibeus Control Module                                     | 131 |

|    | 6.4   | Conclusion                                                  | 134 |

| 7  | Cor   | nclusion & Future Work                                      | 137 |

|    | 7.1   | Towards Performant Batteryless Hardware                     | 137 |

|    |       | 7.1.1 Reliability Testing                                   | 137 |

|    |       | 7.1.2 Supercapacitor-based Systems                          | 139 |

|    | 7.2   | Towards an Operating System                                 | 141 |

|    |       | 7.2.1 Expanding Concurrency                                 | 141 |

|    | 7.3   | Towards Wide-Scale System Integration                       | 145 |

|    | 7.4   | Recurring Themes                                            | 149 |

| Bi | bliog | graphy                                                      | 153 |

# List of Figures

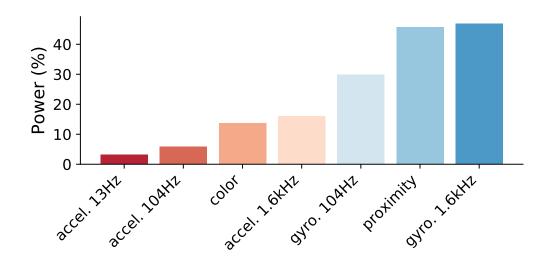

| 1.1 | Peripheral Power Percentage. The peripherals on a Capybara                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | device consume a large percentage of the total power, but there is a wide range based on the exact peripheral configuration.                                                                                                                                                                                                                                                                                                                                                                         | 5  |

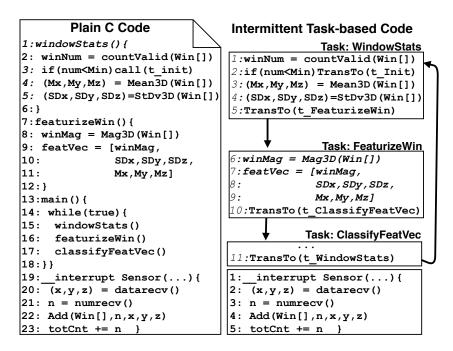

| 2.1 | Activity Recognition code. The code at right translates the C code at left into task-based code for intermittent execution.                                                                                                                                                                                                                                                                                                                                                                          | 10 |

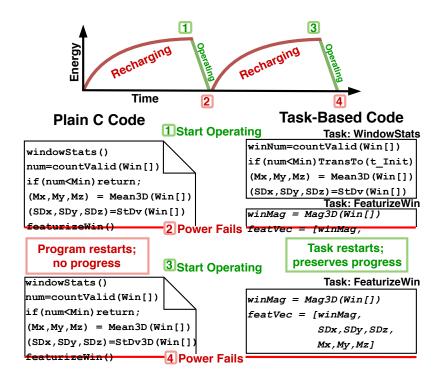

| 2.2 | Plain C code vs intermittent task-based code. Task-based code makes progress despite power failures.                                                                                                                                                                                                                                                                                                                                                                                                 | 11 |

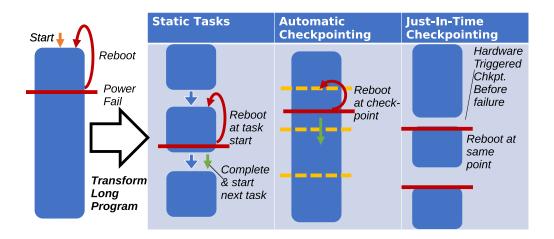

| 2.3 | Software Support for Intermittent Execution. Strategies for intermittent computing all divide a long running program into shorter segments, but they vary in their hardware and programmer requirements.                                                                                                                                                                                                                                                                                             | 12 |

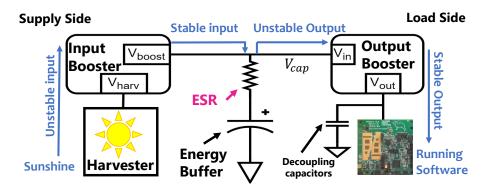

| 2.4 | Annotated power system schematic. The supply side harvests<br>energy into the energy buffer that the output booster accesses to<br>provide a stable voltage to the load                                                                                                                                                                                                                                                                                                                              | 15 |

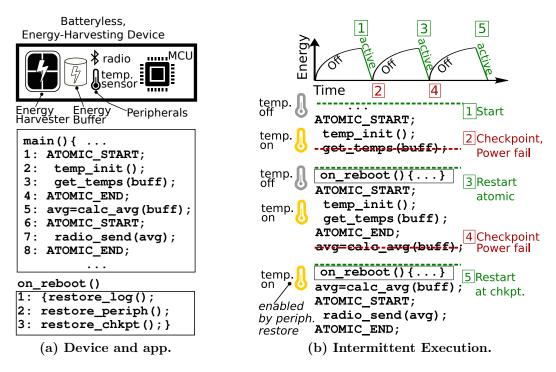

| 2.5 | <b>Batteryless Device Example Execution.</b> A batteryless device<br>supports peripherals, even though it experiences frequent power fail-<br>ures, using software support. The example code, shown left, executes<br>intermittently on the right with JIT checkpoints to preserve progress.<br>After each power failure (red, dashed lines), and corresponding restarts<br>(green dashed lines), the sensor's operating mode is restored and the<br>program resumes from the most recent checkpoint | 17 |

| 2.6 | Capybara hardware prototype. The MCU, and peripherals are                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | on the front side (left), and the power system with reconfigurable capacitor banks is on the back (right).                                                                                                                                                                                                                                                                                                                                                                                           | 18 |

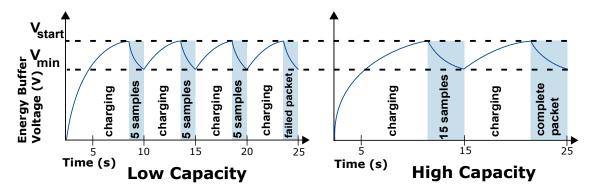

| 2.7 | <b>Execution with a low or high fixed capacity buffer.</b> Small energy buffers support frequent sensing, but not high energy operations. Large energy buffers support high energy operations, but are powered off for long periods of time while recharging. | 19 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

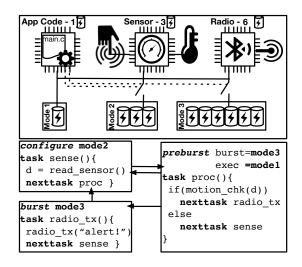

| 2.8 | <b>Overview of Capybara</b> . The platform has resources for computa-<br>tion, sensing, and communication. An example program has tasks<br>annotated with energy mode requirements.                                                                           | 20 |

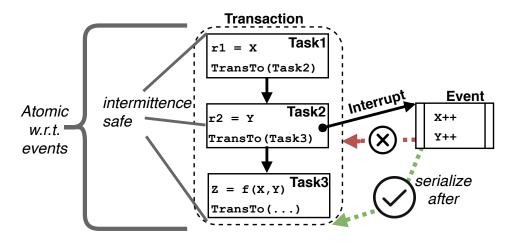

| 3.1 | <b>Coati program.</b> The program contains three tasks encapsulated in a transaction and an asynchronous event. The event cannot violate the atomicity of the transaction.                                                                                    | 25 |

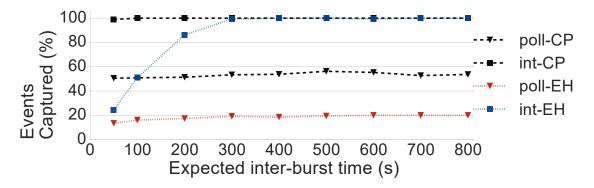

| 3.2 | Interrupts support bursts of events. Using<br>terrupts, the simulated energy harvesting device (int-EH) outperforms<br>the continuously powered, polling baseline (poll-CP) if there is time<br>to recharge between bursts                                    | 28 |

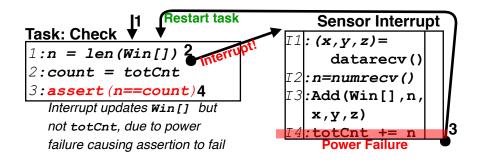

| 3.3 | The "Interrupt Interrupted" problem. The interrupt updates Win[]'s length without updating totCnt, leaving the two inconsistent.                                                                                                                              | 29 |

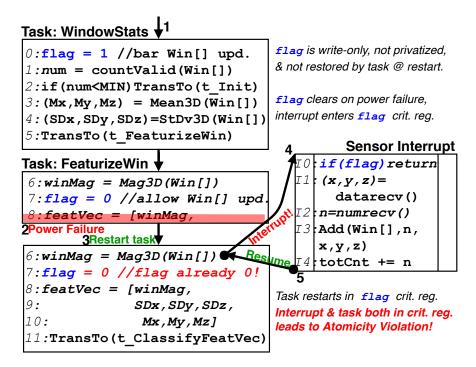

| 3.4 | The "False Flag" problem. When power fails after FeaturizeWin clears flag, the task and the interrupt are both in the critical region, violating atomicity.                                                                                                   | 31 |

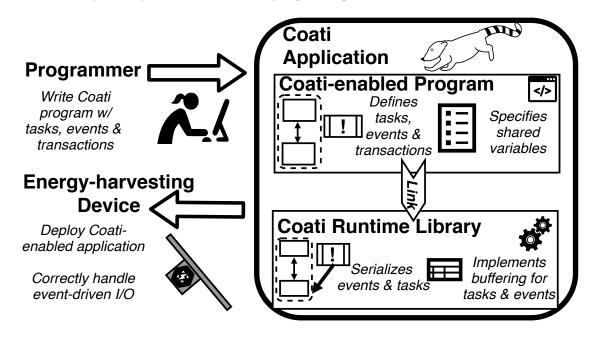

| 3.5 | <b>Overview of Coati.</b> The programmer codes using Coati primitives and links the Coati-enabled program to the Coati runtime, handling both intermittence and interrupts so the app executes correctly when deployed                                        | 32 |

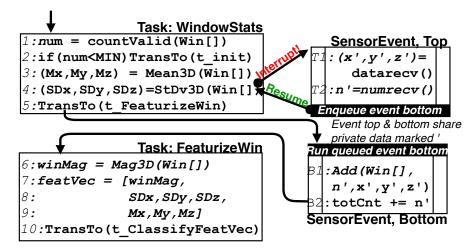

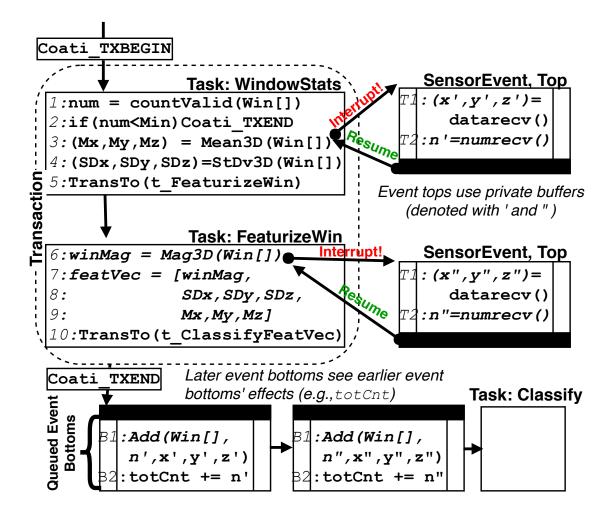

| 3.6 | Task and split-phase event interaction. Split-phase events are separated into a top half which executes immediately, and a bottom half which runs after the interrupted task commits.                                                                         | 33 |

| 3.7 | A transaction using split-phase serialization. Each time a sensor event occurs, the top half captures data and enqueues a bottom                                                                                                                              |    |

|     | half to execute after the transaction.                                                                                                                                                                                                                        | 36 |

| 3.8 | <b>Task &amp; buffered event interaction.</b> Buffered serialization forces tasks to restart after an event. If the event interrupts a transaction, only the interrupted <i>task</i> must restart.                                                            | 40 |

|     | $omy \text{ uncharged use must result. } \dots $                                                                                                        | 40 |

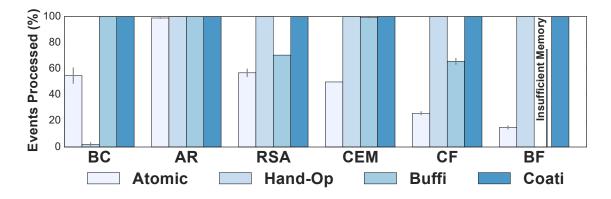

| 3.9  | Events Captured. Under harvested energy, Coati consistently pro-                          |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | cessed 100% of the events that occurred while the device was powered                      |    |

|      | on                                                                                        | 46 |

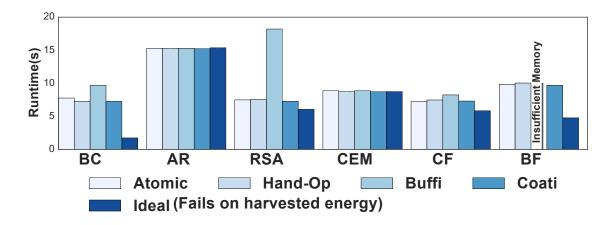

| 3.10 | Runtime on continuous power. For applications that are bound                              |    |

|      | by event arrival frequency, Coati performs as well as the ideal baseline.                 | 47 |

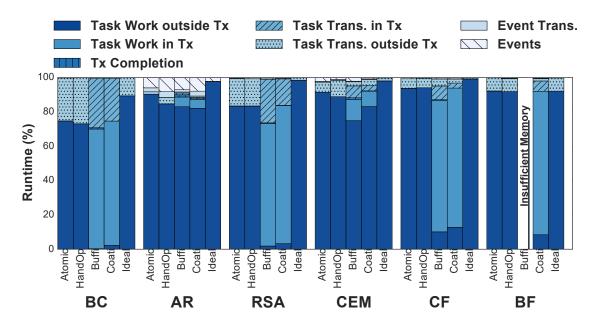

| 3.11 | Breakdown of runtime usage. The runtime usage varies across                               |    |

|      | the benchmark applications. The intermittent failure-safe systems all                     |    |

|      | incur additional buffering and commit overhead compared to the ideal                      |    |

|      | baseline                                                                                  | 48 |

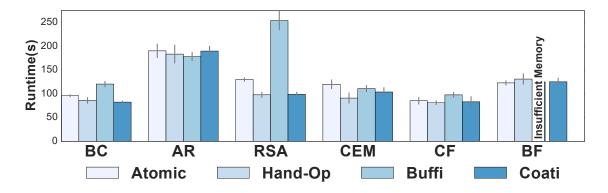

| 3.12 | Runtime on harvested energy. Coati's performance is comparable                            |    |

|      | to Hand-Op's without the additional programming overhead                                  | 49 |

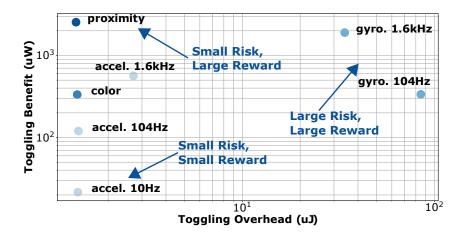

| 4.1  | Peripheral Design Space. This graph compares the toggling cost                            |    |

|      | and benefit for different peripheral sensors and (where applicable)                       |    |

|      | different sampling rates on a single device. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 56 |

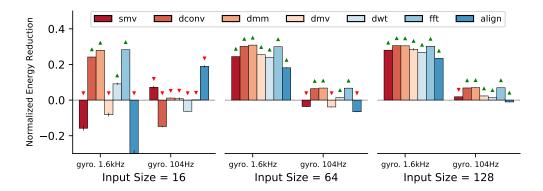

| 4.2  | Toggled vs No-Toggle. The graphs show the normalized energy                               |    |

|      | reduction of toggled applications.                                                        | 57 |

| 4.3  | Sensing Energy. As sensing energy decreases there is more energy                          |    |

|      | savings available to capture                                                              | 58 |

| 4.4  | Peripheral Toggling Cost. "T" indicates a program that toggles                            |    |

|      | off the gyroscope around the computation, "NT" leaves the gyro                            |    |

|      | enabled. The relative cost to toggle a peripheral varies depending on                     |    |

|      | the library code called and arguments passed. Minute changes in code                      |    |

|      | can result in large changes in the energy breakdown.                                      | 60 |

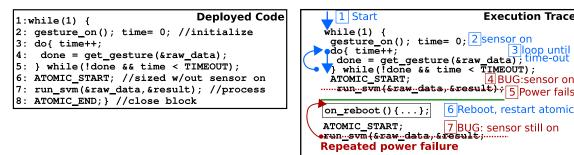

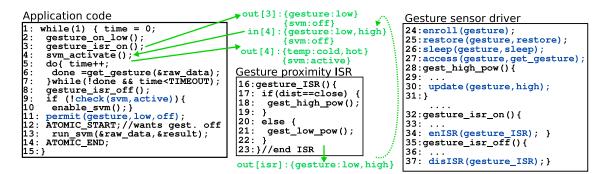

| 4.5  | Gesture Detector Bug. get_gesture quietly disables the sensor                             |    |

|      | if valid data are captured, but if the loop exits via the time-out, the                   |    |

|      | sensor will be active in the atomic block and exhaust the energy buffer.                  | 61 |

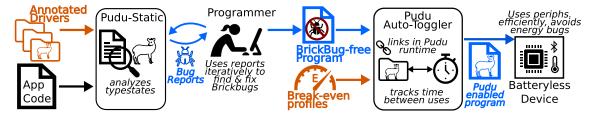

| 4.6  | Pudu Overview. Pudu uses annotated driver code, peripheral break-                         |    |

|      | even profiles and source code to produce BrickBug reports and instru-                     |    |

|      | mented app code without BurnBugs                                                          | 63 |

| 4.7  | Example code annotated for Pudu. An improved gesture detec-                               |    |

|      | tion application code example uses Pudu's checking annotations and                        |    |

|      | relies on a Pudu annotated driver (shown in blue). The effects of the                     |    |

|      | gesture ISR on the output of the Pudu pass are shown in green                             | 66 |

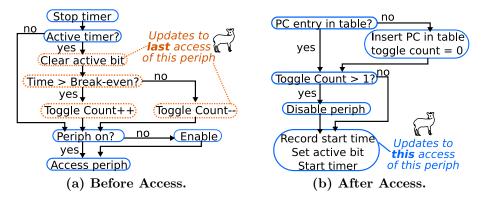

| 4.8  | Pudu Auto-Toggle Instrumentation. Before an access, Pudu                            |    |

|------|-------------------------------------------------------------------------------------|----|

|      | updates the toggling decision for the $last$ access to the peripheral               |    |

|      | in use. After the access, Pudu acts on the toggling decision for the                |    |

|      | current access.                                                                     | 70 |

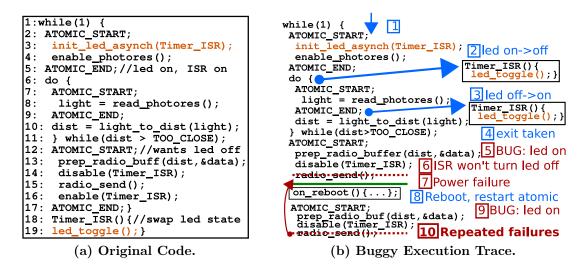

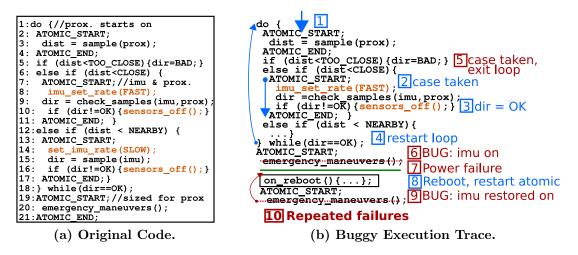

| 4.9  | Concurrent Changes. Peripheral state changes, shown in orange,                      |    |

|      | in asynchronous events can cause BrickBugs.                                         | 80 |

| 4.10 | Multiple Peripherals. BrickBugs are likely if multiple peripherals                  |    |

|      | are active simultaneously                                                           | 81 |

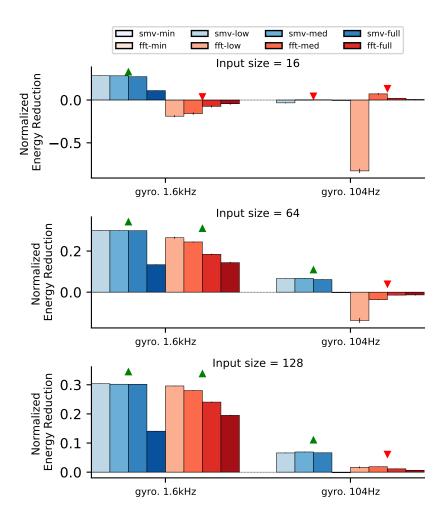

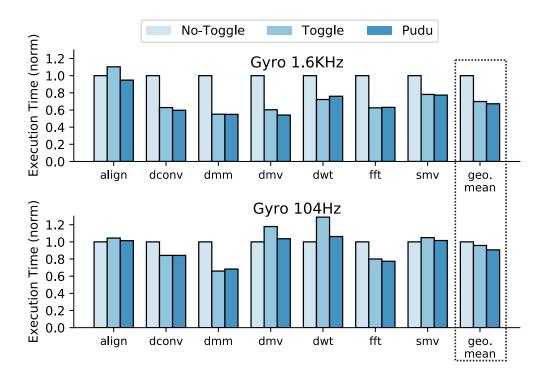

| 4.11 | Benchmark Study. The graph compares execution time across                           |    |

|      | different toggling strategies normalized to No-Toggle. Pudu Auto-                   |    |

|      | Toggle adapts to changes in peripheral modes and kernel runtimes,                   |    |

|      | avoiding slowdowns when static decisions are wrong                                  | 84 |

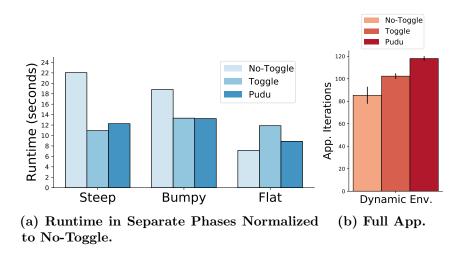

| 4.12 | Robot Motion Case Study. Pudu avoids slowdowns from static                          |    |

|      | toggling decisions in each app phase,(a), lower is better. Under                    |    |

|      | dynamic conditions,(b), Pudu increases the work completed in a fixed                |    |

|      | time, higher is better.                                                             | 87 |

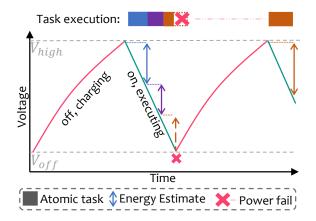

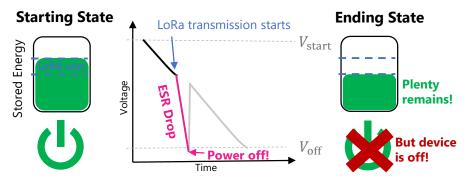

| 5.1  | Capacitor voltage over time in an intermittent execution.                           |    |

|      | Consuming energy lowers the voltage level; if it drops below $V^{\text{off}}$ , the |    |

|      | device powers off.                                                                  | 92 |

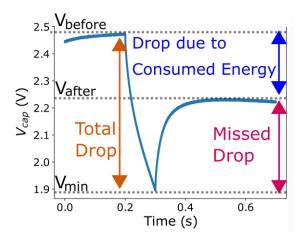

| 5.2  | Voltage vs. time in high ESR supercapacitors. In batteryless                        |    |

|      | devices with high ESR supercapacitors, considering only energy misses               |    |

|      | a key voltage drop that can lead to unexpected power failures. $\  \   . \   .$     | 93 |

| 5.3  | Voltage vs. Energy. Voltage drop due to ESR can cause the device                    |    |

|      | to power down even when there is plenty of stored energy                            | 95 |

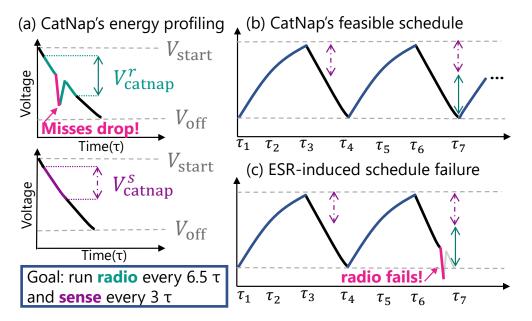

| 5.4  | Catnap Protocol. CatNap's feasibility test will lead to failed exe-                 |    |

|      | cutions                                                                             | 97 |

| 5.5  | Safe voltage estimates from prior work. Estimating the safe                         |    |

|      | voltage at which to run a task by energy costs alone results in wildly              |    |

|      | incorrect predictions. Depending on the implementation, voltage-                    |    |

|      | based energy approximations like CatNap can fare better, but are                    |    |

|      | highly dependent on the implementation.                                             | 98 |

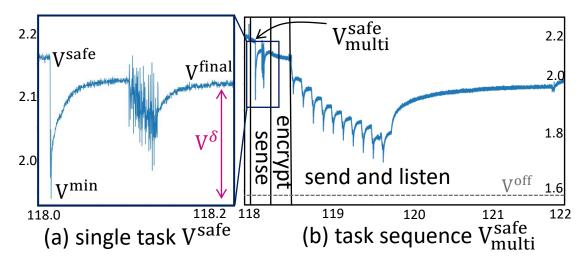

| 5.6  | Culpeo Definitions. $V^{safe}$ guarantees that a task will complete, but                                                                                                                                                                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | the $V^{\delta}$ parameter is required to calculate $V_{multi}^{safe}$ , a safe voltage for a                                                                                                                                                                                                           |

|      | sequence of tasks                                                                                                                                                                                                                                                                                       |

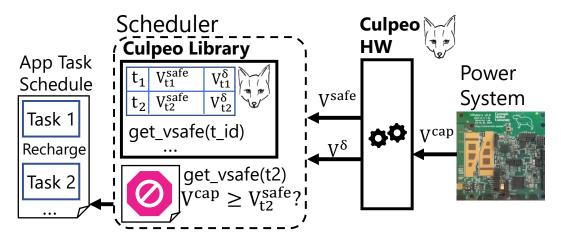

| 5.7  | Culpeo Integration. Culpeo is integrated with a scheduler using                                                                                                                                                                                                                                         |

|      | the Culpeo hardware and software components                                                                                                                                                                                                                                                             |

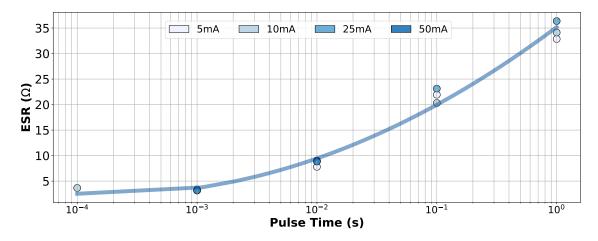

| 5.8  | <b>ESR versus pulse width.</b> This graph shows the change in ESR with pulse width, and its logarithmic fit, for Capybara's capacitor                                                                                                                                                                   |

|      | 45mF bank                                                                                                                                                                                                                                                                                               |

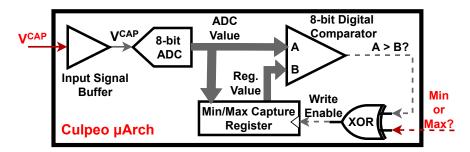

| 5.9  | Culpeo $\mu$ Arch The Culpeo $\mu$ Arch is a low overhead design that uses<br>an 8-bit ADC, a comparator and a single register to track capacitor<br>voltage for Culpeo-R. Red arrows indicate inputs, solid arrows are<br>analog signals, dashed arrows are boolean and wide arrows are 8-bit<br>buses |

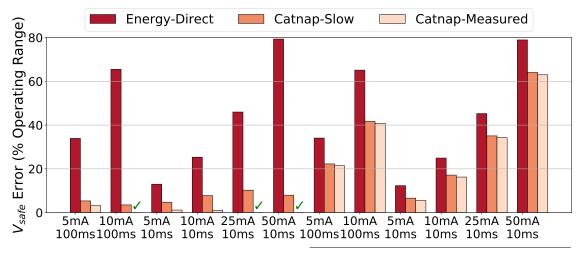

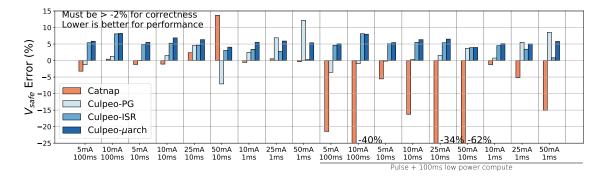

| 5.10 | $V^{safe}$ Error. The $V^{safe}$ estimates produced by CatNap and other                                                                                                                                                                                                                                 |

|      | energy-based methods produce radically incorrect estimates. Culpeo (both static and dynamic) produce safe (> 0) and performant (<10% error) estimates                                                                                                                                                   |

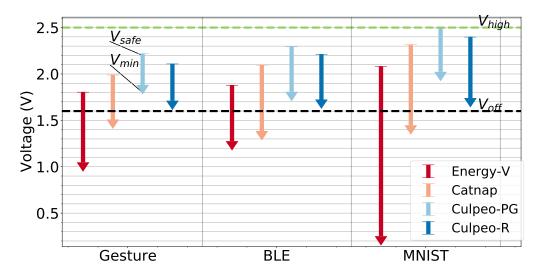

| 5.11 | $V^{safe}$ Accuracy on Real Peripherals. Culpeo-R and Culpeo-PG's $V^{safes}$ (arrow tops) result in $V^{min}$ (arrow points) above $V^{off}$ for tests on three real peripherals. The Energy and CatNap $V^{safe}$ estimates are                                                                       |

|      | unsafe                                                                                                                                                                                                                                                                                                  |

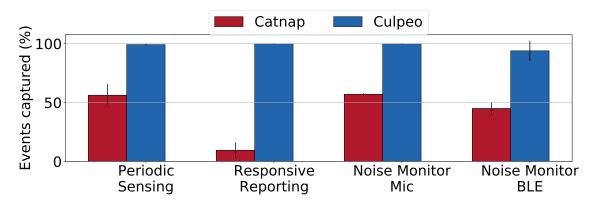

| 5.12 | <b>Events Captured.</b> Culpeo's accurate $V^{safe}$ estimates enable high event capture rates where CatNap's estimates cause it to fail 118                                                                                                                                                            |

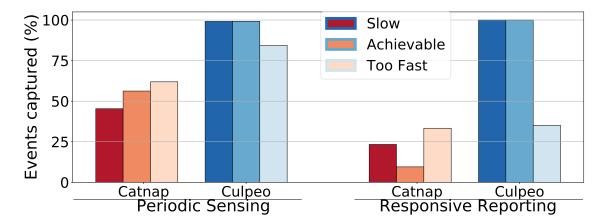

| 5.13 | <b>Events Captured vs. Event Frequency.</b> Culpeo has nearly ideal event capture for achievable event rates, but CatNap discharges the capacitor too low while performing background work and inverts the expected improvements                                                                        |

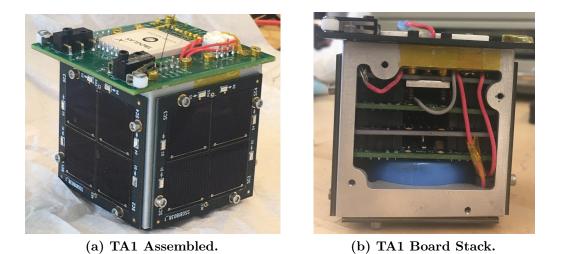

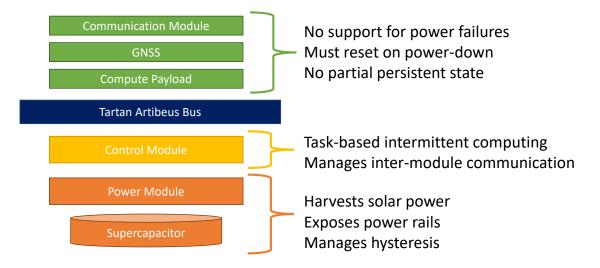

| 6.1  | <b>TA-1 Satellite.</b> TA-1's modular stacking design (visible at right in                                                                                                                                                                                                                              |

|      | a prototype) easily integrates new payloads                                                                                                                                                                                                                                                             |

| 6.2  | <b>TA-1 Module Stack.</b> TA-1 separates the failure-aware components from the failure-agnostic components using the Tartan-Artibeus Bus                                                                                                                                                                |

|      | interface                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                                                                                                                                                                                         |

| 6.3 | TA-1 hardware. TA-1 circuit boards, aluminium chassis and FR4          |    |

|-----|------------------------------------------------------------------------|----|

|     | base plate                                                             | 28 |

| 6.4 | TA-1 hardware stack. Stack of TA-1 circuit boards and superca-         |    |

|     | pacitor                                                                | 28 |

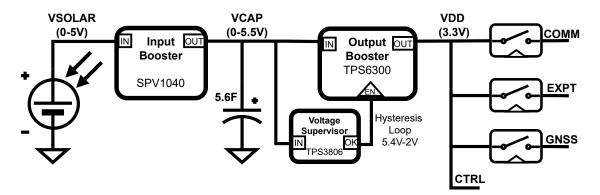

| 6.5 | <b>TA-1 Power System.</b> The TA-1 power system harvests solar power   |    |

|     | into a 5.6 F supercapacitor and uses separate voltage rails to support |    |

|     | isolated peripheral subsystems                                         | 30 |

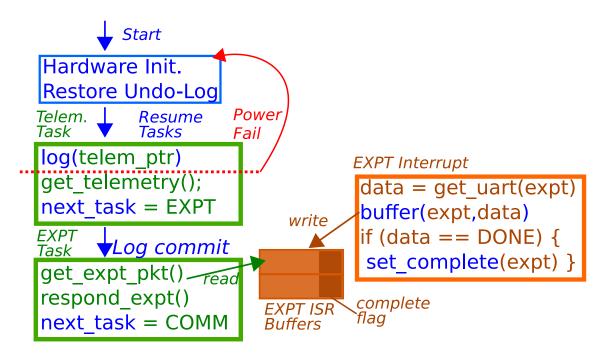

| 6.6 | <b>CTRL failure-aware programming.</b> CTRL programs are written       |    |

|     | as a series of tasks (shown in green). The power-failure-aware runtime |    |

|     | components (shown in blue) correctly restart the program after a       |    |

|     | power-failure. Interrupts from the TAB (in orange) share data with     |    |

|     | tasks through a managed buffer (center).                               | 33 |

# List of Tables

| 3.1 | A summary of the Coati API. t is a task, ev is an event bottom, x a variable, val a value, and type a C type                                                                                                                                                                                                          | 38 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | <b>Commit Statistics.</b> The average and maximum number of entries committed at the end of each task and transaction in benchmark applications.                                                                                                                                                                      | 42 |

| 3.3 | <ul> <li>Correctness. Coati prevents incorrect behavior during intermittent execution. Using Alpaca alone, most applications crash or hang.</li> <li>✓ indicates correct execution, X is incorrect. Mean time to failure (MTTF) varies with event timing, and application behavior, not measurement error.</li> </ul> | 44 |

| 3.4 | <b>Programming Effort.</b> Coati (C) reduces the effort to write correctly synchronized code. Synchronizing the code by hand(H) required up to 10x more lines of code to manage extra variables, tasks and transitions.                                                                                               | 45 |

| 4.1 | A summary of the Pudu API. per is a peripheral. state is a peripheral typestate value. func is a function. ISR is an interrupt triggered by an asynchronous event.                                                                                                                                                    | 65 |

| 4.2 | <b>Pudu dataflow framework.</b> Pudu's framework closely resembles that of the reaching definitions problem. Minor changes include the starting (boundary) conditions and the addition of active ISRs $(isrs(B))$ to a block's predecessors.                                                                          | 69 |

| 4.3 | <b>Peripheral profiling results.</b> The break-even times on a Capybara sensor span two orders of magnitude. The Toggle-Time is the minimum time to shift from sleep to active according to the datasheet                                                                                                             | 74 |

| 4.4 | Peripheral Energy Bug Survey. We characterize potential bugs                                      |     |

|-----|---------------------------------------------------------------------------------------------------|-----|

|     | in terms of the software runtime $(\mathbf{SW})$ , hardware platform $(\mathbf{HW})$ ,            |     |

|     | application $(App)$ , lines of code $(LoC)$ , number of peripherals $(NP)$ ,                      |     |

|     | the peripheral involved as well as it's current savings from toggling $(\mathbf{I})$              |     |

|     | and toggling time $(\mathbf{TT})$ . 💐 indicates a potential BrickBug, 🄌 indicates                 |     |

|     | a BurnBug due to either under $(\bigtriangledown)$ or over $(\bigtriangleup)$ toggling. *Pressure |     |

|     | sensor current is likely higher, data<br>sheet only reports power for $1~\mathrm{Hz}$             |     |

|     | data rate, but it is running at 10 Hz                                                             | 79  |

| 4.5 | BrickBug Results. Pudu-Static correctly identifies all BrickBugs                                  |     |

|     | for both synchronous (S) and asynchronous (A) cases. $\pmb{\times}$ indicates a                   |     |

|     | failure. $\sim$ represents a success as a side-effect of the restoration policy.                  |     |

|     | ✓ indicates successful completion or bug detection. * [220], † [33], ‡                            |     |

|     | $[41]  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                           | 82  |

| 4.6 | Pudu-Static Bug Reports. Atomic blocks with multiple reaching                                     |     |

|     | peripheral typestates trigger Pudu-Static reports. False positives                                |     |

|     | (F.P.) occur if the reported block never caused a BrickBug in testing.                            |     |

|     | F.P's include HAL accesses to driver code, I/O calls, and application                             |     |

|     | logic (App).                                                                                      | 83  |

| 5.1 | Impact of safe starting voltages. Accurate task starting voltages                                 |     |

|     | allow the application to capture interrupts and prevents unexpected                               |     |

|     | failures.                                                                                         | 99  |

| 5.2 | Culpeo-R Runtime calls. id is a task identifier.                                                  | 108 |

| 5.3 | Culpeo on-chip command interface Culpeo on-chip is a memory-                                      |     |

|     | mapped peripheral with two control and data registers                                             | 111 |

| 5.4 | <b>Loads tested.</b> Description of different loads used in our evaluation                        | 112 |

## Chapter 1

## Introduction

As the Internet of Things (IoT) expands, it is pushing more and more deeply embedded sensors out into the world. These sensors gather critical data from their environment and perform some actuation in response or transmit the data to a more powerful base station to relay across a network. It is these tiny nodes well beyond "the edge" [214] of a distributed network that provide the essential information to make a smart and connected world a reality. However, as sensor data volumes grow, these devices do more than basic sense-and-send tasks. To improve reliability [132], reaction time [99], and energy efficiency [98] deeply embedded sensors can use onboard compute resources to process the sensed information before acting on it.

In typical sensor network applications for IoT, battery-powered motes schedule sensing, processing, and compute tasks with sleep operations that drop the device into a low-power wait state [84, 141, 209]. Programming models for battery-powered motes are designed to help the programmer maximize battery life given a set of applications. The goal is to do as little as possible and still meet application demands. Eventually, though, the battery is fully discharged and the device is dead until the battery is replaced. In contrast, energy-harvesting sensor nodes greatly extend device lifetime by using rechargeable batteries or capacitors to store energy captured from the environment [7, 59, 88, 124, 128, 180, 216]. Energy-harvesting systems capture sources like solar, RF, vibration, or temperature gradients [180, 229, 260, 279].

However, rechargeable batteries do not solve all challenges associated with ubiquitous computing initiatives. Reducing system weight, volume, or cost can preclude the use of batteries entirely in applications like miniature satellites [285], inside the body [62, 119, 156, 211] or object tagging [208]. Uncontrolled environments also can be out of scope for batteries due to temperature constraints [171, 194] or humidity [8]. Further, size and weight constraints limit the harvestable power in addition to the available energy by capping the size of harvesters. For instance, solar harvester power is determined by the area of the panel- the power drops off as the size is reduced to fit in a tiny envelope. If the power to run the sensor, including the central microcontroller (MCU), and the peripheral sensors, radios, and actuators, exceeds the harvested power, the device must draw the energy from its energy buffer, a capacitor. In highly constrained systems, the capacitor discharges rapidly and the device is forced to power off. Once the device is off and no longer using power, the harvester can refill the energy buffer and the device can once again turn on. As strange as a device that intentionally turns on and off may seem, prior work has succeeded in building complex applications including maintenance-free sensing [8, 44, 110, 122, 217, 229], gaming [64], image processing [191, 193], miniature robotics [233] and machine learning [99, 121, 193]. This thesis focuses on these *batteryless* devices that use a capacitor for an energy buffer and harvest too little power to operate continuously.

The key innovation from prior work that enabled long running applications (i.e. those that take more energy than is ever available in the energy buffer) is an execution model called *intermittent* computing. Intermittent computing extends the lifetime of a software task across hardware power failures. This work started in the domain of Computational RFID tags (CRFIDs), and allowed CRFIDs to compute very slowly [44, 217, 229, 290, 292] with minimal harvested power. Novel circuitlevel hardware support for intermittent computing pursues low-power persistent memory technologies tightly integrated with the processor [170] or in the memory [127, 261, 262], integrated checkpointing [269] and cheap voltage monitoring [280]. However, this thesis focuses on software and printed-circuit board (PCB) level support for intermittent systems, working only with commodity MCUs, sensors, actuators and power system components, composed in novel ways. Focusing on commodity hardware enables batteryless device usage in the short term and defines strategies that can reduce cost in the future. For instance, supporting the mixture of volatile and non-volatile memory in commodity MCUs [268] allows batteryless devices to use cheap, well established, low-power MCUs instead of an exotic fabrication technology [170].

The original runtime support for intermittent execution was designed for applications with tens of milliseconds of active time on each reboot. Subsequent software work followed suit and developed *task-based* programming models [55, 168, 174] that minimize the overhead of computing across power failures. These models divide the program into atomic regions of code and guarantee that the regions will eventually complete from start to finish, without an intervening power failure, and do so idempotently. The problem though, is this work only focused on how to extend compute across power failures. It relied on extremely basic peripheral sensors and actuators, including nearly passive radio communication [164], on-chip ADCs [168] and LEDs [168]. Such restrictions are necessary for CRFIDs– doing any more than quickly reading from a peripheral is prohibitively expensive for truly tiny devices. However, peripherals are absolutely critical to the mission of batteryless systems. Putting a computer in a hard-to-reach physical location is only useful because it is co-located with peripherals to sense data that cannot be acquired by other means. Radios or actuators (which are peripherals) then allow the device act on the data.

#### 1.1 Peripherals in Batteryless Devices

To understand the challenge of adding peripherals to an intermittent execution, we must consider the typical hardware architecture of a batteryless device. To the best of our knowledge, all batteryless systems give a single MCU the responsibility to restore state after power failures, coordinate peripheral power access [57, 61, 284] and manipulate peripheral configuration [33, 41, 220]. Peripherals may be complete Systems on Chip (SoCs) in their own right, but we consider any chip that is not failure-aware (i.e. the central MCU) a peripheral. It is thus the MCU's job to manage all of the constraints a peripheral places on a program and all of its *state*. State in this thesis comprises the memory, and configuration of a peripheral. The MCU must persist concurrent changes to peripheral state and satisfy peripheral *constraints*, including timeliness and energy requirements, while the whole device is executing intermittently.

Managing peripherals on batteryless devices is more difficult than on a continuously powered device for two major reasons: first, peripheral state is cleared on a power failure, second, peripherals consume a large percentage of the total energy budget of a batteryless device. When power fails, each peripheral's configuration, i.e. the operating mode that results from commands sent by the MCU, is assumed to be lost because the voltage supplied to the peripheral (likely) falls below its minimum operating voltage. Upon reboot, the MCU must carefully reinitialize peripherals before using them to prevent the program from hanging due to a misconfigured peripheral. Further, the dynamic software state shared with the peripheral, e.g. memory accesses and code in a peripheral triggered interrupt service routine (ISR), is also lost in the event of a power failure. If a power failure interrupts an ISR, the ISR is not restarted on reboot– the source of the interrupt is gone. The loss of state forces the programmer to judiciously use peripherals with predictable access patterns, e.g. polling, and their relatively high power raises the cost of mismanaging a peripheral.

Figure 1.1 shows the percentage of the total power each peripheral individually consumes on the Capybara [57] batteryless sensing and computing platform. On a single platform, the cost ranges from 10% to 40% to run one peripheral at a time. That said, the actual impact of a peripheral (i.e. the same sensor) will vary between devices and deployment scenarios. For instance, if a peripheral deployed on a solar powered sensor that generates 90 mW [166] is moved to an RF harvesting node (10 mW [183]), its effect on the system behavior will be more pronounced. Beyond the total system power, the incoming power determines which sensors will have a noticeable impact on end-to-end efficiency. Similarly, decreasing the frequency of the central MCU can change the system's baseline power by more than 8x [268], which increases the percentage of system power attributed to a peripheral. As a result, it is difficult for a software developer to know when to prioritize peripheral state management, i.e. strategically putting the peripheral to sleep to save power, and the effort to manage peripherals is non-trivial.

Previous work in intermittent computing guaranteed correctness strictly in terms of the memory state of the MCU [55, 174, 254], and subsequent models addressed other aspects of running peripherals including timeliness [63, 111, 148, 253], atomic operation [57, 176, 253], and peripheral configuration [33, 41, 220]. The problem is that these models are not designed to work together. In fact, we show that combining seemingly independent pieces of system support for using peripherals on batteryless systems causes buggy execution.

Figure 1.1: Peripheral Power Percentage. The peripherals on a Capybara device consume a large percentage of the total power, but there is a wide range based on the exact peripheral configuration.

### 1.2 Thesis Statement & Contributions

The goal of this thesis is to manage the shared state that exists between peripherals and the central MCU. On a batteryless device, the failure-aware MCU explicitly coordinates a large set of failure-agnostic peripherals from the main loop of a program. However, additional state is shared between the MCU and peripherals, e.g ISR accesses to global memory, that implicitly allow peripherals to affect the program running on the MCU. This thesis identifies unintended interactions that emerge between peripherals and the MCU in batteryless devices and builds programming models, compiler tooling, and light-weight hardware models to correct them. In the course of demonstrating the interactions, removing the problem, and evaluating the results on batteryless hardware, we demonstrate the validity of the following thesis:

System support for managing the data, power, and energy state that are shared by peripherals and the central microcontroller improves the reliability, performance, and programmability of batteryless, energyharvesting devices.

The key contributions of this thesis are as follows:

1. We identify concurrency control bugs in task-based languages for intermittent execution that prevent programmers from correctly synchronizing accesses to shared memory from peripheral-triggered interrupt service routines. We then propose a programming model that provides correct, low-overhead access to shared data.

2. We describe a new category of energy bugs due to changes in peripheral operating power that cause hard-stop failures in batteryless systems and demonstrate the effects in hardware. We propose a programming interface and compiler tool that reports potential hard-stop energy bugs.

3. We demonstrate that peripheral mismanagement in the context of batteryless energy harvesting systems manifests as application-wide slowdowns. We develop a failure-aware runtime module that automatically configures peripherals to minimize their total energy consumption.

4. We show that energy-based assumptions for peripheral event scheduling fail when using dense supercapacitors as an energy buffer. We develop a lightweight model to accurately predict the effect of a software task (e.g. peripheral access) on the state of the energy buffer at runtime.

5. We apply the peripheral-induced bug awareness accrued in this thesis to build an energy-harvesting power system and failure-aware control system for a batteryless nanosatellite. The failure-aware subsystems support a wide range of failure-agnostic peripherals that allow for greater flexibility and reduced development effort when building complex batteryless systems.

Detailing the range of problems that occur as system developers integrate more capabilities into batteryless systems clarifies the gap between where system support for intermittent execution is, and where it needs to be. The tooling presented in this thesis takes one step towards closing that gap, and empowers developers to build impactful batteryless applications.

#### 1.3 Outline

The remainder of this thesis is organized into six chapters. This introduction explained the basics of intermittent execution as a model of computation to motivate the importance of this work's contributions. Chapter 2 will delve into the specifics of the hardware and software that underpin batteryless applications before exploring trends in intermittent computing literature that motivate this thesis' focus on peripherals. With the background in place, we move on to Chapters 3-5 which each describe a different type of state shared between peripherals and the central MCU.

Chapter 3 poses the question, how should intermittent execution models support arbitrary accesses to shared memory? After exploring the software bugs that can emerge while trying to control concurrent accesses to shared memory, this chapter ultimately answers "it shouldn't". We demonstrate in this chapter that supporting arbitrary access to shared memory while allowing flexible semantics has a prohibitively high overhead in many cases. Instead, we propose Coati [224], a programming model and runtime implemented in C that restricts the quantity of data that is actually shared between asynchronous and scheduled code. The restriction allows Coati to minimize the overhead of shared state and achieve concurrency control with little programmer effort.

Chapter 4 continues the theme of bugs due to concurrent peripheral accesses, but we study the system-wide effects of an individual peripheral's power consumption instead of its accesses to shared memory. In this study, we find that a programmer's decision of whether or not to turn off a peripheral after using it has a substantial effect on the performance and correctness of an application. In particular, we examine the consequences of system support for intermittent execution that does not consider peripheral power. We show that the resulting systems are not composable without introducing the potential for fail-stop bugs. We then develop a methodology called Pudu to remove the bugs that result from peripheral power. Pudu comprises a set of annotations, implemented in C, that indicate changes in peripheral power as well as compile-time and runtime components implemented, respectively with LLVM [153] and C. Using the Pudu methodology we identify bugs that cause hard-stop failures and remove the inefficiency of poor power management code.